高速数模转换器的设计思路

解读高速数模转换器(DAC)的建立和保持时间

解读高速数/模转换器(DAC)的建立和保持时间Oct 10, 2007摘要:本应用笔记定义了高速数/模转换器(DAC)的建立和保持时间,并给出了相应的图例。

高速DAC的这两个参数通常定义为“正、负”值,了解它们与数据瞬态特性之间的关系是一个难点,为了解决这些难题,本文提供了一些图例。

介绍为了达到高速数/模转换器(DAC)的最佳性能,需要严格满足数字信号的时序要求。

随着时钟频率的提高,数字接口的建立和保持时间成为系统设计人员需要重点关注的参数。

本应用笔记对建立和保持时间进行详尽说明,因为这些参数与Maxim的高性能数据转换方案密切相关。

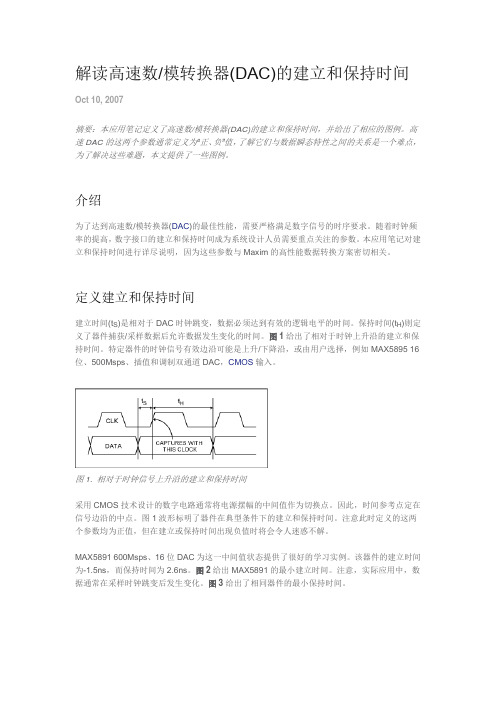

定义建立和保持时间建立时间(t S)是相对于DAC时钟跳变,数据必须达到有效的逻辑电平的时间。

保持时间(t H)则定义了器件捕获/采样数据后允许数据发生变化的时间。

图1给出了相对于时钟上升沿的建立和保持时间。

特定器件的时钟信号有效边沿可能是上升/下降沿,或由用户选择,例如MAX5895 16位、500Msps、插值和调制双通道DAC,CMOS输入。

图1. 相对于时钟信号上升沿的建立和保持时间采用CMOS技术设计的数字电路通常将电源摆幅的中间值作为切换点。

因此,时间参考点定在信号边沿的中点。

图1波形标明了器件在典型条件下的建立和保持时间。

注意此时定义的这两个参数均为正值,但在建立或保持时间出现负值时将会令人迷惑不解。

MAX5891 600Msps、16位DAC为这一中间值状态提供了很好的学习实例。

该器件的建立时间为-1.5ns,而保持时间为2.6ns。

图2给出MAX5891的最小建立时间。

注意,实际应用中,数据通常在采样时钟跳变后发生变化。

图3给出了相同器件的最小保持时间。

图2. MAX5891的最小建立时间图3. MAX5891的最小保持时间为满足这些是需要求,用户需要分析数据源的传输延迟和抖动。

传输延迟决定了时钟的标称定时要求,而抖动指标则决定了所允许的容限。

为了解释这一关系,我们以具有1.5ns传输延迟的逻辑门电路为例。

数模转换器工作原理

数模转换器工作原理数模转换器(ADC)是一种电子设备,它可以将连续的模拟信号转换成离散的数字信号。

这种转换器在现代电子设备中被广泛应用,比如数字音频设备、数字电视、数字相机等等。

在这篇文章中,我们将深入探讨数模转换器的工作原理,了解它是如何将模拟信号转换成数字信号的。

首先,让我们来了解一下模拟信号和数字信号的概念。

模拟信号是连续变化的信号,它可以取任意的数值。

比如我们平时听到的声音、看到的图像等都是模拟信号。

而数字信号是离散的信号,它只能取有限个数值。

在计算机和数字设备中,所有的信号最终都会被转换成数字信号进行处理。

数模转换器的工作原理可以分为三个主要步骤,采样、量化和编码。

首先是采样,即将连续的模拟信号在时间上进行离散化。

这个过程是通过一个时钟信号来控制的,时钟信号会以一定的频率对模拟信号进行采样,将连续的信号转换成离散的信号。

采样的频率通常以赫兹(Hz)为单位,常见的采样频率有44.1kHz、48kHz等等。

接下来是量化,即将采样得到的离散信号转换成数字信号。

量化的过程是通过一个模数转换器(ADC)来完成的。

模数转换器会将采样得到的离散信号转换成一系列的数字代码,这些代码代表了信号的幅度。

量化的精度通常以位数来表示,比如8位、16位、24位等等,位数越多,表示精度越高,能够更准确地表示原始信号的幅度。

最后是编码,即将量化得到的数字代码转换成二进制形式。

这个过程通常是通过一个编码器来完成的,编码器会将数字代码转换成二进制形式,以便于数字设备进行处理和存储。

总的来说,数模转换器的工作原理可以简单概括为将连续的模拟信号经过采样、量化和编码三个步骤转换成离散的数字信号。

这种转换过程是通过时钟信号、模数转换器和编码器来完成的。

数模转换器的性能取决于采样频率、量化精度和编码方式,不同的应用场景需要选择合适的数模转换器来满足其要求。

在实际应用中,数模转换器的性能对于信号的质量和精度有着重要的影响。

因此,在设计数字设备和电子系统时,需要根据具体的应用需求选择合适的数模转换器,以确保信号的准确性和稳定性。

高速ADC的结构和工作原理

3.6高速ADC电路结构和工作原理目前,高速ADC主要有逐次逼近型,并行比较型(闪烁型),分级型(半闪烁型)和流水线型等几种电路结构。

其中,逐次逼近型是较为经典的低成本电路结构,主要用于中高速(<1MSPS)分辨率在(10至16位)场合。

并行比较ADC 是现今速度最快的模/数转换器,采样速率可达到1GSPS以上,本节主要介绍后几种。

3.6.1并行比较型(闪烁型)模数转换器(Flash ADC)并行ADC通常也称为“闪烁式”ADC。

它由电阻分压器、比较器、缓冲器及编码器四部分组成。

这种结构的ADC所有位的转换是同时完成的,其转换时间主要取决于比较器的开关速度、编码器的传输时间延迟等。

增加输出代码对转换时间的影响较小,但随着分辨率的提高,需要高密度的模拟设计以实现转换所必需的数量很大的精密分压电阻和比较器电路。

输出数字增加一位,精密电阻数量就要增加一倍,比较器也近似增加一倍。

例如,n位的ADC需要2n个精密电阻和2n-1个并联比较器。

分压电阻网络的电压彼此相差1个最低有效位V R/2n。

原理电路如下图所示。

闪烁式ADC要实现快速转换,每个比较器必须在相当高的功率状态下工作。

如果要求提高其分辨率,除了增加比较器和电阻器的数量以外,基准电阻链上的每个电阻值都要很低,以对快速比较器提供足够大的偏置电流,从而要求基准电压源必须提供相当大的电流(>10mA)。

因此闪烁式ADC存在的问题是有限的分辨率,功耗大和芯片尺寸大(从而成本高)。

闪烁式ADC的分辨率受管芯尺寸、过大的输入电容、大量比较器所产生的功率消耗等限制。

结构重复的并联比较器如果精度不匹配,还会造成静态误差,如会使输入失调电压增大。

同时,这一类型的ADC由于比较器的亚稳态、编码气泡,还会产生离散的、不精确的输出,即所谓的“火花码”。

这类ADC的优点是模/数转换速度最高,缺点是分辨率不高,功耗大,成本高。

注解:“火花码”根据闪光式ADC的电路结构,在使用时应该考虑所有的静态误差源和动态误差源。

传统数模转换器的优缺点分析及高性能PWM-DAC的基本设计思想

传统数模转换器的优缺点分析及高性能PWM-DAC的基本设计思想辛德环【摘要】分析了基于零阶保持器( ZOH)原理的传统数模转换器(DAC)和线性功率放大器的优点和缺点,以及基于脉冲宽度调制( PWM)技术的D类功率放大器在节能方面的优势和性能上的不足.详细分析了数字PWM调制器( PWM- DAC)的基本原理并推导其算法,进行了性能仿真分析计算,证明了用PWM-DAC同时完成数模转换和PWM调制的可行性,结果表明,这种转换性能优良.【期刊名称】《机械工程师》【年(卷),期】2011(000)010【总页数】5页(P29-33)【关键词】脉冲宽度调制;PWM;PWM波;数模转换器;数字化PWM调制【作者】辛德环【作者单位】北京航空航天大学自动化科学与电气工程学院,北京100191【正文语种】中文【中图分类】TP212虽然离散控制理论已经发展成熟,在多数情况下,通过细致的设计,可以获得媲美连续控制系统的性能,但是当回首离散控制理论几十年的发展过程,我们发现,对于离散信号-连续信号的转换过程,并没有得到研究者的关注,而且几十年来一直停滞不前[1]。

1 传统数模转换器的优缺点分析1.1 传统数模转换器(DAC)的困局1.1.1 信号的离散与连续离散控制理论引入了采样的概念,将信号进行时间离散化,便于计算机进行处理和储存。

但是,信号最终还要以时间连续信号的形式进行输出,为了完成这一转换过程,多种转换器件的概念被提出,如ZOH(Zero-Order-Hold 零阶保持器),FOH(First-Order-Hold 一阶保持器),延迟一拍FOH。

其中ZOH 由于更好的动态性能和更小的相位延迟得到了最广泛的应用。

但ZOH 并不是理想的转换器件,首先,ZOH 的输出信号是阶梯信号,这可引起信号失真,向输出信号中加入高次谐波;其次,ZOH 只有在采样数据到来之后输出才有响应,且在下一个采样周期内保持不变,由于ZOH 的输出信号在每个采样周期内保持不变,这将引起信号的传递延迟,如图1。

2Gbps GaAs单片4bit数模转换器的设计与实现

tc n l g n NEDI 7 e h oo y i 6 mm Asp o e s l e Ga r c s i .DAC i d sg e o n wae / i e a c n s e in d f ro fr IO mp d n e

ma c ig t t hn .IsDⅣ L i s± 0 2 L B,a d Ⅳ L i .2S n s± 0 4 LS Th c u a yo hs4 i DAC i u o . 5 B. ea c r c ft i bt p t s 5 2bt . i.Th ic i h st o ecr ut a wo c mpe e t r u p t . n t o g t r c a a trs i h sn rf. lm n a yo t u s a disln e m h r ce it a od it c

De i n a a i a i n o G b a s 4 t D AC s g nd Re lz t o f 2 ps G A bi

Z HANG u a 。 XI Gu n u GAO in e g M x a 。 Yo to ・ A a q n Ja fn Fu io

张 涛 有 夏冠 高 李 。 群 建峰 拂晓

(中国科学院上海微系统与信息技术 研究 所 。上海 , 0 0 0 。 2 0 5 )(南京电子器件研究所 , 南京 ,2 0 1 ) 1 0 6

20 —2 2 0 40— 7收 稿 ,0 40 一 l 改稿 2 0— 6O 收

摘 要 : 述 了 单 片 超 高 速 2 p As4 i数 模 转 换 器 ( AC) 设 计 、 造 及 测 试 。在 南 京 电子 器 件 研 究 所 标 详 Gb sGa bt D 的 制 准 7 G As 艺 线 采 用 0 5 6 m a 工 n . m 全 离 子 注 入 ME F T 工 艺 完 成 流 片 芯 入 输 入 输 出 阻抗 实 现 在 片 5 匹 配 SE On 4bt AC 的 微 分 非 线 性 ( | ) 土0 2 最 低 有 效 位 ( S ) 积 分 非 线性 (ⅣL 为 土0 4 L B, 到 5 2bt iD DⅣL 为 .2 LB, ) .5 S 达 . i 的转 换

基于电流舵的高精度低功耗13-bits DAC设计

76电子技术Electronic Technology电子技术与软件工程Electronic Technology & Software Engineering数模转换器(Digital-to-Analog Converter ,简称DAC ),顾名思义,是集成电路领域中连接数字电路和模拟电路的桥梁,亦是数字电路系统与外部模拟信号世界间交换信息的主要渠道。

利用DAC ,可以将离散的数字信号转化为连续的模拟信号,其在现代5G 通信、高速雷达探测、医疗通信系统及物联网等信号处理过程中扮演着不可或缺的角色,重要性不言而喻。

目前,随着集成电路技术的飞速发展,各电子技术应用领域对DAC 的指标性能也提出了更加苛刻的要求,研究和设计低功耗、宽范围、高精度、高速率的数模转换器具有十分重要的实践意义。

传统的DAC 结构有权电阻结构、R-2R 结构、电荷分布结构等;一般地,电压型DAC 多用于低速转换器内,且电阻结构中电阻的数量会随着转换位数的增加而带来版图面积的消耗。

因此,在高速、高精度的应用需求下,设计一款性能优越的电流舵型DAC 将对通信领域起到推动型的作用。

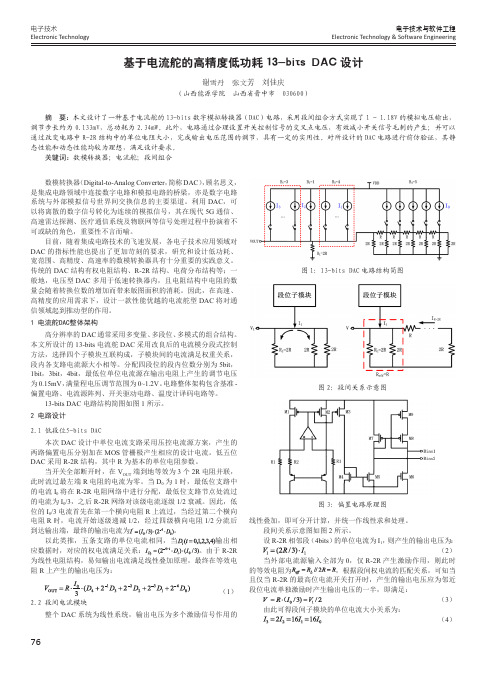

1 电流舵DAC整体架构高分辨率的DAC 通常采用多变量、多段位、多模式的组合结构。

本文所设计的13-bits 电流舵DAC 采用改良后的电流模分段式控制方法,选择四个子模块互联构成,子模块间的电流满足权重关系,段内各支路电流源大小相等。

分配四段位的段内位数分别为5bit ,1bit ,3bit ,4bit ,最低位单位电流源在输出电阻上产生的调节电压为0.15mV ,满量程电压调节范围为0~1.2V 。

电路整体架构包含基准-偏置电路、电流源阵列、开关驱动电路、温度计译码电路等。

13-bits DAC 电路结构简图如图1所示。

2 电路设计2.1 低段位5-bits DAC本次DAC 设计中单位电流支路采用压控电流源方案,产生的两路偏置电压分别加在MOS 管栅极产生相应的设计电流。

模数和数模转换器(ADC和DAC)工作原理

模数和数模转换器(ADC和DAC)工作原理为了能够使用数字电路处理模拟信号,必须把模拟信号转化成相应的数字信号,方能送入数字系统进行处理.同时也要把处理后得到的数字信号在转换成相应的模拟信号,作为最后的输出.我们把前一种从模拟信号到数字信号的转换叫做模-数转换,或简称A/D;把后一种从数字信号到模拟信号的转换叫做数-模转换,或简称D/A.同时把A/D或D/A 转换的电路叫做模数转换器(简称ADC)或数模转换器(简称DAC)主要分成以下几个部分:1、取样:取样(也称采样)是将时间上连续变化的信号,转换为时间上离散的信号,即将时间上连续变化的模拟量转换为一系列等间隔的脉冲,脉冲的幅度取决于输入模拟量。

2、保持:模拟信号经采样后,得到一系列样值脉冲。

采样脉冲宽度一般是很短暂的,在下一个采样脉冲到来之前,应暂时保持所取得的样值脉冲幅度,以便进行转换。

因此,在取样电路之后须加保持电路。

3、量化:将采样后的样值电平归化到与之接近的离散电平上,这个过程称为量化。

4、编码:把量化的结果用代码表示出来,称为编码。

这些代码就是A/D转换的输出结果。

模拟信号数字化需要注意两个问题:①每秒钟需要采集多少个信号样本,也就是采样频率(fs)是多少,②每个信号样本的比特数b/s(bit per sample)应该是多少,也就是量化精度。

根据奈奎斯特理论(Nyquist theory),采样频率的高低是由模拟信号本身的最高频率决定的。

奈奎斯特理论指出,采样频率不应低于模拟信号最高频率的两倍,这样就能把以数字表达的信号还原成原来的信号,这叫做无损数字化(lossless digitization)。

采样定律用公式表示为fs ≥ 2f或者T s ≤ T/2其中f为被采样信号的最高频率,T为被采样信号的最低周期,fs 称为采样频率,Ts为采样间隔。

如下图,图中的正弦曲线代表原始音频曲线;填了颜色的方格代表采样后得到的结果,二者越吻合说明采样结果越好。

详谈数模转换器(DAC)的工作原理与应用

详谈数模转换器(DAC)的工作原理与应用数模转换器是执行转换操作的电子设备。

顾名思义,它将数字输入信号转换为模拟输出信号。

可以使用数模转换器将诸如数字音乐之类的数字信号转换为模拟声音。

它是数据转换器的一种。

数模转换器也称为数模转换器,D转换器,数模转换器转换器,D / A转换器等,数模转换器(ADC)进行反向操作。

一、数模转换器的工作原理数模转换器是用于数模转换的设备。

数字信号定义为时间离散和幅度信号离散。

同时,将模拟信号定义为时间连续和连续幅度信号。

数模转换器将定点二进制数字(适当的抽象精度数字)转换为物理测量结果。

数模转换器基于Nyquist-Shannon采样定理工作。

它指出–如果采样率大于或等于输入信号中存在的最高频率分量的两倍,则可以从其采样输出中恢复输入信号。

有几个参数可以测量数模转换器的性能。

输出信号的带宽,信噪比是一些参数。

二、数模转换器的电气符号数模转换器的符号三、数模转换器的应用1、音频处理在当今的数字化时代,音乐和其他音频以数字化格式存储。

当我们需要在扬声器或耳机中听到它们时,则必须将数字形式转换为模拟信号。

这就是为什么在每个可以播放音乐的设备中都找到数模转换器的原因,例如MP3音乐播放器,DVD播放器,CD播放器,笔记本电脑,移动电话等。

高端高保真系统使用专用的独立数模转换器。

在现代数字扬声器(例如USB扬声器,声卡等)中可以找到类似的数模转换器。

在IP语音通信中,源被数字化。

因此,需要一个数模转换器将数字化部分重构为模拟信号。

2、视频编码视频编码器系统处理视频信号并将数字信号发送到IC。

3、数字显示图形控制器通常使用查找表来生成发送到模拟输出的信号(例如RGB信号)以驱动显示器。

4、校准数模转换器可以提供动态类型的校准,以提高测试系统的精度。

5、控制电机数模转换器还用于需要电压控制信号的电动机控制设备中。

数模转换器还用于数据分配系统,数字电位计,软件无线电和许多其他地方。

多路高速adc方案

多路高速ADC方案概述多路高速ADC(Analog-to-Digital Converter)方案是指针对需要同时采集多个模拟信号并将其转换为数字信号的应用场景所设计和实现的方案。

在很多领域,如无线通信、医疗设备、机器人和仪器仪表等领域中,需要对多个信号进行实时采集和处理。

因此,多路高速ADC方案变得非常重要。

本文将介绍多路高速ADC方案的基本原理以及常见的设计和应用。

多路高速ADC原理多路高速ADC方案的基本原理是将多个输入模拟信号经过采样和转换,转换为数字信号进行处理。

它主要包括以下几个关键步骤:1.采样:采样是将连续的模拟信号转换为离散的样本值,通常使用模拟开关或采样保持电路来完成。

采样率需要根据信号频率和需要的精度来确定,通常以每秒采样次数(Samples per Second,SPS)来表示。

2.AD转换:模拟-数字转换器(ADC)将采样后的模拟信号转换为数字信号。

根据使用的ADC器件不同,可以将模拟信号转换为不同的数字编码方式,如二进制码、格雷码等。

3.数据处理:将数字信号进行处理,如滤波、放大、校正等。

根据具体应用,可能还需要进行数字信号的数字滤波、调制解调、时域分析等操作。

4.输出:将数字信号转换为对应的输出形式,如数字显示、数据存储、通信传输等。

多路高速ADC设计方案选择合适的ADC器件在设计多路高速ADC方案时,选择合适的ADC器件非常重要。

常见的ADC器件有逐次逼近型(Successive Approximation,SAR)ADC、ΔΣ型(Delta-Sigma,ΔΣ)ADC和高速平行型(High-Speed Parallel,HSP)ADC等。

•SAR ADC:逐次逼近型ADC采用比较器和逐次逼近寄存器来实现AD 转换,具有较高的抗噪声性能和较低的功耗,适合用于低功耗和较低采样率的应用。

•ΔΣ ADC:ΔΣ型ADC采用ΔΣ调制器和数字滤波器来实现AD转换,具有较高的精度和动态范围,适合用于精密测量和高精度的应用。

S7-200模拟量转换器设计算法

S7-200模拟量转换器设计算法介绍本文档介绍了S7-200模拟量转换器的设计算法,该算法用于将模拟量输入信号转换为数字信号,以实现与S7-200 PLC的通信。

算法设计步骤1. 确定输入信号范围:首先,需要确定输入模拟量的范围,例如0-10V或4-20mA。

这将有助于后续的转换计算。

确定输入信号范围:首先,需要确定输入模拟量的范围,例如0-10V或4-20mA。

这将有助于后续的转换计算。

2. 标定系数计算:标定系数用于将模拟量输入信号映射到数字输出信号的范围。

标定系数的计算方法如下:标定系数计算:标定系数用于将模拟量输入信号映射到数字输出信号的范围。

标定系数的计算方法如下:- 对于0-10V的输入信号范围,标定系数计算方法如下:模拟量输入范围 = 10V - 0V = 10数字输出范围 = - (-) =标定系数 = 数字输出范围 / 模拟量输入范围= / 10 ≈ 6553.4- 对于4-20mA的输入信号范围,标定系数计算方法如下:模拟量输入范围 = 20mA - 4mA = 16数字输出范围 = - (-) =标定系数 = 数字输出范围 / 模拟量输入范围= / 16 ≈ 4095.8753. 输入信号转换:通过计算将输入模拟量信号转换为数字信号。

转换方法如下:输入信号转换:通过计算将输入模拟量信号转换为数字信号。

转换方法如下:- 对于0-10V输入信号范围,使用以下计算方法:输入信号数值 = 输入信号电压值 / 标定系数- 对于4-20mA输入信号范围,使用以下计算方法:输入信号数值 = (输入信号电流值 - 4) / 标定系数4. 输出信号处理:根据需要,对数字信号进行进一步处理,例如取整或四舍五入。

输出信号处理:根据需要,对数字信号进行进一步处理,例如取整或四舍五入。

5. 传输至S7-200 PLC:将转换后的数字信号传输至S7-200 PLC,以实现与PLC的通信和控制。

传输至S7-200 PLC:将转换后的数字信号传输至S7-200 PLC,以实现与PLC的通信和控制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

高速数模转换器的设计思路及应用考虑(上) 北京市英赛尔器件集团(100044)高 工 中国科学院长春物理研究所(130021)徐 健

摘 要: 在分析影响高速数模转换器的主要问题(毛刺和无杂散动态范围)基础上,总结出四种基本电路结构的设计思路及应用考虑。 关键词: 毛刺 无杂散动态范围 全译码式DAC 分段式DAC 插值式DAC

1 概述 随着通信事业、多媒体技术和数字化设备的飞速发展,促进了高速(一般指更新速率大于1MS PS)数模转换器(DAC)有了长足进步,牵动着DAC制造商研制出许多新结构、新工艺及各种特殊用途的高速DAC。譬如用于通信系统信号发送信道的TxDAC,用于CRT光栅扫描系统的Video DAC,用于CD唱机再现音频信号的Audio DAC。有些Video DAC内部含有调色板存储器并且 具备图形显示系统常用功能的DAC又称作RAMDAC。高速DAC的应用领域主要有三个方面:(1)数字化仪器,包括波形重建和任意波形发生器;(2)直接数合成(DDS),包括接收器本机振荡器、跳频无线电设备、通信系统、正交调制(QAM)系统和雷达系统;(3)图形显示系统,包括失量扫描和光栅扫描。为了满足高速DAC上述应用领域的要求,提高DAC的动态技术指标,美国模拟器件公司(ADI)在DAC电路结构上做了一系列改进,研制出带SHA式DAC、全译码式DAC,分段式DAC以及插值式DAC。本文通过对高速DAC的设计思路及应用考虑做简单综述,希望能对读者应用高速DAC有所裨益。

2 影响高速DAC的主要问题 21 主要动态技术指标 高速DAC的主要动态(或交流)技术指标: 建立时间(settling time),通常指DAC从数字输入变迁(通常从半满度即50%点,例如从011„11到100„00)开始到达并保持在规定终值附近的误差带(一般为±1/2LSB)所需要的时间。

输出更新速率(output update rate),指从数据寄存器精确地向DAC传输数据的速率,但并不意味着这个速率能达到规定位数的精度。无杂散动态范围(SFDR),指在规定带宽范围内,DAC输出信号幅度的有效值与峰值杂散信号的有效值之差,通常用分贝(dB)表示。

总谐波失真(THD),指DAC输出前6次谐波总有效值与输入信号(基波)有效值之比,可用百分比表示,也可用分贝(dB)表示。毛刺脉冲(glitch impulse),指由于DAC的开关时间不对称引起的讨厌的瞬变,它是影响高速DAC的关键指标。

22 毛刺的产生机理、性质及其表示方法 近年来DAC制造商一直围绕如何消除或减小毛刺脉冲的影响研制出不同结构的高速DAC,所以有必要清楚地了解毛刺脉冲的成因、性质及其表示方法。当DAC的输入发生变迁(即从一个数码跳变到另一个数码)时,理想情况下DAC的输出波形应该是单调地变化,如图1a所示,实际上会出现类似正脉冲、负脉冲或两者都出现(见图1b,c)。 图1 DAC发生变迁时,产生的尖峰或毛刺 DAC在变迁期间,在输出端出现的这种不受控制的尖脉冲的产生机机理有两种。一种机理是由于数字变迁对模拟输出的电容耦合引起的,通常将这种现象称为

尖峰(spikes)、数模馈通(digital\|to\|analog feedthrough)或电荷迁移。电于电容耦合产生的正尖峰和负尖峰的幅度大约相等(见图1 b),有时又称为双尖峰(过一段时间,它 们或多或少有些消失)。这些尖峰的频率通常很高,而且相当均匀,与数码无关,因此可以滤掉。不论DAC是否加基准电压,这种双尖峰都会出现,一般在零基准电压情况下检测它。另一种机理是由于DAC的电流开关时间不相等(数字输入位同步误差、开关导通时间和关断时间不相等以及传输延迟时间不相等)造成的暂时的杂散输出(ΣΔDAC除外),通常将这种现象称为毛刺(glitch)。由于开关时间上的差异产生的这种毛刺通常是单极性的,幅度很高,而且不加基准电压时不会出现,因此双尖峰与单极性毛刺通常可以区分开。另外这种毛刺与数码相关,所以很难滤掉。毛刺的宽度取决于DAC并行输入各位同步误差和开关时间的差异程度,而其幅度则取决于DAC数码变迁时引起开关切换的数目。通常在主变迁或半满度时,即数码从100„00到0111„111之间产生的毛刺最大,而在其它变迁(例如1/4或3/4满度)情况下毛刺通常都比较小,这是因为在主变迁时DAC的所有位码都发生变化,产生的累积误差最大。

毛刺的大小一般用毛刺脉冲面积(glitch impulse area),即单个毛刺的面积来表示单位是pV\|s(皮伏秒)。为了对不同的DAC产生的毛刺进行比较,必须知道其满度输出电压。 图2中示出A1,A2和A3,A4分别对应两种变迁产生的毛刺脉冲面积。另外用净毛刺脉冲面积表示相对应的变迁产生的毛刺也是很有意义的,即|A1-A2|对应011„1到100„0,|A3-A4|对应100„0到011„1(注意这两种变迁产生的毛刺不同)。因为有两种方法表示毛刺脉冲面积,在具体衡量这项技术指标时,应根据产品说明中的定义,明确函义。 图2 DAC的毛刺脉冲波形 应当指出,TTL兼容DAC,由于TTL逻辑电路采用饱和电压开关,在逻辑电平正向跳变和负向 跳变之间的延迟时间和上升时间差异很大,所以毛刺作用明显。然而ECL兼容DAC,由于使用 非饱和电流开关,其正向跳变和负向跳变的延迟时间差异很小,所以许多低失真高速DAC都 采用非饱和电流开关。

23 毛刺对DAC输出频谱的影响 我们考虑由数字数据产生的DAC重建波形,发现除了期望的频谱(根据重建波形的性质,应该 含有一种以上的频率成份)还应有噪声和失真分量。与数码相关的毛刺在谱带内和谱带外都 会产生谐波。因为在半满度变迁时产生的毛刺在重建正弦波一个周期内出现两次(每次越过 半满度都出现一次毛刺),所以产生二次谐波,

如图3所示。其中信号频率fo=3MHz,采样频率fs=10MHz。由于正弦波的高次谐波的镜像(例如二次谐波的镜像fs-2fo)混叠到奈奎斯特频带(DC至fs/2)内,所以不能滤掉。应当指出,直接从毛刺脉冲面积这一项指标预测总谐波失真或SFDR是很困难的,因为还有其它因素(例如DAC的积分线性误差)对失真有影响。

图3 与数码相关的DAC毛刺对其输出频谱的影响 在许多DDS应用中,DAC输出的谱纯度是主要考虑。即使是理想的N位DAC,在DDS系统中也要产谐波。因为这些谐波的幅度强烈地依赖于输出频率对时钟频率的比率,这个因为DAC量化噪声的谱成份,随着这种比率变化而变化。如果使DAC时钟频率是DAC输出频率的整数倍,那么它的量化噪声集中在输出频率的倍频处,即与信号密切相关。如果使输出频率稍稍偏移整数倍,量化噪声变得比较随机,从而可有效地改善SFDR。

3 高速DAC的几种电路结构 高速低失真DAC的核心问题是去掉毛刺和提高SFDR。采用线性滤波电路来滤掉毛刺的常规方 法是行不通的。因为这些毛刺的大小是不均匀的,而且也不是按等间隔出现的,线性滤波 反而会使其波形失真更加严重。为了解决上述问题,近年来出现以下几种不同的电路结构。

31 带SHA式DAC 高速采样保持放大器(SHA),例如AD9100和AD9101可以用作DAC输出去毛刺电路,如图4所示 。像先将锁存的数据送入DAC一样,使SHA进入保持方式,以便使DAC开关产生的毛刺与输出隔离。在时钟作用下,由SHA产生的开关尖峰与输入码无关,因此很易滤掉。但必须注意SHA的采样时钟与DAC的更新速率之间的相对时序关系,一定要匹配好。另外SHA的失真指标应该至少优于DAC 6~10dB,否则改善SFDR是不现实的。当时钟频率高达100MSPS时,使用外部SHA的去毛刺电路相当困难。

AD6742是ADI公司采用最新专利技术——介质 隔离超高速互补双极型(XFCB)制造工艺专门为通信应用设计的内部带SHA去毛刺电路,65MSPS低失真12位DAC。这种DAC在20MHz输出情况下,SFDR可达75dB,内部带基准电压,+5V单电源,功耗800mW。

图4 SHA用作DAC去毛刺电路 32 全译码式DAC 普通DAC的电路结构有权电阻网络、R\|2R梯形电阻网络、倒梯形电阻网络和权电流网络。 这些电路结构的共同特点是直接二进制码控制DAC(可称作直接二进制码DAC),每一位有一个电流开关,所以会产生与数码相关的毛刺,这当然不是最佳结构。如果不考虑价格、功耗和杂散电容等实际问题,理想的去毛刺DAC应该是每个等权重码有一个电流开关,不会产生 与数码相关的毛刺,这种DAC称作全译码式(fullydecoded)DAC,例如5位全译码式DAC电路结构

(见图5)有31个电流开关。

图5 5位全译码DAC电路结构 首先将输入二进制码锁存,然后译成31路输出,每路输出再驱动第二级锁存器。第二级锁存器的输出驱动31个等权重的电流开关,然后再对它们的输出求和。在二进制译码逻辑电路之后加第二级锁存器是为了均衡实际电流开关的延迟时间。在设计电流开关时应选用低电平逻 辑开关,以使其对输出的耦合作用最小。因此这种结构几乎能消除所有与数码相关的输出毛刺。在DAC输出端出现的剩余毛刺不论其数码如何变化总是相等的,所以可以滤掉。造成这种全译码DAC失真的主要因素是各个电流源的输出转换速率不相等,开关导通时间与关断时间有限以及积分线性误差等。 33 分段式DAC 全译码式DAC的明显缺点是需要大量的锁存器和电流开关,对于N位DAC,在全译码和锁 存之后需要(2N-1)个等权重电流开关。因此对于高分辨率DAC,显然上述方法是不合适的 。为了充分发挥全译码DAC的去毛刺优势,又节省硬件开销,可以采用分级式(subran ge or multistep)ADC的设计思想。例如10位DAC中的高5位采用全译码式DAC,而低5位则采用直接二进制码DAC(见图6),这种结构的DAC,称作分段式(segmented)DAC。这种DAC可使与数码相关的毛刺明显减少,它是目前高速、低失真、较高分辨率DAC常用的一种方法。

图6 10位分段式DAC结构框图 用等权重电流源驱动R2R梯形电阻网络应该能驱动最低位(LSB),但是用低价格CMOS工艺制做的薄膜电阻一般不能满足这个要求。另外,使用R2R梯形电阻网络会降低DAC的输出阻抗,因此要在固定负载电阻上产生相同的电压,需要较大的驱动电流。用差动PMOS对管组成的基本电流开关电路如图7所示。差动对管用低电平逻辑驱动以使开关瞬变和导通与关断时间差异最小。要求输出DAC的差动电流对称性好,有助于减小偶数次失真分量,尤其是像变压器或运放差动式I/V变换器那种差动输出。