AD精选高速数模转换器中文

AD7520中文资料

数模(D/A)转换器基础知识在电子技术中,模拟量和数字量的相互转换非常重要。

例如,用电子计算机对生产过程进行控制时,必须先将模拟量转换成数字量,才能送到计算机中去进行运算和处理;然后又要将处理得出的数字量转换为模拟量,才能对被控制的模拟量进行控制。

另外,在数字仪表中,也必须将被测的模拟量转换为数字量才能实现数字显示。

能将模拟量转换为数字量的电路称为模数转换器,简称A/D转换器或ADC;能将数字量转换为模拟量的电路称为数模转换器,简称D/A转换器或DAC。

因此,模数转换器和数模转换器是沟通模拟电路和数字电路的桥梁,也可称之为两者之间的接口。

实际上,在数据传输系统、自动测试设备、医疗信息处理、电视信号的数字化、图像信号的处理和识别、数字通信和语音信息处理等方面都离不开模数转换器和数模转换器。

数模转换器是将一组输入的二进制数转换成相应数量的模拟电压或电流输出的电路。

因为数字量是用二进制代码按数位组合起来表示的,对于有权码,每位代码都有一定的权。

所以,为了将数字量转换成模拟量,必须将每一位的代码按其权的大小转换成相应的模拟量,然后将代表各位的模拟量相加,所得的总模拟量就与数字量成正比,这样便实现了从数字量到模拟量的转换。

这就是组成数模转换器的基本指导思想。

数模转换器根据工作原理基本上可以分为二进制权电阻网络数模转换器和T形电阻网络数模转换器(包括倒T形电阻网络数模转换器)两大类。

权电阻网络数模转换器的优点是电路结构简单,可适用于各种有权码。

缺点是电阻阻值范围太宽,品种较多。

要在很宽的阻值范围内保证每个电阻都有很高的精度是极其困难的。

因此,在集成数模转换器中很少采用权电阻网络。

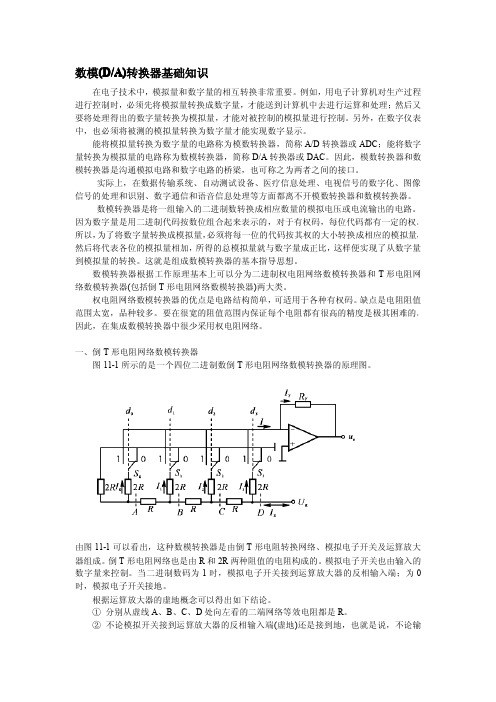

一、倒T形电阻网络数模转换器图11-1所示的是一个四位二进制数倒T形电阻网络数模转换器的原理图。

由图11-1可以看出,这种数模转换器是由倒T形电阻转换网络、模拟电子开关及运算放大器组成。

倒T形电阻网络也是由R和2R两种阻值的电阻构成的。

AD介绍

积分非线性误差(DNL) :指的是实际步宽和 1LSB 理想值之间的差值。如果 DNL 超过 了 1LSB, 转换器可能是非单调的。 这就意味着当输入幅度增加的情况下, 输出幅度反而变小。 也有可能丢失编码, 2n 个二进制编码中的一个或多个将永远不会输出。 微分非线性误差(INL) :实际转换函数和理想直线的偏差。理想直线普遍采用的定义是 增益和偏置误差被消除的前提下,连接函数端点之间的一条直线。偏离量是按照转换函数从 一个步长到下一个步长来度量。 动态误差:表征 ADC 参数表征 ADC 电路在动态环境下的性能,也就是说输入信号是时间的 函数。动态特性比表征 ADC 静态特性复杂得多,其动态特性参数主要包括信噪比(SNR) 、 信噪谐波比(SINAD) 、有效位数(ENOB) 、总谐波失真(THD) 、无杂散动态范围(SFDR) 、 满功率带宽(FPBW) 、孔径误差等。 在实际中,由于静态误差和动态误差的存在,即使 N 位的 ADC 的外围电路引入的误差可 以忽略不计,其有效位数 ENOB 往往是小于 N ,且从芯片制作工艺的角度而言,同样为 N 位 的 ADC,采样率不同,芯片类型(内部实现结构)不同,误差的影响也不同。在表 2 中比较 了 ADI 公司的几款 16 位 ADC 的性能。

ADC 的误差:

静态误差:在转换直流信号时影响转换器精度的误差,可以由偏置误差、增益误差、积分非 线性误差、微分非线性误差描述。 偏置误差:标准偏置点与实际偏置点之间的差值。当数字输出是零时,偏置点是步长的 中间值。这种误差是以同样的值影响所有的编码并通过修正处理过程来补偿,若不能修正, 这种误差是指零尺度误差。 增益误差:在偏置误差被修正为零后,转换函数标准增益点和实际增益点之间的误差。 当数字输出是全标度时增益点是步长中间值。这种误差表示实际转换函数和理想转换函数斜 率的差值以及每一步长中相应的同一百分比误差,可以通过修正的方法调整到零。

AD9248 中文资料

AD9248 概述AD9248是一款双核、3 V、14位、20/40/65 MSPS模数转换器(ADC),集成了两个高性能采样保持放大器和一个基准电压源。

AD9248采用多级差分流水线架构,内置输出纠错逻辑,在最高65 MSPS数据速率时可提供14位精度,并保证在整个工作温度范围内无失码。

AD9248采用先进的CMOS工艺制造,提供节省空间的64引脚LQFP封装,与AD9238引脚兼容,额定温度范围为-40°C至+85°C工业温度范围。

AD9248 特性集成式双核14位模数转换器3 V单电源供电(2.7 V至3.6 V)信噪比(SNR):71.6 dBc(至Nyquist频率,AD9248-65)无杂散动态范围(SFDR):80 dBc(至Nyquist频率,AD9248-65)低功耗:600 mW(65 MSPS)差分输入、500 MHz 3dB带宽出色的抗串扰特性:大于85 dB片内基准电压源和SHA灵活的模拟输入范围:1 Vp-p至2 Vp-p数据格式:偏移二进制或二进制补码时钟占空比稳定器与AD9238引脚兼容AD9248是一种基于流水线型的ADC,这种流水线型结构的特点是由一系列标志1级、2级等各级构成。

每级的结构是相同的,包含一个采样保持电路(S/H) 、一个子模数转换电路(ADC)和一个乘积数模转换器(MDAC)电路[1]。

AD9248的主要引脚的功能包括:VIN+、VIN-是模拟差分信号输入端;D0~D13是数据输出端;OEA、OEB分别是A、B两通道数据输出使能位;PDWN_A、PDWN_B分别是两通道的Power-Down功能选择位,为0 时, 使能通道, 为1时, 关闭通道;DFS是输出数据格式选择位,为0时, 数据输出格式为偏移的二进制,为1时,数据输出格式为二进制补码格式;OTR_A、OTR_B是两通道的溢出标志位;MUX_SELECT是数据复用模式选择位,该管脚接高电平时,则可保证两通道数据分别从各自通道输出,该管脚接时钟时,两通道数据将复用输出数据端口, 此时数据输出速率是采样速率的两倍。

(最新整理)AD转换器的介绍

AD转换器的介绍编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(AD转换器的介绍)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为AD转换器的介绍的全部内容。

在仪器仪表系统中,常常需要将检测到的连续变化的模拟量如:温度、压力、流量、速度、光强等转变成离散的数字量,才能输入到计算机中进行处理.这些模拟量经过传感器转变成电信号(一般为电压信号),经过放大器放大后,就需要经过一定的处理变成数字量。

实现模拟量到数字量转变的设备通常成为模数转换器(ADC),简称A/D.随着集成电路的飞速发展,A/D转换器的新设计思想和制造技术层出不穷。

为满足各种不同的检测及控制需要而设计的结构不同、性能各异的A/D转换器应运而生.下面讲讲A/D转换器的基本原理和分类根据A/D转换器的原理可将A/D转换器分成两大类。

一类是直接型A/D转换器,将输入的电压信号直接转换成数字代码,不经过中间任何变量;另一类是间接型A/D转换器,将输入的电压转变成某种中间变量(时间、频率、脉冲宽度等),然后再将这个中间量变成数字代码输出。

尽管A/D转换器的种类很多,但目前广泛应用的主要有三种类型:逐次逼近式A/D转换器、双积分式A/D 转换器、V/F变换式A/D转换器.另外,近些年有一种新型的Σ—Δ型A/D转换器异军突起,在仪器中得到了广泛的应用。

逐次逼近式A/D转换器的基本原理是:将待转换的模拟输入信号与一个推测信号进行比较,根据二者大小决定增大还是减小输入信号,以便向模拟输入信号逼进。

推测信号由D/A转换器的输出获得,当二者相等时,向D/A转换器输入的数字信号就对应的时模拟输入量的数字量。

模数转换器

A/D转换器模数转换器即A/D转换器,或简称ADC,通常是指一个将模拟信号转变为数字信号的电子元件。

通常的模数转换器是将一个输入电压信号转换为一个输出的数字信号。

由于数字信号本身不具有实际意义,仅仅表示一个相对大小。

故任何一个模数转换器都需要一个参考模拟量作为转换的标准,比较常见的参考标准为最大的可转换信号大小。

而输出的数字量则表示输入信号相对于参考信号的大小。

模数转换器最重要的参数是转换的精度,通常用输出的数字信号的位数的多少表示。

转换器能够准确输出的数字信号的位数越多,表示转换器能够分辨输入信号的能力越强,转换器的性能也就越好。

A/D转换一般要经过采样、保持、量化及编码4个过程。

在实际电路中,有些过程是合并进行的,如采样和保持,量化和编码在转换过程中是同时实现的。

一般来说,AD比DA贵,尤其是高速的AD,因为在某些特殊场合,如导弹的摄像头部分要求有高速的转换能力。

一般那样AD要上千美元。

还有通过AD的并联可以提高AD的转换效率,多个AD同时处理数据,能满足处理器的数字信号需求了。

模数转换过程包括量化和编码。

量化是将模拟信号量程分成许多离散量级,并确定输入信号所属的量级。

编码是对每一量级分配唯一的数字码,并确定与输入信号相对应的代码。

最普通的码制是二进制,它有2n个量级(n为位数),可依次逐个编号。

模数转换的方法很多,从转换原理来分可分为直接法和间接法两大类。

直接法是直接将电压转换成数字量。

它用数模网络输出的一套基准电压,从高位起逐位与被测电压反复比较,直到二者达到或接近平衡(见图)。

控制逻辑能实现对分搜索的控制,其比较方法如同天平称重。

先使二进位制数的最高位Dn-1=1,经数模转换后得到一个整个量程一半的模拟电压VS,与输入电压Vin 相比较,若V in>VS,则保留这一位;若V in<V in,则Dn-1=0。

然后使下一位Dn-2=1,与上一次的结果一起经数模转换后与V in相比较,重复这一过程,直到使D0=1,再与V in相比较,由V in>VS还是V in<V来决定是否保留这一位。

几款高速数模转换芯片的中文资料

AD9221、AD9223和AD9220均为新一代高性能、12位模数转换器,采用单电源供电。

每款器件都具有真12位线性度和温度漂移性能1,以及11.5位或更佳的交流性能2。

AD9221/AD9223/AD9220均采用相同的接口选项、封装和引脚排列。

因此,该产品系列可根据性能、采样速率和功耗,向上或向下选择器件型号。

这些器件的额定采样速率和功耗各不相同,体现在各自基于频率的动态性能上。

AD9221/AD9223/AD9220采用高速、低成本的单CMOS工艺及新颖的架构,分辨率和速度均达到现有混合单芯片方案的水平,而功耗与成本却低得多。

每款器件均为完整的单芯片ADC,内置片内高性能、低噪声采样保持放大器和可编程基准电压源。

也可以选用外部基准电压,以满足应用的直流精度与温度漂移要求。

这些器件采用多级差分流水线架构,内置数字输出纠错逻辑,在额定数据速率时可提供12位精度,并保证在整个工作温度范围内无失码。

AD9221/AD9223/AD9220的输入非常灵活,能够与成像、通信、医疗和数据采集系统实现轻松接口。

真差分输入结构使单端输入和差分输入采样接口均支持各种输入范围。

采样保持(SHA)放大器既适用于在连续通道中切换满量程电平的多路复用系统,也适合采用最高Nyquist速率及更高的频率对单通道输入进行采样。

此外,AD9221/AD9223/AD9220特别适合采用IF下变频的通信系统,因为在差分输入模式下,SHA可以实现远超过其额定Nyquist频率2的出色动态性能。

采用一个单时钟输入来控制所有内部转换。

数字输出数据格式为标准二进制。

超量程(OTR)信号表示溢出状况,可由最高有效位来确定是下溢还是上溢。

特点和优势∙单芯片12位模数转换器产品系列∙该系列包括:AD9221、AD9223和AD9220∙灵活的采样速率:1.5 MSPS、3.0 MSPS和10 MSPS∙低功耗:59 mW、100 mW和250 mW∙+5 V单电源∙积分非线性误差:0.5 LSB∙微分非线性误差:0.3 LSB∙信噪比(SNR):70 dB;无杂散动态范围(SFDR):86 dB∙超量程指示∙28引脚SOIC和28引脚SSOP封装∙Resolution (Bits): 12bit∙# Chan: 1∙Sample Rate: 10MSPS∙Interface: Par∙Analog Input Type: Diff-Uni,SE-Uni∙Ain Range: 2 V p-p,5V p-p∙ADC Architecture: Pipelined∙Pkg Type: SOIC,SOPAD9225是一款单芯片、12位、25 MSPS模数转换器(ADC),采用单电源供电,内置一个片内高性能采样保持放大器和基准电压源。

LED显示AD转换器中英文对照外文翻译文献

中英文资料外文翻译213Digit, LCD/LED Display, A/D Converters Abstract: The Intersil ICL7106 and ICL7107 are high performance, low power,213digit A/D converters. Included are seven segment decoders, display drivers, a reference, and a clock. The ICL7106 is designed to interface with a liquid crystal display (LCD) and includes a multiplexed backplane drive; the ICL7107 will directly drive an instrument size light emitting diode (LED) display.The ICL7106 and ICL7107 bring together a combination of high accuracy, versatility, and true economy. It features autozero to less than 10μV, zero drift of less than 1μV/℃, input bias current of 10pA (Max), and rollover error of less than one count. True differential inputs and reference are useful in all systems, but give the designer an uncommon advantage when measuring load cells, strain gauges and other bridge type transducers. Finally, the true economy of single power supply operation (ICL7106), enables a high performance panel meter to be built with the addition of only 10 passive components and a display.Keyword : 213Digit LCD/LED Display A/D Converters1 Features (1)Guaranteed Zero Reading for 0V Input on All Scales(2)1pA Typical Input Current(3)True Differential Input and Reference, Direct Display Drive -LCD ICL7106, LED LCL7107(4)Low Noise - Less Than 15μVP-P(5)On Chip Clock and Reference(6)Low Power Dissipation - Typically Less Than 10mW(7)No Additional Active Circuits Required2 Detailed Description2.1 Analog SectionFigure 1 shows the Analog Section for the ICL7106 and ICL7107. Each measurement cycle is divided into three phases. They are (1) auto-zero (A-Z), (2) signal integrate (INT) and (3) de-integrate (DE).FIGURE 1 ANALOG SECTION OF ICL7106 AND ICL71072.2 Auto-Zero PhaseDuring auto-zero three things happen. First, input high and low are disconnected from the pins and internally shorted to analog COMMON. Second, the reference capacitor is charged to the reference voltage. Third, a feedback loop is closed around the system to charge the auto-zero capacitor CAZ to compensate for offset voltages in the buffer amplifier, integrator, and comparator. Since the comparator is included in the loop, the AZ accuracy is limited only by the noise of the system. In any case, the offset referred to the input is less than 10μV.2.3 Signal Integrate PhaseDuring signal integrate, the auto-zero loop is opened, the internal short is removed, and theinternal input high and low are connected to the external pins. The converter then integrates the differential voltage between IN HI and IN LO for a fixed time. This differential voltage can be within a wide common mode range: up to 1V from either supply. If, on the other hand, the input signal has no return with respect to the converter power supply, IN LO can be tied to analog COMMON to establish the correct common mode voltage. At the end of this phase, the polarity of the integrated signal is determined.2.4 De-Integrate PhaseThe final phase is de-integrate, or reference integrate. Input low is internally connected to analog COMMON and input high is connected across the previously charged reference capacitor. Circuitry within the chip ensures that the capacitor will be connected with the correct polarity to cause the integrator output to return to zero. The time required for the output to return to zero is proportional to the input signal. Specifically the digital reading displayed is: DISPLAY COUNT=⎪⎪⎭⎫ ⎝⎛REFIN V V 1000 2.5 Differential Input The input can accept differential voltages anywhere within the common mode range of the input amplifier, or specifically from 0.5V below the positive supply to 1V above the negative supply. In this range, the system has a CMRR of 86dB typical. However, care must be exercised to assure the integrator output does not saturate. A worst case condition would be a large positive common mode voltage with a near full scale negative differential input voltage. The negative input signal drives the integrator positive when most of its swing has been used up by the positive common mode voltage. For these critical applications the integrator output swing can be reduced to less than the recommended 2V full scale swing with little loss of accuracy. The integrator output can swing to within 0.3V of either supply without loss of linearity.2.6 Differential ReferenceThe reference voltage can be generated anywhere within the power supply voltage of the converter. The main source of common mode error is a roll-over voltage caused by thereference capacitor losing or gaining charge to stray capacity on its nodes. If there is a large common mode voltage, the reference capacitor can gain charge (increase voltage) when called up to de-integrate a positive signal but lose charge (decrease voltage) when called up to de-integrate a negative input signal. This difference in reference for positive or negative input voltage will give a roll-over error. However, by selecting the reference capacitor such that it is large enough in comparison to the stray capacitance, this error can be held to less than 0.5 count worst case.2.7 Analog COMMONThis pin is included primarily to set the common mode voltage for battery operation (ICL7106) or for any system where the input signals are floating with respect to the power supply. The COMMON pin sets a voltage that is approximately 2.8V more negative than the positive supply. This is selected to give a minimum end-of-life battery voltage of about 6V. However, analog COMMON has some of the attributes of a reference voltage. When the total supply voltage is large enough to cause the zener to regulate (>7V), the COMMON voltage will have a low voltage coefficient (0.001%/V), low output impedance (≅15Ω), and a temperature coefficient typically less than 80ppm/×℃.The limitations of the on chip reference should also be recognized, however. With the ICL7107, the internal heating which results from the LED drivers can cause some degradation in performance. Due to their higher thermal resistance, plastic parts are poorer in this respect than ceramic. The combination of reference Temperature Coefficient (TC), internal chip dissipation, and package thermal resistance can increase noise near full scale from 25μV to 80μVP-P. Also the linearity in going from a high dissipation count such as 1000 (20 segments on) to a low dissipation count such as 1111(8 segments on) can suffer by a count or more. Devices with a positive TC reference may require several counts to pull out of an over-range condition. This is because over-range is a low dissipation mode, with the three least significant digits blanked. Similarly, units with a negative TC may cycle between over-range and a non-overrange count as the die alternately heats and cools. All these problems are of course eliminated if an external reference is used.The ICL7106, with its negligible dissipation, suffers from none of these problems. Ineither case, an external reference can easily be added, as shown in Figure 2.Analog COMMON is also used as the input low return during auto-zero and de-integrate. If IN LO is different from analog COMMON, a common mode voltage exists in the system and is taken care of by the excellent CMRR of the converter. However, in some applications IN LO will be set at a fixed known voltage (power supply common for instance). In this application, analog COMMON should be tied to the same point, thus removing the common mode voltage from the converter. The same holds true for the reference voltage. If reference can be conveniently tied to analog COMMON, it should be since this removes the common mode voltage from the reference system.Within the lC, analog COMMON is tied to an N-Channel FET that can sink approximately 30mA of current to hold the voltage 2.8V below the positive supply (when a load is trying to pull the common line positive). However, there is only 10μA of source current, so COMMON may easily be tied to a more negative voltage thus overriding the internal reference.FIGURE 2 USING AN EXTERNAL REFERENCE2.8 TESTThe TEST pin serves two functions. On the ICL7106 it is coupled to the internally generated digital supply through a 500Ω resistor. Thus it can be used as the negative supply for externally generated segment drivers such as decimal points or any other presentation the user may want to include on the LCD display. Figures 3 and 4 show such an application. Nomore than a 1mA load should be applied.The second function is a “lamp test”. When TEST is pulled high (to V+) all segments will be turned on and the display should read “1888”. The TEST pin will sink about 15mA under these conditions.FIGURE 3 SIMPLE INVERTER FOR FIXED DECIMAL POINTFIGURE 4 EXCLUSIVE …OR‟ GATE FOR DECIMAL POINT DRIVE2.9 Digital SectionFigures 5 and 6 show the digital section for the ICL7106 and ICL7107, respectively. In the ICL7106, an internal digital ground is generated from a 6V Zener diode and a large P-Channel source follower. This supply is made stiff to absorb the relative large capacitive currents when the back plane (BP) voltage is switched. The BP frequency is the clock frequency divided by 800. For three readings/sec., this is a 60Hz square wave with a nominal amplitude of 5V. The segments are driven at the same frequency and amplitude and are in phase with BP when OFF, but out of phase when ON. In all cases negligible DC voltage exists across the segments.Figure 6 is the Digital Section of the ICL7107. It is identical to the ICL7106 except thatthe regulated supply and back plane drive have been eliminated and the segment drive has been increased from 2mA to 8mA, typical for instrument size common anode LED displays. Since the 1000 output (pin 19) must sink current from two LED segments, it has twice the drive capability or 16mA.In both devices, the polarity indication is “on” for negative analog inputs. If IN LO and IN HI are reversed, this indication can be reversed also, if desired.FIGURE 5 ICL7106 DIGITAL SECTIONFIGURE 6 ICL7107 DIGITAL SECTION2.10 System TimingFigure 7 shows the clocking arrangement used in the ICL7106 and ICL7107. Two basic clocking arrangements can be used:1. Figure 7A. An external oscillator connected to pin 40.2. Figure 7B. An R-C oscillator using all three pins.The oscillator frequency is divided by four before it clocks the decade counters. It is then further divided to form the three convert-cycle phases. These are signal integrate (1000 counts), reference de-integrate (0 to 2000 counts) and auto-zero (1000 to 3000 counts). For signals less than full scale, auto-zero gets the unused portion of reference de-integrate. This makes a complete measure cycle of 4,000 counts (16,000 clock pulses) independent of input voltage. For three readings/second, an oscillator frequency of 48kHz would be used.To achieve maximum rejection of 60Hz pickup, the signal integrate cycle should be a multiple of 60Hz. Oscillator frequencies of 240kHz, 120kHz, 80kHz, 60kHz, 48kHz, 40kHz, 3331kHz, etc. should be selected. For 50Hz rejection, Oscillator frequencies of 200kHz,100kHz, 6632kHz, 50kHz, 40kHz, etc. would be suitable. Note that 40kHz (2.5 readings/second) will reject both 50Hz and 60Hz (also 400Hz and 440Hz).FIGURE 7 CLOCK CIRCUITS三位半LCD/LED 显示A/D 转换器摘要:ICL7106和ICL7107是高性能、低功耗的三位半A/D 转换电路。

AD转换器介绍

AD转换器介绍D/A 转换器是将输⼊的⼆进制数字量转换成模拟量,以电压或电流的形式输出。

D/A 转换器实质上是⼀个译码器(解码器)。

⼀般常⽤的线性D/A 转换器,其输出模拟电压uO 和输⼊数字量Dn 之间成正⽐关系。

UREF为参考电压。

uO =DnUREF将输⼊的每⼀位⼆进制代码按其权值⼤⼩转换成相应的模拟量,然后将代表各位的模拟量相加,则所得的总模拟量就与数字量成正⽐,这样便实现了从数字量到模拟量的转换。

D/A 转换器⼀般由数码缓冲寄存器、模拟电⼦开关、参考电压、解码⽹络和求和电路等组成。

数字量以串⾏或并⾏⽅式输⼊,并存储在数码缓冲寄存器中;寄存器输出的每位数码驱动对应数位上的电⼦开关,将在解码⽹络中获得的相应数位权值送⼊求和电路;求和电路将各位权值相加,便得到与数字量对应的模拟量。

开关Si 的位置受数据锁存器输出的数码di 控制:当di=1时,Si 将对应的权电阻接到参考电压UREF 上;当di=0时,Si 将对应的权电阻接地。

权电阻⽹络D/A 转换器的特点①优点:结构简单,电阻元件数较少;②缺点:阻值相差较⼤,制造⼯艺复杂。

2. 倒T 型电阻⽹络D/A 转换器3. 电阻解码⽹络中,电阻只有R 和2R 两种,并构成倒T 型电阻⽹络。

当di=1时,相应的开关Si 接到求和点;当di=0时,相应的开关Si 接地。

但由于虚短,求和点和地相连,所以不论开关如何转向,电阻2R 总是与地相连。

这样,倒T 型⽹络的各节点向上看和向右看的等效电阻都是2R ,整个⽹络的等效输⼊电阻为R 。

倒T 型电阻⽹络D/A 转换器的特点:①优点:电阻种类少,只有R 和2R ,提⾼了制造精度;⽽且⽀路电流流⼊求和点不存在时间差,提⾼了转换速度。

②应⽤:它是⽬前集成D/A 转换器中转换速度较⾼且使⽤较多的⼀种,如8位D/A 转换器DAC0832,就是采⽤倒T 型电阻⽹络。

三、D/A 转换器的主要技术指标1. 分辨率分辨率⽤于表征D/A 转换器对输⼊微⼩量变化的敏感程度。

AD数模转换器

目录一.设计的目的和意义----------------------------------2 二.设计的内容与要求----------------------------------2 三.系统的硬件要求-------------------------------------2 (1)所用芯片的功能介绍------------------------3(2)设计原理与硬件电路------------------------3 四.系统的软件设计-------------------------------------5 (1)软件控制流程---------------------------------5(2)程序清单---------------------------------------5 五.系统调试与运行-------------------------------------10 六.设计收获----------------------------------------------11 七.主要参考文献----------------------------------------11一.设计的目的与意义1.加深理解逐次逼近法模数转换器的特征和工作原理。

2.掌握ADC0809的接口方法以及A/D输入程序的设计和调试方法。

3.熟悉DAC0832数模转换器的特性和接口方法。

4.掌握D/A输出程序的设计和调试方法。

5.熟悉LED显示器的星系显示方法。

6.利用对以上知识点的掌握设计出一个自动温控系统。

二.设计的内容与要求利用芯片0832、芯片0809、单片机、温敏电阻或温度传感器、调温器和导线等构建一个完整的全自动的温控系统。

用程序控制0809芯片实现A/D 转换,控制0832芯片实现D/A转换,用程序控制单片机实现温控信号的分析命令的下达,线路实现模拟信号的传输。

三、系统的硬件要求(1)所用芯片的功能介绍ADC0809:ADC0809是采样分辨率为8位的、以逐次逼近原理进行模—数转换的器件。

ad9163 指标

ad9163 指标

AD9163是ADI(Analog Devices)推出的一款高性能、低功耗

的数模转换器(DAC),主要应用于通信、无线基础设施、雷达、测

试仪器等领域。

该器件具有多种指标,包括分辨率、采样率、功耗、动态范围、接口类型等。

首先,AD9163的分辨率为16位,这意味着它可以提供高精度

的数字到模拟转换。

其采样率高达12 GSPS(Giga Samples Per Second),使其能够处理高速数据并实现高频率信号的精确重建。

此外,AD9163具有较低的功耗,这对于需要长时间运行或者对功耗

有严格要求的应用非常重要。

在动态范围方面,AD9163能够提供较高的性能,确保在处理各

种信号时能够保持精确度和稳定性。

另外,它还支持多种接口类型,包括JESD204B接口,这使得它能够与各种数字信号处理器(DSP)

和微处理器进行高速数据传输。

总的来说,AD9163作为一款高性能、低功耗的数模转换器,在

多个指标上都表现出色,使其在通信、雷达等领域具有广泛的应用

前景。

希望这些信息能够对你有所帮助。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AD76816-Bit高速数模转换器特性刷新率:30MSPS分辨率:16-Bit线性度:1/2LSBDNL@14Bits1LSBINL@14Bits最快建立时间:满量程25ns,精度0.025%SFDR@1MHz 输出:86dBcTHD@1MHz 输出:71dBc低干扰脉冲:35pV-s功率消耗:465mW片上基准源:2.5V边沿触发锁存器乘法参考能力应用任意波形发生器通信波形重建矢量图形显示产品描述AD768是16-Bit高速数模转换器(DAC )提供优良的交流和直流性能。

AD768是ADI公司的先进双极CMOS制造(abcmos )处理,结合双极晶体管的速度,激光微调薄膜电阻的精度和有效CMOS逻辑。

一个分段电流源架构与专有开关技术相结合,以减少毛刺能量来获得最大化的动态精度。

边沿触发输入锁存器和一个温度补偿的带隙基准源已集成,提供一个完整的单片DAC解决方案。

AD768是电流输出DAC标称满量程输出电流20mA和一个1K :的输出阻抗。

差分电流输出提供支持单端或差分应用。

电流输出可以绑接输出电阻提供电压输出,或连接到高速放大器的求和点提供一个缓冲电压输出。

同时,差分输出可以连接到变压器或差分放大器。

片上基准源和控制放大器配置为最大的准确性和灵活性。

AD768可以通过芯片上的基准源或由一个外部基准电压基于一个外部电阻的选择驱动。

外部电容器允许用户优化变换参考带宽和噪声性能。

AD768采用土5V电源运行,典型的消耗功率465毫瓦。

该芯片采用28引脚SOIC封装,规定工作在工业温度范围。

产品亮点1、低干扰和快速建立时间提供杰出的波形重建或数字动态性能合成的要求,包括通信。

2、A D768优良的直流精度使得它适合高速A/D转换应用。

3、温度补偿,包括片上2.5V带隙基准。

4、允许的参考同一个外部电阻器使用电流输入。

外部基准也可以使用。

5、A D768电流输出可单独使用或差分,无论是负载电阻,外部运算放大器求和点或变压器。

6、适当选择一个外部电阻和补偿电容允许用户优化AD768的参考标准和目标带宽应用。

AD768 技术参数仃MINt°TMAX,VDD=+5.°V,VEE=-5.°V,LADC°M,REFC°M,DC°M=°V,IREFIN=5mA,CLOCK=10M Hz, unlessotherwisenoted)说明:1、I OUTA测量,为虚拟接地。

2、标称FS输出电流是4倍的IREFIN电流,当IREFIN=5mA时,FS电流是20mA3、输出电流定义为用于IREFIN和任何外部负载的总电流。

4、参考带宽是一个外部限制NR/引脚的函数。

参考补偿章节的详细数据表。

5、排除内部基准源漂移。

6、包含内部基准源漂移。

7、测量无缓冲的输出电压范围(1V)和FSIOUTB50:负载电流。

规格变更,恕不另行通知。

绝对最大额定参数**强调高于列出“绝对最大额定值”之上可能会造成永久性损坏器件。

这是一个强调评级只有和功能操作的器件在这些或任何其他条件高于表示在操作该规范的部分不是暗示。

长时间暴露在绝对最大额定值可能影响器件可靠性。

订购指南晶片测试范围1(T A=+258C,V DD=+5.0V,V EE=-5.0V,l REFIN =5mA,除非另有说明)说明:1、电气测试执行限制显示晶片探针。

由于不同的装配方法和正常的成品率损失, 成品率为标准产品包装后不能保证切为骰子。

2、限制推测的单个比特错误的测试。

3、固死锁存器控制。

当锁存器控制和时钟衬垫高时边缘触发锁存成为电平触发。

4、固死衬底连接到VEE。

芯片管脚描述技术参数定义线性误差(也称积分非线性或lNL) 线性误差被定义为实际的最大偏差, 是模拟输出和理想输出的比值, 决定从零到满刻度的直线绘制。

微分非线性(DNL)DNL是衡量变化的模拟值,归一化满刻度,与1LSB数字输入代码的变化。

单调性当数字输入增加如果输出增加或保持不变D/A 转换器是单调。

偏置误差理想的输出电流的偏差为零称为偏移误差。

预计当IOUTA,OmA俞出的输入都是0。

预计IOUTB,OmA俞出当所有的输入都设置为1。

增益误差实际和理想输出跨度之间的区别。

实际的跨度是由所有输入输出设置1s- 输出时所有输入都设置为0。

理想的输出电流跨度是应用于IREFIN 管脚电流的4倍。

合规输出范围电压在允许范围内的输出电流输出DAC。

操作超出了最大合规限制导致输出级饱和度或故障, 导致非线性性能。

温度漂移温度漂移是指在环境(+25 ° C)下的最小温度或最高温度的最大的变化。

为了抵消和增益漂移, 漂移指定为满刻度范围(FSR)每度ppm/度.基准源漂移,漂移是在ppm/度o电源抑制当满刻度输出时, 供电电源在标称电压下最小值和最大值的最大的变化.建立时间输出所需的时间达到并保持在一个对其最终值指定的误差范围, 测量的开始输出的转换。

无失真动态范围输入信号有效值幅值和杂散信号峰值超过指定的带宽的区别,用dB表示。

总谐波失真THD是测量输入信号六次谐波的有效值总和和基波的比值。

它用百分比或分贝(dB)表示。

干扰脉冲在DAC上有不对称开关时间产生干扰输出量化的瞬态故障脉冲。

这是指定的净区域上产生小毛刺。

数字接口提供了 CM0兼容的边沿触发输 C 标称满刻度电C 转换功锁存,该接口容易连接CM0逻辑和支 持片钟频率高基准源与外部芯片上集成器 '对的最小的存脉性和增加功能和保存放 极器可以是不同的时调周宽,降低满宽 极定过最低节点到虽然源管这些过渡连接外 缘可能会影响数字直器能限字带宽和值 设置为CMpS 兼容逻辑大约为正电源电功能描述AD768是电流输出型DA ADmA 和可用于电流输。

差分俞出提供支持流 增 能曲线比和U 但这种效应:IOUTB (27〈LADCOM (28 就动 不需要稳定和不会影响 R L VA 49,9ii------- 满刻度 VB yLoMIOUTA ( 1器典型输 有况下3 另有说 标称值最刻 彳的电 电公差 R L49.90AD768%的求允许简单这个线F性的增益误差变化结能以很容易地通过调整I 效价数字输补偿路。

在这个配置要的是要注意合规的俞这是一个不制变输入大的负电压合规是线性禁:使以它看起的负载产生V-2V 分非非线性幅!:式操作额外的考输出这点一个积210如V无缓冲电压输出分非线性模式操作。

当电压输出节点变化时有限的输出阻抗使AC电流转向开关产生小的变化输出电流随输出电压同,产产生变化生一个弓形的L大于8LSB)。

要达到最优L性能建议使用缓冲电压输出模式。

INL 也有点依赖未使用的(IOUTB)输出端,在模拟输出章节中有所描述。

为了消除这 种影响,IOUTB 端应该和IOUTA —样的阻抗,因此这两个输出对地是同样的电阻分压器。

这 将保持电流在LADCOM 的常数,最小化任何相关代码相关的IR 滴落在DAC 的阶梯内可能 产生额外的非线性。

AC-耦合输出如图22所示AD768配置的输出提供了一个 双相输出信号而无需使用求和放大器。

交流 负载阻抗和AD768输出阻抗并联组成DAC 输出,即RL 和偏压电阻RB并联。

额定输出 振幅图22中给出的值是±0.5V ,假设条件 RB>>RL 。

电路的增益是阻抗 RLAD 、RB 和 RL 给定的公差函数。

选择RB 和C 值的大小 主要取决于需要3dB 高通截止频率和偏置电 流,连接RB 的后级电流IB 。

3dB 频率特性的 近似方程为,f -3dB =1/[2 x ? x (R B +R L 〃R LAD ) x C]. ?输出的直流偏移量是后级偏置电流和 RB 电阻值de一个函数。

例如,如果 C=390pF,RB=20K :,和IB=1.0 :A,-3dB 的频率大约是20.4kHz 和直流偏移量将 20mV 。

缓冲电压输出配置单极配置 对于正输出电压,或电压范围大于允许输出合 规参数,一些类型要采用外部缓冲。

在基于考 虑诸如速度、精度和成本的情况下可以选择 各种各样的放大器。

当动态性能很重要时, AD9631是一个很好的选择,可提供低失真的 10MHz 频宽。

图23显示了 0V 到+2V 的满刻 度单极缓冲电压输出。

图23显示了 0V 到+2V 的满刻度单极缓冲电压输出。

缓冲输出电压的 结果是从DAC 输出电流流经放大器的反馈电阻,R FB 。

在这种情况下,20mA 满刻度的电流 在RFB(100;)产生一个输出电压 0V 到+2V 的 范围。

为了实现最佳的直流线性度可采用相 同的配置和建议使用精密放大器 AD845。

使用分流器缓冲输出图23中所示的配置是放大器不可能在这种情况下提供需要的 替代方法,图24显示了放大器A1结合电阻分流。

选择R FF 和RL 的值是为了限制电流,电流 I3,必须由A1提供。

电流I 2应通过电阻器RL 接地分流。

R FF 和RL 并联电阻值不应超过60 ■ 避免超过指定的合规电压。

图 24中给出的AD768值等于4mA,结果是单极性输出摆幅0V 到AD768 R L 49.9Q 图22 ± 0.5V 无缓冲AC 耦合输出图23单极性0V 到2V 的缓冲电压输出 20mA 反馈电流。

作为一种IOUTAIOUTB (27 图24c 使用分流器单极性 0V 到2VIOUTAIOUTB 27LADCOM 49.9U 28 1kn~:----- 7工 LI BIPOLAR * 7 75(1 I DAC 1 ---- V~~VA ----------Rf B Iku2V 。

注意,因为A1获得大约-4的反相增益和+5噪声增益,所以应考虑A1的失真和噪声性双极性配置双极性模式是通过提供一个补偿电流「BIPOLAR ,加至I/V 放大器(A1)求和节点来完成。

通过设 置I BIPOLAR 准确的满刻度电流的一半通过 R FB ,结果得到相对典型地对称求和节点电压输出。

图25显示了实现双极土 2的电压输出。

电阻分压器设置为I DAC 满刻度电流是5mA 。

内部2.5V?基准产生在I BIPOLAR 的2.5mA 电流流过 RBIP 。

当DAC 设置半刻度(1000),1 DAC 输出 图25双极性土 2.5V 缓冲电压输出 2.5mA 电流,正好是I BIPOLAR所抵消,A1输出为0V.由于DAC 输出从零到满刻度变化,所以 A1可获得从-2.5V 到+2.5V 的输出电压。

注意,对于这种配置从R EFOUT 输出总电流为15mA, 所以外部缓冲是必需的。

虽然运算放大器AD811、AD8001和AD9631等的选择具有优良 的动态性能。