解读高速数模转换器(DAC)的建立和保持时间

高速数模转换器AD9779/AD9788的应用

高速数模转换器AD9779/AD9788的应用卫晓娟;李军红【摘要】This article briefly introduces the features and application of two types of high-speed DACs: AD9779 and AD9788. It includes the design idea of software driver and the configuration for the internal registers. The main content is very practical because of coming from practice.%介绍了高速数模转换器AD9779和AD9788的使用方法,重点介绍了其驱动软件设计方法和内部寄存器的配置方式等。

文中内容都是实践经验,具有很强的实用性和参考价值。

【期刊名称】《微型机与应用》【年(卷),期】2011(030)024【总页数】2页(P79-80)【关键词】AD9779;AD9788;数模转换器;串行外设接口;锁相环【作者】卫晓娟;李军红【作者单位】凯迈(洛阳)电子有限公司,河南洛阳471000;凯迈(洛阳)电子有限公司,河南洛阳471000【正文语种】中文【中图分类】TP21AD9779是ADI公司的一款产品,是双通道、宽动态范围数模转换器(DAC),提供 1 GS/s采样速率,允许高至奈奎斯特频率的多载波生成[1]。

AD9788提供800 MS/s的采样速率,其性能和应用方式与AD9779非常相似[2]。

AD9779和AD9788虽然不是一个系列,但芯片管脚是兼容的,在硬件电路的设计上并没有区别,两者均使用标准的SPI接口来驱动,因此软件实现上也可以采用统一的驱动方式。

但在寄存器的配置上,两者存在差异,这在后面会具体介绍。

为了描述方便,如不特殊说明,下文中使用AD97××来统一表示 AD9779和 AD9788。

解读高速数模转换器(DAC)的建立和保持时间

解读高速数/模转换器(DAC)的建立和保持时间Oct 10, 2007摘要:本应用笔记定义了高速数/模转换器(DAC)的建立和保持时间,并给出了相应的图例。

高速DAC的这两个参数通常定义为“正、负”值,了解它们与数据瞬态特性之间的关系是一个难点,为了解决这些难题,本文提供了一些图例。

介绍为了达到高速数/模转换器(DAC)的最佳性能,需要严格满足数字信号的时序要求。

随着时钟频率的提高,数字接口的建立和保持时间成为系统设计人员需要重点关注的参数。

本应用笔记对建立和保持时间进行详尽说明,因为这些参数与Maxim的高性能数据转换方案密切相关。

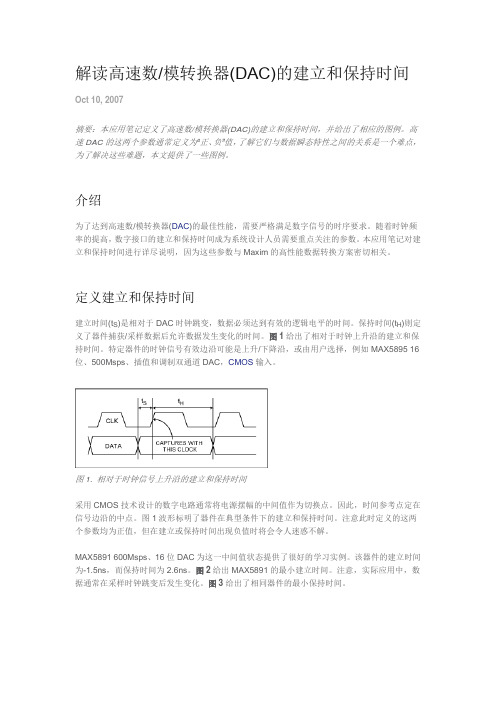

定义建立和保持时间建立时间(t S)是相对于DAC时钟跳变,数据必须达到有效的逻辑电平的时间。

保持时间(t H)则定义了器件捕获/采样数据后允许数据发生变化的时间。

图1给出了相对于时钟上升沿的建立和保持时间。

特定器件的时钟信号有效边沿可能是上升/下降沿,或由用户选择,例如MAX5895 16位、500Msps、插值和调制双通道DAC,CMOS输入。

图1. 相对于时钟信号上升沿的建立和保持时间采用CMOS技术设计的数字电路通常将电源摆幅的中间值作为切换点。

因此,时间参考点定在信号边沿的中点。

图1波形标明了器件在典型条件下的建立和保持时间。

注意此时定义的这两个参数均为正值,但在建立或保持时间出现负值时将会令人迷惑不解。

MAX5891 600Msps、16位DAC为这一中间值状态提供了很好的学习实例。

该器件的建立时间为-1.5ns,而保持时间为2.6ns。

图2给出MAX5891的最小建立时间。

注意,实际应用中,数据通常在采样时钟跳变后发生变化。

图3给出了相同器件的最小保持时间。

图2. MAX5891的最小建立时间图3. MAX5891的最小保持时间为满足这些是需要求,用户需要分析数据源的传输延迟和抖动。

传输延迟决定了时钟的标称定时要求,而抖动指标则决定了所允许的容限。

为了解释这一关系,我们以具有1.5ns传输延迟的逻辑门电路为例。

dac转换原理

dac转换原理DAC转换原理DAC转换器(Digital-to-Analog Converter)是一种将数字信号转换为模拟信号的电子器件。

它将数字信号以一定的精度和速度转换为模拟电压或电流输出,被广泛应用于各种电子设备中,如音频设备、通信设备、仪器仪表等。

DAC转换原理基于数模转换(Digital-to-Analog Conversion)技术,通过将离散的数字信号转换为连续的模拟信号实现。

数模转换的过程可以分为两个主要步骤:采样和保持(Sampling and Holding)以及量化和编码(Quantization and Encoding)。

在采样和保持阶段,DAC转换器接收到输入的数字信号,并将其转换为模拟信号。

这个过程涉及到采样器和保持器的工作,采样器负责按照一定的频率对输入信号进行采样,而保持器则用于在采样的瞬间将采样到的信号保持住,以便后续的处理。

在量化和编码阶段,DAC转换器将经过采样和保持的信号进行量化和编码,将离散的数字信号转换为模拟信号。

量化是将连续的信号离散化,将其划分为一系列离散的电平,用来表示输入信号的幅度。

编码则是将离散的电平映射为模拟信号的幅度,通常采用二进制编码方式。

在DAC转换原理中,一个重要的参数是分辨率(Resolution),它表示DAC转换器能够分辨的电平数量。

分辨率越高,表示DAC转换器能够输出更精确的模拟信号,但同时也需要更复杂的电路设计和更高的成本。

另一个重要的参数是采样率(Sampling Rate),它表示DAC转换器每秒对输入信号进行采样的次数。

采样率越高,表示DAC转换器能够更快地将数字信号转换为模拟信号,从而提高信号的还原度和准确性。

DAC转换器的实现方式有很多种,常见的包括串行式DAC、并行式DAC和Σ-Δ调制式DAC等。

串行式DAC通过串行输入方式将数字信号转换为模拟信号,适用于低速和低分辨率的应用。

并行式DAC通过并行输入方式将数字信号转换为模拟信号,适用于高速和高分辨率的应用。

数模转换器的建立时间测试方法及系统与设计方案

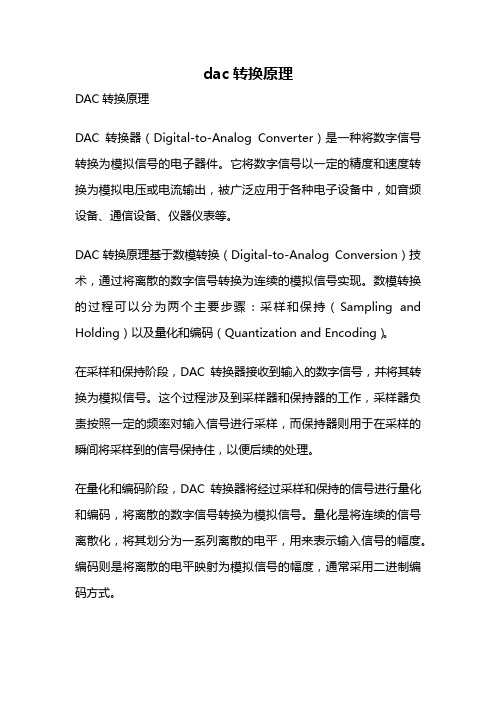

图片简介:本技术揭示了一种数模转换器的建立时间测试方法,包括对一数模转换器的电信号进行采样;根据采样数据,得到一个采样周期中的高电平平均值;得到一电压震荡结束后的高电平稳定区间;在所述采样数据中找到所述高电平稳定区间的起始采样点,记为建立时间结束点;在所述采样数据中查找最长的电压值连续上升区间,记为最大上升区间;在所述采样数据中找到所述最大上升区间结束后第一个电压值为高电平平均值的采样点,记为建立时间起始点;根据所述建立时间起始点和建立时间结束点,得到所述建立时间。

本技术还提供一种使用上述方法的数模转换器的建立时间测试系统,可以自动测试建立时间。

技术要求1.一种数模转换器的建立时间测试方法,其特征在于,包括:一示波器对一数模转换器的电信号进行采样;根据所述示波器的采样数据,得到一个采样周期中的高电平平均值;根据建立时间的精度要求以及所述高电平平均值,得到一电压震荡结束后的高电平稳定区间;在所述采样数据中找到所述高电平稳定区间的起始采样点,记为建立时间结束点;在所述采样数据中查找最长的电压值连续上升区间,记为最大上升区间;在所述采样数据中找到所述最大上升区间结束后第一个电压值为高电平平均值的采样点,记为建立时间起始点;根据所述建立时间起始点和建立时间结束点,得到所述建立时间。

2.如权利要求1所述的数模转换器的建立时间测试方法,其特征在于,得到一个采样周期中的高电平平均值的步骤包括:对所述采样数据进行直方图统计,在所述直方图中,横坐标为电压,纵坐标为点数,根据高电平的主峰,得到所述高电平平均值,并根据低电平的主峰,得到所述采样周期中的低电平平均值。

3.如权利要求2所述的数模转换器的建立时间测试方法,其特征在于,所述纵坐标的跨度为:(Vmax-Vmin)×z%,1%≤z≤5%,Vmax为所述采样周期中的最低电压值,Vmax为所述采样周期中的最高电压值。

4.如权利要求1所述的数模转换器的建立时间测试方法,其特征在于,在所述采样数据中查找所述最大上升区间的步骤包括:对依次所述采样数据中相邻的两个采样点进行比较,比较后一采样点的电压值与前一采样点的电压值的大小,找到后一所述采样点的电压值连续大于前一所述采样点的电压值的最长区间,记为假定最大区间,判断所述假定最大区间是否同时满足以下要求:所述假定最大区间起始点的电压值是否小于等于(1+x)×VLmean,0.001%≤x≤10%,VLmean为低电平平均值;所述假定最大区间的结束点的电压值是否大于等于(1-x)×VHmean, VHmean为高电平平均值;所述假定最大区间是否经过所述示波器的采样触发点。

第9章-DAC和ADC

图9.2.6

DAC——CB7520电路原理图

【例1】 下图是用CB7520和74LS161组成的波形发生器电路。已 知CB7520的VREF=-10V,试画出输出电压V0的波形,并标出波形图 上各点电压的幅度。

9.2.7

DAC——CB7520应用举例

§9.2.3 权电流型D/A转换器

在权电阻网络DAC和倒T形电阻网络DAC中的模拟开关在实 际应用中,总存在一定的导通电阻和导通压降,而且每个开关的 情况又不完全相同,所以它们的存在无疑会引起转换误差,影响 转换精度。 权电流型DAC可有效的解决这一问题。其示意图如下:

n

其中: X X n 2

n 1

X n 1 2

n2

X 1 2 Dn

0

一般的数模转换器的基本组成可分为四部分,即:电 阻译码网络、模拟开关、基准电压源和求和运算放大器。

图9.2.2 数模转换器原理图

目前使用最广泛的D/A转换技术有两种:权电阻网络 D/A转换和T形电阻网络D/A转换。

本章主要内容

第一节

概述

第二节

D/A转换器

第三节 A/D转换器

§9.1 概述

DAC和ADC的应用举例:

DAC和ADC的应用举例——MP3播放器:

DAC和ADC的应用举例——数字温度计:

DAC和ADC的应用举例——数字血压计:

在过程控制和信息处理中,经常会遇到一些连续变化的 物理量,如话音、温度、压力、流量等,它们的量值都是 随时间连续变化的。为了能使用数字电路处理模拟信号, 必须把模拟信号转换成相应的数字信号,方能送入数字系 统进行处理。同时,还往往要求将处理后得到的数字信号 再转换为相应的模拟信号作为最后的输出。 图9.1.1所示即为一个典型的数字控制系统框图:

DAC_ADC模数及数模转换器的发展综述

DAC_ADC模数及数模转换器的发展综述1 概述随着数字技术,特别是计算机技术的飞速发展普及,在现代控制、通讯及检测领域中,对信号的处理广泛采用了数字计算机技术。

由于系统的实际处理对象往往都是一些模拟量(如温度、压力、位移、图像等),要使计算机或数字仪表能识别和处理这些信号,必须首先将这些模拟信号转换成数字信号;而经计算机分析、处理后输出的数字量往往也需要将其转换成为相应的模拟信号才能为执行机构所接收。

这样,就需要一种能在模拟信号与数字信号之间起桥梁作用的电路——模数转换电路或数模转换电路。

能将模拟信号转换成数字信号的电路,称为模数转换器(简称ADC转换器);而将能反数字信号转换成模拟信号的电路称为数模转换器(简称DAC转换器),ADC转换器和DAC 转换器已经成为计算机系统中不可缺少的接口电路。

2 数模转换电路2.1 数模转换电路原理数字量是用代码按数位组合起来表示的,对于有权码,每位代码都有一定的权。

为了将数字量转换成模拟量,必须将每1位的代码按其权的大小转换成相应的模拟量,然后将这些模拟量相加,即可得到与数字量成正比的总模拟量,从而实现了数字—模拟转换。

这就是构成DAC转换器的基本思路。

2.2 数模转换电路的主要性能指标DAC转换器的主要性能指标有:转换速度、转换精度、抗干扰能力等。

在选用D/A转换器时,一般应根据上述几个性能指标综合进行考虑。

2.3 二进制加权架构从概念上讲,最简单的DAC采用的是二进制加权架构,在该架构中,将n个二进制加权元件(电流源、电阻器或电容器)进行组合以提供一个模拟输出(n = DAC分辨率)。

这种架构虽然最大限度地减少了数字编码电路,但MSB和LSB加权之间的差异却随着分辨率的增加而增大,从而使得元件的精确匹配变得很困难。

采用该架构的高分辨率DAC不仅难以制造,而且还对失配误差很敏感。

2.4 开尔文(Kelvin)分压器架构开尔文分压器架构由2的n次方个等值电阻器组成,与二进制加权法相比,这种架构简化了匹配处理(见图1)。

DAC的定义及工作原理详解

DAC的定义及工作原理详解一、DAC定义数模转换器,又称D/A转换器,简称DAC,它是把数字量转变成模拟的器件。

D/A转换器基本上由4个部分组成,即权电阻网络、运算放大器、基准电源和模拟开关。

模数转换器中一般都要用到数模转换器,模数转换器即A/D转换器,简称ADC,它是把连续的模拟信号转变为离散的数字信号的器件。

按照二进制数字量的位数划分,有8 位、10 位、12 位、16位D/A转换器;按照数字量的数码形式划分,有二进制码和BCD码D/A转换器;按照D/A转换器输出方式划分,有电流输出型和电压输出型D/A转换器。

在实际应用中,对于电流输出的D/A转换器,如需要模拟电压输出,可在其输出端加一个由运算放大器构成的I/V转换电路,将电流输出转换为电压输出。

单片机与D/A转换器的连接,早期多采用8位数字量并行传输的并行接口,现在除并行接口外,带有串行口的D/A转换器品种也不断增多。

除了通用的UART串行口外,目前较为流行的还有IIC串行口和SPI串行口等。

所以在选择单片D/A转换器时,要考虑单片机与D/A 转换器的接口形式。

目前部分单片机芯片中集成的D/A转换器位数一般在10位左右,且转换速度很快,所以单片的DAC开始向高位数和高转换速度上转变。

低端的产品,如8位的D/A转换器,开始面临被淘汰的危险,但是在实验室或涉及某些工业控制方面的应用,低端的8位DAC以其优异性价比还是具有相当大的应用空间的。

二、DAC性能指标1)分辨率分辨率是指输入数字量的最低有效位(LSB)发生变化时,所对应的输出模拟量(常为电压)的变化量。

它反映了输出模拟量的最小变化值。

分辨率与输入数字量的位数有确定的关系,可以表示成FS/2n。

FS表示满量程输入值,n为二进制位数。

对于5V的满量程,采用8位的DAC 时,分辨率为5V/28=19.5mV;当采用12位的DAC时,分辨率则为5V/212=1.22mV。

显然,位数越多,分辨率就越高。

数模转换转器DAC基本原理剖析

电路分析专题研讨数模转换转器DAC基本原理剖析数模转换转器DAC基本原理剖析摘要:在信息处理技术方面,为解决数字信号与模拟信号间转换的问题,产生了DAC数字-模拟转换器,将计算机二进制编码转换成被处理的物理量,即模拟信号。

本文详细阐述了R-2R网络型D/A转换器的基本原理,通过运用等效方法和叠加原理推导出了R-2R网络型D/A转换的基本规律:V0=k*(2n-1Dn-1+ (21)1+20D).并且运用EWB工作台进行静态特性验证和动态波形输出的仿真,系统地阐明了DAC数模转换器的工作原理。

关键词:数模转换、EWB仿真、数字控制电压增益1 引言:随着数字技术,特别是数字计算机的迅猛发展,人类在处理可靠性、精度等重要指标方面有了更加高的要求。

由于数字信号具有比模拟信号更加稳定,更易压缩,更易传输,失真率小的优越性,因此数字信号与模拟信号的转换成了当今科研的热点课题。

本文主要介绍数字信号与模拟信号转换的桥梁之一----DAC数模转换器的基本原理,DAC:将计算机或控制器产生的二进制数字转换成与之成比例的模拟电压。

并运用EWB工作台进行仿真,验证结论。

2 D/A转换器基本原理推导:图 2—1是3位R-2R网络型D/A转换器的基本原理图,主要由电阻网络、3个单刀双掷模拟开关、参考电压Vs及运算放大器四部分组成。

图中的电阻网络由3个R-2R网络块,每块对应一个输入位,块与块之间串联成R-2R电阻网络。

对于每个电阻网络块,若输入的二进制代码是1,则开关拨向电压源那端的触点,参考电压接入了该电阻网络中。

若输入的是0则开关拨向空载导线那端的触点,此时,电压源未接入网络中。

考虑运算放大器的“虚地”特性,无论输入数字量Di为何值每个2K欧姆的电阻的下端都相当于接地,所以从每个1K欧姆电阻向右看过去对地电阻都是2K欧姆。

因此,网络中电压的分配应该是,从参考电源输出的总电压Vs每向右经过一个2K欧姆电阻,该电阻上的电压就被分为一半。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

解读高速数/模转换器(DAC)的建立和保持时间

摘要:本应用笔记定义了高速数/模转换器(D AC)的建立和保持时间,并给出了相应的图例。

高速D AC的这两个参数通常定义为“正、负”值,了解它们与数据瞬态特性之间的关系是一个难点,为了解决这些难题,本文提供了一些图例。

介绍

为了达到高速数/模转换器(DAC)的最佳性能,需要严格满足数字信号的时序要求。

随着时钟频率的提高,数字接口的建立和保持时间成为系统设计人员需要重点关注的参数。

本应用笔记对建立和保持时间进行详尽说明,因为这些参数与Maxim的高性能数据转换方案密切相关。

定义建立和保持时间

建立时间(t S)是相对于DAC时钟跳变,数据必须达到有效的逻辑电平的时间。

保持时间(t H)则定义了器件捕获/采样数据后允许数据发生变化的时间。

图1给出了相对于时钟上升沿的建立和保持时间。

特定器件的时钟信号有效边沿可能是上升/下降沿,或由用户选择,例如MAX5895 16位、500Msps、插值和调制双通道DAC,CMOS输入。

图1. 相对于时钟信号上升沿的建立和保持时间

采用CMOS技术设计的数字电路通常将电源摆幅的中间值作为切换点。

因此,时间参考点定在信号边沿的中点。

图1波形标明了器件在典型条件下的建立和保持时间。

注意此时定义的这两个参数均为正值,但在建立或保持时间出现负值时将会令人迷惑不解。

MAX5891 600Msps、16位DAC为这一中间值状态提供了很好的学习实例。

该器件的建立时间为-1.5ns,而保持时间为2.6ns。

图2给出MAX5891的最小建立时间。

注意,实际应用中,数据通常在采样时钟跳变后发生变化。

图3给出了相同器件的最小保持时间。

图2. MAX5891的最小建立时间

图3. MAX5891的最小保持时间

为满足这些是需要求,用户需要分析数据源的传输延迟和抖动。

传输延迟决定了时钟的标称定时要求,而抖动指标则决定了所允许的容限。

为了解释这一关系,我们以具有1.5ns传输延迟的逻辑门电路为例。

如果在逻辑门电路作用相同的时钟信号,MAX5891将刚好满足如图2所示的建立时间。

这种情况下,对于温度漂移、时钟或数据抖动以及器件之间存在的差异都不具备任何设计裕量。

可以采用两种方法对建立和保持时间进行优化,包括增加时钟延迟、保持一致的引线长度等。

在数据源和DAC之间增加时钟延迟有助于解决上述例子中的传输延迟问题。

保持一致的数据源与DAC输入引脚之间的引线长度可以确保抖动、漂移不会使某一位进入下一个时钟周期。

需要注意的是,我们现在处理的是包含多条数据线的高速数据总线,任何时刻所有位都必须满足时序要求。

结论

处理高频数据的定时面临诸多挑战,解决这些难题需要设计人员或系统设计工程师充分理解具体信号链路中所有器件的规格。

如果链路中任一器件的规格要求得不到满足,系统性能将会降低。

性能的降低表现为DAC输出精度的下降或限制时钟频率。