实验35 数字集成电路的Verilog描述与仿真

实验二 全加器的设计与仿真

实验二全加器的设计与仿真全加器是非常典型的数字单元电路,在数字系统中常常用到全加器。

一般认为加法器是纯组合逻辑电路,只要用一些基本门电路就可以设计出全加器。

通常情况下,全加器是数字系统中的一个子模块,为了使加法器能与系统在时钟的驱动下同步工作,我们把全加器设计成由时钟控制带一级流水线的加法器。

需要指出的是,在数字集成电路设计中,大多数公司使用VerilogHDL进行RTL设计,较少使用VHDL,主要的原因是VerilogHDL语法简单易学,底层库支持好,EDA工具支持全面,集成电路发达的国家和地区应用广泛。

而VHDL的发展逐渐式微,越来越多的公司正逐渐向VerilogHDL转移。

建议使用VerilogHDL进行RTL设计,便于交流。

集成电路设计中心实验室的工作站运行环境为:•Sun Blade2000两台•双64-bit CPU, 内存4GB ,•硬盘73GB用户可以通过Xmanager 登录,每个用户拥有50MB的磁盘配额。

2.1设计文件准备和编译按可综合风格写出VerilogHDL代码如下(仅供参考):module Adder8 (ain, bin, cin, sout, cout, clk,rst);/* Eight Bit Adder Module */output [7:0] sout;output cout;input [7:0] ain, bin;input cin, clk,rst;wire [7:0] sout_tmp, ain, bin;wire cout_tmp;reg [7:0] sout, ain_tmp, bin_tmp;reg cout, cin_tmp;always @(posedge clk)beginif (rst==1)beginsout=0;cout=0;ain_tmp=ain;bin_tmp=bin;cin_tmp=cin;endelsebegincout = cout_tmp;sout = sout_tmp;ain_tmp = ain;bin_tmp = bin;cin_tmp = cin;endendassign {cout_tmp,sout_tmp} = ain_tmp + bin_tmp + cin_tmp;endmodule上述代码在Unix/Linux 系统中,在用户目录下,建文件夹Adder8_full, 下建src,sim,syn,pr四个目录。

verilog教程

verilog教程Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它是一种流行的HDL,广泛用于硬件设计和验证领域。

本教程将介绍Verilog的基本概念和语法,以帮助初学者入门。

一、Verilog的基本概念1.1 什么是VerilogVerilog是一种描述数字系统的语言,它可以用来描述硬件电路、验证设计的正确性以及进行电路仿真。

1.2 Verilog的应用领域Verilog广泛应用于硬件设计和验证领域,包括用于开发ASIC(应用特定集成电路)、FPGA(现场可编程门阵列)以及其他数字系统的设计。

1.3 Verilog的版本Verilog有多个版本,包括Verilog-1995、Verilog-2001以及最新的Verilog-2005、这些版本之间有一些语法和功能上的差异。

二、Verilog的语法结构2.1模块和端口在Verilog中,所有的电路描述都是由模块(module)组成的。

模块是电路的基本组成单元,可以看作是一个黑盒子,它接受一些输入,产生一些输出。

2.2信号声明在Verilog中,我们需要声明所有的输入和输出信号。

可以使用`input`和`output`关键字来声明这些信号。

2.3电路实现Verilog允许使用多种语句和结构来描述电路的行为和结构。

这些语句包括顺序语句、条件语句、循环语句以及层次结构。

2.4实例化模块在一个模块中,我们可以实例化其他的模块。

这样可以将一个大的电路拆分成多个小的模块,方便编写和测试。

三、Verilog的仿真和验证3.1静态验证Verilog语言本身提供了很多语法和语义层面的验证功能,对于语法和类型错误会有相应的提示。

3.2激励设计在进行电路验证时,我们需要为输入信号提供激励。

Verilog提供了一种称为`testbench`的特殊模块,用于生成输入信号并将其应用到待验证的电路中。

3.3波形仿真在Verilog中,我们可以使用仿真器来模拟电路的行为,并生成波形图来验证电路是否按预期工作。

Verilog的用途

Verilog的用途1. 数字系统设计:Verilog最常见的用途之一是设计数字电路和系统。

它提供了一种描述硬件功能和结构的方式,使工程师能够将问题抽象成代码,并在硬件中实现。

因此,Verilog在各种应用中都发挥作用,包括处理器、存储器、通信系统、图像处理、音频处理等。

2. 硬件建模:Verilog可以用于建模和验证硬件系统的功能。

它允许工程师在早期设计阶段使用软件来仿真硬件行为,以验证设计的正确性。

通过建立准确的模型,工程师能够更好地理解和评估硬件系统。

3. 硬件验证:Verilog提供了一种验证硬件系统的方法。

验证是确保硬件系统工作正常的过程,通过提供大量的测试用例来检查系统的正确性。

工程师可以使用Verilog编写测试用例,并使用仿真器来验证硬件的行为。

4. 电路综合:Verilog还可以用于电路综合,将高级级代码转换为逻辑门级网表。

这是将设计从概念级到实施级的重要步骤。

通过电路综合,工程师可以根据特定的目标(如时延、功耗等)生成一个优化的电路设计。

5. FPGA和ASIC设计:Verilog是在FPGA(可编程逻辑器件)和ASIC(应用特定集成电路)上实现硬件设计的主要语言之一、由于FPGA和ASIC的实现目标不同,Verilog提供了灵活的设计风格和优化技术,以满足不同的需求。

6. 混合信号系统设计:除了数字设计外,Verilog还可以与模拟和混合信号系统集成。

这使得工程师能够在一个环境中同时处理数字和模拟信号,从而提高系统的整体性能和可靠性。

7. 硬件仿真:Verilog除了用于描述硬件行为外,还可以用于进行硬件仿真。

工程师可以在仿真器中加载Verilog代码,并模拟硬件的行为。

这样,他们可以在实际硬件实现之前评估系统的性能、功能和正确性。

8. 硬件调试:Verilog在硬件调试中也是非常有用的。

由于硬件设计的复杂性,出现错误时找到问题可能会很困难。

Verilog提供了调试功能,如信号波形查看、断点设置、单步执行等,可以帮助工程师定位和修复问题。

verilog 门电路 移位算法 -回复

verilog 门电路移位算法-回复Verilog门电路移位算法指的是使用Verilog语言实现的一种算法,用于在数字电路设计中实现移位操作。

移位操作是对数据位进行移动的操作,可以向左或向右移动指定的位数。

在数字集成电路中,移位操作常常用于实现乘法、除法、逻辑运算等功能。

本文将一步一步回答关于Verilog门电路移位算法的问题,并详细介绍其原理、应用和实现方式。

第一步:了解移位算法的基本原理和分类移位算法是一种将数据位向指定方向移动的算法。

根据移位方向的不同,可以将移位算法分为左移和右移。

左移是将数据位向数的高位方向移动,右移是将数据位向数的低位方向移动。

在Verilog门电路中,通常使用逻辑门电路实现移位算法。

第二步:理解移位算法的应用场景移位算法在数字电路设计中有广泛的应用场景。

例如,在乘法电路中,移位算法可以用于实现两个数相乘的操作。

将一个数向左移动一定位数,可以实现将该数乘以2的指定次方。

在除法电路中,移位算法可以用于实现两个数相除的操作。

将一个数向右移动一定位数,可以实现将该数除以2的指定次方。

此外,移位算法还可以用于实现逻辑运算,例如逻辑与、逻辑或等。

第三步:了解Verilog语言的基本结构和语法Verilog是一种用于数字电路描述和仿真的硬件描述语言。

在Verilog 中,可以使用门电路、寄存器、触发器等电路元件来构建数字电路。

Verilog语言基于C语言的语法,具有模块化、并发和分层设计的特点。

第四步:编写移位算法的Verilog代码在Verilog中,可以使用逻辑门电路和移位操作符(<<、>>)来实现移位算法。

首先,需要定义输入和输出的位宽。

然后,使用逻辑门电路(如与门、或门等)来实现位的移动。

最后,通过组合逻辑将各个部分连接起来,形成完整的移位算法。

第五步:进行Verilog代码的仿真和验证在编写完Verilog代码后,可以使用Verilog仿真工具进行代码的仿真和验证。

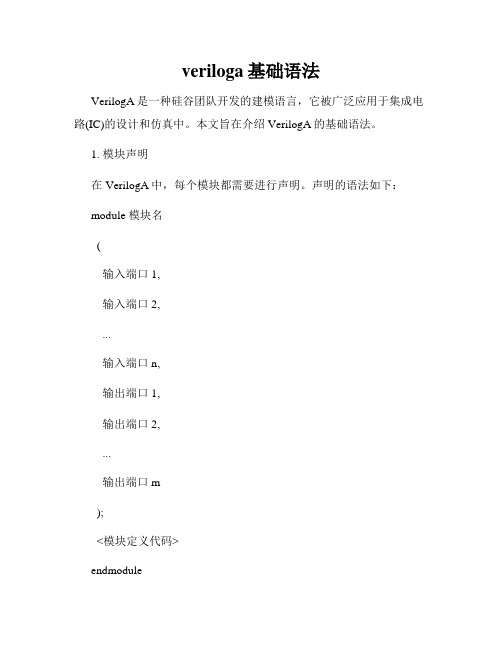

veriloga基础语法

veriloga基础语法VerilogA是一种硅谷团队开发的建模语言,它被广泛应用于集成电路(IC)的设计和仿真中。

本文旨在介绍VerilogA的基础语法。

1. 模块声明在VerilogA中,每个模块都需要进行声明。

声明的语法如下:module 模块名(输入端口1,输入端口2,...输入端口n,输出端口1,输出端口2,...输出端口m);<模块定义代码>endmodule其中,模块名可以由字母、数字和下划线组成,不能以数字开头;输入端口和输出端口可以是标量或向量。

2. 参数声明VerilogA允许在模块中声明参数,以便在实例化时进行配置。

语法如下:parameter 参数名 = 值;参数可以通过assign语句进行连接,也可以在实例化时进行配置。

3. 变量声明在VerilogA中,可以使用不同的变量类型进行声明,如实数、整数、布尔值等。

real: 实数类型,用于存储实数值。

integer: 整数类型,用于存储整数值。

boolean: 布尔类型,用于存储真/假值。

语法如下:real 变量名;integer 变量名;boolean 变量名;4. 函数和任务在VerilogA中,可以使用函数和任务来实现特定的功能。

函数是一段可重用的代码,它接收输入参数并返回一个值。

函数的语法如下:function 返回类型函数名(输入参数);<函数定义代码>return 返回值;endfunction任务是一段可重用的代码,不返回值,但可以通过参数进行输入和输出。

任务的语法如下:task 任务名(输入参数);<任务定义代码>endtask5. 运算符VerilogA支持各种常见的数学和逻辑运算符,如加减乘除、取余、与或非等。

加法运算符:+减法运算符:-乘法运算符:*除法运算符:/取余运算符:%与运算符:&&或运算符:||非运算符:!6. 控制结构在VerilogA中,可以使用if-else、for、while等控制结构来实现条件判断和循环。

verilog中ip核的语法

Verilog中IP核的语法一、IP核概述1. IP核的定义和作用IP核是指可重用的知识产权模块,它可以在数字集成电路设计中被多次使用。

IP核是现代芯片设计中的重要组成部分,能够提高设计的灵活性和可重用性,加速设计过程,降低开发成本。

2. IP核的分类IP核按照功能和用途的不同可以分为逻辑IP核、存储IP核、串行IP 核等。

不同类型的IP核在Verilog语法中的使用也略有不同。

二、Verilog中IP核的语法1. 实例化IP核在Verilog中,实例化IP核是将IP核的定义添加到设计中的过程。

实例化IP核可以通过以下语法实现:```verilogmodule top_module;// 实例化一个逻辑IP核IP_core_logic core_inst (.input1(input1), // 连接输入端口.input2(input2),.output(output) // 连接输出端口);// 实例化一个存储IP核IP_core_memory mem_inst (.clk(clk), // 连接时钟.rst(rst), // 连接复位.data_in(data_in), // 连接数据输入.data_out(data_out) // 连接数据输出);endmodule```2. IP核的端口连接在Verilog中,连接IP核的端口需要使用`.`操作符来指定连接的是哪个端口,语法格式如上例所示。

3. IP核的参数化有些IP核在实例化的过程中需要指定参数,比如宽度、位数等。

在Verilog中,可以使用参数来实现IP核的参数化,示例代码如下:```verilogmodule top_module;parameter WIDTH = 8; // 定义参数宽度为8位parameter DEPTH = 16; // 定义参数深度为16// 实例化一个参数化的IP核IP_core_parametrized #(.WIDTH(WIDTH), // 指定宽度参数.DEPTH(DEPTH) // 指定深度参数) core_inst (.input(input), // 连接输入端口.output(output) // 连接输出端口);endmodule```4. IP核的内部逻辑大多数IP核在Verilog中是使用黑盒方式实现的,而IP核的内部逻辑通常是由供应商提供的,用户无法直接查看或修改。

Verilog-A

Verilog-A的模拟电路行为模型及仿真作者:朱樟明,张春朋,杨银堂,付永朝关键词:Verilog-A,行为,模型,仿真摘要:分析了模拟硬件描述语言Verilog-A的特点及模型结构,根据仿真速度和仿真精度的折衷考虑,设计实现了模拟开关、带隙基准电压源及运放的Verilog-A行为模型。

根据数模转换器(DAC)的特性,基于Verilog-A设计了DAC参数测试模型,也建立8位DAC 的行为模型。

所有行为模型都在Cadence Spectre仿真器中实现了仿真验证。

随着集成电路技术的不断发展,片上系统(SOC)设计正在成为集成电路设计的发展方向。

SOC芯片集成了大量的IP核,如微处理器、数字信号处理器(DSP)、模/数转换器(ADC)、数/模转换器(DAC)、模拟滤波器、存储器及射频(RF)单元等,使得芯片的设计规模远远超过了以往的设计,其片内通讯及IP核接口的复杂程度也大大提高,从而使其设计的难度和复杂度都达到了前所未有的程度[1],而SOC系统验证就成为了设计的难点。

SOC系统验证就是对基于IP核实现的SOC系统进行功能验证、静态时序分析、功耗分析等,以保证正确的系统功能和良好的产品性能。

以前的SOC验证方法是基于混合信号集成电路仿真方法,其中模拟IP核的仿真则采用Spice仿真方法实现。

虽然这种仿真方法具有较高的仿真精度,但是仿真速度无法满足产品开发的时间要求,也对仿真收敛性提出了新的要求。

本文基于模拟硬件描述语言Verilog-A,研究模拟电路的行为模型及仿真,建立了带隙基准电压源、运放等模拟IP核的精确行为模型。

如果对所有的模拟IP核建立精确行为模型,不仅可以很好的解决SOC的系统验证,也可以解决ADC等混合信号集成电路的参数测试问题。

1模拟硬件描述语言Verilog-AVerilog-A是描述模拟电路系统和模拟电路单元的结构、行为及特性参数的模块化硬件描述语言[2-3],也可以用于描述传统的信号系统,如固体力学、流体力学、热力学等系统。

数字集成电路的设计.

9.2.1数字集成电路的设计目前集成电路设计中最常用的逻辑仿真工具是Cadence公司的Verilog系列仿真器,包括上世纪80年底由Cadence公司创始人Phil Moorby设计的Verilog-XL以及基于Verilog-XL 的升级版本NC-Verilog。

Verilog-XL是伴随Verilog HDL(Hardware Description Language)硬件描述语言而建立起来的解释型仿真器,其有一个运行时间解释工具执行每一条Verilog指令,并且与事件队列进行交流,是基于XL算法的快速门级仿真。

V erilog HDL是目前行业内公认的标准行为级硬件设计语言,V erilog-XL也是Verilog-1995标准的参考仿真器。

NC-Verilog是Verilog-XL的升级版本,它采用了原素编译(Native-Compiled)技术,无论仿真速度、编辑能力、存储容量、侦错环境以及处理电路的规模等都大大升级。

与Verilog-XL不同的是,NC-Verilog是一个编译仿真器,它把Verilog代码转换成一个C程序,再把C程序编译成仿真器,这种编译而成的仿真器运行速度要比Verilog-XL解释仿真器快,并且与Verilog-2001标准兼容。

这里还是针对Cadence的经典仿真器Verilog-XL,以6.6节中所介绍的计数器为例介绍逻辑仿真的基本概念和流程。

1、仿真对象的确定在6.6节中所列出的图6-5是一个8位异步计数器,由8个触发器构成,采用Verilog-XL 可以在Schematic(电路图)这一个层次对该计数器进行仿真,跟在HDL(硬件描述语言)这个层次上进行仿真是两个不同的概念,适合于不同的集成电路设计流程和方法,这里简单解释如下:第一种设计流程是通过对将要设计的产品用硬件描述语言来表达其逻辑功能,然后采用仿真工具如Verilog-XL来进行行为级的仿真(即不涉及到具体逻辑电路图);在仿真通过后可以采用逻辑综合工具如Cadence公司的BuildGates或者Synopsys公司的Design Compiler 等得到门级电路图,然后继续下面的流程;第二种设计流程是在门级电路图上开始,如采用9.1.3节中所介绍的ChipAnalyzer软件,基于一个现有芯片的背景图像提取其逻辑电路图,也可以是集成电路设计者利用其自身知识搭建电路图,然后采用Verilog-XL在电路图这个层面上进行功能验证。

数字系统设计与Verilog HDL

数字系统设计与Verilog HDL(复习)EDA(Electronic Design Automation)就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子CAD(Computer Aided Design)2.电子CAE(Computer Aided Engineering)3.EDA(Electronic Design Automation)EDA技术及其发展p2EDA技术的应用范畴1.3 数字系统设计的流程基于FPGA/CPLD的数字系统设计流程1. 原理图输入(Schematic diagrams )2、硬件描述语言 (HDL文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(Synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(RTL)◆逻辑综合:RTL级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对CPLD器件而言,产生熔丝图文件,即JEDEC文件;对FPGA器件则产生Bitstream 位流数据文件p8仿真(Simulation)功能仿真(Function Simulation)时序仿真(Timing Simulation)仿真是对所设计电路的功能的验证p9编程(Program)把适配后生成的编程文件装入到PLD器件中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program),将基于SRAM 工艺结构的PLD器件的下载称为配置(Configure)。

Verilog语言详解

第三章 Cadence仿真器

学习内容

逻辑仿真算法 如何启动Verilog-XL和NC Verilog仿真器 如何显示波形

仿真算法

主要有三种仿真算法

基于时间的(SPICE仿真器) 基于事件的(Verilog-XL和NC Verilog仿真器) 基于周期的(cycle)

仿真算法

基于时间的算法用于处理连续的时间及变量

课程内容(三)

• 逻辑综合的介绍

– – – – – 简介 设计对象 静态时序分析 (STA) design analyzer环境 可综合的HDL编码风格

• 可综合的Verilog HDL

– Verilog HDL中的一些窍门 – Designware库 – 综合划分

•

实验 (1)

课程内容(四)

• 设计约束( Constraint)

Verilog HDL是在1983年由GDA(GateWay Design Automation)公司的Phil Moorby所创。Phi Moorby 后来成为Verilog-XL的主要设计者和Cadence公司的第一个合伙人。

在1984~1985年间,Moorby设计出了第一个Verilog-XL的仿真器。

Verilog还有一定的晶体管级描述能力及算法级描述能力

行为级和RTL级

MUX的行为可以描述为:只要信号a或b或sel发生变化,如果sel为0则选择a输出;否则选择 b输出。

module muxtwo (out, a, b, sel); input a, b, sel; output out; reg out; always @( sel or a or b) if (! sel) out = a; else out = b; endmodule