ARM与FPGA通信接口板设计.

ARM与FPGA高速数据通信接口设计研究

ARM与FPGA高速数据通信接口设计研究作者:邱浩淼来源:《科学与信息化》2019年第06期摘要在当前,利用ARM与FPGA高速数据通信接口的相关设计,满足了数据采集器相关设备工作中对信号的高速要求。

如果要实现ARM与FPGA之间的信号交互工作,主要是通过SPI总线来进行完成,然后数据的上传工作,主要需采用双口RAM来完成。

这种设计其主要目的为了解决在ARM于FPGA运行中,其对数据的处理速度匹配不良或不匹配的情况,并且该设计满足高速、实时的需求。

与此同时,根据相关的测试可以看出,此系统的设计不仅促使操作更为简单,功能也稳定正常。

在仪器控制、电子测量的相关工作中应用广泛。

本文结合自己相关经验,对基于ARM与FPGA高速数据通信接口设计进行相关探讨。

关键词 ARM与FPGA;数据通信;接口设计前言这些年来我国的科技日新月异,各类仪器的性能也变得越来越高,从而对仪器的性能也有了更高的要求和标准,其中对于仪器控制方面有诸多的要求,无论从仪器的实时性能,还是其精准度、采样速度等方面,都有着非常高的要求和标准。

为了满足仪器的控制需求,则需要不断应用先进的技术,不断提升通信质量,建立高速数据通信接口设计,满足人们的使用需求。

1 LINUX程序设计在过去的信号采集工作中,通常需要通过单片机或者通过DSP来完成。

但是,单片机存在时钟频率不高的情况,导致信号采集没有足够的速度,也无法提升效率。

如果想要进行高速的信息采集,就无法应用单片机[1]。

DSP虽然拥有较快的运算速度,但其对于外部复杂的硬件没有良好的控制。

而如果应用FPGA就可以避免上述的问题,非常适合于高速信号的采集工作和控制工作,对提高信息通讯的效率有着极大的作用,进而满足数据采集和控制工作需求。

相对来说,ARM技术具有成本低、体积小、速度很快等优势,诸多优点集于一身,其比较适合处理大容量的数据和控制。

如果想要linux系统与FPGA可以配合并使用,就需要设计出相应的驱动。

详解ARM处理器和FPGA之间的通信技术

详解ARM处理器和FPGA之间的通信技术详解ARM处理器和FPGA之间的通信技术1前言在ARM+FPGA系统结构中,实现基于ARM的嵌入式处理器和FPGA之间通信最简单的方法就是通过异步串行接口EIARS232C。

考虑选用集成有UART(Universal Asynchronous Receiver / TraNSmitter )控制器的嵌入式处理器(例如,EP7312),那么嵌入式处理器一侧就具有了利用异步串行接口收、发通信的能力。

然而,FPGA内部并不拥有CPU控制单元,无法处理由UART控制器产生的中断,所以FPGA 一侧不能利用现成的UART控制器构成异步串行接口,必须将UART控制器的功能集成到FPGA内部。

同一个系统中的ARM与FPGA之间属于短距离通信连接,他们之间的异步串行通信并不需要完整的UART功能,那些RS232标准中的联络控制信号线可以省略,仅仅保留收、发数据线和地线,这样给UART功能的FPGA编程实现带来了极大的省略。

嵌入式处理器EP7312带有2个支持异步串行通信RS232的16550类型的UART,UART1不仅有TX,RX,而且支持Modem控制信号,UART2只有标准的TX,RX以及地信号,刚好能够利用UART2与FPGA实现通信。

2简化UART功能的FPGA实现本文将详细地讨论简化UART功能在FPGA中的实现方法。

简单回顾一下异步串行通信的数据格式。

图2表明在异步传送中串行发送一个数据字节的位定时关系(图中没有包括奇偶校验位)。

发送一个完整的字节信息,首先是一个作为起始位的逻辑0位,接着是8个数据位,然后是1个、1+1/2个或2个停止位逻辑1位,数据线空闲时呈现为高或1状态。

在字符的8位数据部分,先发送数据的最低位,最后发送最高位。

每位持续的时间是固定的,由发送器本地时钟控制,每秒发送的数据位个数,即为波特率。

起始位和停止位起着很重要的作用。

显然,他们标志每个字符的开始和结束,但更重要的是他们使接收器能把他的局部时钟与每个新开始接收的字符再同步。

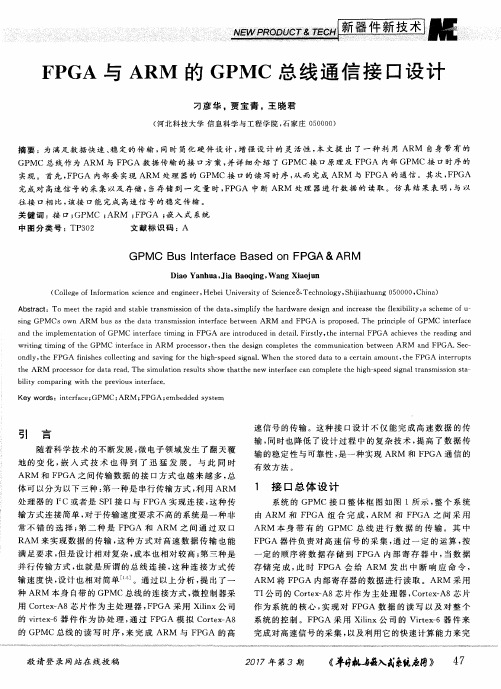

FPGA与ARM的GPMC总线通信接口设计

敬请登录网 站在线投稿

2 0 1 7 # - g 3 期

《 平 机 1 菡 } 入式豪 碗启I j 9 》

4 7

l l

|

l 。

成信 号 的 计算 , 最 重 要的 是 它本 身 灵 活 的 编程 方 式 能 很 好 地模 拟 GP MC总 线 接 口 的读 写 时 序 , 从而 实现 F P GA 和 ARM 之 间数 据 的稳 定 传 输 。

定 的顺 序 将 数 据 存 储 到 F P GA 内 部 寄 存 器 中 , 当 数 据

存储 完 成 , 此时 F P GA 会 给 AR M 发 出 中断 响应 命 令 ,

AR M将F P G A 内部 寄 存 器 的 数 据 进 行 读 取 。AR M 采 用

TI 公司的 C o r t e x - A8芯 片作 为 主 处 理 器 , C o r t e x - A8芯 片 作 为 系 统 的核 心 , 实 现对 F P GA 数 据 的 读 写 以 及 对 整 个 系 统 的 控 制 。F P GA 采 用 Xi l i n x公 司 的 Vi r t e x - 6器 件 来 完成对高速信号的采集 , 以及 利 用 它 的快 速 计 算 能 力 来 完

fpga与arm通信

FPGA 与ARM 连接图 Data[7:0]

Re_En Re_Finish clk signal rst 50MHz 时钟编码器脉冲信号

复位信号P2[7]-P2[0]Data[15:8] P0[22]-P0[15]

P0[10]P0[11]

FPGA

ARM FPGA 内部逻辑图 counter0

counter1clk

rst Re_Finish signal

Data[15::0]

Re_En

Counter_flag Counter0_Data

[15::0]

Counter1_Data [15::0]

数据采集板存在的问题及改进方法

1、AD采集模块没有用单独稳压电源

电源模块采用两级连接DC-DC、LDC,DC-DC初步稳压到6V,在用LDC稳压输出一个平稳电源5v电压,提供给AD模块。

2、AD模块未按照芯片手册进行器件连接和布局

按照所用AD转换器的使用说明,选用适当型号尺寸的电阻、电容,按照要求进行AD模块元器件布局。

3、以太网模块没有使用独立地

以太网模块PCB布线时尽量把该模块RJ-45的地独立出来,提高电磁兼容性。

4、PCB布线数字模拟地未分离

PCB布线时应该把数字模拟地分离,提高板子抗干扰性能。

5、模拟信号接口BNC体积过大

建议采用SMA接口

6、没有总的电源开关和标准电源接口

在板子上设计总的电源开关和电源接口,外部连接类似手机充电器的电源。

7、板子上几个接口CAN总线、RS485没有用

去除无用模块,减小板子尺寸。

8、PCB走线杂乱,信号干扰大

采用四层PCB板设计。

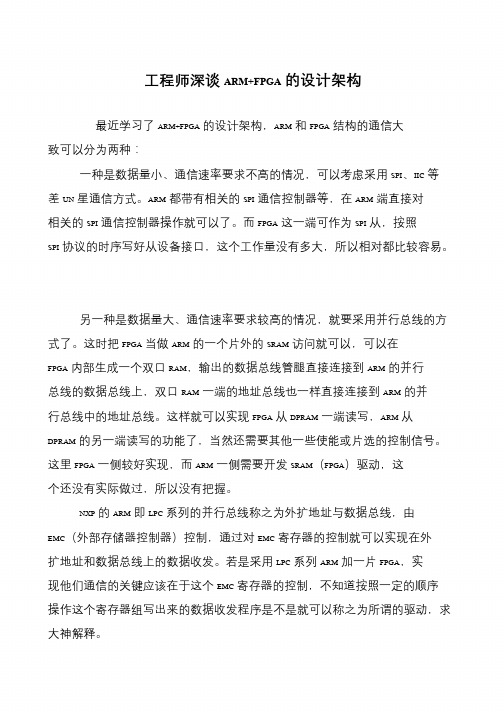

工程师深谈ARM+FPGA的设计架构

工程师深谈ARM+FPGA的设计架构最近学习了ARM+FPGA的设计架构,ARM和FPGA结构的通信大致可以分为两种:一种是数据量小、通信速率要求不高的情况,可以考虑采用SPI、IIC等差UN星通信方式。

ARM都带有相关的SPI通信控制器等,在ARM端直接对相关的SPI通信控制器操作就可以了。

而FPGA这一端可作为SPI从,按照SPI协议的时序写好从设备接口,这个工作量没有多大,所以相对都比较容易。

另一种是数据量大、通信速率要求较高的情况,就要采用并行总线的方式了。

这时把FPGA当做ARM的一个片外的SRAM访问就可以,可以在FPGA内部生成一个双口RAM,输出的数据总线管腿直接连接到ARM的并行总线的数据总线上,双口RAM一端的地址总线也一样直接连接到ARM的并行总线中的地址总线。

这样就可以实现FPGA从DPRAM一端读写,ARM从DPRAM的另一端读写的功能了,当然还需要其他一些使能或片选的控制信号。

这里FPGA一侧较好实现,而ARM一侧需要开发SRAM(FPGA)驱动,这个还没有实际做过,所以没有把握。

NXP的ARM即LPC系列的并行总线称之为外扩地址与数据总线,由EMC(外部存储器控制器)控制,通过对EMC寄存器的控制就可以实现在外扩地址和数据总线上的数据收发。

若是采用LPC系列ARM加一片FPGA,实现他们通信的关键应该在于这个EMC寄存器的控制,不知道按照一定的顺序操作这个寄存器组写出来的数据收发程序是不是就可以称之为所谓的驱动,求大神解释。

TI 的ARM 或DSP 都有一个GPMC(通用内存控制器),它类似于LPC 的EMC,是TI 的芯片中用于与外部存储设备如NORFLASH、NANDFLASH、SRAM 等通信的一个借口。

对于这个同样也有上边的那个疑问。

三星的S5PV210 则是有一组并行总线接口,称之为SROM,同样也有一个SROM 控制器,支持外扩的NORFALSH、NANDFLASH、SRAM 等,应该也类似于LPC 系列的EMC。

ARM与FPGA通信接口板设计.

ARM与FPGA通信接口板设计关键词:双口RAM;乒乓操作;流控机制1 概述某项目中需设计一块通信接口板,实现ARM 2440核心板和FPGA信号处理板之间的通信,因该板交换速率达到10Mbps,要求不能频繁中断ARM处理器,且具备流控机制,设计上有一定难度,基于双口RAM设计了乒乓操作机制和流控机制,有效地降低了系统负荷。

2 电路及驱动设计2.1 接口板电路设计接口板基于两片双口RAM芯片IDT CY7C007AV实现,电路示意图如图1所示。

每片CY7C007AV有8KB的存储空间,12位地址总线,8位数据总线。

为提高端口读写效率,FPGA对ARM发送时采用乒乓操作方式,ARM对FPGA发送时采用流控方式。

由于核心板扩展槽的地址总线和数据总线位宽限制,采用两片双口RAM,一片供FPGA向ARM发送数据用,另一片供ARM向FPGA发送数据用,以下分别建成上部双口RAM和下部双口RAM。

上部双口RAM分为两部分,供FPGA采用乒乓操作方式写入数据,FPGA写完上半部后通过在EINT5上产生上升沿中断通知ARM,写完下半部后通过通过在EINT6上产生上升沿中断通知ARM。

下部双口RAM供ARM向FPGA写入数据,其接线方式与上部双口RAM类似。

两块双口RAM的电路采用对称方式,其电路如图2所示。

两片双口RAM可以互换,下部双口RAM也可供FPGA写入数据,而ARM则写入上部双口RAM。

在实际测试中,两种方式均测试过。

ARM与双口RAM连接时,采用SRAM时序,为避免/减弱二次反射,ARM与总线驱动之间加33欧的串联匹配电阻,匹配电阻靠近扩展槽的近端。

FPGA端对双口RAM的读写也采用SRAM时序,在与双口RAM连接时均串了33欧姆的匹配电阻。

由于核心板上ARM处理器距离接口板较远,接近十厘米,且核心板为四层板,总线驱动能力较弱,在ARM处理器和双口RAM之间添加四片总线驱动芯片,除增加总线驱动能力外还可通过关断总线驱动芯片,避免接口板噪声干扰核心板。

基于FPGA的ARM与绝对式编码器的通信接口实现

基于FPGA的ARM与绝对式编码器的通信接口实现基于FPGA(现场可编程逻辑门阵列)的ARM(高级RISC机器)与绝对式编码器的通信接口实现,可以实现ARM处理器与外部设备的数据交互。

本文将探讨FPGA与ARM在绝对式编码器通信接口上的应用,包括通信原理、通信接口实现的关键步骤以及通信应用场景等。

绝对式编码器是一种用于测量旋转角度的装置,它可以提供高分辨率的角度测量精度。

在工业自动化、机械加工等领域中广泛应用。

FPGA是一种重构可编程逻辑门阵列,可以根据用户需求重构硬件逻辑。

ARM则是一种广泛应用于嵌入式系统的处理器架构,如ARM Cortex-M系列。

通信原理:FPGA与ARM的通信基于串行通信协议,一般采用SPI(串行外围接口)或I2C(串行总线)协议。

这两种协议在通信速率、传输距离等方面有所不同,可以根据具体需求进行选择。

接口实现步骤:1.确定通信协议:根据系统需求和绝对式编码器的通信规范,选择合适的通信协议。

2.硬件连接:连接FPGA与ARM的通信接口,一般是通过引脚连接或者片上总线连接。

3.编写通信驱动程序:在ARM上编写通信驱动程序,包括发送和接收数据的函数。

4. FPGA逻辑设计:使用VHDL或Verilog等硬件描述语言,在FPGA上实现通信接口的逻辑设计。

5.配置FPGA:将FPGA逻辑设计烧录到FPGA芯片中。

6.ARM程序使用通信接口:ARM程序通过调用通信驱动程序,与FPGA进行数据交互。

通信应用场景:1.位移测量系统:将绝对式编码器与FPGA、ARM集成,实现对位移的测量和位置控制。

2.机器人控制系统:使用绝对式编码器测量机器人关节的角度,通过FPGA和ARM进行数据处理和控制。

3.包装设备控制系统:使用绝对式编码器测量包装设备的位置和速度,通过FPGA和ARM实现位置和速度控制。

总结:基于FPGA的ARM与绝对式编码器的通信接口实现,可以实现ARM处理器与绝对式编码器之间的数据交互。

ARM与FPGA通用GPMC总线接口设计实现

ARM与FPGA通用GPMC总线接口设计实现引言:随着计算机科学的不断发展,特别是嵌入式系统的迅速发展,ARM和FPGA的结合越来越受到关注。

ARM作为一种高性能、低功耗的处理器,广泛应用于移动设备、智能家居和工业自动化等领域。

而FPGA则具有灵活可重构的特点,可以实现各种不同的数字电路和逻辑功能。

为了实现ARM与FPGA之间的通信,我们可以采用GPMC(General-Purpose Memory Controller)总线接口。

GPMC是一种高性能、灵活的AMBA(ARM Advanced Microcontroller Bus Architecture)总线接口,主要用于处理大容量主存储器和外部设备的访问。

设计思路:1.通过FPGA实现GPMC总线控制器,与ARM处理器相连。

2.根据GPMC总线协议规范,实现数据、地址、控制和时钟信号的交互。

3.通过GPMC总线控制器,实现ARM与FPGA之间的数据传输和通信。

设计细节:1.GPMC总线控制器的设计:-实现GPMC总线接口的时序控制逻辑,包括数据传输的读写控制和时钟同步。

-实现对外设的地址和数据的读写控制。

-实现GPMC总线控制器与ARM处理器的接口逻辑。

2.GPMC总线接口的数据传输:-对于数据的读取,ARM发送读命令和地址给GPMC控制器,控制器从外设读取数据,并将数据发送给ARM。

-对于数据的写入,ARM发送写命令、地址和数据给GPMC控制器,控制器将数据写入外设。

3.GPMC总线接口的时钟同步:-ARM和FPGA可能有不同的时钟频率,需要实现时钟同步。

- 可以使用FPGA中的PLL(Phase-Locked Loop)模块,将ARM的时钟频率转换为与FPGA相同的频率。

4.GPMC总线接口的地址映射:-ARM和FPGA之间的地址映射需要一致,以确保ARM访问FPGA上的正确地址。

-可以通过使用地址转换模块来实现地址映射。

5.GPMC总线接口的信号标准:-GPMC总线接口的信号标准需要符合AMBA总线接口规范。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

矿产资源开发利用方案编写内容要求及审查大纲

矿产资源开发利用方案编写内容要求及《矿产资源开发利用方案》审查大纲一、概述

㈠矿区位置、隶属关系和企业性质。

如为改扩建矿山, 应说明矿山现状、

特点及存在的主要问题。

㈡编制依据

(1简述项目前期工作进展情况及与有关方面对项目的意向性协议情况。

(2 列出开发利用方案编制所依据的主要基础性资料的名称。

如经储量管理部门认定的矿区地质勘探报告、选矿试验报告、加工利用试验报告、工程地质初评资料、矿区水文资料和供水资料等。

对改、扩建矿山应有生产实际资料, 如矿山总平面现状图、矿床开拓系统图、采场现状图和主要采选设备清单等。

二、矿产品需求现状和预测

㈠该矿产在国内需求情况和市场供应情况

1、矿产品现状及加工利用趋向。

2、国内近、远期的需求量及主要销向预测。

㈡产品价格分析

1、国内矿产品价格现状。

2、矿产品价格稳定性及变化趋势。

三、矿产资源概况

㈠矿区总体概况

1、矿区总体规划情况。

2、矿区矿产资源概况。

3、该设计与矿区总体开发的关系。

㈡该设计项目的资源概况

1、矿床地质及构造特征。

2、矿床开采技术条件及水文地质条件。