ARM与FPGA的接口实现

《ARM和FPGA协同实现高速Hadamard单像素相机的研究》范文

《ARM和FPGA协同实现高速Hadamard单像素相机的研究》篇一ARM与FPGA协同实现高速Hadamard单像素相机的研究一、引言随着科技的进步和数字成像技术的发展,单像素相机以其独特的技术优势,如高空间分辨率、高信噪比和低功耗等特性,在科研和工业应用中得到了广泛的关注。

其中,Hadamard单像素相机以其快速成像和良好的图像质量,成为了当前研究的热点。

本文将探讨如何利用ARM和FPGA的协同作用,实现高速Hadamard单像素相机的设计与应用。

二、Hadamard单像素相机技术概述Hadamard单像素相机是一种基于Hadamard变换的编码型相机。

通过与特殊的Hadamard编码/解码矩阵结合,它可以提高单像素成像的精度和速度。

由于其对光的快速处理和可编码的特点,它已广泛应用于多模式光测量系统。

三、ARM与FPGA协同设计的必要性ARM是一种广泛使用的微处理器架构,具有强大的控制能力和灵活的扩展性。

而FPGA(现场可编程门阵列)则具有强大的并行处理能力和可定制性。

将ARM和FPGA结合起来,可以充分利用两者的优势,实现对数据的快速处理和精准控制。

对于高速Hadamard单像素相机而言,需要强大的数据传输能力和高速的处理能力,而ARM与FPGA的协同设计正是满足这一需求的最佳选择。

四、ARM与FPGA协同实现高速Hadamard单像素相机的设计1. 硬件设计:设计一个以ARM为核心的控制系统,负责整个相机的控制和数据处理。

同时,使用FPGA作为数据处理单元,实现对数据的快速处理。

通过ARM与FPGA的高速通信接口,实现数据的快速传输。

2. 软件设计:在ARM端设计一个主控制器程序,实现对整个系统的控制和监控。

在FPGA端设计一个数据处理解码器程序,利用Hadamard变换对接收到的数据进行处理和解码。

通过主控制器与数据处理解码器的协同工作,实现对数据的快速处理和高质量成像。

五、实验结果与分析通过实验验证了ARM与FPGA协同实现高速Hadamard单像素相机的可行性和有效性。

fpga arm联合原理

fpga arm联合原理FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,而ARM(Advanced RISC Machines)则是一种基于精简指令集(RISC)的处理器架构。

本文将探讨FPGA和ARM的联合原理,即在FPGA中实现ARM处理器的设计和应用。

我们来了解一下FPGA。

FPGA是一种可编程逻辑器件,可以通过编程来实现不同的数字电路功能。

与传统的固定功能集成电路(ASIC)相比,FPGA具有灵活性和可重构性,能够根据需要进行重新编程,使其适用于多种应用场景。

FPGA的核心是由大量的可编程逻辑单元(CLB)和可编程互连资源(IOB)组成的,可以通过内部连接和外部引脚与其他电路元件进行通信。

而ARM是一种处理器架构,被广泛应用于各种嵌入式系统和移动设备中。

ARM处理器以其低功耗、高性能和高度灵活的特性而闻名。

ARM处理器采用了精简指令集(RISC)的设计理念,使其指令集简洁而高效,能够在有限的资源下提供强大的计算能力。

将FPGA和ARM结合起来,可以充分发挥两者的优势,实现更灵活、高性能的系统设计。

在FPGA中实现ARM处理器的设计主要通过将ARM的RTL(Register-Transfer Level)描述转化为FPGA可编程逻辑的实现方式。

具体而言,可以使用硬件描述语言(HDL)如VHDL 或Verilog来编写ARM处理器的RTL描述,然后使用FPGA开发工具将其综合为FPGA的配置文件。

在配置文件中,ARM处理器被映射到FPGA的CLB和IOB资源中,以实现ARM指令的执行和数据处理。

通过FPGA实现ARM处理器的设计具有多个优势。

首先,FPGA可以提供更大的逻辑资源和存储容量,可以容纳更复杂的ARM处理器设计和更丰富的外设接口。

其次,FPGA的可编程性使得ARM处理器可以根据需要进行灵活的配置和优化,以满足不同应用场景的需求。

此外,FPGA具有较低的功耗和较高的计算性能,可以为ARM处理器提供更好的运行环境。

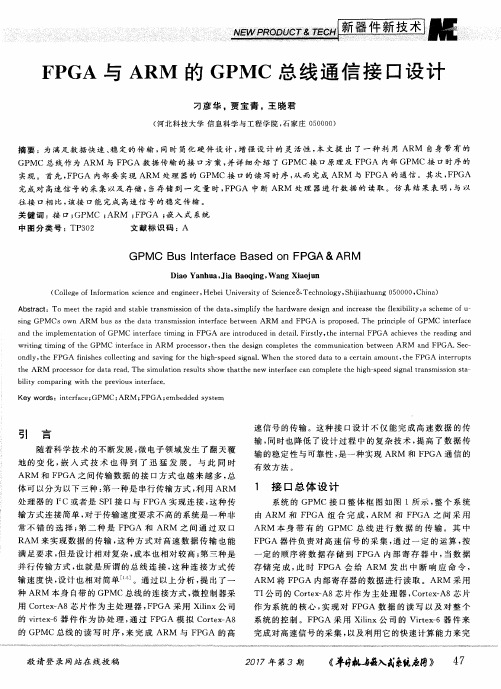

FPGA与ARM的GPMC总线通信接口设计

敬请登录网 站在线投稿

2 0 1 7 # - g 3 期

《 平 机 1 菡 } 入式豪 碗启I j 9 》

4 7

l l

|

l 。

成信 号 的 计算 , 最 重 要的 是 它本 身 灵 活 的 编程 方 式 能 很 好 地模 拟 GP MC总 线 接 口 的读 写 时 序 , 从而 实现 F P GA 和 ARM 之 间数 据 的稳 定 传 输 。

定 的顺 序 将 数 据 存 储 到 F P GA 内 部 寄 存 器 中 , 当 数 据

存储 完 成 , 此时 F P GA 会 给 AR M 发 出 中断 响应 命 令 ,

AR M将F P G A 内部 寄 存 器 的 数 据 进 行 读 取 。AR M 采 用

TI 公司的 C o r t e x - A8芯 片作 为 主 处 理 器 , C o r t e x - A8芯 片 作 为 系 统 的核 心 , 实 现对 F P GA 数 据 的 读 写 以 及 对 整 个 系 统 的 控 制 。F P GA 采 用 Xi l i n x公 司 的 Vi r t e x - 6器 件 来 完成对高速信号的采集 , 以及 利 用 它 的快 速 计 算 能 力 来 完

fpga arm联合原理

fpga arm联合原理FPGA(现场可编程门阵列)和ARM(高级微处理器)是两种常见的硬件技术,在计算机领域发挥着重要作用。

本文将探讨FPGA和ARM 的联合原理,介绍它们的基本概念、特点以及相互结合的优势。

一、FPGA的基本概念与特点FPGA是一种可编程逻辑器件,由大量的可编程逻辑单元和可编程互连资源组成。

它的主要特点是灵活性和可重构性。

与传统固定功能集成电路相比,FPGA可以根据用户的需求进行灵活的编程和配置,实现各种不同的功能。

这使得FPGA在许多领域中具有广泛的应用,如数字信号处理、通信、嵌入式系统等。

二、ARM的基本概念与特点ARM是一种基于RISC(精简指令集计算机)架构的微处理器。

它具有高性能、低功耗、可扩展性和易于设计的特点。

ARM处理器广泛应用于移动设备、嵌入式系统和智能家居等领域。

ARM架构提供了丰富的指令集和强大的软件生态系统,使得开发者可以方便地进行软件开发和调试。

三、FPGA与ARM的联合原理FPGA和ARM可以通过将ARM处理器与FPGA芯片相结合,实现更高性能和更灵活的系统设计。

具体来说,ARM处理器可以作为FPGA系统的主控制器,负责处理复杂的软件算法和任务调度。

而FPGA则可以作为ARM处理器的协处理器,负责高速的数据处理和硬件加速。

FPGA与ARM的结合可以发挥各自的优势。

ARM处理器具有强大的运算和控制能力,适合处理复杂的软件算法和任务调度。

而FPGA具有并行处理和定制化硬件加速的能力,可以实现高速的数据处理和特定功能的硬件加速。

通过将二者结合起来,可以充分发挥硬件和软件的优势,提高系统的性能和灵活性。

具体来说,FPGA和ARM可以通过总线接口进行通信。

ARM处理器可以通过总线接口向FPGA发送控制指令和数据,FPGA则可以通过总线接口将处理结果返回给ARM处理器。

这种方式可以实现高速的数据传输和灵活的任务分配,提高系统的整体性能。

在联合设计中,需要将ARM处理器的软件编程与FPGA的硬件编程相结合。

ARM与FPGA通信接口板设计.

ARM与FPGA通信接口板设计关键词:双口RAM;乒乓操作;流控机制1 概述某项目中需设计一块通信接口板,实现ARM 2440核心板和FPGA信号处理板之间的通信,因该板交换速率达到10Mbps,要求不能频繁中断ARM处理器,且具备流控机制,设计上有一定难度,基于双口RAM设计了乒乓操作机制和流控机制,有效地降低了系统负荷。

2 电路及驱动设计2.1 接口板电路设计接口板基于两片双口RAM芯片IDT CY7C007AV实现,电路示意图如图1所示。

每片CY7C007AV有8KB的存储空间,12位地址总线,8位数据总线。

为提高端口读写效率,FPGA对ARM发送时采用乒乓操作方式,ARM对FPGA发送时采用流控方式。

由于核心板扩展槽的地址总线和数据总线位宽限制,采用两片双口RAM,一片供FPGA向ARM发送数据用,另一片供ARM向FPGA发送数据用,以下分别建成上部双口RAM和下部双口RAM。

上部双口RAM分为两部分,供FPGA采用乒乓操作方式写入数据,FPGA写完上半部后通过在EINT5上产生上升沿中断通知ARM,写完下半部后通过通过在EINT6上产生上升沿中断通知ARM。

下部双口RAM供ARM向FPGA写入数据,其接线方式与上部双口RAM类似。

两块双口RAM的电路采用对称方式,其电路如图2所示。

两片双口RAM可以互换,下部双口RAM也可供FPGA写入数据,而ARM则写入上部双口RAM。

在实际测试中,两种方式均测试过。

ARM与双口RAM连接时,采用SRAM时序,为避免/减弱二次反射,ARM与总线驱动之间加33欧的串联匹配电阻,匹配电阻靠近扩展槽的近端。

FPGA端对双口RAM的读写也采用SRAM时序,在与双口RAM连接时均串了33欧姆的匹配电阻。

由于核心板上ARM处理器距离接口板较远,接近十厘米,且核心板为四层板,总线驱动能力较弱,在ARM处理器和双口RAM之间添加四片总线驱动芯片,除增加总线驱动能力外还可通过关断总线驱动芯片,避免接口板噪声干扰核心板。

基于ARM的嵌入式系统从串配置FPGA的实现

基于ARM的嵌入式系统从串配置FPGA的实现1 引言(Advanced RISC Machines)既可以认为是一个公司,也可以认为是对一类微处理器的统称,还可以认为是一项技术。

基于ARM技术的微处理器应用约占领了32位 RISC微处理器75%以上的市场份额,ARM技术正在逐步渗入到人们生活的各个方面。

到目前为止,ARM微处理器及技术已经广泛应用到各个领域,包括工业控制领域、网络应用、消费类产品、成像和平安产品等。

(Field Programmable Gate Array)是一种高密度现场可编程规律器件,其规律功能是通过把设计生成的数据文件配置到器件内部的静态配置数据存储器(SRAM)来实现的。

FPGA具有可重复编程性,能灵便实现各种规律功能。

基于SRAM工艺的FPGA具有易失性。

系统掉电以后其内部配置数据简单走失,因此需要外接ROM保存其配置数据,系统上电后必需重新配置数据才干正常工作。

目前有两种计划可以实现,一种是用法专用的PROM,以公司FPGA,XCFxx系列PROM为例,能够提供FPGA的配置时序,上电时自动加载PROM中的配置数据到FPGA的SRAM中;另一种是在含有微处理器的系统(如系统)中采纳其他非易失性存储器如E2PROM、Flash 存储配置数据,微处理器模拟FPGA的配置时序将ROM中的数据置入FPGA。

与第一种计划相比,该计划节约成本、缩小系统体积,适用于对成本和体积苛刻要求的系统。

在便携式设计中,用法嵌入式系统和FPGA实现系统功能。

嵌入式微处理器采纳Samsung公司的ARM7TDMI系列处理器S3C44BOX:FPGA采纳Xilinx公司的Spartan-3E系列XC3S100E,采纳S3C44BOX完成对XC3S100E的配置。

取得了良好效果。

第1页共5页。

基于FPGA的ARM与绝对式编码器的通信接口实现

基于FPGA的ARM与绝对式编码器的通信接口实现基于FPGA(现场可编程逻辑门阵列)的ARM(高级RISC机器)与绝对式编码器的通信接口实现,可以实现ARM处理器与外部设备的数据交互。

本文将探讨FPGA与ARM在绝对式编码器通信接口上的应用,包括通信原理、通信接口实现的关键步骤以及通信应用场景等。

绝对式编码器是一种用于测量旋转角度的装置,它可以提供高分辨率的角度测量精度。

在工业自动化、机械加工等领域中广泛应用。

FPGA是一种重构可编程逻辑门阵列,可以根据用户需求重构硬件逻辑。

ARM则是一种广泛应用于嵌入式系统的处理器架构,如ARM Cortex-M系列。

通信原理:FPGA与ARM的通信基于串行通信协议,一般采用SPI(串行外围接口)或I2C(串行总线)协议。

这两种协议在通信速率、传输距离等方面有所不同,可以根据具体需求进行选择。

接口实现步骤:1.确定通信协议:根据系统需求和绝对式编码器的通信规范,选择合适的通信协议。

2.硬件连接:连接FPGA与ARM的通信接口,一般是通过引脚连接或者片上总线连接。

3.编写通信驱动程序:在ARM上编写通信驱动程序,包括发送和接收数据的函数。

4. FPGA逻辑设计:使用VHDL或Verilog等硬件描述语言,在FPGA上实现通信接口的逻辑设计。

5.配置FPGA:将FPGA逻辑设计烧录到FPGA芯片中。

6.ARM程序使用通信接口:ARM程序通过调用通信驱动程序,与FPGA进行数据交互。

通信应用场景:1.位移测量系统:将绝对式编码器与FPGA、ARM集成,实现对位移的测量和位置控制。

2.机器人控制系统:使用绝对式编码器测量机器人关节的角度,通过FPGA和ARM进行数据处理和控制。

3.包装设备控制系统:使用绝对式编码器测量包装设备的位置和速度,通过FPGA和ARM实现位置和速度控制。

总结:基于FPGA的ARM与绝对式编码器的通信接口实现,可以实现ARM处理器与绝对式编码器之间的数据交互。

ARM与FPGA通用GPMC总线接口设计实现

ARM与FPGA通用GPMC总线接口设计实现引言:随着计算机科学的不断发展,特别是嵌入式系统的迅速发展,ARM和FPGA的结合越来越受到关注。

ARM作为一种高性能、低功耗的处理器,广泛应用于移动设备、智能家居和工业自动化等领域。

而FPGA则具有灵活可重构的特点,可以实现各种不同的数字电路和逻辑功能。

为了实现ARM与FPGA之间的通信,我们可以采用GPMC(General-Purpose Memory Controller)总线接口。

GPMC是一种高性能、灵活的AMBA(ARM Advanced Microcontroller Bus Architecture)总线接口,主要用于处理大容量主存储器和外部设备的访问。

设计思路:1.通过FPGA实现GPMC总线控制器,与ARM处理器相连。

2.根据GPMC总线协议规范,实现数据、地址、控制和时钟信号的交互。

3.通过GPMC总线控制器,实现ARM与FPGA之间的数据传输和通信。

设计细节:1.GPMC总线控制器的设计:-实现GPMC总线接口的时序控制逻辑,包括数据传输的读写控制和时钟同步。

-实现对外设的地址和数据的读写控制。

-实现GPMC总线控制器与ARM处理器的接口逻辑。

2.GPMC总线接口的数据传输:-对于数据的读取,ARM发送读命令和地址给GPMC控制器,控制器从外设读取数据,并将数据发送给ARM。

-对于数据的写入,ARM发送写命令、地址和数据给GPMC控制器,控制器将数据写入外设。

3.GPMC总线接口的时钟同步:-ARM和FPGA可能有不同的时钟频率,需要实现时钟同步。

- 可以使用FPGA中的PLL(Phase-Locked Loop)模块,将ARM的时钟频率转换为与FPGA相同的频率。

4.GPMC总线接口的地址映射:-ARM和FPGA之间的地址映射需要一致,以确保ARM访问FPGA上的正确地址。

-可以通过使用地址转换模块来实现地址映射。

5.GPMC总线接口的信号标准:-GPMC总线接口的信号标准需要符合AMBA总线接口规范。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.2 基于Altera公司的Excalibur 系列芯片实现的图像采集处理系统

4.2 基于FPGA+ARM实现的星敏感器

4.2.1 星敏感器的原理框图

星空

光学 系统

图像 传感器

信号 处理

星点 提取

星图 识别

姿态 计算

姿态

导航星库

星表/导航星

观测星图/观测星

4.2.2 星敏感器的相关技术

镜头设计 图像传感器选择 图像驱动 图像处理(星图识别)

3 SOPC开发工具及开发流程

QUARTUS II + SOPC Builder + Nios II IDE

EDK(XPS+SDK) + ISE

-参考书 《基于EDK的FPGA嵌入 式系统开发》

4 嵌入式系统应用实例

4.1 基于Altera公司的Excalibur 系列芯片的EPXA10开发板

2 FPGA的嵌入式处理器

选择软核处理器还是硬核处理器?

对处理器的性能要求不高(仅要求几个到一两百个DMIPS,采用不多的 FPGA资源就可以,则采用嵌入软核处理器是合适的选择。

需要数据、协议处理能力超过300DMIPS,且难以由多个处理器分担,则

采用1,100MIPS的高性能PowerPC嵌入硬核处理器较合适。 FPGA中嵌入的处理器应当与FPGA及其所面向的市场、应用需求相匹配。

是否需要在FPGA中嵌入处理器?

FPGA适合用于逻辑控制、接口控制、规则数据处理,设计具有复杂算 法和逻辑控制系统时,需要结合使用嵌入式处理器 对系统集成度要求较高,将处理器嵌入FPGA能最大限度地提高系统集 成度,降低系统设计复杂度,加快上市时间。 对需求变化提供较大的灵活性,在FPGA中嵌入处理器较为合适。FPGA 与芯片处理器的结合的优点是无

User Module Requiring Direct Access DualPort SRAMs

User’s Slave Module in tne FPGA

FPGA部分

4.1.2 ARM-ARM922T

工作频率最高可达200MHz; 采用5级流水线,指令执行效率更高; 提供1.1MIPS/MHz的哈佛总线结构; 支持32位ARMv4T指令集和16位Thumb扩展指令集; 支持32位AMBA总线接口,便于外部扩充; 具有全性能的内存管理单元(MMU),支持Windows CE、Linux、Palm OS等多种主流嵌入式操作系统; 具有8K的指令缓存和8K数据缓存,能实现更高效的指 令和数据处理; 支持C语言和汇编语言编程。

1 SOPC概述

传统数字系统设计:

FPGA和处理器分离; FPGA(数字系统的接口、控制、逻辑控制和复杂数字

信号处理或数据处理算法的协处理);

电路规模较大、设计复杂,功耗较高、保密性也较差。

FPGA工艺的发展使FPGA的容量愈来愈大,一款低端FPGA 就可能具有比几年前最高端FPGA更大的容量和资源。 容量的增加和性能的提升允许在FPGA内部实现硬核或软 核处理器,从而实现更高的系统集成度。

在中低性能FPGA中采用MicroBlaze、Nios/NiosII等软核处理器,

在高性能平台FPGA中采用PowerPC高性能硬核处理器。

例如采用Spartan3 FPGA中的MicroBlaze软核处理器实现中低复杂度系统控 制和低速协议处理,采用Vitex-5 FXT平台FPGA中的PowerPC440实现大批量的 数据处理和复杂的高速网络协议处理。

1 SOPC概述

SOPC具有如下特点:

1.至少包含一个嵌入式处理器内核。 2.具有一定容量的片内高速RAM。 3.具有足够的片上可编程逻辑资源。 4。具有处理器调试接口和编程接口。

2 FPGA的嵌入式处理器

各主流FPGA厂商都在FPGA产品中提供了嵌入式硬核或软 核处理器的支持

2 FPGA的嵌入式处理器-软核

2 FPGA的嵌入式处理器

FPGA中的处理资源的快速增长促进了设计方法学 的变化 从新的系统设计观点角度重新考虑嵌入式系统中 FPGA与嵌入式处理器的相互关系,可以更好地满足 复杂系统对性能、电路设计、功耗、保密性方面的 苛刻要求。 将FPGA看作数字系统集成的平台,统一考虑接口、 逻辑控制、协处理和系统控制,统一考虑硬件逻辑 处理和软件逻辑,统一考虑FPGA中的硬件开发和软 件开发,并根据系统需要做出合理的平衡。

2 FPGA的嵌入式处理器

选择通用处理器还是专用处理器?

在性能均等的情况下,采用专用处理器还是通用的ARM、PowerPC处 理器,主要取决于对工具包的支持情况和对可移植性的需求。 为有效实现与FPGA逻辑的整合,专用处理器一般需要厂商自己提供 的编译、仿真、调试工具。如果集成ARM、PowerPC等通用处理器则可 以更多地采用GCC、GDB等通用开发工具。通用处理器也具有更广泛的 开发社区支持,具有更丰富、更成熟的资源。 从可移植性的角度,通用处理器也要优于专用软核处理器。以前采 用ARM、PowerPC等外置通用处理器的系统设计可以轻松地移植到FPGA 内部的嵌入处理器。当采用FPGA的系统设计达到一定量后需转化为 ASIC时,通用嵌入处理器也更容易转化,因为大的晶元代工厂一般都 有ARM7/9、PowerPC的工艺库。

OpenRISC1200

OpenRISC1200 是OpenRISC 系列RISC 处理器内核的一员。 OpenRISC 是由OpenCores 组织负责开发和维护的,免费、 开源的RISC 处理器内核家族。OpenRISC 包括 OpenRISC1000 和OpenRISC2000 两个体系。

2 FPGA的嵌入式处理器

4.1.3 FPGA

查找表(LUT)逻辑, 乘积项(Product-Term)逻辑, 嵌入式增强型存储器, 可以嵌入大量的MegaCore、 AMPP函数和IP核, 最高工作频率可达100MHz, 非常适于片上可编程系统(SOPC)设计

4.1.4 先进的存储支持

集成了2块SRAM和1或2块DPRAM SRAM的容量为2×16Kbytes;DPRAM的容量为 1×16Kbytes SDRAM 控制器 用于控制片外单倍速(SDR 133MHz)/双倍速(DDR 266MHz) SDRAM,支持容量高达512Mbytes EBI接口 最多可外接4个存储设备,如Flash存储器、SRAM等, 总容量高达 128Mbytes

2 FPGA的嵌入式处理器 FPGA的嵌入式处理器-软核

Leon2\Leon3

Leon2\Leon3 由Jiri Gaisle 个人开发,受到欧洲航天局 工作的支持。Leon2 使用VHDL 描述,分为两个版本:标 准版和容错(Fault Tolerant)版。标准版是一种开源的软 核,使用GNU LGPL 授权协议,可以免费地应用于研究、 教学和商业目的。

4.1.7 Excalibur系列芯片的通讯方式

ARM作为AHB1总线的主控,直接访问AHB1总线的从属 资源,包括SDRAM 控制器、片上SRAM、中断控制器、 定时器等。 ARM作为AHB1总线的主控,通过AHB1-2 桥访问AHB2 总线上的从属资源,包括UART、EBI、SRAM、 Stripe-To-FPGA 桥等,同时通过Stripe-To-FPGA桥 对FPGA进行访问和控制。 FPGA通过AHB2的总线主控 FPGA-To-Stripe桥访问 AHB2总线上的从属资源,包括SRAM、SDRAM控制器、 UART等。总线仲裁确保了每一时刻只有一个总线主 控可以启动数据传输。总线译码器用来为数据传输 提供目标设备的地址和片选信号。

4.1.5 其它嵌入式周边外设

UART PLLs Timer 中断控制器

Watchdog Timer

4.1.6 Excalibur系列芯片支持引导方式

Flash引导配置:将设计下载到片外Flash Memory中,设计

中必须包含对ARM的应用。启动时需要系统引导ARM启动,这个任务 由下载到Flash中Bootloader文件来完成。然后ARM为主动,初始化 各种寄存器、划分地址空间以及配置FPGA逻辑。最后将程序代码段 拷贝到SRAM或SDRAM中,开始执行用户代码。 E2PROM引导配置:将设计下载到片外E2PROM中,设计中可以 只包含FPGA部分的应用。启动时FPGA为主动,初始化各种寄存器、 划分地址空间以及配置FPGA逻辑,这时ARM处于复位状态。配置完 成后,如果有对ARM的应用,则ARM解除复位,开始执行E2PROM中的 用户代码。反之,ARM一直处于复位状态。 直接配置芯片:将设计通过下载线直接对芯片进行引导配置, 将用户代码下载到片内SRAM中,配置完成直接运行。以这种方式配 置的芯片,掉电数据就会丢失。(开发调试阶段常用)

4.2 基于Altera公司的Excalibur 系列芯片实现的图像采集处理系统

4.2 基于Altera公司的Excalibur 系列芯片实现的图像采集处理系统

数据存储模块 SDRAM 程序存储模块 1-Flash

程序存储模块 2-EEPOM

UART 接口模块 EPXA10/EPXA1 (内嵌ARM核的FPGA芯片) JTAG 下载线

AHB2

Master Slave

FPGA -ToStripe Bridge

DualPort SRAM0

Port A

SinglePort SRAM0

Port B

StripeToFPGA Bridge

Slave Master

AHB Master Port

AHB Slave Port

FPGA Master(s)

SDR/DDR SDRAM