一种图像处理算法FPGA开发平台的系统设计

基于FPGA的双通道实时图像处理系统

p o e sn d l s i lme td tr u h Ve i g HDL.e e d d DS a d c r n o Ip o e s r T e e . r c s i g mo u e i mpe ne h o g rl o mb d e P h r — o e a d Nis I r c so h x

第2 3卷 第 8期 21 0 0年 8月

传 感 技 术 学 报

C N S O HI E E J UR NA E OR ND A T L OF S NS S A C UA OR T S

V0 _ 3 No. l2 8 Au . 2 0 g 01

Du lCh n e m a e Re lTi e Pr c s i g S se s d o a - a n lI g a — m o e sn y t m Ba e n FPGA

视频 线 送 至 A V 10完成 视 频 解码 , 像处 理模 块 通 过 V ro 语 言 、 D 78 图 ei g l 内嵌 D P硬核 以及 No 处 理 器 予 以 实现 。实 验表 明 , S i I sI

系统实时性强、 图像处理效果 良好 , 并具有成本低 、 设计简单 、 应用灵活等特点 。

,

.

h g o t ih c s ,

i a e u t s fr s u c sa d dfiu tt sg _ PGA +DS due a d s n o e u 1c a n l ma e r . n d q ae u e o e o r e n i c l ode in frF f 0 P mo l e i f w d a . h n e g e g n i a -i r c si g s se i o o e lt me p o e sn y tm sprp s d.Th y tm a e n F e s se tk s a PGA hp a e r c s o c pu e vde ma e b c i s k y p o e s r a tr i o i g y

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

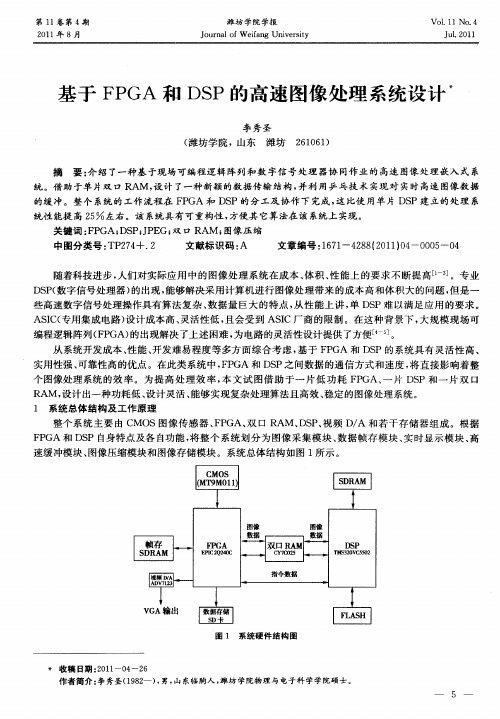

基于FPGA和DSP的高速图像处理系统设计

的缓 冲 。整 个 系统的 工作 流 程 在 F GA 和 D P的分 工 及协 作 下 完成 , 比使 用单 片 DS P S 这 P建 立 的处 理 系

统性 能提 高 2 左右 。该 系统 具 有可重 构性 , 5 方便 其 它算 法在该 系统上 实现 。

关键 词 : P F GA; S J E 双 口 RAM ; D P;P G; 图像 压 缩

第 1 卷 第 4期 1

21 0 1年 8月

潍 坊 学 院 学报

J u n l fW efn ie st o r a ia g Unv r i o y

V0 . 1N0 4 11 .

J 12 1 u. 0 1

基 于 F GA 和 DS P P的 高 速 图 像 处 理 系 统设 计

确 的配置之后 , 就可 以输 出 1 的图像数据 和一些 同步信 号 。在本系统 中采用 I O位 z C实现 传感 器配 置 ,P F— G 管脚通 过模拟 IC时序 , A 。 完成 对 C MOS 感器 的初始 化配置 , 中要 配置 的寄存 器如表 1 传 其 所示 。

表 1 MT M0 9 1寄存 器 设 置

编程逻 辑 阵列 ( P F GA) 出现解 决 了上 述 困难 , 电路 的灵活 性设 计提 供 了方便 [ 。 的 为 4 ]

从 系 统开发 成本 、 能 、 性 开发难 易程 度等 多方 面综 合考 虑 , 基于 F G 和 D P的系 统具 有 灵 活性 高 、 P A S 实用性 强 、 可靠性 高 的优 点 。在此类 系 统 中 ,P F GA和 DS P之 间 数据 的通 信 方式 和速 度 , 直 接影 响着 整 将 个 图像 处理 系统 的效 率 。为 提 高 处 理 效 率 , 文 试 图 借 助 于 一 片 低 功耗 F GA、 片 D P和 一 片 双 口 本 P 一 S

图像缩放算法的研究与FPGA设计

whole structure of scaler is designed starting、析m the analysis of scaling core.It also

brings up a new optimized algorithm···-·-window scaling algorithm on the base of research in the classical image scaling algorithm and then simplifies the calculation tlexity.In FPGA implementation,our design separates the

下面对几种平板显示技术的基本特征进行概述,以比较异同及发展前景。 1.液晶显示技术(LCD,Liquid Crystal Display) LCD有“第二半导体”的称谓,它具有低工作电压、功耗小、重量轻、厚度 薄、长寿命、无电磁辐射、不耀眼、抗干扰性好、抗震性能好、有效显示面积大、 适于大规模集成电路直接驱动、易于实现全彩色显示等优良特色。 液晶显示器件利用了液晶晶体各向异性产生光电效应的物理特性:在通电导 通后排列有序,使光线容易通过;不通电时排列混乱,阻止光线通过。液晶显示 技术经历了扭曲向歹IJ【121(TN.LCD)、超扭曲向列‘131(STN.LCD)和薄膜晶体管

design of scaler and implements its verification in FPGA.Our scaler is able to support scaling operation to images with different resolution in adjustable modes.Besides,it

基于FPGA和DSP架构的红外图像实时处理系统设计

Ke y wor : FPG A; ds DS P; ma e p o e ห้องสมุดไป่ตู้n ;i f a e i g r c s ig n r r d

处理 的各 个领 域 ,相 关 的 图像处 理 算法 复杂 灵

活 、数 据 处 理 量大 。因 此 ,图像 处 理 硬 件 系 统 要

求具 有运 行复 杂灵 活算 法 的能 力 ,以保 证 实现

系统 的 实时性 。半导 体 制造 工 艺 的快速 发 展 以

收 稿 日期 :2 1— 82 02 0 3

0 引 言

图 像 处 理 技 术 已 经 被 广 泛 应 用 于 视 频 图 像

及 计算 机体 系结构 的进一 步 改进 ,使得 数 字信 号 处理器 (i tl i a P oe osD P ) Dg a S n l rcs r, S s 芯片 的 i g s

功能变得越来越 强大;同时, 其数 字器件特有 的 稳定性、可重复性 以及可 大规模集成 的特点 , 也 使得信号 处理 的手 段变得更 加灵 活 [ 。 自从 2 0 世纪 8 0年代 初 D P 投入市 场 以来 ,实时 D P Ss S

数据采 集、数据处理和 数据传输 的并行化 。实验结果表 明,该方 案设计合理 、可行 ,具

有 较高 的工程 实用价值 。

关 键 词 :F GA ; D P; 图像 处 理 ;红 外 P S 中 图分 类 号 : T 1 . 文 献 标 识 码 : A DOI 1. 6/.s.6288 . 1.1. 6 N917 3 : 03 9jsn17—752 2 00 9 i 0 0 0

ISP系统设计及FPGA硬件实现的开题报告

ISP系统设计及FPGA硬件实现的开题报告

【目的】

本文旨在介绍一种设计和实现ISP系统的方案,该系统可以在FPGA 上实现硬件加速和快速图像处理。

【背景】

ISP系统是一种用于数字图像处理的系统。

它可以进行多种图像处理操作,例如去噪、变形、增强、降噪等。

常见的ISP系统包含编解码器、降噪滤波器、色彩空间转换器等。

FPGA是一种可编程逻辑器件,具有高度的定制能力。

它可以用于加速处理器或实现硬件加速模块,从而提高系统性能。

【方案】

本文将设计一个基于FPGA的ISP系统,其中包含以下模块:

- 传感器接口:用于读取图像传感器中的原始数据。

- 预处理模块:对原始数据进行预处理,例如降噪、增强等。

- 编码器:将处理后的数据进行压缩编码。

- 降噪滤波器:对编码后的数据进行降噪处理。

- 色彩空间转换器:将降噪后的数据转换到目标色彩空间。

- 存储器:存储处理后的数据。

除此之外,我们还将在FPGA上实现硬件加速模块,例如引用域滤

波器、多级二次插值算法等。

【预期成果】

- 实现基于FPGA的ISP系统设计。

- 测试和评估硬件加速模块的性能和效率。

- 对系统的性能和功耗进行分析和优化。

【结论】

本文将会实现一种基于FPGA的ISP系统设计,该系统具有较高的性能和灵活性,并实现硬件加速模块,从而提高系统的速度和效率。

该系统在数字图像处理领域具有广泛的应用前景。

基于FPGA和DSP的高速图像处理系统

基于FPGA和DSP的高速图像处理系统作者:舒志猛陈素华来源:《现代电子技术》2012年第04期摘要:为了提高图像处理系统的高性能和低功耗,提出了一种基于FPGA和DSP协同作业的高速图像处理嵌入式系统,其中DSP为主处理器,负责图像处理,而FPGA为协处理器,负责系统的所有数字逻辑。

整个系统中FPGA和DSP的工作之间形成流水,同时借助于单片双口RAM()完成两者的通信,比使用单片DSP建立的处理系统性能提高25%左右。

该系统具有可重构性,方便其他的算法于该系统上实现。

关键词:图像处理; FPGA; DSP;双口RAM中图分类号:; TP274+.2文献标识码:A文章编号:(1. Xuji Metering Limited Company, Xuchang 461000, China;2. College of Electrical & Information Engineering, Xuchang University, Xuchang 461000, China)Abstract: In order to improve the performance of image processing embedded system and reduce its powerpaper. DSP as a main processor is used to control the module of image process, and FPGA chip as aration in the system is divided between the FPGA and DSP in the form of the pipelined, the performance of the system is 25% higher than that of the processing system based on the single DSP. The system is easy to transplant other algorithms into it due to its reconfigurability.Keywords:收稿日期:引言现阶段用于数字图像处理的系统有很多种,而从成本、性能、开发难易程度等多方面的考虑,基于FPGA和DSP的灵活性高、实用性强、可靠性高的图像压缩系统脱颖而出。

基于FPGA的图像处理探究

隹Isl^iSls V12021年第03期(总第219期)基于FPGA的图像处理探究王建,赵红霞(运城职业技术学院,山西运城044000)摘要:随着图像处理的数量的增大和图形处理算法复杂度变高,图像处理实时性就变得十分重要。

为了解决图像处理中数据实时性问题,文章基于FPGA的图像处理进行分析,文章基于边缘检测算法和滤波算法,选择以Sobel算子对图像进行预处理,并选择Matlab软件对算法进行仿真,研究算法的可行性。

实验表明文章提出的基于FPGA的图像处理系统具有良好的边缘检测效果,能够实现数据处理实时要求。

关键词:图像处理;FPGA;边缘检测;中值滤波中图分类号:TP391文献标识码:B文章编号:2096-9759(2021)03-0079-03在图像处理的数量的增多,以及图形处理算法复杂度日益变高的背景下,针对图像处理实时处理难度将越来越高。

结合国内外学者研究的文献,主要集中了图像处理算法的研究层面上,关于选择具体的处理器和仿真软件两者融合进行研究的文献较少。

因此,本文基于FPGA对图像进行处理,釆用边缘检测和滤波算法,以Sobel算子对图像进行实时处理,从而满足图像处理时间和速度的要求,结合仿真结果验证本次设计的实用性,从而说明本研究实际意义。

1边缘检测和Sobel算法、中值滤波理论分析在实际生活中,边缘是指两个灰度值在相差较大的相邻区域当中,具体表现为特征不连续性。

通常用导数函数变化收稿日期:2020-12-29图2两种过滤方法实验结果对比图由图2中的四组曲线对两种过滤方法的拟合优度和误判率分别进行分析。

首先,针对拟合度优度指数分析得出,本文过滤方法的拟合度和传统过滤方法的拟合度在整体上註的差异性较小,数值基本接近,但仍然能够看出本文过滤方法的拟合优度指数更高,由本文上述计算可知,拟合优度指数数值越高,则说明过滤的精度越高。

因此,证明本文提出的异常信息流过滤方法与传统过滤方法相比,在实际应用中的过滤精度更高。

一种基于FPGA的红外图像预处理算法的实现

始 图像 数 据 , 过 b x滤 波 模块 处 理 后 有 3种 不 同 的 滤 波 结 果 ; 经 o 滤波 后 的数 据 进 行 融 合 处 理 , 后 进 过 二值 化 的分 割 处 理 , 出候 选 然 突 目标 ; 制 电 路 控 制 着 各 个 模 块 流 程 的 操 作 。 控 1 . 分 辨 率模 块 1降

进不 同 而 已 。

11 .. 2结构 框 图 和说 明

量 和 实时 性 分 析 。 实验 证 明 , 预 处理 算 法在 F G 上 的 实现 完全 满 足 实 时处 理 的 需求 , 该 P A 并达 到各 项性 能指 标 。

关 键 词 : 字 图 像 处 理 ; 处 理 :P 数 预 F GA ; 波 ; 时 性 滤 实 中 图 分 类 号 : P3 1 T 0 文献标识码 : A 文 章 编 号 : 0 9 3 4 (0 1 1 — 9 3 2 1 0 - 0 42 1 ) 6 3 4 —0

算 法 的 实 现 , 过 在 F G 内部 搭 建 滤 波 器 结 构 来 独 立 完 成 预 处 理 工 作 , 验 证 明 该 方 法 能够 对 采 集 图像 进 行 实 时 的 处 理 并 达 到 通 PA 实

预期 指标 , 同时 对 于 F G 内部 资 源 的消 耗 也在 合 理 范 同之 内 。 PA

在 图像 处 理 系统 结 构 中 . 像 预 处 理 算 法 通 常 在 整 个 核 心 算 法 的最 前 端 。 各 种 传 感 器 在 获 取 真 实 世 界 的 场 景 时 , 于 内部 A 图 由 D 转换 器 本 身 存 在 的量 化 误 差 , 可 避 免 的造 成 图 像 失 真 , 时 , 字 图像 在 传 输 过 程 中也 会 受 到 各 种 噪 声 的 干 扰 , 致 最 终 获取 的 不 同 数 导 数 字 图像 和 真 实场 景 有 较 大 区别 , 类 现 象 在 红 外 图像 的 获 取 过 程 中尤 其 严 重 。 因 此 直 接 在 红 外 图像 上进 行 诸 如 目标 识 别 、 析 、 此 分

基于DSP和FPGA架构的嵌入式图像处理系统设计

Vo .9 11 No.2 2

电 子 设 计 工 程

E e to i sg n i e r g l cr n c De in E gn e i n

2 1 年 1 月 01 1

NO . 0 1 V 2 1

基亏 DS P和 F GA 架构 的嵌入 式图像处 理 系统设计 P

关 键 词 : S ; P A; 入 式 ;图像 处 理 D P FG 嵌

中图 分 类 号 : P 1 . T 3 74

文献标识 码 : A

文 章 编 号 :17 — 2 6 2 1 )2 0 2 — 4 64 6 3 (0 12 — 0 1 0

Em b d e a e p o e sn y t m e in b s d o P a d FP e d d i g r c si g s se d sg a e n DS n GA m

F G 架 构 的 嵌 入 式 图像 处 理 系统 , PA 简要 介 绍 了 系统 的 工 作 原 理 , 细介 绍 了 系统 硬 件 设 计 方 案 和 具 体 的 电路 组 成 , 详

并针对 F G P A程 序 处 理 的 难 点和 解 决 办法进 行 了说 明 , 出 了时序 仿 真 波 形 , 后 利 用 目标 复 原 算 法对 系统加 以验 证 。 给 最

p n il fsse i to u e re y n ytm ad r einsh mea dmae a i ut r rs ne emli i r cpeo tm si rd c db f ,a ds s y n i l e h rwaed sg c e n tr l r iyaepe e tdi d t i cc r n n