集成电路CMOS试题库

芯片设计基础知识题库50道及答案

芯片设计基础知识题库50道及答案1. 数字集成电路中最基本的逻辑门是:A. 与门B. 或门C. 非门D. 异或门答案:C2. 下列哪种电路可以实现逻辑“与”功能?A. 与门B. 或门C. 非门D. 异或门答案:A3. 在CMOS电路中,N沟道MOSFET的漏极电压VDS 与栅极电压VGS的关系是:A. VDS随VGS增大而增大B. VDS随VGS增大而减小C. VDS与VGS无关D. VDS随VGS增大而先增大后减小答案:A4. 在数字电路中,以下哪个参数表示信号在传输过程中的延迟?A. 延迟时间B. 上升时间C. 下降时间D. 幅度答案:A5. 在CMOS电路中,以下哪种器件的开关速度快?A. N沟道MOSFETB. P沟道MOSFETC. 双极型晶体管D. 漏极跟随器答案:A二、填空题6. 数字电路中的基本逻辑门包括:______、______、______。

答案:与门、或门、非门7. CMOS电路由______和______两种器件组成。

答案:N沟道MOSFET、P沟道MOSFET8. 信号的上升时间是指信号从______到______所需的时间。

答案:10%幅度、90%幅度9. 信号的下降时间是指信号从______到______所需的时间。

答案:90%幅度、10%幅度三、判断题10. CMOS电路的功耗比双极型电路低。

(正确)11. 逻辑门电路的输出电平越高,电路的驱动能力越强。

(正确)12. 信号在传输过程中的延迟与传输距离无关。

(错误)四、简答题13. 简述CMOS电路的工作原理。

答案:CMOS电路由N沟道MOSFET和P沟道MOSFET 组成,当输入信号为高电平时,N沟道MOSFET导通,P 沟道MOSFET截止,电路输出低电平;当输入信号为低电平时,N沟道MOSFET截止,P沟道MOSFET导通,电路输出高电平。

14. 简述数字电路中信号传输的延迟因素。

答案:信号传输的延迟主要受以下几个因素影响:电路结构、传输距离、信号频率、电路器件特性等。

整理版 集成电路 题目

一、填空1、 CMOS 逻辑电路中 NMOS 管是增强型,PMOS 管是增强型; NMOS 管的体端接地 ,PMOS 管的体端接VDD 。

2、 CMOS 逻辑电路的功耗由 3 部分组成,分别是 动态功耗 、开关过程中的短路功耗和 静态功耗 ;增大器件的阈值 电压有利于减小短路功耗和静态 功耗。

3、饱和负载 NMOS 反相器的 3 个主要缺点是: 输出高电平有阈值损失 、 输出低电平不是 0,与比例因子 Kr 相关 、输出低电平时有静态功耗 。

4、 三态输出电路的 3 种输出状态是: ( 高电平 ) ,( 低电平 )和( 高阻态 ) 。

2、CMOS 工艺可分为 p 阱 、 n 阱 、 双阱 三种。

在CMOS 工艺中,N 阱里形成的晶体管是PMOS3、通常情况下,在IC 中各晶体管之间是由 场氧 来隔离的;该区域的形成用到的制造工艺是 氧化 工艺。

4、集成电路制造过程中,把掩膜上的图形转换成晶圆上器件结构一道工序是指 光刻 ,包括 晶圆涂光刻胶 、 曝光 、 显影 、 烘干 四个步骤;其中曝光方式包括 ① 接触式 、② 非接触式 两种。

5、阈值电压VT 是指 将栅极下面的si 表面从P 型Si 变成N 型Si 所必要的电压,根据阈值电压的不同,常把MOS 区间分成 耗尽型 、 增强型 两种。

降低VT 的措施包括: 降低杂质浓度 、 增大Cox 两种。

1.写出传输门电路主要的三种类型和他们的缺点:(1)NMOS 传输门,缺点:不能正确传输高电平 ; (2)PMOS 传输门,缺点:不能正确传输低电平; (3)CMOS 传输门,缺点:电路规模较大。

2、对于一般的动态逻辑电路,逻辑部分由输出低电平的 NMOS 网组成,输出信号与电源之间插入了栅控制极为时钟信号的 PMOS ,逻辑网与地之间插入了栅控制极为时钟信号的 NMOS二、简答题1. 为什么的PMOS 尺寸通常比NMOS 的尺寸大?答:1)电子迁移率较大,是空穴迁移率的两倍,即μN =2μP 。

CMOS集成电路设计答案

2.5)a) λ=0.1,γ=0.45, 2F Φ=0.9, THD V =0.7x GS V V -=3 ,x DS V V -=3 , x SB V V =F SB F THO TH V V V ϕϕγ22(-++= So, ()()x x x ox n x V V V LWC I -+-+---=31))9.09.0(45.07.03(212λμThe above equation is valid for()09.09.045.07.03>-+---x x V V, ie 297.1<x VSo ,()()x x x ox n x V V V LW C I 1.03.19.045.0727.2212-+--=μAnd 0=x Ifor x V <97.1x ox n D oxn m I LW C I L W C g μμ22==2.5)b)0==γλ7.0=TH Vfor 10<<x V , S and D exchange theirroles.x GS V V -=9.1x DS V V -=1 x BD V V -=2.1()()()⎥⎦⎤⎢⎣⎡--⨯⨯--=-x V V L WC I V x x ox n x 12122.121μ ()()x x ox n x V V LWC I ---=4.1121μ()x ox n DS ox n m V LWC V L W C g -•=1μμ (absalutate value)The above equations are valid for 1<x VThen the direction of current is reversed.9.019.1=-=GS V1-=x DS V V 2.07.09.0=-=DB Vfor2.1<x V , device operates in the triode region .()()⎥⎦⎤⎢⎣⎡---⨯⨯=2112.0221x x ox n x V V L WC I μ ()1-=x ox n m V LWC g μfor 2.1>x V , device goes into saturation again .So ,()22.021LWC I ox n x μ=()2.0LWC g oxn m μ=2.5)c)0==γλ7.0=TH VS and D exchange their roles .x GS V V -=1 x DS V V -=9.1 x TH GS BD V V V V -=-=3.0Device is in saturation region , so 2)3.0(21x ox n x V LWC I --=μDevice turns off when 3.0=x Vand never turns on again .So ,2)3.0(21x ox n x V LWC I --=μ ; x<0.30=x I;otherwiseThen , )3.0(x oxn m V LWC g --=μ ; x<0.32.5)d)8.0-=TH V0=γD and S exchange their roles9.0-=GS V9.1-=x DS V Vfor 8.1<x V ; 2)1.0(21LWC I ox n x μ-=)1.0(LWC g ox n m μ-=Deviceremains in the saturation region until8.11.09.1=-=x V, then device goes into the triode region .for 9.18.1<<x V : ])9.1(21)9.1)(1.0[(2-----=x x ox n x V V L W C I μ)9.1(-=x ox n m V L W C g μfor 9.1>xV: S and D exchange their roles again,when 9.1=x Vfor 9.1>x V ,device operates into the triode regionx GS V V -=1 x DS V V -=9.1])9.1(21)9.1)(8.1[(2x x x oxn x V V V L W C I ----=μ)9.1(x ox n m V LW C g --=μSo , 8.10<<x V : )1.0(221ox n x C I μ-=)1.0(LWC g oxn m μ-= 38.1<<x V:)7.1)(9.1(21--=V V LWC I x ox n x μ)9.1(-=x ox n m V LWC g μ2.5)e)7.0=THO V45.0=γ 9.02=F φ 0=λx SB V V -=1)9.019.0(45.07.0--++=x TH V V9.0=GS V 5.0=DS Vfor 0=x V , 893.0=TH V so device is in saturation region.so 2)]9.09.1(45.02.0[21---=x ox n x V LWC I μ)]9.09.1(45.02.0[---=x ox n m V LWC g μthese equations are valid upon the edge of triode region,i.e.5.0)9.09.1(45.02.0=---x V ⇒82.1=x VAbove 82.1=x V ,device is in the triode region.]5.0))9.09.1(45.02.0(5.02[212----⨯⨯=x ox n x V LWC I μ)5.0(LWC g ox n m μ=;This problem has been considered only for 9.10<<x V inwhich schich-Hodges E9. is valid forTHV .2.7)a⇒0==γλ 7.0=TH VD and S exchange their roles for 7.00<<in Vdevice is off 0=out Vfor7.17.0<<in V device is in the saturation region21)7.0(21--==out in ox n out D V V LWC R V I μfor 33.1<<in V device is in the triode regionout in GS V V V -=out DSV V -=1])1()1)(7.0(2[2121out out out in ox n out D V V V V LWC R V I -----==μ2.7)b0==λγ7.0=TH V⇒D and S exchange their rolesfor3.10<<in Vdevice is in triodeout GS V V -=2out in DS V V V -=])())(7.02(2[2121out in out in out ox n out D V V V V V LWC R V I -----==μfor 33.1<<in V device is in the saturation region21)7.02(21--==out ox n out D V LWC R V I μout Vdoesn’t depend on in V and it is consfant for 3.1>inV2.7)c0==λγ7.0=TH Vfor3.20<<inV device is in triodeout GS V V -=3out in DS V V V -=])())(7.03(2[2121out in out in out ox n out D V V V V V LWC R V I -----==μfor33.2<<in V device is in the satution region21)7.03(21--==out ox n out D V LWC R V I μout Vis constant for 3.2>in V(it doesn’t depend on in V )2.7)d8.0=TH V0==λγfor8.10<<in Vdevice is off ⇒ 0=out Vthen device turns on andoutV goes up until8.1=out V ,then device enters triode regionfor 8.1>in V and 8.1<out V21)8.1(21-==in ox n out D V L WC R V I μ⇒21)8.1(21-=in ox n out V LWR C V μThis is good for 128.128.1R LW C V ox n inμ⨯<<for 128.12R LW C V ox n inμ⨯>])())(8.1(2[2121out in out in in ox n out D V V V V V LWC R V I ----==μNow by subsfifufly 01V ,02V and x V in ①and ②we have:{0)2)(11()11)(2(0301=•-+++-++++oc D mb m P in m o P D od oc V R r r g g R V g V R R V V{0)2)(1()11)(2(03020=•-++-++-oc Dmb m in m D od oc V R r r g g V g r R V Vor:0)111(21)]2)(11(111[100300=+•+++•++++++in m od P D oc D mb m D P D V g V r R R V R r g g r R r R R ③0)11(21)]2)(1(11[200300=++-++++in m od D oc D mb m D V g V r R V R r r g g r R ⑨From equation ③ and ⑨ od V and oc Vcan be solued in farmsof 1in V and 2in V. Now if 0==γλ,we have:⑤{0)(01101=-+-+P xx in m D R V V V V g R V {0)(202=-+x in m DV V g R V ⇒ Dm in xR g V V V 022+= {00201=-V V , 0201V V V out -= ⇒201outV V =202outV V -=⑤⇒ 02222221=+-++-+Dm P outP in P out D out in m in m D out R g R V R V R V R V V g V g R V Pin in in m D P m P D out R V V V g R R g R R V 221)()2111(+--=+++2221212in in in in in V V V V V --+=⇒ Pin in in in P m P D m P D out R V V V V R g R R g R R V 2))(21()21211(2121++-+-=++)22](2))(21([2121P D m P D Pin in in in P m out R R g R R R V V V V R g V ∥∥++-+-= 212121+=+=m P PP m g R R R g CMRR)22)(1(P D m P D Pm dm dm R R g R R R g A ∥∥+-=-PPD m P D dm cm R R R g R R A 22∥∥-=-5.9)a5.9)b5.9)c 5.9)d 5.9)e6.9)a(i)at low fraguency , x V is like virtual groundout in V SC V SC 21-=21C CV V in out -= (ii) At high fraguency, the quiralent circuit∞→-=)(03011r r g A m V ∥ if0=λ6.9)c(i) At low frequancy , the equivalent circuitThe impedance @ 31m out g V =31311m m m m V g g g g A -=•-≅ (ii) at high frequency21m m in x g gV V -=▁ the inpedance looking into x V The inpedance @ 21R R V out ∥=)()()1(21121221R R g R R g g g A m m m m V ∥∥-=•••-= 6.9)d(i) at low frequancy ,the equivalent circuit is∞→+≅++=12020********)(1)])1([m m m xm x m m in out g g r r g Z g Z g r g V V ∥∥ if 0=λmx g Z 1=KCL @ x V ,out V :)()(033022r VV g r V V V V g R V out x m x out x in m P x +-=-+-= ⇒)1(303Pm x out R g r V V +-= P x x out x in m R V r V V V V g =-+-022)( ⇒ 022022)11(r Vout V g r R V g x m P in m +++= ⇒ out Pm m P in m V r R g r g r R V g ]1)1(1)11([022032022++++-= ⇒∞→+-+++-=)1()11()1(302032023032Pm m P Pm m inoutR g r r g r R R g r g V V if 0=λgiven mA I SS 1= , mA I I D D 5.0129=- 5.0100)(129=-L W (a) V n mk LW C I V V ox D TH GS 289.0])32.0100)(6.383100()5.0(2[])(2[21219999=⨯==-μ⇒ V V GS 089.19= V V V V GS DD CM y x 911.19,,=-= (b) V V swing x 2.0= , V V CM y x 911.1,,=V V x 011.2max ,= V V x 811.1m in ,=495.02011.232max,57=-=-==x DD OD OD V V V V 7055.024.0811.12min ,31=-=-==SSI x OD OD V V V V 02.97)495.02.41)(495.0)(886.3)(100()5.0(2)1()(2)(285=⨯+=+-=-n mA V V V C I L WDS TH GS ox P D offλμ m m L W off μμ1.3105.3102.9785≈=⨯=-14)7055.01.01)(7055.0)(6.383)(350()5.0(2)1()(2)(241=⨯+=+-=-n mA V V V C I L WDS TH GS ox n D offλμ m W μ8.441≅-(c) )()(01109907055010331r r g r r g r r g g A m m m m V ∥∥= 111417.17055.0)5.0(22-Ω==-=m mA V V I g TH GS D m113417.1-Ω==m g g m m155022.2495.0)5.0(22-Ω==-=m mA V V I g THP GS D m1946.3289.0)5.0(2-Ω==m mA g mΩ======k mA I r r r r D on 20)5.0)(1.0(110110301λ Ω====•=k mA I r r r r D op 10)5.0)(2.0(11090705λ )2010(46.3]1010022.22020417.1)[417.1(k k m k k m k k m m A V ∥∥⨯⨯⨯⨯⨯⨯= 4871=V AAssuming all transistors are in saturation, we have12223)(2)(2TH ox n outTH ox n outout V LW C I V LW C I R I +=++μμ When we have assumed 34)()(LW L W = and 0=λ Thus , 2212])()([1LWL W R C I Sox n out -=μWhen the circuit turns on , inifically both M5 and H6 are off and x V andy V rise together,i.e.,y x V V =. When y V reaches 6TH V , x V is also near 5TH V .Thus,M6 and H5 turn on almost simultanecusly . The surge in the drain current ef M5 turns the rest of the circuit on .As y V increases further, x V begins to drop if M6 is turned on sidffreiently became the voltage gain of H6 and b R exceels unity. For high value of y V , x V can be lower than 5TH V . Since 6626)()(D ox n TH a D DD I LWC V R I V =•-•-μ , we solve the quadratic equatiom:0)(])(1)(2[266262=-++--TH DD ox n TH DD a D D aV V LW C V V R I I R μ⇒2222662)(4])(1)(2[)(1)(2aTH DD aox n TH DD a ox n TH DD a D R V V R LW C V V R LW C V V R I --+-++-=μμThis value is substifuted in the other condition:56)(TH b a D DD V R R I V ≤+-To give the condition for furning off H5.。

试题标准答案模版A4-数字集成电路设计A答案[1]

![试题标准答案模版A4-数字集成电路设计A答案[1]](https://img.taocdn.com/s3/m/b1c5702d0b1c59eef9c7b432.png)

3考虑图3,

a.下面的CMOS晶体管网络实现什么逻辑功能?反相器的NMOS W/L=4,

PMOS W/L=8时输出电阻相同,根据这个确定该网络中各个器件尺寸。

b.最初的输入模式是什么,必须采用哪一种输入才能取得最大传输延时?

考虑在内部节点中的电容的影响。(给出分析过程)

图3

b. 放电——>充电;为了使延时最小,放电过程要求所有的内部电容全部放电,因此ABCDE=10101;充电过程要求所有的内部电容充电,因此ABCDE=10100;

5简述静态CMOS电路的优缺点。

答:静态CMOS电路在电源的两条轨线之间电压的摆幅,即VOH=VDD,VOL=GND。由于上拉和下拉网络是互斥网络,因此电路没有静态功耗。但存在有两个主要问题:一是有N个输入的门uyao晶体管数目为2N个,大大增加了它的实现面积;二是静态CMOS门的传播延时随扇入数的增加而迅速增加。

解:1)

2.将每道大题得分和总分填入得分栏中。

R=30kΩ,

假设晶体管处于线性区。

证明该晶体管处于线性区。

四、设计题(共30分,每题10分)

1.使用互补CMOS电路实现逻辑表达式 ,当反相器的NMOS W/L=2, PMOS W/L=4时输出电阻相同,根据这个确定该网络中各个器件尺寸。

三、计算题(共25分,第一题10分,第二题15分)

1.已知集成电路中Al1层参数如下:单位长度电容120aF/um;单位长度电阻0.065Ω/um。计算在该层长为12cm的导线传播延时。为减小此导线的传播延时将此导线3等分并插入2个传播延时为80ps的反相器,计算在这种情况下各层上整个导线的传播延时。

共页第页

说明:1。标准答案务必要正确无误。

络为对偶网络。

数字集成电路--电路、系统与设计(第二版)课后练习题 第六章 CMOS组合逻辑门的设计

Chapter 6 Problem Set

Chapter 6 PROBLEMS

1. [E, None, 4.2] Implement the equation X = ((A + B) (C + D + E) + F) G using complementary CMOS. Size the devices so that the output resistance is the same as that of an inverter with an NMOS W/L = 2 and PMOS W/L = 6. Which input pattern(s) would give the worst and best equivalent pull-up or pull-down resistance? Implement the following expression in a full static CMOS logic fashion using no more than 10 transistors: Y = (A ⋅ B) + (A ⋅ C ⋅ E) + (D ⋅ E) + (D ⋅ C ⋅ B) 3. Consider the circuit of Figure 6.1.

2

VDD E 6 A A 6 B 6 C 6 D 6 E F A B C D 4 4 4 4 E 1 A B C D 4 4 4 4 E 1 6 F 6 B 6 C 6 D

Chapter 6 Problem Set

VDD 6

Circuit A

Circuit B

Figure 6.2 Two static CMOS gates.

扎维模拟CMOS集成电路设计第四章习题

I SS 1103 0.72V 4 0.383510 50 W p Cox L 3

Vout max 3 0.72 2.28V Vout , swing 2Vout max Vout min 22.28 0.673 3.214 V

Chapter 4 习题

4.11

Cox

0 ox

tox

8.851014 F / cm 3.9 7 2 3 . 835 10 F / cm 9 109 m

cm2 F 4 A nCox 350 3.835107 1 . 34225 10 V s cm2 V2 cm2 F 4 A pCox 100 3.835107 0 . 3835 10 V s cm2 V2

b. VDD 0.8V时,M 3截止,Vout 0, AV 0 VDD 0.8V时,M 3导通,M1工作在线性区,VDD ,Vout , AV 当VDD 上升到一定值时,M1进入饱和区。

VinCM 1.2V时,满足M1工作在饱和区的最小电 源电压为 VDD min VinCM VTH 1 VGS 3 1.2 0.7 1.607 2.107V

2 I D1 VGS 1 Vod 1 VTH 1 0.7 W nCox L 1 2 0.25103 0.7 0.893 V 4 1.3422510 100

VinCM min VodSS VGS 1 0.273 0.893 1.166 V

a. VinCMmin VodSS VGS1 VinCMmax VDD VGS3 VTH1

Razavi《模拟CMOS集成电路设计》习题答案精编版

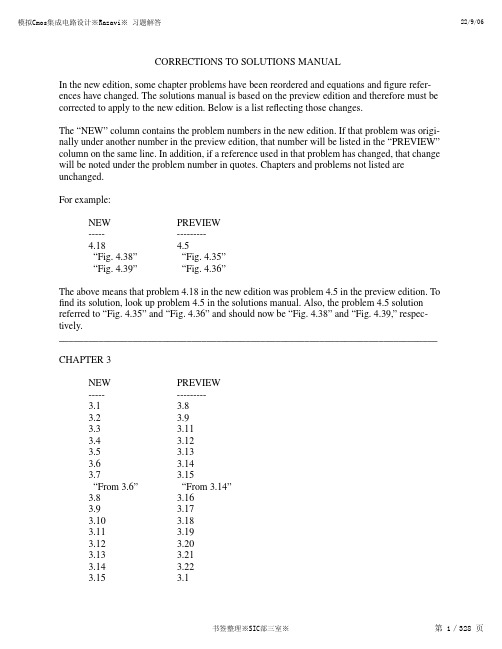

CORRECTIONS TO SOLUTIONS MANUALIn the new edition, some chapter problems have been reordered and equations and figure refer-ences have changed. The solutions manual is based on the preview edition and therefore must be corrected to apply to the new edition. Below is a list reflecting those changes.The “NEW” column contains the problem numbers in the new edition. If that problem was origi-nally under another number in the preview edition,that number will be listed in the“PREVIEW”column on the same line.In addition,if a reference used in that problem has changed,that change will be noted under the problem number in quotes. Chapters and problems not listed are unchanged.For example:NEW PREVIEW--------------4.18 4.5“Fig. 4.38” “Fig. 4.35”“Fig. 4.39” “Fig. 4.36”The above means that problem4.18in the new edition was problem4.5in the preview edition.To find its solution, look up problem 4.5 in the solutions manual. Also, the problem 4.5 solution referred to “Fig. 4.35” and “Fig. 4.36” and should now be “Fig. 4.38” and “Fig. 4.39,” respec-tively._____________________________________________________________________________ CHAPTER 3NEW PREVIEW--------------3.1 3.83.2 3.93.3 3.113.4 3.123.5 3.133.6 3.143.7 3.15“From 3.6” “From 3.14”3.8 3.163.9 3.173.10 3.183.11 3.193.12 3.203.13 3.213.14 3.223.15 3.13.16 3.23.17 3.2’3.18 3.33.19 3.43.20 3.53.21 3.63.22 3.73.23 3.103.24 3.233.25 3.243.26 3.253.27 3.263.28 3.273.29 3.28 CHAPTER 4NEW PREVIEW--------------4.1 4.124.2 4.134.3 4.144.4 4.154.5 4.164.6 4.174.7 4.18“p. 4.6” “p. 4.17”4.8 4.194.9 4.204.10 4.214.11 4.224.12 4.234.13 4.24“p. 4.9” “p. 4.20”4.14 4.1“(4.52)” “(4.51)”“(4.53)” “(4.52)”4.15 4.24.16 4.34.17 4.44.18 4.5“Fig. 4.38” “Fig. 4.35”“Fig. 4.39” “Fig. 4.36”4.19 4.6“Fig 4.39(c)” “Fig 4.36(c)”4.20 4.74.21 4.84.22 4.94.23 4.104.24 4.114.25 4.254.26 4.26“p. 4.9” “p. 4.20”CHAPTER 5NEW PREVIEW--------------5.1 5.165.2 5.175.3 5.185.4 5.195.5 5.205.6 5.215.7 5.225.8 5.235.9 5.15.10 5.25.11 5.35.12 5.45.13 5.55.14 5.65.15 5.75.16 5.85.17 5.95.18 5.10“Similar to 5.18(a)” “Similar to 5.10(a)”5.19 5.115.20 5.125.21 5.135.22 5.145.23 5.15CHAPTER 6NEW PREVIEW--------------6.1 6.76.2 6.86.3 6.9“from eq(6.23)” “from eq(6.20)”6.4 6.106.5 6.11“eq (6.52)” “eq (6.49)”6.6 6.16.7 6.26.8 6.36.9 6.46.10 6.56.11 6.66.13 6.13“eq (6.56)” “eq (6.53)”“problem 3” “problem 9”6.16 6.16“to (6.23) & (6.80)” “to (6.20) & (6.76)”6.17 6.17“equation (6.23)” “equation (6.20)”CHAPTER 7NEW PREVIEW--------------7.27.2“eqn. (7.59)” “eqn. (7.57)”7.177.17“eqn. (7.59)” “eqn. (7.57)7.197.19“eqns 7.66 and 7.67” “eqns 7.60 and 7.61”7.217.21“eqn. 7.66” “eqn. 7.60”7.227.22“eqns 7.70 and 7.71” “eqns. 7.64 and 7.65”7.237.23“eqn. 7.71” “eqn. 7.65”7.247.24“eqn 7.79” “eqn 7.73”CHAPTER 8NEW PREVIEW--------------8.18.58.28.68.38.78.48.88.58.98.68.108.78.118.88.18.98.28.108.38.118.48.138.13“problem 8.5” “problem 8.9”CHAPTER 13NEW PREVIEW--------------3.17 3.17“Eq. (3.123)” “Eq. (3.119)”CHAPTER 14 - New Chapter, “Oscillators”CHAPTER 15 - New Chapter, “Phase-Locked Loops”CHAPTER 16 - Was Chapter 14 in Preview Ed.Change all chapter references in solutions manual from 14 to 16. CHAPTER 17 - Was Chapter 15 in Preview Ed.Change all chapter references in solutions manual from 15 to 17. CHAPTER 18 - Was Chapter 16 in Preview Ed.NEW PREVIEW--------------18.316.3“Fig. 18.12(c)” “Fig. 16.13(c)”18.816.8“Fig. 18.33(a,b,c,d)” “Fig. 16.34(a,b,c,d)”Also, change all chapter references from 16 to 18.。

集成电路试题库

集成电路试题库(总49页) -本页仅作为预览文档封面,使用时请删除本页-半导体集成电路典型试题绪论1、什么叫半导体集成电路?【答案:】通过一系列的加工工艺,将晶体管,二极管等有源器件和电阻,电容等无源元件,按一定电路互连。

集成在一块半导体基片上。

封装在一个外壳内,执行特定的电路或系统功能。

2、按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写【答案:】小规模集成电路(SSI),中规模集成电路(MSI),大规模集成电路(VSI),超大规模集成电路(VLSI),特大规模集成电路(ULSI),巨大规模集成电路(GSI)3、按照器件类型分,半导体集成电路分为哪几类?【答案:】双极型(BJT)集成电路,单极型(MOS)集成电路,Bi-CMOS型集成电路。

4、按电路功能或信号类型分,半导体集成电路分为哪几类?【答案:】数字集成电路,模拟集成电路,数模混合集成电路。

5、什么是特征尺寸它对集成电路工艺有何影响【答案:】集成电路中半导体器件的最小尺寸如MOSFET的最小沟道长度。

是衡量集成电路加工和设计水平的重要标志。

它的减小使得芯片集成度的直接提高。

6、名词解释:集成度、wafer size、die size、摩尔定律?【答案:】7、分析下面的电路,指出它完成的逻辑功能,说明它和一般动态组合逻辑电路的不同,分析它的工作原理。

【答案:】该电路可以完成NAND逻辑。

与一般动态组合逻辑电路相比,它增加了一个MOS管M kp,它可以解决一般动态组合逻辑电路存在的电荷分配的问题。

对于一般的动态组合逻辑电路,在评估阶段,A=“H” B=“L”, 电荷被OUT处和A处的电荷分配,整体的阈值下降,可能导致OUT的输出错误。

该电路增加了一个MOS管M kp,在预充电阶段,M kp导通,对C点充电到V dd。

在评估阶段,M kp截至,不影响电路的正常输出。

8、延迟时间【答案:】时钟沿与输出端之间的延迟第1章集成电路的基本制造工艺1、四层三结的结构的双极型晶体管中隐埋层的作用【答案:】减小集电极串联电阻,减小寄生PNP管的影响2、在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响【答案:】电阻率过大将增大集电极串联电阻,扩大饱和压降,若过小耐压低,结电容增大,且外延时下推大3、简单叙述一下pn结隔离的NPN晶体管的光刻步骤【答案:】第一次光刻:N+隐埋层扩散孔光刻第二次光刻:P隔离扩散孔光刻第三次光刻:P型基区扩散孔光刻第四次光刻:N+发射区扩散孔光刻第五次光刻:引线孔光刻第六次光刻:反刻铝4、简述硅栅p阱CMOS的光刻步骤【答案:】P阱光刻,光刻有源区,光刻多晶硅,P+区光刻,N+区光刻,光刻接触孔,光刻铝线5、以p阱CMOS工艺为基础的BiCMOS的有哪些不足【答案:】NPN晶体管电流增益小,集电极串联电阻大,NPN管的C极只能接固定电位6、以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法【答案:】首先NPN具有较薄的基区,提高了其性能:N阱使得NPN管C极与衬底断开,可根据电路需要接任意电位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、选择题 Moore在1965年预言:每个芯片上晶体管的数目将每个月翻一番。 (B)

2.MOS管的小信号输出电阻是由MOS管的效应产生的。 (C) A.体 B.衬偏 C.沟长调制 D.亚阈值导通 3.在CMOS模拟集成电路设计中,我们一般让MOS管工作在区。 (D) A.亚阈值区 B.深三极管区 C.三极管区 D.饱和区 管一旦出现现象,此时的MOS管将进入饱和区。 (A) A.夹断 B.反型 C.导电 D.耗尽 5.表征了MOS器件的灵敏度。 (C) A.or B.bmg C.mg D.oxncu 6.Cascode放大器中两个相同的NMOS管具有不相同的。 (B) A.or B.bmg C.mg D.oxncu 7.基本差分对电路中对共模增益影响最显著的因素是。 (C) A.尾电流源的小信号输出阻抗为有限值 B.负载不匹配 C.输入MOS不匹配 D.电路制造中的误差 8.下列电路不能能使用半边电路法计算差模增益。 ( C ) A.二极管负载差分放大器 B.电流源负载差分放大器 C.有源电流镜差分放大器 负载Casocde差分放大器 9.镜像电流源一般要求相同的。 ( D ) A.制造工艺 B.器件宽长比 C.器件宽度W D.器件长度L 10. NMOS管的导电沟道中依靠导电。 ( ) A.电子 B.空穴 C.正电荷 D.负电荷 11.下列结构中密勒效应最大的是。 (A) A.共源级放大器 B.源级跟随 器 C.共栅级放大器 D.共源共栅级放大器 12.在NMOS中,若0Vsb会使阈值电。 (A) A.增大 B.不变 C.减小 D.可大可小 13. 模拟集成电路设计中可使用大信号分析方法的是。 (C) A.增益 B.输出电阻 C.输出摆幅 D.输入电阻 14. 模拟集成电路设计中可使用小信号分析方法的是。 (A) A.增益 B.电压净空 C.输出摆幅 D.输入偏置 15. 下图中,其中电压放大器的增益为-A,假定该放大器为理想放大器。请计算该 电路的等效输入电阻为。 ()

第15题 A. AR1 B.AR11 )1(AR. )11(AR 16.不能直接工作的共源极放大器是共源极放大器。 (C) A.电阻负载 B.二极管连接负载 C.电流源负载 D.二极管和电流源并联负载 17.模拟集成电路设计中的最后一步是。 (B) A.电路设计 B.版图设计 C.规格定义 D.电路结构选 择 18.在当今的集成电路制造工艺中,工艺制造的IC在功耗方面具有最大的优势。 (B)

管的导电沟道中依靠导电。 (B) B.电子 B.空穴 C.正电荷 D.负电荷 20.电阻负载共源级放大器中,下列措施不能提高放大器小信号增益的是。 (D) A.增大器件宽长比 B.增大负载电阻 C.降低输入信号直流电平 D.增大器件的沟道长度L 21. 下列不是基本差分对电路中尾电流的作用的是。 (D) A.为放大器管提供固定偏置 B.为放大管提供电流通路 C.减小放大器的共模增益 D.提高放大器的增益 22.共源共栅放大器结构的一个重要特性就是输出阻抗。 (D) A.低 B.一般 C.高 D.很高 23. MOS管的漏源电流受栅源过驱动电压控制,我们定义来表示电压转换电流的能力。 (A) A.跨导 B.受控电流源 C.跨阻 D.小信号增益 管漏电流的变化量除以栅源电压的变化量是。 (C) A.电导 B.电阻 C.跨导 D.跨阻 25.随着微电子工艺水平提高,特征尺寸不断减小,这时电路的工作电压会( D) A.不断提高 B.不变 C.可大可小 D.不断降低 26.工作在饱和区的MOS管,可以被看作是一个。 (B) A.恒压源 B.电压控制电流源 C.恒流源 D.电流控制电压源 27.模拟集成电路设计中的第一步是。 (C) A.电路设计 B.版图设计 C.规格定义 D.电路结构选择 管中,如果VB变得更负,则耗尽层。 (C) A.不变 B.变得更窄 C.变得更宽 D.几乎不变 29.模拟集成电路设计中的最后一步是。 (B) A.电路设计 B.版图设计 C.规格定义 D.电路结构选择

30. 不能直接工作的共源极放大器是( C )共源极放大器。

A.电阻负载 B.二极管连接负载 C.电流源负载 D.二极管和电流源并联负载 31.采用二极管连接的CMOS,因漏极和栅极电势相同,这时晶体管总是工作在 。 ( ) A.线性区 B.饱和区 C.截止区 D.亚阈值区 32.对于MOS管,当W/L保持不变时,MOS管的跨导随过驱动电压的变化 是 。 ( ) A.单调增加 B.单调减小 C.开口向上的抛物线 D.开口向下的抛物线 33.对于MOS器件,器件如果进入三极管区(线性区), 跨导将 。 ( ) A.增加 B.减少 C.不变 D.可能增加也可能减小 34. 采用PMOS二极管连接方式做负载的NMOS共源放大器,下面说法正确的是 。 ( ) A. PMOS和NMOS都存在体效应,电压放大系数与NMOS和PMOS的宽长比有关 。 B. PMOS和NMOS都存在体效应,电压放大系数与NMOS和PMOS的宽长比无关。 C. PMOS和NMOS 不存在体效应,电压放大系数与NMOS和PMOS的宽长比无 关 。 D. PMOS和NMOS不存在体效应,电压放大系数与NMOS和PMOS的宽长比有关 。 35. 在W/L保持不变的情况下,跨导随过驱动电压和漏电流变化的关系是 ( ) A.跨导随过驱动电压增大而增大,跨导随漏电流增大而增大。 B. 跨导随过驱动电压增大而增大,跨导随漏电流增大而减小。 C. 跨导随过驱动电压增大而减小,跨导随漏电流增大而增大。 D. 跨导随过驱动电压增大而减小,跨导随漏电流增大而减小。 36.和共源极放大器相比较, 共源共栅放大器的密勒效应要 。 ( ) A.小得多 B.相当 C.大得多 D.不确定 37. MOSFETs的阈值电压具有 温度特性。 ( ) A . 零 B. 负 C. 正 D. 可正可负。 38.在差分电路中, 可采用恒流源替换”长尾”电阻. 这时要求替换”长尾”的恒流源的输出电阻 。 ( ) A.越高越好 B.越低越好 C. 没有要求 D. 可高可低 器件中,保持VDS不变,随着VGS的增加,MOS器件 。 ( ) A. 从饱和区——>线性区——>截止区 B. 从饱和区——>截止区——>线性区 C. 从截止区——>饱和区——>线性区 D. 从截止区——>线性区——>饱和区 40.对于共源共栅放大电路, 如果考虑器件的衬底偏置效应, 则电压增益会( )A.增大 B.不变 C.减小 D.可能增大也可能减小 41.在当今的集成电路制造工艺中, 工艺制造的IC在功耗方面具有最大的优势。 ( )

42. 保证沟道宽度不变的情况下,采用电流源负载的共源级为了提高电压增益,可以 。 ( ) A. 减小放大管的沟道长度,减小负载管的沟道长度; B. 减小放大管的沟道长度,增加负载管的沟道长度; C. 增加放大管的沟道长度,减小负载管的沟道长度; D. 增加放大管的沟道长度,增加负载管的沟道长度。 43. 随着微电子工艺水平提高,特征尺寸不断减小,这时电路的工作电压会

。 ( ) A.不断提高 B.不变 C.可大可小 D.不断降低 44. NMOS管中,如果VB电压变得更负,则耗尽层 。 ( ) A.不变 B.变得更窄 C.变得更宽 D.几乎不变

45. 在CMOS差分输入级中, 下面的做法哪个对减小输入失调电压有利

( )

A.减小有源负载管的宽长比 B.提高静态工作电流. C.减小差分对管的沟道长度和宽度 D.提高器件的开启(阈值)电压 二、简答题 1.CMOS模拟集成电路中,PMOS管的衬底应该如何连接为什么(5分) 解:在CMOS工艺中,由于PMOS管做在N型的“局部衬底”也就是N阱里面,因此PMOS管的局部衬底接局部高电位。 2. 什么是N阱(5分) 解:CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,若衬底为P型,则PMOS管要做在一个N型的“局部衬底”上,这块与衬底掺杂类型相反的N型“局部衬底”叫做N阱。 3.解释什么叫沟道长度调制效应(5分) 解:MOS晶体管存在速度饱和效应。器件工作时,当漏源电压增大时,实际的反型层沟道长度逐渐减小,即沟道长度是漏源电压的函数,这一效应称为“沟道长度调制效应” 4.何谓MOS管的跨导写出NMOS管在不同工作区域中的跨导表达式。(10分) 解:漏电流的变化量除以栅源电压的变化量称之为跨导。

放大区: 饱和区: 截止区:电流为0无跨导 设计常用软件有哪些(10分) 解:Cadence、Mentor Graphics和Synopsys 模拟集成电路中,NMOS管的衬底应该如何连接为什么(5分) 解:NMOS衬底接最低电位;目的是为了让衬底PN结反偏,限制载流子只在沟道里流动。 7.简单说明模拟集成电路芯片一般的设计流程。(5分) 8.何谓MOS管的跨导写出PMOS管在不同工作区域中的跨导表达式。(10分) 解:漏电流的变化量除以栅源电压的变化量称之为跨导。

放大区:gm=μp 饱和区;