AND-XOR Network Synthesis (2008)

KEYWORDS

KEYWORDSVHDL, Optimization, Simulation ABSTRACTThis paper proposes a new method to speedup si-mulation of VHDL models. Therefore, a tool na-med ATOMS (Automatic Optimization of VHDL Models for Simulation) reads in a VHDL source model and generates automatically a new optimized VHDL model which is simulated fa-ster by the same simulator. ATOMS arises out of an approach to speedup simulation of a RISC computer system running its operating system. The CPU is modeled near gate level to calculate the rate of gate level faults covered by pin level faults. This is performed by software based fault injection experiments.ATOMS achieves the speedup by reducing the number of processes and signals of the source model. The lower the abstraction level of the VHDL source model the higher is the speedup of the simulation. Though, optimizing gate level models promises the most efficient speedup. The average speedup of the simulation is measured to 5-8, the best measured speedup was 20. INTRODUCTIONVHDL models of contemporary systems are as complex as the system itself. Synthesis of gate le-vel models ends in a very complex network of lo-gic gates, flipflops and latches. Simulating these gate level models requires a lot of CPU time. E.g. for a simulation interval of 1 ms the VHDL simu-lator needs 2.5 hours CPU time to simulate a VHDL model of a MVME188 32 bit RISC sy-stem (Motorola INC. 1992), although only the CPU, an M88000, is modeled near gate level and the periphery is modeled at an abstract behaviou-ral level. The target machine simulating the MVME188 is a SPARCstation LX running the Modeltech VHDL-Simulator.Efforts analyzing performance of simulation of VHDL models started with Hueber 1991. Levia O. 1991 and Bonomo et al. 1992 show, how to write VHDL models which can be simulated ef-ficiently. This paper introduces ATOMS, a tool which optimizes VHDL models automatically. The paper is divided into three further sections. The following section describes two tasks a VHDL simulator has to deal with and how the CPU time is split to these tasks. Based on this re-sult optimization methods are presented.The next section presents the implementation of ATOMS. The stages starting from reading in the VHDL source model and specifying the entity and architecture to optimize till the output of the automatically optimized model are explained. Finally, the conclusion summarizes the most im-portant results and the section future research ex-plains what else can be done to speedup simulati-on.OPTIMIZATION METHODSCPU time used for simulation of VHDL models can be split into two parts. The time needed toATOMS - A Tool for Automatic Optimization of Gate Level VHDL Models for SimulationOliver Tschäche and Volkmar SiehDepartment of Computer Science IIIUniversity of Erlangen-NürnbergMartensstr.391058 Erlangen, GermanyEmail: {ortschae,vrsieh}@rmatik.uni-erlangen.deschedule processes and to switch between pro-cesses and the rest of CPU time which is used to execute the statements of the processes, doing the actual behaviour. Considering the VHDL model of an logic NAND gate with two inputs in figure 1, gate level models consist of many signals and processes and very few statements in the proces-ses, one bold printed statement in figure 1.Figure 1: VHDL model of a NAND gateTo calculate the CPU time used for execution of the statements, the VHDL model in figure 2 is si-mulated with num =1 and num =2 . The difference of the measured CPU times of the simulations is the time needed to process the inner for-loop (1000 additions). Running the Modeltech VHDL simulator on an SPARCstation LX, this time is 6.8s-3.9s=2.9s. The times are measured by using the UNIX command time which runs the simula-tor in batch mode.Figure 2: VHDL model to estimate time ofstatement executionENTITY nand2 IS PORT(i0,i1 : IN bit;o : OUT bit);END nand2;ARCHITECTURE behaviour OF nand2 IS BEGINPROCESS( i0,i1) BEGIN o <= i0 NAND i1;END PROCESS;END behaviour;ENTITY perf_calc ISGENERIC( num : integer );END perf_calc;ARCHITECTURE behaviour OF perf_calc IS SIGNAL o : integer;BEGINPROCESSVARIABLE c,d,e : integer;BEGINFOR c IN 1 TO num LOOP e:=0;FOR d IN 1 TO 1000 LOOP e := e + d;END LOOP;END LOOP;o <= e;WAIT FOR 10 ns;END PROCESS;END behaviour;Starting the simulator and loading the VHDL model needs 0.2s. Thus, the CPU time spent for scheduling is 3.9s-2.9s-0.2s=0.8s. Assuming that a logic expression like AND, OR, XOR, and so on is calculated as fast as an addition by the simu-lating machine the CPU time for processing simple statements like that of the NAND2 ex-ample is about 2.9s/1000=2.9ms. Thus, the CPU time used to schedule processes amounts to less than 0.4% (2.9ms/0.8s) of the CPU time needed for simulation. Because of the higher number of processes and signals in a gate level model the CPU time used by the scheduler constitutes more than 99.6%. Because of this portion of CPU time used for scheduling reducing the number of pro-cesses and signals promises the best reduction of CPU time.A very simple method to reduce the number of processes is to search for flipflops which are trig-gered by the same event. For example, a 32 bit re-gister consists of 32 single bit flipflops and so 32processes in a gate level model. The statements of these processes can be collected in one single process. For three flipflops collected in one pro-cess the CPU time is 86% of the original model.Another way to reduce the number of processes and signals of the VHDL source model is to se-arch for connected combinational processes. A combinational process describes a combinational circuit like an AND gate, multiplexer or decoder.These components have no internal state unlike a flipflop or latch. Combinational processes can be collected in one single processes, if they are con-nected with signals and if they are feed-forward.To generate the correct logic function it is neces-sary to sort the statements of the combinational processes in the way the signals flow through them. This optimization method eliminates hazards and spikes, since the sorting of processes excludes delta cycles. An example for this me-thod is shown in figure 3.The speedup of this method is presented by an example of adders of different bit length. The ad-ders are implemented as ripple carry adders built up from full adders which are modeled in one process. Thus, a 16 bit adder consists of 16 pro-cesses. Optimization of all adder models results in a model with one single process. For lengths of 1 to 32 bits (processes) the CPU time used forsimulating the source and optimized VHDL mo-dels is measured. To this end, input vectors of the adders are stimulated with different wave tables changing their value in cycles of 100 ns:•counter stimulus: the bits of the input vectors of the adders are concatenated to one vector. The number represented by this vector is incremented by 1 each cycle.•random stimulus: the bits of the input vector are changed randomly each cycle.Figure 3: combinational optimizationThe diagram in figure 4 shows the speedup for the different number of processes of the VHDL source model. For the counter stimulus the opti-ENTITY xor2 ISPORT(i0,i1 : IN bit;o : OUT bit);END xor2;ARCHITECUTRE gateOF xor2 IS SIGNAL ii0,ii1 : bit;SIGNAL m1,m2 : bit;BEGINinv_i0 : nand2PORT MAP(i0,i0,o=>ii0);inv_i1 : nand2PORT MAP(i1,i1,o=>ii1);gen_m1 : nand2PORT MAP(i0,ii1,m1);gen_m2 : nand2PORT MAP(ii0,i1,m2);gen_result : nand2PORT MAP(m1,m2,o);END gate;xor2ARCHITECTURE optimized OF xor2 IS BEGINPROCESS( i0,i1 )VARIABLE ii0,ii1,m1,m2 : bit;BEGINii0 := i0 NAND i0;ii1 := i1 NAND i1;m1 := i0 NAND ii1;m2 := ii0 NAND i1;o <= m1 NAND m2;END PROCESS;END optimizedmized model for less processes is simulated fa-ster than the original. Then, starting at 7 proces-ses it is simulated slower. The optimized model is slower because the stimulus activates less than two processes per cycle independent to the length of an adder. Thus, the statements of two proces-ses are to be processed. The process of the opti-mized model processes the statements of all bits.Starting at seven processes it is faster to schedule the processes and process the statements of the source model than processing the statements for all bits in one process of the optimized model. If the stimuli activate a fraction of the processes of the source model like the random stimulus does the optimized model is simulated faster.Figure 4: Speedup for ripple carry addersUsing the methods of combining flipflops and building combinational blocks concurrently VHDL models can be optimized to one single process if all triggered components like flipflops are sensitive to the same trigger (clock) signal.The combination of the two methods is not imp-lemented yet.IMPLEMENTATIONContemporary models are so complex that they cannot be optimized manually because of the time needed to generate and to verify the optimi-zed model. Therefore, we searched for a way to optimize VHDL models automatically. This is achieved by ATOMS.ATOMS is developed in an UNIX environment.It is started with two parameters. The first para-meter is the name of the entity and the second the510.581624322randomcounternumber of processess p e e d u pname of the appendant architecture which is to be optimize. In addition to the command line para-meters ATOMS reads in a configuration file in which the user has to write the names of the VHDL source files. Then, ATOMS processes the VHDL source model in three stages:1.Reading the VHDL source2.Analysation of VHDL source3.Opimization and outputThe last stage puts out the optimized VHDL mo-del, an architecture named ’optimized’. This ar-chitecture consists of signal declarations and the processes generated by the optimization stage. There are no component instantiations in the op-timized architecture.ATOMS supports different levels of VHDL sub-sets in different stages. In the stage reading VHDL source and transforming it into a syntax tree ATOMS supports the ’93 VHDL standard. The next stages only support VHDL elements used by the VHDL model of the MVME188 sy-stem. The VHDL feature of resolved signals is not implemented yet.The first stage of ATOMS processes the VHDL source in two moduls. The load module reads all files pointed to by the configuration file and con-verts them into a syntax tree. The load module consists of the lexical and grammatical descripti-on. To achieve best portability the GNU tools Flex and Bison are used to produce C modules of these descriptions which are derived from the ALLIANCE CAD toolset. The resolve module checks references to names introduced by USE-clauses and resolves them if they are valid.The next stage of ATOMS analyses the seman-tics of the VHDL source. It is divided in two mo-dules: the behavioural and structural analysis. Before the behavioural analysis all processes are explored for signals the process uses for input, output or sensitivity. Signals a process is sensitiv to are described in the process’ sensitivity list. In-put signals are the signals used in the process’statements to calculate new values at the right of variable/signal assign statements or forming con-ditions in IF- or CASE-statements. The output si-gnals of a process are the signals referenced at the left of a signal assignment expression.Behaviour analysis inspects all processes of the VHDL source in the syntax tree whether they ser-ve conditions for a combinatorical process or not. These are:•All input signals must be sensitivity signals and must be on the sensitivity list of a pro-cess. Wait statements are not allowed.•To a value variables must be assigned befo-re they are used in expressions.•IF and CASE statements must have a de-fault alternative. An IF statement musthave an ELSE alternative and a CASE sta-tement must have an WHEN OTHERS al-ternative.•All alternatives of an IF or CASE statement must assign values to exactly the same va-riables and signals.If a process meets all of these conditions it is combinatorical. If only one of these conditions do not meet the process is assumed to be non combi-natorical.Structural analysis resolves component instantia-tions and generates a planar, non hierarchical view of the VHDL source model. Starting with the architecture which should be optimized structural analysis searches in the architecture body for processes and component instantiation statements. If a component instantiation state-ment is found the same procedure searches recur-sively in the architecture body of that component for further processes and component instantiation statements. At the end of structural analysis for each process a list with the signals connected to this process exists and for each signal a list of connected processes exists.The last stage of ATOMS does the optimization and the output of the optimized VHDL model. One optimization module searches for non com-binatorical processes which are sensitive to one single signal. Processes sensitive to the same si-gnal are combined to one process sensitive to this signal and the processes optimized in this way are removed from the list of processes.A further module of the optimizing stage sear-ches for blocks of connected combinational pro-cesses to build a single optimized process for each block. To achieve this, the signals of the first combinational process in the list of proces-ses are searched for other connected combinatio-nal processes. Then, the signals of this process are examined to which other combinational pro-cesses they are connected. Interrogation of all si-gnals of all interconnected processes results in a combinational block. Starting from the input si-gnals of this block it is searched for processes ha-ving only input signals which are input signals of the block. The output signals of these processes are added to the list of input signals and the se-arch for processes depending only on these si-gnals starts again. The sequence in which the pro-cesses are found is the same as the sequence in which the statements of the processes must be co-pied to the optimized process. Finally all proces-ses used to build the new block are removed from the list of processes.The processes left in the list cannot be optimized by the current implementation of ATOMS. To complete the optimized model they are copied unchanged.In the current implementation the optimization stage of ATOMS does not handle resolved si-gnals. Thus, only parts of MVME188 model can be optimized by ATOMS.CONCLUSIONATOMS is a tool which speeds up simulation of VHDL models of low abstraction level. For gate level models the average speedup is about 5-8.The speedup depends on the stimuli. Thus, it is possible that the optimized model is simulated slower for very special stimuli.ATOMS supports only a subset of VHDL ’93. The most important restriction is that ATOMS cannot handle resolved signals.FUTURE RESEARCHATOMS optimizes VHDL models so that the time spent for scheduling and switching proces-ses is decreased and the time spent to process the statements is increased. No efforts are made to decrease the time spent to process the statements of a process. This could be a potential place to speedup the simulation of the optimized model (Aho et al. 1996).Since ATOMS rearranges the VHDL source mo-del additional information should be generated which makes it possible to map the states of the signals from the source model to the optimized model and vice versa.REFERENCESAho, A. V.; R. Sethi and J. D. Ullman pilers.Addison-Wesley, ISBN 0-201-10088-6.Balboni, A.; P. Cavalloro; M. Mastretti; A. Bonomo; E.Paschetta; G. Buonanno; and D. Sciuto. ”A Set ofTools for VHDL-Code Quality Evaluation”,Proceedings of the 1994 VHDL-FORUM for CAD in EUROPE.Bonomo A.; P. Garino; G. Ghigo; A. Balboni; and M.Mastretti. 1992.”VHDL optimization techniques forcoding and simulation”, Technical Report, CSELTTorino.Hueber M. 1991. ”VHDL experiments on Performance”, Proceedings of the 1991 EURO-VHDL Conference. Jenn, E.; J. Arlat; M. Rimén; J. Ohlsson; and J. Karisson.1994. ”Fault Injection into VHDL Models: TheMEFISTO Tool.” In digest of papers of the 24.International Symposium on Fault-TolerantComputing (Pasadena, California, June 27-30, 1994), IEEE Computer Society, 66-75Levia, O. 1991. ”Writing High Performance VHDL Models”, Proceedings of the 1991 EURO-VHDLConference.Motorola INC. 1992.MVME188A VMEmodule RISC Microcomputer User’s Manual.Sieh V.; O. Tschäche; and F. Balbach. 1996. ”VHDL based Fault Injection with VERIFY”, internal reportUniversity of Erlangen-Nürnberg, IMMD IIITschäche O. 1996. ”Automatische Optimierung von VHDL-Modellen” (German), Diplomarbeit amLehrstuhl IMMD III der Friedrich-AlexanderUniversität Erlangen-Nürnberg, postscript versionavailable fromrmatik.uni-erlangen. de:1200/Staff/ ortschae/papers/dipl.ps。

ch4_VHDL_en

Chapter 4

VHDL

Description Style

• Structure Description: describe as logic schematic diagram(example1 & example2) • Behavior Description: describe as the behavior or function of circuit(example3 & example4)

Chapter 4

VHDL

-- Example3. VHDL Description of multiplexer 21 LIBRARY IEEE; a USE IEEE. STD_LOGIC_1164.ALL; y b ENTITY mux21 IS PORT(a,b:IN STD_LOGIC ; s:IN STD_LOGIC ; s y:OUT STD_LOGIC); END mux21; ARCHITECTURE example3 OF mux21 IS BEGIN y<=a WHEN s=„0‟ ELSE b; END ARCHITECTURE example3;

• Library – entity, architecture, package designed in advance – IEEE library – composed of packages • Package – data types, declaration, sub-program shared by other entities

Architecture ART1 OF NAND2 IS

Chapter # 3 MultiLevel Combinational Logic:3章#多级组合逻辑.ppt

AND/NOR Equivalence

A A B B A • B A+ B A • B A +B A

0 1 01 0

0

1

1

B

0 1 10 0

0

0

0

1 0 01 0

0

0

0

1 0 10 1

1

0

0

A

B

AND NOR

A B

AND

A B

NOR

It is possible to convert from networks with ANDs and ORs to networks with NANDs and NORs by introducing the appropriate inversions ("bubbles")

Time Response in Combinational Networks Gate Delays and Timing Waveforms Hazards/Glitches and How To Avoid Them

No. 3-2

Multi-Level Logic: Advantages

Chapter # 3: Multi-Level Combinational Logic

No. 3-1

Chapter Overview Multi-Level Logic Conversion to NAND-NAND and NOR-NOR Networks DeMorgan's Law and Pushing Bubbles AND-OR-Invert Building Blocks CAD Tools for Multi-Level Optimization

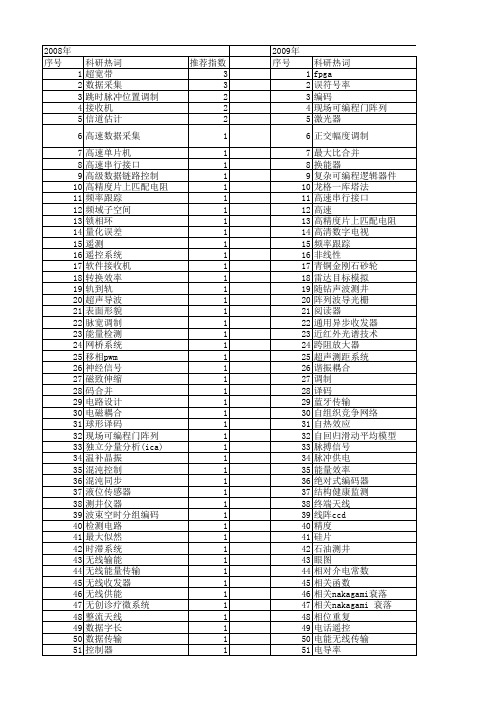

【国家自然科学基金】_接收电路_基金支持热词逐年推荐_【万方软件创新助手】_20140801

分集 全球导航卫星系统(gnss) 全球定位系统 全差分 全双工 光通信 光电集成 光电转换 光接收机 光学制造 像素补偿 修整 低成本 位置敏感器件 传递函数 传输线 传感器网络 二维瑞克接收机 串行收发器 wcdma usb2.o usb 2.0 uart stc单片机 pn序列估计 mimo雷达 flash dtmf信号 dsss/cdma信号 cpld can总线 bpi配置 arm 8051单片机

接收器 捕获跟踪 扭转弹性波 扩频通信 成型滤波器 快速傅立叶变换 微系统 微控制器 微带贴片 循环相关 并行同步捕获 平方根升余弦滚降fir滤波器 干涉条纹 嵌入式技术 射频 多用户检测 多普勒频移 多天线cdma 多传感器 复杂度 复杂可编程逻辑器件(cpld) 壁虎动物机器人 基于数字化的模拟技术 四象限光电探测器 同步数字系统 同步捕获 同步 发射电路 发射天线选择 参数自适应 压电陶瓷 卫星定位系统 单片机 功率放大电路 前置放大 分层空时码 分块传输 准正交 内插walsh序列 全球定位系统 信号处理 低压差分信号 低功耗 串行总线 usb2.0 turbo码 soc qr分解 osic nrf905 nj1030a芯片 nj1006a芯片 m元双正交键控 mmse v-balst

科研热词 推荐指数 超宽带 3 数据采集 3 跳时脉冲位置调制 2 接收机 2 信道估计 2 高速数据采集 1 高速单片机 1 高速串行接口 1 高级数据链路控制 1 高精度片上匹配电阻 1 频率跟踪 1 频域子空间 1 锁相环 1 量化误差 1 遥测 1 遥控系统 1 软件接收机 1 转换效率 1 轨到轨 1 超声导波 1 表面形貌 1 脉宽调制 1 能量检测 1 网桥系统 1 移相pwm 1 神经信号 1 磁致伸缩 1 码合并 1 电路设计 1 电磁耦合 1 球形译码 1 现场可编程门阵列 1 独立分量分析(ica) 1 温补晶振 1 混沌控制 1 混沌同步 1 液位传感器 1 测井仪器 1 波束空时分组编码(bstbc) 1 检测电路 1 最大似然 1 时滞系统 1 无线输能 1 无线能量传输 1 无线收发器 1 无线供能 1 无创诊疗微系统 1 整流天线 1 数据字长 1 数据传输 1 控制器 1 接收电路 1

ComparatorDesign5

High-speed multi-input comparatorS.-C.HsiaAbstract:A comparison cell is presented that is able to compare n -data at a time and is based on dynamic logic methodology.The results of the n -data are sent to an m -bit NAND gate for the m Ân comparison,where m corresponds to the word length of each pared to conventional comparators the proposed comparator requires fewer transistors and the circuit delay time is also shortened.To verify this comparator architecture,a 4-data Â6-bit comparator is prototyped with only 66transistors.The circuit delay time is only about 5ns using the UMC 0.5m m process.The fabricated chips have been successfully tested.Due to its regular structure,the comparison cell can be easily expanded to meet any required specification.1IntroductionCurrently cell-based VLSI design is becoming increasingly popular for system implementation since its use means that we can reduce the design cycle.In cell-based design,a circuit and its layout in a standard cell are pre-designed and stored in a cell library [1].The standard cells are generally built from basic logic cells (NAND,NOR,NOT ...),selection cells,latch cells and adder cells [2–5].Recently,computer-aided design (CAD)tools have proved to be effective in VLSI design.A logic synthesis tool has been successfully realised that is able to synthesise a gate-level circuit from cells in the cell library using HDL (high-level description language)coding [6].Most cell libraries are targeted at CMOS fabrication processes due to their high regulation and low power consumption.A circuit can be quickly synthesised from the CMOS cell library using CAD tools.Thus,we need to be able to synthesise the module of a particular function from basic cells.However,this approach can often have a poor design efficiency due to large core sizes.If a module is widely used in real systems then the circuit and layout can be pre-designed using a full-custom methodology which will allow us to minimise the chip size and improve the system performance.For example,in order to implement a module for a subtractor,the circuit is synthesised with an adder cell and a two’s complement cell.If the subtractor cell is designed with a dedicated circuit and layout,we can not only reduce the core size but also shorten the circuit delay time.However,the circuit and its layout for a dedicated cell have to be carefully created using a manual design.Thus,the design cycle will become longer since we are not able to use an automatic layout design tool.The comparison function has found application in areas such as digital signal processing and also image and voice processing [7,8].A high performance comparator is highly desirable if we are to successfully design circuits for real-time VLSI implementation.Generally speaking,compar-ison cells can be split into two types:analogue comparators;and digital comparators [9,10].An analogue comparator compares the voltages of two input signals and then decides on the output level.A digital comparator determines the output logic status by checking individual bits of the inputs.However,a conventional comparator only allows us to check two inputs.When the number of input signals is greater than two,the data are sequentially compared,i.e.the current signal is compared with the following signal which is in turn compared with the next signal.The comparator network often uses a cascade structure which increases the computing time.This kind of circuit is not applicable to high-speed systems.In this study,a dedicated comparison cell is presented that uses MOS technology for the digital circuits.A clocking charge concept will be used which will allow the proposed comparison to perform multi-input checking at various bit resolutions thereby reducing the computing time.Since the proposed comparison architecture is regular,the digital comparison cell will be able to be easily synthesised to any resolution using current synthesis tools and thereby the design cycle should be reduced.For successful operation the proposed cell should have lower complexity,lower power consumption and shorter cell delay time than currently the existing comparators.2Multi-input comparison cell designThis paper presents a digital comparator for multi-input data computing.Suppose that there are n data,and that each datum has m bits,the circuit performs the comparison function one comparison at a time using a parallel architecture.When the input bits of the data all have the same value then,the comparison circuit output logic status is high.Otherwise,the output logic status is low.2.1Conventional comparison circuitsThe basic comparison function can be implemented with a NXOR operation.The input data compare is the most significant bit (MSB)to the least significant bit (LSB)as is shown in Fig.1.The design example we are following can be found in [1].When each bit has the same level,the compared output logic status is high.For multi-data comparisons,we need to sequentially compare the bits one-by-one.Basically,this method used a cascade compar-ison.The circuit delay time becomes long and so this circuitThe author is with the Department of Computer and Communication Engineering,National Kaohsiung First University of Science and Technology,Kaohsiung 824,Taiwan,Republic of China E-mail:hsia@.twr IEE,2005IEE Proceedings online no.20041174doi:10.1049/ip-cds:20041174Paper first received 6th March 2003and in revised form 15th July 2004becomes incompartable with high-speed systems.Instead,we can design a comparison cell using NAND/NOR cells with parallel circuits.The structure is shown in Fig.2.In multi-data comparisons,the NAND and NOR gates individually check whether the m th bit of the input data has a high or low logic status.If the input bits are all high (low),the NAND (NOR)gate outputs low (high).The outputs of the NAND and the inversion of the NOR are sent to a 2-bit XOR gate.If the NOR gate output logic status is high,this denotes that the m th bits of the mutli-word are equal since all the inputs are zero.To realise such a comparison cell with a CMOS circuit and NAND and NOR gates we need 2n transistors if there are n data.Moreover the 2-bit XOR gate and the inverter gate require a further 12transistors.Thus,a total of 4n +12transistors are required to perform a 1-bit comparison.To compare an entire word,where each data has m bits we would require at least m times this number of transistors.2.2The proposed comparison cell with dynamic logicIn order to reduce the cell complexity,we now present a comparison circuit with a MOS clocking charge approach that is based on dynamic logic.Figure 3illustrates theproposed comparison cell,where the pseudo-capacitor represents the gate capacitor of the next stage input.When the clock signal (clk)is low,PMOS Q1turns on and the pseudo-capacitor is charged to V dd .In such a case,NMOS Q2turns off,so all inputs and output are isolated.When the clk signal becomes high,PMOS Q1turns off and NMOS Q2turns on.When all the input signals (a ,b ,...,n )are low,NMOS Q3to NMOS Q n all turn off,hence the capacitor voltage remains high.If all the input signals are high,then the capacitor voltage remains at a high level since there are no discharge loops.Otherwise,as the input logic is different,at least one of NMOS Q3to NMOS Q n is turned on,so the output level becomes low as the capacitor discharges via the turned on NMOS.For example,when input (a ,b ,c ,d )¼(1011),Q3is turned on,the discharge path is from Q2,Q3to b .In the same way,we check all cases where the output becomes low if the input logic levels are different.With the clock charge structure,a comparison cell only requires (n +2)transistors.Moreover,the power dissipation is very low because there are never any loops between the power and the ground.In order reduce the power dissipation further,the system can control the clock signal so that it becomes idle when the comparator is not used during a time period.Therefore,a clocking charge comparison cell is of considerable interest for application in low-power portable systems.The proposed cell can be easily expanded to meet any specification required in multi-data comparisons.If there are n data to be compared,one can check whether the m th bits of all the data are equal with the proposed comparison cell.Since the entire word has m bits,the result of each comparison cell is sent to an m -bit CMOS NAND gate,as shown in Fig.4.The clocking charge comparison cells output their results to the NAND gate.If any input bit differs then the compared result should have a logic status of low.Clearly our NAND gate outputs high if any one input is low.Also,if all the input data are equal then the expected output is high.However,CMOS NAND gate outputs is low in such a case.Therefore,an inverter cell is required to invert the logic level of the NAND output.Finally,a D-type flip-flopAB Fig.1Comparator implementation with the cascade comparisoncellcFig.2Comparison cell design using CMOS NAND and NORgatesV a b c nnFig.3Proposed comparison cell circuitV ddFig.4Enlarged comparison cell able to perform the entire m-bit word comparison(DFF)is used to latch the result with a negative edge trigger to obtain a stable logic status.Since a clocking charge comparison cell requires (n +2)transistors,the circuit needs (n +2)Âm transistors in order to compare a m -bit word length.Moreover,the CMOS NAND gate,inverter and DFF require 2m ,2and 16transistors,respectively.Thus,the total comparison circuit needs (mn +4m +18)transistors in order to compare n data with m -bit resolution.With the proposed comparison cell,the multi-input data can be compared in one go and the circuit delay time can be reduced accordingly.3Simulations and comparisonsTo realise the comparison cell,Tanner tools are used for the circuit simulation and T-Spice and L-Edit are used for the chip layout.The technology file employs the UMC 0.5m m process to map the real circuit delay.In order to verify the cell function,the prototype of a four-input comparison cell has been designed.In simulations,we employ the exhaustive test,where the input data consist of 16patterns to test each condition.The test patterns are generated like a counter from (0,0,0,0),(0,0,0,1),(0,0,1,0),(0,0,1,1),...,(1,1,1,0),(1,1,1,1).The simulated results are shown in Fig.5.The output is latched by a DFF,so there is one clock delay in the output waveform.One can see that the output is high when the inputs are either (0,0,0,0)or (1,1,1,1).The function can meet the requirements of a comparison cell.From experiments,the critical path is found in the discharge loop at the last NMOS.Clearly,the falling time is much longer than the rising time since the capacitor energy discharges though NMOS devices to the input.The input often has a large gate capacitor and so the discharge time becomes long.The maximum delay time is about 3.2ns in Fig.6,where itis measured from the discharge path,as the input signals abcd ¼{0000}-{0001}-{0000}.From simulations,the maximum frequency of this cell is a clock frequency of 1.0GHz with an input data rate of about 300MHz.However,increasing the clock frequency increases the power dissipation without producing any performance benefit.To measure the actual power dissipation,the clock frequency is set equal to the data rate.The power consumption was measured when the clock frequency and the data rate were set to 150MHz at a circuit voltage of 5thV.The power ranges from about 5Â10À4to 3.6Â10À4W,and the average power is 4.3Â10À4W.Next,the chip layout for a four-input comparison cell was designed using the L-Edit tool.The layout successfully passed LVS and DRC ing this comparison cell,the prototype of a 4-data Â6-bit comparison circuit could be produced.It consists of six comparison cells,a 6-bit CMOS NAND gate,one inverter and a DFF.The kernel core of the 4-data Â6-bit comparison circuit only occupies an area of about 1.2mm 2using the UMC 0.5m m process.Since the chip is packaged with 28pins,the die size of thisv o l t a g e , V5.01.50.10.20.30.40.50.60.70.80.9time, usout5.01.50.10.20.30.40.50.60.70.80.9time, usclk5.01.50.10.20.30.40.50.60.70.80.9time, usv (a0)5.01.50.10.20.30.40.50.60.70.80.9time, usv (b0)1.55.000.10.20.30.40.50.60.70.80.9time, usv (c0)5.01.50.10.20.30.40.50.60.70.80.9time, usv (d0)Fig.5Simulation results of the proposed comparison cellV i (d )V outFig.6Delay measure from the critical path in the discharge loopchip is about3.2mm2.The chip layout is shown in Fig.7, where some layers have been hidden so that the layout mapping to the circuit can be clearly seen.The maximum delay time of a data transition is about4.9ns.When the input data transition rate is150MHz,the power dissipation is about38.5Â10À4W.The chip has been fabricated using the CIC MPC project.It has been successfully fabricated eight times.We have verified the performance of the system.Table1 lists the results obtained using:(i)a pass-transistor with a cascade comparison cell with XOR;(ii)a parallel CMOS cell:and(iii)the proposed cell.Based on the pass-transistor method a NXOR cell is realised with six transistors,thus we require6n transistors for the n-bit cascade comparators. When n¼4,the number of transistors used to implement the cascade NXOR pass-logic,the parallel CMOS cell and the proposed cell are24,28and6respectively.Clearly,our circuit size is much smaller than those of the conventional comparator cells.Owing to low circuit complexity,our average power is lower than that for the pass-transistor and the CMOS structures,and the time delay is also shorter than those experienced by the other structures.In the design of a n-dataÂm-bit comparator the cascade pass logic requires6nm transistors.The CMOS comparator cell uses4n+12transistors,we therefore need a total of (4n+12)m+2m+2¼4nm+14m+2transistors.Since ourFig.7Chip layout for4Â6comparatorcomparison cell only used n+2transistors,nm+4m+18 transistor are required for the m-bit comparisons.The prototype circuit was designed for4-dataÂ6-bit ing the proposed comparator cell,the circuit only used66transistors.To demonstrate the superiority of our technique,Table2shows the performance of the4Â6 comparator with various methods.Our chip complexity is significantly smaller than those of the conventional circuits. Additional advantages of our comparison circuit are that it can achieve a shorter delay time and a lower power consumption.Since our comparison cell has high regula-tion,it can be easily expanded to the comparison of multi-input data for any bit size.The basic cells that consist of an inverter,a pass-transistor,and a DFF can be synthesised into a n-inputÂm-bit comparison circuit using a logic synthesis tool.When the resolution m increases,then the stack height of the network also increases.Next,we evaluate the delay time for various resolutions for the four data comparisons.The results are listed in Table3for various resolutions.The delay time for the cascade comparator is almost a linear function of the number of cascade stages.Hence,the delay time becomes significant in high-resolution systems.Our proposed comparator uses a parallel structure,thus we can perform the comparisons n-dataÂm-bits in one go.In this manner the delay time can be efficiently reduced.When the resolution increases,the circuit delay time slowly increases in the proposed cell.4ConclusionsThe design of a multi-input comparator cell using a dynamic CMOS pass-transistor network has been de-scribed.The use of clocking charge techniques has enabled us to use only n+2transistors in an n-input comparison cell.This basic comparison cell can be easily expanded to handle multi-data input for any bit resolution.The prototype of four-inputÂ6-bit comparison circuit has been successfully realised using the UMC0.5m m process.We have tested our comparator and have shown that it can meet our specifications.The maximum clocking frequency and the input data transition rate are1GHz and200MHz, respectively.The performance of the dynamic comparison cell is much better than that of a pass-transistor or a CMOS-based circuit.In summary,the proposed compara-tor has the following advangtages:(i)the power consump-tion can be significantly reduced:(ii)the circuit delay time becomes shorter;(iii)the chip core size is efficiently reduced; (iv)the circuit is easily expanded to multi-input data comparison in various resolutions;and(v)the comparison circuit can be quickly synthesised by using a logic synthesis tool for cell-based designs.5References1Pucknell,D.A.,and Eshraghian,K.:‘Basic VLSI design’(Prentice Hall,3rd edn.)2Corsonello,P.,Perri,S.,and Kantabutra,V.:‘Design of3:1 multiplexer standard cell’,Electron.Lett.,2000,36,(24),pp.1994–19953Alioto,M.,and Palumnbo,G.:‘Modeling and optimized design of current mode Mux/Xor and D Flip-Flop’,IEEE Trans.Circuits Syst.II,Analog Digit.Signal Process.,2000,47,(5),pp.453–4614Rahakrishnan,D.:‘Low voltage CMOS full adder cells’,IEE Proc.Circuits Devices Syst.,2001,148,(1),pp.19–245Sharms, A.M.,and Bayoumi,M.A.:‘A novel high-performance CMOS1-bit full adder cell’,IEEE Trans.Circuits Syst.II,Analog Digit.Signal Process.,2000,47,(5),pp.478–4816Palnitkar,S.:‘Verilog HDL’(Prentice Hall,1996)7Oppenheim,A.V.,and Schafter,R.W.:‘Discrete-time signal proces-sing’(Prentice Hall,Englewood Cliffs,NJ,1989)8Tekalp,A.M.:‘Digital video processing’(Prentice Hall,Englewood Cliffs,NJ,1995)9Razavi,B.,and Wooley,B.A.:‘Design techniques for high-speed high-resolution comparators’,IEEE J.Solid-State Circuits,1992,27,(12), pp.1916–192610Lim,P.J.,and Wooley, B.A.:‘An8-bit200MHz BICMOS comparator’,IEEE J.Solid-State Circuits,1990,25,(1),pp.192–199Table1:Comparison of the proposed cell with the other investigated cellsPass-transistor (Fig.1)CMOS(Fig.2)Proposed nNumber of transistors for n bits(n¼4)6n(24)4n+12(28)n+2(6)Avg.power(at5V),W16.3Â10À418.6Â10À4 4.3Â10À4 Max.delay time,ns 6.8 4.7 3.2n Measured as input data transmitted at150MHzTable2:Implementation of4-data x6-bit comparison circuitsPass-transistor (Fig.1)CMOS(Fig.2)Proposed nNumber of transistors (n¼4,m¼6)6nm(144)4mn+14m+2(182)mn+4m+18(66)Avg.power(at5V).W120.4Â10À4143.5Â10À438.5Â10À4 Max.delay time,ns8.9 6.2 4.9n Measured as input data transmitted at150MHz Table3:Delay time(in nanoseconds)evaluation in m-bit resolution for4data comparisonsPass-transistor(Fig.1)CMOS(Fig.2)Proposedm¼811.1 6.6 5.2m¼1614.38.1 6.8m¼2016.58.97.6。

IC Design(IC 设计)

WELL + Diffusion Poly

WELL + Diffusion + Poly Metal + CONT

About Frontend Design & Backend Design

Frontend Design

Chip architecture design Module design Digital design - write RTL code, logic simulation and synthesis Analog design - draw schematics, analog simulation Chip level design Pre-layout and post-layout simulations

Design methodology is “stable” Experience is very important

Digital Circuit Design Flow

Digital design : RTL to GDSII

RTL Coding verification

Fully supported by EDA tools

Example: RTL code in Verilog module inverter (Y, A); output Y; input A; assign Y = ~A; endmodule

What is Layout?

A set of overlapped geometric drawing Represent physical design (corresponding to mask layers) Database format for Layout: GDSII Example: Inverter (cell INVX1)

GCC的流水冲突识别器和并行调度器

$%&’()&*()E)*>&E&>F+-(.) 5H8HZHP3< Q<:P67;Z

描述指令流水线特点的最主要的数据结构"5H8HZHP3< 以字符串形式给出指令的内部名称"Q<Z

7P;<HTY TOHQ5;5OH =<X<aS%

:P67;Z7P;<HTY 给出该指令的等待时间"TOHQ5;5OH 给出该指令所对应的 =;7 模板"=<X<aS

%&’()&*>&E&>F+-(.) 0%1*%>0 0%1*%>4 G %1*%>! G %1*%>? G %1*%>@0 %&’()&*>&E&>F+-(.) 0%1*%A0 0%1*%A4 G %1*%A!0 %&’()&*>&E&>F+-(.) 0%1*+>0 0%1*+>4 G %1*+>!0 %&’()&*>&E&>F+-(.) 0%1*+>0 0%1*+>4 G %1*+>!0 上面第一个模板定义了自动状态机的名称"第二个模板定 义了处理器可用的功能单元!第三个模板处理的是数据通路的 限制" 其中 %1*%>H,/ 和 %1*%AH,/ 分别代表数据寄存器文件 的 读 I 写 口 "%1*+>H,/ 和 %1*+AH,/ 分 别 代 表 地 址 寄 存 器 文 件 的 读 I 写 口 "%1*2>H,/ 和 %1*2AH,/ 分 别 代 表 推 断 寄 存 器 的 读 I 写口! 后面的 %&’()&*>&E&>F+-(.) 是为了简化随后的描述"如 果数据寄存器文件的读口中的任何一个都可以的话" 就使用 %1*%>! 同样的方式可以定义数据寄存器的写口"地址寄存器的 读 I 写口和推断寄存器的读 I 写口的简化形式! %&’()&*()E)*>&E&>F+-(.) 0%1*J.+%0 @

数字逻辑英汉词汇对照表

常用的专业词汇Synchronous sequential circuit 同步时序电路Asynchronous sequential circuit异步时序电路Analysis and synthesis分析与综合Mealy model and moore model米里型和摩尔型State diagrams状态图Timing diagram时序图State Transition Table/Diagram状态转换表/图Excitation k-map激励卡诺图Excitation table激励表Counter circuit计数器电路Shift register移位寄存器Synchronous binary counter同步二进制计数器Up/down counter可逆计数器Modulo-N counter模-N计数器State table and diagram状态表和图Memory device记忆设备Latch锁存器Set-Reset latch SR锁存器Flip-flop触发器Excitation table激励表Characteristic equation特征方程Master-Slave JK flip-flop主从JK触发器Edge-triggered D flip-flop边沿触发D触发器Posititive/rising Edge正边沿Negative/falling Edge负边沿Decoder译码器Encoder编码器Priority Encoder优先编码器Multiplexer/data selector数据选择器Demutiplexers/data distributor数据分配器Half adder半加器Full adder全加器C omparator比较器Fan-ins fan-outs扇入,扇出POS (product of sum)和之积SOP(sum of product)积之和Karnaugh Map卡诺图Incompletely Specified Functions非完全确定函数Don’t-care term无关项Basic postulates基本公设Boolean algebra布尔代数Switching function开关函数Truth table真值表Canonical form 范式Minterm, maxterm最小项,最大项duality expression对偶式Gate symbol门符号AND,OR,NOT,NAND,NOR,XOR 与,或,非,与非,或非,异或Positive logic, negative logic正逻辑,负逻辑Digital system数字系统Chip芯片Positional notation位置计数法Addition,subtraction,multiplication加减乘除Conversion变换Signed Number representation符号数的表示Complementary number system补码系统Two’s Complement补码Sign Magnitude Number原码One’s Complement反码Binary Coded Decimal(BCD)BCD码Error Detection Code检错码Error Correction Code纠错码Odd-parity Code奇校验码E ven-parity Code偶校验码非专业常用词汇Translate into翻译Fill in the blank填空differ to有别于in that因为depend on取决于supposing/assume假设most simplified/reduced最简form形式following expression下列表达式derive推导whether or not是否modify修改reduce简化correspond to符合implement实现acronym 首字母缩略词。

lm5020用户指南1

AN-1875LM5073HE Evaluation Board With Active BridgeUser's GuideLiterature Number:SNVA355July2008Contents 1Introduction (5)2Features (5)3Theory of Operation (5)4Important Information About theMaximum Power Capability,Cable Usage and PoE Input Potentials (5)5Loading (6)6Efficiency (7)7Printed Circuit Layout (7)2Table of Contents SNVA355–July2008Submit Documentation FeedbackCopyright©2008,Texas Instruments IncorporatedList of Figures1LM5073HE Evaluation Board Block Diagram (6)2Typical Evaluation Setup (7)3Efficiency at48V Input (7)4Top Silkscreen (8)5Top Copper (8)6Bottom Copper (8)7LM5073Evaluation Board:Input40-57V Startup,720mA (8)List of Tables1Bill of Materials (9)3 SNVA355–July2008List of Figures Submit Documentation FeedbackCopyright©2008,Texas Instruments IncorporatedUser's GuideSNVA355–July2008 AN-1875LM5073HE Evaluation Board With Active BridgeThe LM5073HE(High Efficiency)evaluation board is designed as a high performance solution for both IEEE802.3af fully compliant and non-compliant High Power over Ethernet(HPoE)applications.The possible intake power of the unit is a minimum of26.6W for a minimum input voltage of37VDC.All trademarks are the property of their respective owners.4AN-1875LM5073HE Evaluation Board With Active Bridge SNVA355–July2008Submit Documentation FeedbackCopyright©2008,Texas Instruments Incorporated Introduction 1IntroductionThe LM5073HE(High Efficiency)evaluation board is designed as a high performance solution for both IEEE802.3af fully compliant and non-compliant High Power over Ethernet(HPoE)applications.Thepossible intake power of the unit is a minimum of26.6W for a minimum input voltage of37VDC.To make a complete evaluation possible,the board also includes integrated Ethernet RX and TXmagnetics and an RJ45interface.2Features•IEEE802.3af fully compliant•Programmable maximum input dc current through PD interface:800mA•Input voltage ranges:–PoE input voltage range at startup:40to57V–PoE input voltage range with normal operation:33to57V•Efficient Mosfet Bridge polarity protection at input•Measured Efficiency:98%@37VDC,720mA input•Measured Efficiency:98.5%@48VDC,555mA input3Theory of OperationThe LM5073is a100V Power over Ethernet PD interface with auxiliary support.The low RDS(ON)PDinterface hot swap MOSFET and programmable DC current limit extend the range of LM5073applications up to twice the power level of IEEE802.3af compliant devices.In a typical configuration,the input ispolarity protected by a bridge rectifier that can cause an efficiency loss of up to3.5%.This configuration assumes that the design requirements include maximum possible efficiency.Therefore,the polarityprotection is provided by an input controlled mosfet bridge which yields a typical worse case loss of0.44%.For a more detailed description of the various features and customizations afforded,please referto application note AN-1574.4Important Information About theMaximum Power Capability,Cable Usage and PoE Input PotentialsThe LM5073HE evaluation board supports a maximum intake power of26.6W.The user must make sure that the Power Sourcing Equipment(PSE)used can provide at least30W,more if long cables are used.Important:Please note that the CAT-5cable may not supportthe maximum power over two pairs oftwisted wires understrict safety ers shall select the proper cablewires to support thedesign power level without compromisingthe applicable safety ing an improper cable at such power levels may violate various safety regulations and may cause damage.Polarity Precaution:PoE applications are typically-48V systems,in which the notations GND and-48V normally refer to the high and low input potentials,respectively.However,for easy readability,the LM5072 datasheet was written in the positive voltage convention with positive input potentials referenced to the VEE pin of the LM5073.Therefore,when testing the evaluation board with a bench power supply,thenegative terminal of the power supply is equivalent to the PoE system’s-48V potential,and the positive terminal is equivalent to the PoE system ground.To prevent confusion between the datasheet and this application note,the same positive voltage convention is used.5 SNVA355–July2008AN-1875LM5073HE Evaluation Board With Active Bridge Submit Documentation FeedbackCopyright©2008,Texas Instruments IncorporatedLoading Figure1.LM5073HE Evaluation Board Block Diagram5LoadingIf using an electronic load,be sure that the“LOAD ON”switch does not cause a large current surge when turned on.The LM5073cannot have a load applied until one of the shutdown outputs attempts to turn on the DC/DC converter.At this time,too much startup current may cause the LM5073to detect an over-current condition.The typical DC/DC converter has a soft-start feature to prevent this from being aproblem.If unable to monitor the shutdown outputs,simply wait a couple of seconds after applying input power before turning on the load.If you wish to test the evaluation board with an actual DC/DC converter as a load,be sure to connect the appropriate shutdown pin(or inverted shutdown pin)of the LM5073HE board to the appropriate shutdown pin(or inverted shutdown pin)of the DC/DC converter.The dual row6pin socket on the LM5073HE board will mate to a standard0.1”center dual row header.The pin out is shown below.The typical evaluation setup shown uses an LM5030evaluation board as a load.There are many other possible choices,but make sure that the electronic load at the output of the LM5030accounts for theefficiency loss of the LM5030board and does not exceed the limits of the LM5073HE board.Other possible evaluation boards to consider as loads include:L M5005Evaluation Board,a2.5A buck regulator for low cost non-isolated PD applicationsLM5020Evaluation Board,a current mode flyback converterLM5025Evaluation Board,a voltage mode active clamp forward converterLM5026Evaluation Board,a current mode active clamp forward converterLM5032Evaluation Board,a current mode dual interleaved converterLM5034Evaluation Board,a current mode dual interleaved converter with active clampLM5115Evaluation Board,a5A buck regulator with synchronous rectification6AN-1875LM5073HE Evaluation Board With Active Bridge SNVA355–July2008Submit Documentation FeedbackCopyright©2008,Texas Instruments Incorporated EfficiencyFigure2.Typical Evaluation Setup6EfficiencyFigure3shows the typical efficiency curve at48VDC input verses load.Since losses are almost entirely resistive,a value of1.05Ohms may be used to estimate losses for other levels of current and voltage.Figure3.Efficiency at48V Input7Printed Circuit LayoutThe layers of the printed circuit board are shown in top down order in Figure4to Figure6.View is from the top of the board.Scale is approximately X1.5.The printed circuit board consists of2layers of2ounce copper on FR4material with a total thickness of0.065inches.7 SNVA355–July2008AN-1875LM5073HE Evaluation Board With Active Bridge Submit Documentation FeedbackCopyright©2008,Texas Instruments IncorporatedPrinted Circuit Layout Figure4.Top SilkscreenFigure5.Top CopperFigure6.Bottom CopperFigure7.LM5073Evaluation Board:Input40-57V Startup,720mA8AN-1875LM5073HE Evaluation Board With Active Bridge SNVA355–July2008Submit Documentation FeedbackCopyright©2008,Texas Instruments Incorporated Printed Circuit LayoutTable1.Bill of MaterialsDesigna Description Manufacturer Part Number torC18.0pF,50V,CER,NPO,0603AVX06031A8R0CAT2A C28.0pF,50V,CER,NPO,0603AVX06031A8R0CAT2A C38.0pF,50V,CER,NPO,0603AVX06031A8R0CAT2A C48.0pF,50V,CER,NPO,0603AVX06031A8R0CAT2A C50.047µF,100V,X7R,0805TDK C2012X7R2A473K C60.047µF,100V,X7R,0805TDK C2012X7R2A473K C70.047µF,100V,X7R,0805TDK C2012X7R2A473K C822µF,100V,ALUM ELECT,LOW ESR PANASONIC EEV-FK2A220PJ1JACK,MODULAR,2PORT RJ45TYCO5569381-1J2SOCKET,.025"SQ POST,3X2,R/A TYCO6-535512-2L1INDUCTOR,4.7µH,1.8A,56m COILCRAFT MSS6132-472MLP1TEST POINT,MINIATURE KEYSTONE5002P2TEST POINT,MINIATURE KEYSTONE5002P3TERMINAL,TURRET KEYSTONE1503P4TERMINAL,TURRET KEYSTONE1503P5TERMINAL,TURRET KEYSTONE1503P6TERMINAL,TURRET KEYSTONE1503Q1MOSFET,P-CH,100V,134mΩ,1212-8VISHAY SI7113DNQ2MOSFET,P-CH,100V,134mΩ,1212-8VISHAY SI7113DNQ3MOSFET,DUAL N-CH,100V,62mΩ,SO8FAIRCHILD FDS3992Q4MOSFET,P-CH,100V,134mΩ,1212-8VISHAY SI7113DNQ5MOSFET,P-CH,100V,134mΩ,1212-8VISHAY SI7113DNQ6MOSFET,DUAL N-CH,100V,62mΩ,SO8FAIRCHILD FDS3992R1RESISTOR,150K,1%,1/8W,0805VISHAY CRCW0805150KFR2RESISTOR,150K,1%,1/8W,0805VISHAY CRCW0805150KFR3RESISTOR,150K,1%,1/8W,0805VISHAY CRCW0805150KFR4RESISTOR,150K,1%,1/8W,0805VISHAY CRCW0805150KFR5RESISTOR,150K,1%,1/8W,0805VISHAY CRCW0805150KFR6RESISTOR,150K,1%,1/8W,0805VISHAY CRCW0805150KFR7RESISTOR,150K,1%,1/8W,0805VISHAY CRCW0805150KFR8RESISTOR,150K,1%,1/8W,0805VISHAY CRCW0805150KFR9RESISTOR,31.6,1%,1/8W,0805VISHAY CRCW080531R6F R10RESISTOR,15.0K,1%,1/8W,0805VISHAY CRCW080515K0FT1SIGNAL PATH HPOE MAGNETICS COILCRAFT ETH1-230LU1IC,POE INTERFACE,TSSOP-14EP NATIONAL SEMICONDUCTOR LM5073MHZ1ZENER,15V@50µA,SOD-123CENTRAL SEMICONDUCTOR CMHZ4702Z2ZENER,15V@50µA,SOD-123CENTRAL SEMICONDUCTOR CMHZ4702Z3ZENER,15V@50µA,SOD-123CENTRAL SEMICONDUCTOR CMHZ4702Z4ZENER,15V@50µA,SOD-123CENTRAL SEMICONDUCTOR CMHZ4702Z5ZENER,15V@50µA,SOD-123CENTRAL SEMICONDUCTOR CMHZ4702Z6ZENER,15V@50µA,SOD-123CENTRAL SEMICONDUCTOR CMHZ4702Z7ZENER,15V@50µA,SOD-123CENTRAL SEMICONDUCTOR CMHZ4702Z8ZENER,15V@50µA,SOD-123CENTRAL SEMICONDUCTOR CMHZ4702Z9DIODE,TVS,60V,SMA DIODES INC.SMAJ60A-139 SNVA355–July2008AN-1875LM5073HE Evaluation Board With Active Bridge Submit Documentation FeedbackCopyright©2008,Texas Instruments IncorporatedPrinted Circuit Layout 10AN-1875LM5073HE Evaluation Board With Active Bridge SNVA355–July2008Submit Documentation FeedbackCopyright©2008,Texas Instruments IncorporatedEVALUATION BOARD/KIT/MODULE(EVM)ADDITIONAL TERMSTexas Instruments(TI)provides the enclosed Evaluation Board/Kit/Module(EVM)under the following conditions:The user assumes all responsibility and liability for proper and safe handling of the goods.Further,the user indemnifies TI from all claims arising from the handling or use of the goods.Should this evaluation board/kit not meet the specifications indicated in the User’s Guide,the board/kit may be returned within30days from the date of delivery for a full refund.THE FOREGOING LIMITED WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES,EXPRESSED,IMPLIED,OR STATUTORY,INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE,NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT,SPECIAL,INCIDENTAL,OR CONSEQUENTIAL DAMAGES.Please read the User's Guide and,specifically,the Warnings and Restrictions notice in the User's Guide prior to handling the product.This notice contains important safety information about temperatures and voltages.For additional information on TI's environmental and/or safety programs,please visit /esh or contact TI.No license is granted under any patent right or other intellectual property right of TI covering or relating to any machine,process,or combination in which such TI products or services might be or are used.TI currently deals with a variety of customers for products,and therefore our arrangement with the user is not exclusive.TI assumes no liability for applications assistance,customer product design, software performance,or infringement of patents or services described herein.REGULATORY COMPLIANCE INFORMATIONAs noted in the EVM User’s Guide and/or EVM itself,this EVM and/or accompanying hardware may or may not be subject to the Federal Communications Commission(FCC)and Industry Canada(IC)rules.For EVMs not subject to the above rules,this evaluation board/kit/module is intended for use for ENGINEERING DEVELOPMENT, DEMONSTRATION OR EVALUATION PURPOSES ONLY and is not considered by TI to be a finished end product fit for general consumer use.It generates,uses,and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to part15of FCC or ICES-003rules,which are designed to provide reasonable protection against radio frequency interference.Operation of the equipment may cause interference with radio communications,in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.General Statement for EVMs including a radioUser Power/Frequency Use Obligations:This radio is intended for development/professional use only in legally allocated frequency and power limits.Any use of radio frequencies and/or power availability of this EVM and its development application(s)must comply with local laws governing radio spectrum allocation and power limits for this evaluation module.It is the user’s sole responsibility to only operate this radio in legally acceptable frequency space and within legally mandated power limitations.Any exceptions to this are strictly prohibited and unauthorized by Texas Instruments unless user has obtained appropriate experimental/development licenses from local regulatory authorities,which is responsibility of user including its acceptable authorization.For EVMs annotated as FCC–FEDERAL COMMUNICATIONS COMMISSION Part15CompliantCautionThis device complies with part15of the FCC Rules.Operation is subject to the following two conditions:(1)This device may not cause harmful interference,and(2)this device must accept any interference received,including interference that may cause undesired operation. Changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.FCC Interference Statement for Class A EVM devicesThis equipment has been tested and found to comply with the limits for a Class A digital device,pursuant to part15of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment.This equipment generates,uses,and can radiate radio frequency energy and,if not installed and used in accordance with the instruction manual,may cause harmful interference to radio communications.Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.FCC Interference Statement for Class B EVM devicesThis equipment has been tested and found to comply with the limits for a Class B digital device,pursuant to part15of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation.This equipment generates,uses and can radiate radio frequency energy and,if not installed and used in accordance with the instructions,may cause harmful interference to radio communications.However,there is no guarantee that interference will not occur in a particular installation.If this equipment does cause harmful interference to radio or television reception,which can be determined by turning the equipment off and on,the user is encouraged to try to correct the interference by one or more of the following measures:•Reorient or relocate the receiving antenna.•Increase the separation between the equipment and receiver.•Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.•Consult the dealer or an experienced radio/TV technician for help.For EVMs annotated as IC–INDUSTRY CANADA CompliantThis Class A or B digital apparatus complies with Canadian ICES-003.Changes or modifications not expressly approved by the party responsible for compliance could void the user’s authority to operate the equipment.Concerning EVMs including radio transmittersThis device complies with Industry Canada licence-exempt RSS standard(s).Operation is subject to the following two conditions:(1)this device may not cause interference,and(2)this device must accept any interference,including interference that may cause undesired operation of the device.Concerning EVMs including detachable antennasUnder Industry Canada regulations,this radio transmitter may only operate using an antenna of a type and maximum(or lesser)gain approved for the transmitter by Industry Canada.To reduce potential radio interference to other users,the antenna type and its gain should be so chosen that the equivalent isotropically radiated power(e.i.r.p.)is not more than that necessary for successful communication.This radio transmitter has been approved by Industry Canada to operate with the antenna types listed in the user guide with the maximum permissible gain and required antenna impedance for each antenna type indicated.Antenna types not included in this list,having a gain greater than the maximum gain indicated for that type,are strictly prohibited for use with this device.Cet appareil numérique de la classe A ou B est conformeàla norme NMB-003du Canada.Les changements ou les modifications pas expressément approuvés par la partie responsable de la conformitéont pu vider l’autoritédel'utilisateur pour actionner l'équipement.Concernant les EVMs avec appareils radioLe présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence.L'exploitation est autorisée aux deux conditions suivantes:(1)l'appareil ne doit pas produire de brouillage,et(2)l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi,même si le brouillage est susceptible d'en compromettre le fonctionnement.Concernant les EVMs avec antennes détachablesConformémentàla réglementation d'Industrie Canada,le présentémetteur radio peut fonctionner avec une antenne d'un type et d'un gain maximal(ou inférieur)approuvépour l'émetteur par Industrie Canada.Dans le but de réduire les risques de brouillage radioélectriqueàl'intention des autres utilisateurs,il faut choisir le type d'antenne et son gain de sorte que la puissance isotrope rayonnéeéquivalente (p.i.r.e.)ne dépasse pas l'intensiténécessaireàl'établissement d'une communication satisfaisante.Le présentémetteur radio aétéapprouvépar Industrie Canada pour fonctionner avec les types d'antenneénumérés dans le manueld’usage et ayant un gain admissible maximal et l'impédance requise pour chaque type d'antenne.Les types d'antenne non inclus dans cette liste,ou dont le gain est supérieur au gain maximal indiqué,sont strictement interdits pour l'exploitation de l'émetteur.【Important Notice for Users of this Product in Japan】This development kit is NOT certified as Confirming to Technical Regulations of Radio Law of JapanIf you use this product in Japan,you are required by Radio Law of Japan to follow the instructions below with respect to this product:e this product in a shielded room or any other test facility as defined in the notification#173issued by Ministry of Internal Affairs andCommunications on March28,2006,based on Sub-section1.1of Article6of the Ministry’s Rule for Enforcement of Radio Law of Japan,e this product only after you obtained the license of Test Radio Station as provided in Radio Law of Japan with respect to thisproduct,ore of this product only after you obtained the Technical Regulations Conformity Certification as provided in Radio Law of Japan withrespect to this product.Also,please do not transfer this product,unless you give the same notice above to the transferee.Please note that if you could not follow the instructions above,you will be subject to penalties of Radio Law of Japan.Texas Instruments Japan Limited(address)24-1,Nishi-Shinjuku6chome,Shinjuku-ku,Tokyo,Japanhttp://www.tij.co.jp【ご使用にあたっての注】本開発キットは技術基準適合証明を受けておりません。

Logic Synthesis with Synopsys

Circuit netlist

ECE 545 – Introduction to VHDL

3

Basic Synthesis Flow

ECE 545 – Introduction to VHDL

4

Synthesis using Design Compiler

ECE 545 – Introduction to VHDL

ECE 545 – Introduction to VHDL 11

Synthesis script (4)

/***************************************************/ /* Apply these constraints to the top-level entity*/ /***************************************************/ set_max_fanout 100 block set_clock_latency 0.1 find(clock, "clk") set_clock_transition 0.01 find(clock, "clk") set_clock_uncertainty -setup 0.1 find(clock, "clk") set_clock_uncertainty -hold 0.1 find(clock, "clk") set_load 0 all_outputs() set_input_delay 1.0 -clock clk -max all_inputs() set_output_delay -max 1.0 -clock clk all_outputs() set_wire_load_model -library tcb013ghptc -name "TSMC8K_Fsg_Conservative"

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2008 IEEE Region 10 Colloquium and the Third ICIIS, Kharagpur, INDIA December 8-10. 404

978-1-4244-2806-9/08/$25.00© 2008 IEEE 1AND-XOR Network Synthesis with Area-Power Trade-off

Sambhu Nath Pradhan Santanu Chattopadhyay Dept. of E & ECE, IIT Kharagpur-721302, India snpradhan@ece.iitkgp.ernet.in santanu@ece.iitkgp.ernet.in

Abstract—As AND-XOR network results in much better realization and requires fewer product terms than AND-OR realization, it network has encouraged researchers to look for efficient minimization and synthesis tools for their realization. Among several canonical representations of AND-XOR networks, popular and most testable one is the Fixed Polarity Reed Muller (FPRM) form. In this paper we have used GA (genetic algorithm) to select the polarities of the variables of the AND-XOR network. The polarity is selected based on the optimization of area, dynamic power and leakage power of the resulting circuit. This is the first ever effort to incorporate leakage power consideration in the variable polarity selection process. Here, we have presented new leakage power model of AND, OR and XOR gates at 90nm technology. The area (in terms of number of product terms) results obtained are superior to those reported in the literature. It also enumerates the trade-offs present in the solution space for different weights associated with area, dynamic power and leakage power of the resulting AND-XOR network.

1. Introduction Logic minimization, in the domain of combinational logic synthesis plays an important role in determining the area and power of the synthesized circuit. Researchers have long back established the suitability of XOR based representation in different domains of applications, such as, linear circuits, arithmetic circuits, telecommunication circuits etc. In such cases, XOR-based realizations often produce more compact circuit than the OR-based realizations. When realized as PLAs, XOR circuits offer high testability. It is also worthwhile to note the fact that several technologies like Field Programmable Gate Arrays (FPGAs) have made the delay and area of all types of gates equal. For example, in Xilinx LUT-type FPGAs, the basic combinational block can realize any function of upto five variables with same area and delay. Similarly, the three-Mux architecture of Actel is quite suitable for XOR realization. Cli6006 from Concurrent Logic includes a 2-input XOR gate in its basic granularity block. Two-level realizations often form the basis for the multilevel minimization tools. Thus, for good realization of combinational functions, it is very important to start with a good two-level decomposition of it. Accordingly, lots of research works have been carried out in XOR-based circuit synthesis and this has been surveyed in Section 2. There are several types of AND-XOR based circuits, namely Positive Polarity Reed-Muller (PPRM), Fixed Polarity Reed-Muller (FPRM), Pseudo Reed-Muller, Generalized Reed-Muller, EXOR sum of products, Kronecker and Pseudo Kronecker forms [6]. Each of these circuits has its own advantages. As far as XOR synthesis is concerned, this paper concentrates on the synthesis of FPRM circuits only. The works reported in the literature so far have the following shortcomings. Most of the works target area minimization and do not account for power.

However, the advent of portable electronic devices has made low power design an increasingly important research area. As leakage current becomes the major contributor to power consumption, the industry must reconsider the power equation that limits system performances, chip sizes and cost. With this background, the current work proposes a solution to the following problem. Given a multiinput, multioutput Boolean function F and a weight factor perform a FPRM synthesis of minimizing the weighted sum of area (number of product terms), dynamic power (switching activity) and leakage power. To solve the above problem we have made a Genetic Algorithm (GA) based formulation to identify the polarity assignment to the input variables. Reed-Muller expansion [10] has long been proposed for realizing Boolean function in the positive polarity AND-XOR form. An n-variable Boolean function f can be expressed in the following Canonical Reed-Muller expansion of 2n terms: f(x1, x

2,

….. xn) = a0 ⊕ a1x1 ⊕ a2x2 ⊕ -----⊕ a2n-1 x1x2….xn, where

ai∈(0, 1). All xi input variables appear in true form in the expansion. A number of modified versions of this basic canonical form have been studied. The constrained version in which each of the variables is allowed to assume only one of the polarities that is maintained throughout the function is known as Fixed Polarity Reed Muller (FPRM) form [10]. This particular form results in much lesser number of product terms than the original Reed-Muller form and is the most testable among all general canonical forms. The rest of the paper is organized as follows: Section 2 enumerates the previous work on AND-XOR synthesis. Section 3 presents our AND-XOR synthesis approach. Power estimation is given in Section 4. Using GA, AND-XOR synthesis solution is given in Section 5. Section 6 presents experimental results.