A circuit SAT solver with signal correlation guided learning

电子信息工程基础知识单选题100道及答案解析

电子信息工程基础知识单选题100道及答案解析1. 以下哪种材料常用于制作半导体器件?()A. 铜B. 硅C. 铁D. 铝答案:B解析:硅是常用的半导体材料。

2. 在数字电路中,基本的逻辑门不包括()A. 与门B. 或门C. 非门D. 与非门答案:D解析:与非门是由与门和非门组合而成的复合门,基本逻辑门是与门、或门、非门。

3. 以下哪种信号是连续变化的?()A. 数字信号B. 模拟信号C. 脉冲信号D. 编码信号答案:B解析:模拟信号是在时间和数值上都连续变化的信号。

4. 电容的单位是()A. 欧姆B. 法拉C. 安培D. 伏特答案:B解析:电容的单位是法拉。

5. 三极管工作在放大区时,发射结和集电结的状态分别是()A. 正偏、正偏B. 正偏、反偏C. 反偏、正偏D. 反偏、反偏答案:B解析:三极管在放大区时,发射结正偏,集电结反偏。

6. 集成电路的英文缩写是()A. ICB. PCBC. CPUD. ROM答案:A解析:集成电路的英文是Integrated Circuit,缩写为IC。

7. 以下哪种通信方式属于无线通信?()A. 双绞线通信B. 同轴电缆通信C. 光纤通信D. 蓝牙通信答案:D解析:蓝牙通信是无线通信方式,双绞线、同轴电缆、光纤通信都是有线通信。

8. 数字电路中,能够存储一位二进制信息的基本单元是()A. 触发器B. 计数器C. 寄存器D. 编码器答案:A解析:触发器能存储一位二进制信息。

9. 以下哪种编程语言常用于嵌入式系统开发?()A. JavaB. PythonC. CD. PHP答案:C解析:C 语言常用于嵌入式系统开发。

10. 频率的单位是()A. 赫兹B. 瓦特C. 焦耳D. 牛顿答案:A解析:频率的单位是赫兹(Hz)。

11. 运算放大器的主要功能是()A. 放大电压B. 放大电流C. 进行逻辑运算D. 存储数据答案:A解析:运算放大器主要用于放大电压信号。

12. 以下哪种存储器断电后数据会丢失?()A. ROMB. RAMC. EPROMD. EEPROM答案:B解析:RAM(随机存储器)断电后数据会丢失。

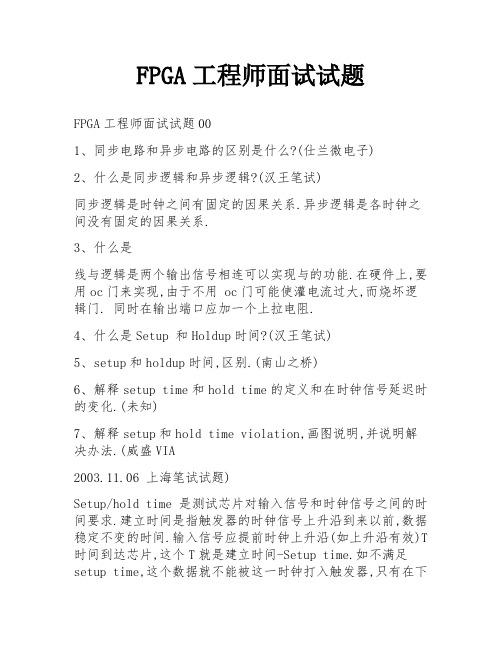

FPGA工程师面试试题

FPGA工程师面试试题FPGA工程师面试试题001、同步电路和异步电路的区别是什么?(仕兰微电子)2、什么是同步逻辑和异步逻辑?(汉王笔试)同步逻辑是时钟之间有固定的因果关系.异步逻辑是各时钟之间没有固定的因果关系.3、什么是线与逻辑是两个输出信号相连可以实现与的功能.在硬件上,要用oc门来实现,由于不用 oc门可能使灌电流过大,而烧坏逻辑门. 同时在输出端口应加一个上拉电阻.4、什么是Setup 和Holdup时间?(汉王笔试)5、setup和holdup时间,区别.(南山之桥)6、解释setup time和hold time的定义和在时钟信号延迟时的变化.(未知)7、解释setup和hold time violation,画图说明,并说明解决办法.(威盛VIA2003.11.06 上海笔试试题)Setup/hold time 是测试芯片对输入信号和时钟信号之间的时间要求.建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间.输入信号应提前时钟上升沿(如上升沿有效)T 时间到达芯片,这个T就是建立时间-Setup time.如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器. 保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间.如果hold time 不够,数据同样不能被打入触发器.建立时间 (Setup Time)和保持时间(Hold time).建立时间是指在时钟边沿前,数据信号需要保持不变的时间.保持时间是指时钟跳变边沿后数据信号需要保持不变的时间.如果不满足建立和保持时间的话,那么DFF将不能正确地采样到数据,将会出现 metastability的情况.如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量.8、说说对数字逻辑中的竞争和冒险的理解,并举例说明竞争和冒险怎样消除.(仕兰微电子)9、什么是竞争与冒险现象?怎样判断?如何消除?(汉王笔试)在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争.产生毛刺叫冒险.如果布尔式中有相反的信号则可能产生竞争和冒险现象.解决方法:一是添加布尔式的消去项,二是在芯片外部加电容.10、你知道那些常用逻辑电平?TTL与COMS电平可以直接互连吗?(汉王笔试)常用逻辑电平:12V,5V,3.3V;TTL和CMOS不可以直接互连,由于TTL是在0.3-3.6V之间,而CMOS则是有在12V的有在5V 的.CMOS输出接到TTL是可以直接互连.TTL接到CMOS需要在输出端口加一上拉电阻接到5V或者12V.11、如何解决亚稳态.(飞利浦-大唐笔试)亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态.当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上.在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去.12、IC设计中同步复位与异步复位的区别.(南山之桥)13、MOORE 与 MEELEY状态机的特征.(南山之桥)14、多时域设计中,如何处理信号跨时域.(南山之桥)15、给了reg的setup,hold时间,求中间组合逻辑的delay范围.(飞利浦-大唐笔试)Delay16、时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min.组合逻辑电路最大延迟为T2max,最小为T2min.问,触发器D2的建立时间T3和保持时间应满足什么条件.(华为)17、给出某个一般时序电路的图,有Tsetup,Tdelay,Tck->q,还有 clock的delay,写出决定最大时钟的因素,同时给出表达式.(威盛VIA 2003.11.06 上海笔试试题)18、说说静态、动态时序模拟的优缺点.(威盛VIA2003.11.06 上海笔试试题)19、一个四级的Mux,其中第二级信号为关键信号如何改善timing.(威盛VIA2003.11.06 上海笔试试题)20、给出一个门级的图,又给了各个门的传输延时,问关键路径是什么,还问给出输入, 使得输出依赖于关键路径.(未知)21、逻辑方面数字电路的卡诺图化简,时序(同步异步差异),触发器有几种(区别,优点),全加器等等.(未知)22、卡诺图写出逻辑表达使.(威盛VIA 2003.11.06 上海笔试试题)23、化简F(A,B,C,D)= m(1,3,4,5,10,11,12,13,14,15)的和.(威盛)24、please show the CMOS inverter schmatic,layout and its cross sectionwith P-well process.Plot its transfer curve (Vout-Vin) And also explain theoperation region of PMOS and NMOS for each segment of the transfer curve? (威盛笔试题circuit design-beijing-03.11.09)25、To design a CMOS invertor with balance rise and fall time,please definethe ration of channel width of PMOS and NMOS and explain?26、为什么一个标准的倒相器中P管的宽长比要比N管的宽长比大?(仕兰微电子)27、用mos管搭出一个二输入与非门.(扬智电子笔试)28、please draw the transistor level schematic of a cmos 2 input AND gate andexplain which input has faster response for output rising edge.(less delaytime).(威盛笔试题circuit design-beijing-03.11.09)29、画出NOT,NAND,NOR的符号,真值表,还有transistor level的电路.(Infineon笔试)30、画出CMOS的图,画出tow-to-one mux gate.(威盛VIA 2003.11.06 上海笔试试题)31、用一个二选一mux和一个inv实现异或.(飞利浦-大唐笔试)32、画出Y=A*B+C的cmos电路图.(科广试题)33、用逻辑们和cmos电路实现ab+cd.(飞利浦-大唐笔试)34、画出CMOS电路的晶体管级电路图,实现Y=A*B+C(D+E).(仕兰微电子)35、利用4选1实现F(x,y,z)=xz+yz’.(未知)36、给一个表达式f=xxxx+xxxx+xxxxx+xxxx用最少数量的与非门实现(实际上就是化简).37、给出一个简单的由多个NOT,NAND,NOR组成的原理图,根据输入波形画出各点波形. (Infineon笔试)38、为了实现逻辑(A XOR B)OR (C AND D),请选用以下逻辑中的一种,并说明为什么?1)INV 2)AND 3)OR 4)NAND 5)NOR 6)XOR 答案:NAND(未知)39、用与非门等设计全加法器.(华为)40、给出两个门电路让你分析异同.(华为)41、用简单电路实现,当A为输入时,输出B波形为…(仕兰微电子)42、A,B,C,D,E进行投票,多数服从少数,输出是F(也就是如果A,B,C,D,E中1的个数比0 多,那么F输出为1,否则F为0),用与非门实现,输入数目没有限制.(未知)43、用波形表示D触发器的功能.(扬智电子笔试)44、用传输门和倒向器搭一个边沿触发器.(扬智电子笔试)45、用逻辑们画出D触发器.(威盛VIA 2003.11.06 上海笔试试题)46、画出DFF的结构图,用verilog实现之.(威盛)47、画出一种CMOS的D锁存器的电路图和版图.(未知)48、D触发器和D锁存器的区别.(新太硬件面试)49、简述latch和filp-flop的异同.(未知)50、LATCH和DFF的概念和区别.(未知)51、latch与register的区别,为什么现在多用register.行为级描述中latch如何产生的. (南山之桥)52、用D触发器做个二分颦的电路.又问什么是状态图.(华为)53、请画出用D触发器实现2倍分频的逻辑电路?(汉王笔试)54、怎样用D触发器、与或非门组成二分频电路?(东信笔试)55、How many flip-flop circuits are needed to divide by 16? (Intel) 16分频?56、用filp-flop和logic-gate设计一个1位加法器,输入carryin和current-stage,输出 carryout和next-stage. (未知)57、用D触发器做个4进制的计数.(华为)58、实现N位Johnson Counter,N=5.(南山之桥)59、用你熟悉的设计方式设计一个可预置初值的7进制循环计数器,15进制的呢?(仕兰微电子)60、数字电路设计当然必问Verilog/VHDL,如设计计数器.(未知)61、BLOCKING NONBLOCKING 赋值的区别.(南山之桥)62、写异步D触发器的verilog module.(扬智电子笔试)module dff8(clk , reset, d, q);input clk;input reset;input [7:0] d;output [7:0] q;reg [7:0] q;always @ (posedge clk or posedge reset)if(reset)qelseqendmodule63、用D触发器实现2倍分频的Verilog描述? (汉王笔试) module divide2( clk , clk_o, reset);input clk , reset;output clk_o;wire in;reg out ;always @ ( posedge clk or posedge reset)if ( reset)outelseoutassign in = ~out;assign clk_o = out;endmodule64、可编程逻辑器件在现代电子设计中越来越重要,请问:a) 你所知道的可编程逻辑器件有哪些? b) 试用VHDL或VERILOG、ABLE描述8位D触发器逻辑.(汉王笔试)PAL,PLD,CPLD,FPGA.module dff8(clk , reset, d, q);input clk;input reset;input d;output q;reg q;always @ (posedge clk or posedge reset)if(reset)qelseqendmodule65、请用HDL描述四位的全加法器、5分频电路.(仕兰微电子)66、用VERILOG或VHDL写一段代码,实现10进制计数器.(未知)67、用VERILOG或VHDL写一段代码,实现消除一个glitch.(未知)68、一个状态机的题目用verilog实现(不过这个状态机画的实在比较差,很容易误解的).(威盛VIA 2003.11.06 上海笔试试题)69、描述一个交通信号灯的设计.(仕兰微电子)70、画状态机,接受1,2,5分钱的卖报机,每份报纸5分钱.(扬智电子笔试)71、设计一个自动售货机系统,卖soda水的,只能投进三种硬币,要正确的找回钱数. (1)画出fsm(有限状态机);(2)用verilog编程,语法要符合fpga设计的要求.(未知)72、设计一个自动饮料售卖机,饮料10分钱,硬币有5分和10分两种,并考虑找零:(1) 画出fsm(有限状态机);(2)用verilog编程,语法要符合fpga设计的要求;(3)设计工程中可使用的工具及设计大致过程.(未知)73、画出可以检测10010串的状态图,并verilog实现之.(威盛)74、用FSM实现101101的序列检测模块.(南山之桥)a为输入端,b为输出端,如果a连续输入为1101则b输出为1,否则为0.例如a: [***********]0110b: [***********]0000请画出state machine;请用RTL描述其state machine.(未知)75、用verilog/vddl检测stream中的特定字符串(分状态用状态机写).(飞利浦-大唐笔试)76、用verilog/vhdl写一个fifo控制器(包括空,满,半满信号).(飞利浦-大唐笔试)77、现有一用户需要一种集成电路产品,要求该产品能够实现如下功能:y=lnx,其中,x为4位二进制整数输入信号.y为二进制小数输出,要求保留两位小数.电源电压为3~5v假设公司接到该项目后,交由你来负责该产品的设计,试讨论该产品的设计全程.(仕兰微电子)78、sram,falsh memory,及dram的区别?(新太硬件面试)79、给出单管DRAM的原理图(西电版《数字电子技术基础》杨颂华、冯毛官205页图9-14b),问你有什么办法提高refresh time,总共有5个问题,记不起来了.(降低温度,增大电容存储容量)(Infineon笔试)80、Please draw schematic of a mon SRAM cell with 6 transistors,point outwhich nodes can store data and which node is word line control? (威盛笔试题circuit design-beijing-03.11.09)81、名词:sram,ssram,sdram名词IRQ,BIOS,USB,VHDL,SDRIRQ: Interrupt ReQuestBIOS: Basic Input Output SystemUSB: Universal Serial BusVHDL: VHIC Hardware Description LanguageSDR: Single Data Rate压控振荡器的英文缩写(VCO).动态随机存储器的英文缩写(DRAM).名词解释,无聊的外文缩写罢了,比如PCI、ECC、DDR、interrupt、pipeline、IRQ,BIOS,USB,VHDL,VLSI VCO(压控振荡器) RAM (动态随机存储器),FIR IIR DFT(离散傅立叶变换)或者是中文的,比如:a.量化误差 b.直方图 c.白平FPGA工程师面试试题011 什么是Setup 和Holdup时间?2 什么是竞争与冒险现象?怎样判断?如何消除?3 用D触发器实现2倍分频的逻辑电路? .......4 什么是5 什么是同步逻辑和异步逻辑?6 请画出微机接口电路中,典型的输入设备与微机接口逻辑示意图(数据接口、控制接口、所存器/缓冲器)。

电子公司笔试题精选

电子类公司笔试题精选一、模拟电路1基尔霍夫定理的内容是什么?〔仕兰微电子〕基尔霍夫电流定律是一个电荷守恒定律,即在一个电路中流入一个节点的电荷与流出同一个节点的电荷相等.基尔霍夫电压定律是一个能量守恒定律,即在一个回路中回路电压之和为零.2、平板电容公式(C=εS/4πkd)。

〔未知〕3、最基本的如三极管曲线特性。

〔未知〕4、描述反馈电路的概念,列举他们的应用。

〔仕兰微电子〕5、负反馈种类〔电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈〕;负反馈的优点〔降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用〕〔未知〕6、放大电路的频率补偿的目的是什么,有哪些方法?〔仕兰微电子〕7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。

〔未知〕8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。

〔凹凸〕9、基本放大电路种类〔电压放大器,电流放大器,互导放大器和互阻放大器〕,优缺点,特别是广泛采用差分结构的原因。

〔未知〕10、给出一差分电路,告诉其输出电压Y 和Y-,求共模分量和差模分量。

〔未知〕11、画差放的两个输入管。

〔凹凸〕12、画出由运放构成加法、减法、微分、积分运算的电路原理图。

并画出一个晶体管级的运放电路。

〔仕兰微电子〕13、用运算放大器组成一个10倍的放大器。

〔未知〕14、给出一个简单电路,让你分析输出电压的特性〔就是个积分电路〕,并求输出端某点的rise/fall时间。

(Infineon笔试试题)15、电阻R和电容C串联,输入电压为R和C之间的电压,输出电压分别为C上电压和R 上电压,要求制这两种电路输入电压的频谱,判断这两种电路何为高通滤波器,何为低通滤波器。

当RC18、说说静态、动态时序模拟的优缺点。

〔威盛VIA 2003.11.06 上海笔试试题〕19、一个四级的Mux,其中第二级信号为关键信号如何改善timing。

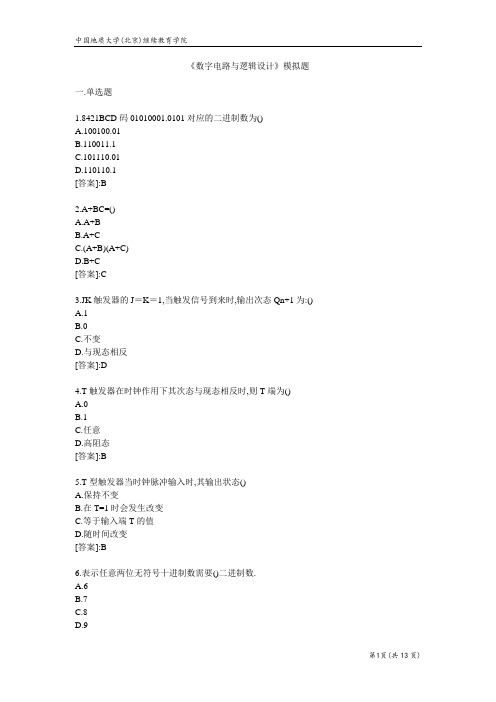

数字电路与逻辑设计-模拟题

《数字电路与逻辑设计》模拟题一.单选题1.8421BCD码01010001.0101对应的二进制数为()A.100100.01B.110011.1C.101110.01D.110110.1[答案]:B2.A+BC=()A.A+BB.A+CC.(A+B)(A+C)D.B+C[答案]:C3.JK触发器的J=K=1,当触发信号到来时,输出次态Qn+1为:()A.1B.0C.不变D.与现态相反[答案]:D4.T触发器在时钟作用下其次态与现态相反时,则T端为()A.0B.1C.任意D.高阻态[答案]:B5.T型触发器当时钟脉冲输入时,其输出状态()A.保持不变B.在T=1时会发生改变C.等于输入端T的值D.随时间改变[答案]:B6.表示任意两位无符号十进制数需要()二进制数.A.6B.7C.8D.9[答案]:B7.补码1.1000的真值是().A.1.0111B.-1.0111C.-0.1001D.-0.1[答案]:D8.采用奇偶校验进行检错时()A.只能发现偶数位出错的情况,不能发现奇数位出错的情况B.只能发现奇数位出错的情况,不能发现偶数位出错的情况C.既能发现偶数位出错的情况,又能发现奇数位出错的情况D.有时能发现出错的情况,有时不能[答案]:B9.常用的BCD码有()A.奇偶校验码B.格雷码C.ASCII码D.余三码[答案]:D10.带符号位的二进制数的原码为11101,则对应的十进制为()A.29B.-29C.-13D.13[答案]:C11.当JK触发器的次态Qn+1=,则输入J,K为()A.0,0B..0,1C.1,0D.1,1[答案]:D12.当逻辑函数有n个变量时,共有()个变量取值组合?A.nB.2nC.n2D.n3[答案]:D13.典型的TTL与非门电路使用的电源电压为()A.5VB.3.6VC.0.35VD.3—18V[答案]:A14.电平异步时序逻辑电路不允许两个或两个以上输入信号().A.同时为0B.同时为1C.同时改变D.同时出现[答案]:C15.多少个二进制数字可以组成一位十六进制数字?()A.2B.3C.4D.5[答案]:C16.二进制的1100.l10相当于十进制的()A.12.75B.16.65C.6.6D.6.3[答案]:A17.二进制数(1111101.0101)2转换为八进制为:()A.37.25B.175.24C.125.3125D.761.2[答案]:B18.二进制数-0.0110的补码是()A.1.101B.1.0101C.1.011D.1.1011[答案]:A19.二进制数-0110的反码是(最高位是符号位)()A.10110C.11010D.110[答案]:B20.构造一个100脉冲序列检测器需要多少个触发器?()A.1个B.2个C.3个D.4个[答案]:B21.函数F=AB+BC,如果要使F=1,则输入ABC的取值应该为()A.ABC=000B.ABC=010C.ABC=101D.ABC=110[答案]:D22.函数描述的电路存在哪些竞争变量?()A.不纯在B.变量AC.变量BD.变量C[答案]:B23.卡诺图上每个小方格代表一个()A.最大项B.最小项C.逻辑函数的取值D.变量的取值[答案]:B24.可编程阵列逻辑简称为什么?()A.GALB.PALC.PLAD.PLD[答案]:B25.逻辑关系为“一件事情的发生是以其相反的条件为依据”的逻辑门是().A.与门B.非门C.异或门[答案]:B26.逻辑函数F(A,B,C)=AB+BC+AC的标准表达式是()A.∑m(3,5,6,7)B.∑m(0,1,2,4)∏m(1,3,5,7)C.∏m(1,3,5,7)D.∑M(0,2,4,6)[答案]:A27.逻辑函数的标准与-或表达式是由()构成的逻辑表达式.A.与项相或B.或项相与C.最小项相与D.最小项相或[答案]:C28.逻辑函数的表示方法中具有唯一性的是:()A.真值表B.表达式C.逻辑图D.状态图[答案]:A29.哪种逻辑门在“当所有输入均为0时,输出才是1”?()A.或门B.与门C.或非门D.与非门[答案]:C30.请问下列哪一项是最适合表示门延迟的时间单位?()A.nsC.msD.s[答案]:A31.如果两输入端与非门的输出z=0时,则其输入x和y的值一定是()A.至少有一个为1B.同时为1C.同时为0D.至少有一个为0[答案]:B32.如果状态A与B,C与D分别构成等效对,那么能构成状态等效类的是()A.ABB.ABCC.BCDD.ABCD[答案]:A33.若JK触发器的J=0,K=0,在CLK触发后,输出Q的状态为()A.0B.1C.不变D.与前一状态Q反相[答案]:C34.设计—个1位十进制计数器至少需要多少个触发器?()A.3个B.4个C.16个D.10个[答案]:B35.十进制19.375转换成二进制时,应为()A.10011.011B.101010.011C.10101.001D.10101.101[答案]:A36.十进制数12.75用二进制表示应为:()A.1010.1B.1100.11C.1010.011D.1100.01[答案]:B37.十进制数15用2421BCD码可以表示为().A.1111B.1001000C.11011D.10101[答案]:C38.十进制数25用8421BCD码表示为().B.100101C.100101D.10101[答案]:B39.十进制数53的余3码为().A.10110011B.1010011C.10000110D.53[答案]:C40.十进制数7的2421码为()A.111B.1010C.1011D.1101[答案]:D41.十进制数9的8421码为()A.1000B.1011C.1001D.1010[答案]:C42.四个变量可以构成多少个最小项?()A.4个B.8个C.15个D.16个[答案]:D43.四路数据选择器的输出端有:()A.1B.2C.3D.4个[答案]:A44.随机存取存储器具有()功能.A.读/写B.无读/写D.只写[答案]:A45.同步时序电路设计中,状态化简的主要目的是()A.减少电路中的触发器B.提高电路速度C.减少电路中的连线D.减少电路中的逻辑门[答案]:A46.无符号位的十六进制数减法(A9)l6-(8A)16=()A.(19)16B.(1F)l6C.(25)16D.(29)16[答案]:B47.下列几种TTL电路中,输出端可实现线与功能的电路是()A.或非门B.与非门C.异或门D.OC门[答案]:D48.下列哪一种逻辑门的输出不能并联使用?().A.TTL集电级开路门(OC门)B.TTL三态输出门C.具有推拉式输出的TTLD.CMOS三态输出门[答案]:C49.下列哪一种相或可以构成标准的与-或逻辑表达式?()A.最大项B.最小项C.或项D.与项[答案]:B50.下列哪种类型的集成电路的集成度更高?()A.CMOSB.TTLC.ECLD.都一样51.下列说法不正确的是()A.集电极开路的门称为OC门B.三态门输出端有可能出现三种状态(高阻态,高电平,低电平)C.OC门输出端直接连接可以实现正逻辑的线或运算D.利用三态门电路可实现双向传输[答案]:C52.下列选项中,()不是单稳态触发器的特点.A.有一个稳定状态,有两个暂稳状态.B.暂稳状态维持一段时间后,将自动返回稳定状态.C.暂稳状态时间的长短与触发脉冲无关,仅决定于电路本身的参数.D.在外来触发脉冲的作用下,能够由稳定状态翻转到暂稳状态.[答案]:A53.下列选项中,叙述不正确的是()A.接入滤波电容引入是消除竞争冒险的方法之一.B.引入选通脉冲不能消除竞争冒险.C.修改逻辑设计,增加冗余项是常用的消除竞争冒险的方法.D.化简电路,减少逻辑器件数目,不能消除竞争冒险.[答案]:B54.下列中规模通用集成电路中,哪一种适合用来设计一个多数表决器?()A.4位计数器74193B.4位并行加法器74153C.4位寄存器74194D.4路数据选择器74152[答案]:D55.要求RS触发器(R,S均为高电平有效)状态由0→1,其输入信号为().A.RS=01B.RS=d1C.RS=d0D.RS=10[答案]:A56.要使JK触发器在时钟作用下的次态与现态相反,JK端取值应为().A.JK=00B.JK=01C.JK=10D.JK=11[答案]:D57.一个数据选择器有3个地址输入端,最多可以有几个数据信号输出()A.3B.6C.8D.16[答案]:C58.一只四输入端或非门,使其输出为1的输入变量取值组合有()种.A.15B.8C.7D.1[答案]:D59.移位寄存器74194工作在左移串行输入方式时,S1S0的取值为()A.0B.1C.10D.11[答案]:C60.以下参数不是矩形脉冲信号的参数?()A.周期B.占空比C.脉宽D.扫描期[答案]:D二.判断题1.输出与输入没有直接的关系,输出方程中不含输入变量的是Mealy型时序电路.() [答案]:F2.“0”的补码只有一种形式.()[答案]:T3.D/A转换器是将模拟量转换成数字量.[答案]:F4.Mealy型时序电路:电路输出是输入变量与触发器状态的函数.()[答案]:T5.Moore型时序电路:电路输出仅仅是触发器状态的函数.()[答案]:T6.八路数据分配器的地址输入(选择控制)端有8个.[答案]:F7.并行加法器采用先行进位(并行进位)的目的是提高运算速度()[答案]:F8.采用奇偶校验电路可以发现代码传送过程中的所有错误.()[答案]:F9.单稳态触发器它有一个稳态和一个暂稳态.[答案]:T10.反码和补码均可实现将减法运算转化为加法运算()[答案]:F11.方波的占空比为0.5.()[答案]:T12.格雷码具有任何相邻码只有一位码元不同的特性.()[答案]:T13.化简完全确定状态表时,最大等效类的数目就是最简状态表中的状态数目[答案]:F14.卡诺图中,两个相邻的最小项至少有一个变量互反.()[答案]:T15.逻辑函数两次求反则还原,逻辑函数的对偶式再作对偶变换也还原为它本身.()[答案]:T16.任意两个不同的最小项之积,值恒为0.()[答案]:T17.若两个函数具有不同的逻辑函数式,则两个逻辑函数必然不相等.()[答案]:F18.若两个函数具有相同的真值表,则两个逻辑函数必然相等.().[答案]:T19.时序逻辑电路由组合逻辑电路和存储电路组成.()[答案]:T20.时序图,状态转换图和状态转换表都可以用来描述同一个时序逻辑电路的逻辑功能,它们之间可以相互转换.()[答案]:T21.时钟触发器仅当有时钟脉冲作用时,输入信号才能对触发器的状态产生影响.()[答案]:T22.输出与输入有直接的关系,输出方程中含输入变量的是Moore型时序电路.()[答案]:F23.数字电路中用“1”和“0”分别表示两种状态,二者无大小之分.()[答案]:T24.所有的触发器都存在空翻现象.[答案]:F25.一个存在无效状态的同步时序电路是否具有自启动功能,取决于确定激励函数时对无效状态的处理.()[答案]:T26.异或函数与同或函数在逻辑上互为反函数.().[答案]:T27.因为逻辑表达式A+B+AB=A+B成立,所以AB=0成立.()[答案]:F28.用4位二进制补码计算2+6,不产生溢出()[答案]:F29.用或非门可以实现3种基本的逻辑运算.()[答案]:T30.约束项就是逻辑函数中不允许出现的变量取值组合,用卡诺图化简时,可将约束项当作1,也可当作0.[答案]:T三.简答题1.PAL和GAL有相同的阵列结构,它们是否可以互相代换使用?为什么?[答案]:不可以,工艺不同GAL可多次编程PAL只能一次编程;GAL的输出电路结构不同.2.TTL与非门如有多余的输入端能不能将它接地,为什么?TTL或非门如有多余的输入端能不能将它接Ucc或悬空,为什么?[答案]:TTL与非门如有多余的输入端能不能将它接地,为什么?TTL或非门如有多余的输入端能不能将它接Ucc或悬空,为什么?3.TTL与非门闲置的输入端能否悬空处理?CMOS与非门呢?[答案]:TTL与非门闲置的输入端一般也不要悬空处理,但当外界干扰较小时,就可以把闲置的输入端悬空处理;而CMOS与非门闲置的输入端是不允许悬空处理的.4.对偶规则有什么用处?[答案]:可使公式的推导和记忆减少一半,有时可利于将或与表达式化简.5.格雷码的特点是什么?为什么说它是可靠性代码?[答案]:格雷码的任意两组相邻代码之间只有一位不同,其余各位都相同,它是一种循环码.这个特性使它在形成和传输过程中可能引起的错误较少,因此称之为可靠性代码.6.公式化简逻辑函数:Y(A,B,C)=∑m(0,1,2,3,4,5,6,7)[答案]:Y=17.何谓“空翻”现象?抑制“空翻”可采取什么措施?[答案]:在时钟脉冲CP=1期间,触发器的输出随输入发生多次翻转的现象称为空翻.抑制空翻的最好措施就是让触发器采取边沿触发方式.8.化简函数:F(A,B,C,D)=∑m(0,2,3,7,8,9,10,11,13,15)[答案]:F(A,B,C,D)=AD+B'D'+CD9.化简函数:F(A,B,C,D)=∑m(1,6,8,10,12,13)+∑d(0,3,5,14)[答案]:F(A,B,C,D)=AD'+ABC'+A'C'D+BCD'10.将下列的十进制数转换成二进制数:(1),8,(2),27,(3),31,(4),100[答案]:(1)(8)10=(1000)2(2)(27)10=(11011)2(3)(31)10=(11111)2(4)(100)10=(1100100)211.逻辑代数与普通代数有何异同?[答案]:都有输入,输出变量,都有运算符号,且有形式上相似的某些定理,但逻辑代数的取值只能有0和1两种,而普通代数不限,且运算符号所代表的意义不同.12.逻辑函数的三种表示方法如何相互转换?[答案]:通常从真值表容易写出标准最小项表达式,从逻辑图易于逐级推导得逻辑表达式,从与或表达式或最小项表达式易于列出真值表.。

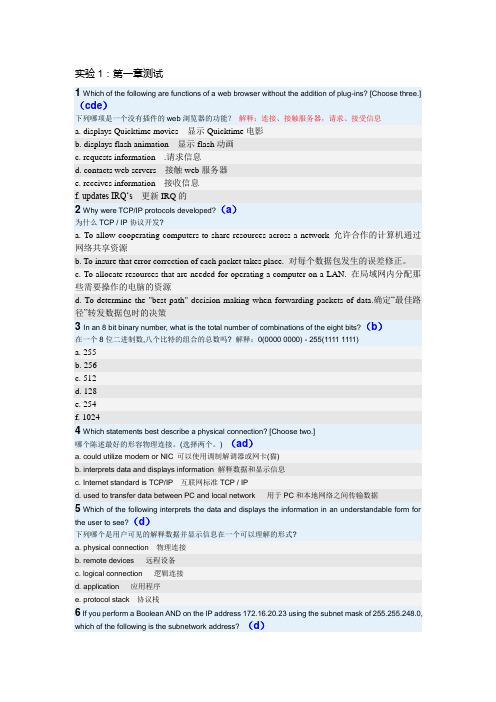

集美大学思科网络技术上级实验题目及答案翻译

实验1:第一章测试1 Which of the following are functions of a web browser without the addition of plug-ins? [Choose three.](cde)下列哪项是一个没有插件的web浏览器的功能?解释:连接、接触服务器,请求、接受信息a. displays Quicktime movies 显示Quicktime电影b. displays flash animation 显示flash动画c. requests information .请求信息d. contacts web servers 接触web服务器e. receives information 接收信息f. updates IRQ…s更新IRQ的2 Why were TCP/IP protocols developed?(a)为什么TCP / IP协议开发?a. To allow cooperating computers to share resources across a network 允许合作的计算机通过网络共享资源b. To insure that error correction of each packet takes place. 对每个数据包发生的误差修正。

c. To allocate resources that are needed for operating a computer on a LAN. 在局域网内分配那些需要操作的电脑的资源d. To determine the "best path" decision making when forwarding packets of data.确定“最佳路径”转发数据包时的决策3 In an 8 bit binary number, what is the total number of combinations of the eight bits?(b)在一个8位二进制数,八个比特的组合的总数吗? 解释:0(0000 0000) - 255(1111 1111)a. 255b. 256c. 512d. 128e. 254f. 10244 Which statements best describe a physical connection? [Choose two.]哪个陈述最好的形容物理连接。

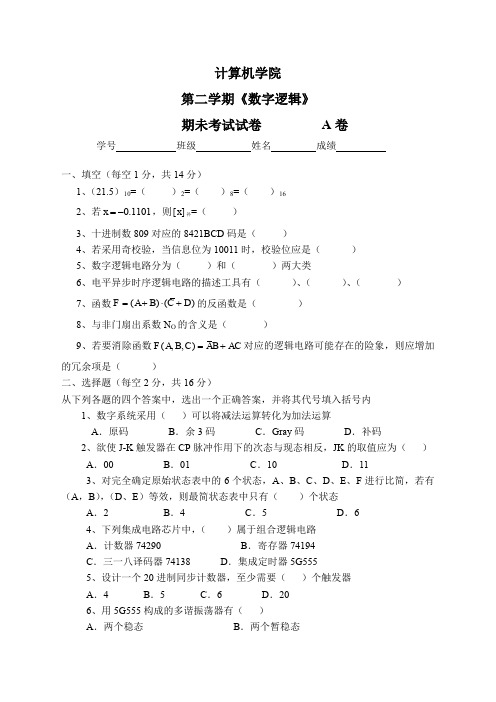

数字逻辑试卷及答案

计算机学院 第二学期《数字逻辑》 期未考试试卷 A 卷学号 班级 姓名 成绩一、填空(每空1分,共14分)1、(21.5)10=( )2=( )8=( )162、若0.1101x =-,则[]x 补=( )3、十进制数809对应的8421BCD 码是( )4、若采用奇校验,当信息位为10011时,校验位应是( )5、数字逻辑电路分为( )和( )两大类6、电平异步时序逻辑电路的描述工具有( )、( )、( )7、函数()()F A B C D =+⋅+的反函数是( )8、与非门扇出系数N O 的含义是( )9、若要消除函数(,,)F A B C AB AC =+对应的逻辑电路可能存在的险象,则应增加的冗余项是( )二、选择题(每空2分,共16分)从下列各题的四个答案中,选出一个正确答案,并将其代号填入括号内1、数字系统采用( )可以将减法运算转化为加法运算A .原码B .余3码C .Gray 码D .补码2、欲使J-K 触发器在CP 脉冲作用下的次态与现态相反,JK 的取值应为( ) A .00 B .01 C .10 D .113、对完全确定原始状态表中的6个状态,A 、B 、C 、D 、E 、F 进行比简,若有(A ,B ),(D 、E )等效,则最简状态表中只有( )个状态A .2B .4C .5D .6 4、下列集成电路芯片中,( )属于组合逻辑电路 A .计数器74290 B .寄存器74194 C .三一八译码器74138 D .集成定时器5G555 5、设计一个20进制同步计数器,至少需要( )个触发器 A .4 B .5 C .6 D .20 6、用5G555构成的多谐振荡器有( )A .两个稳态B .两个暂稳态C .一个稳态,一个暂稳态D .既没有稳态,也没有暂稳态 7、可编程逻辑阵列PLA 的与、或陈列是( )A .与阵列可编程、或阵列可编程B .与阵列不可编程、或阵列可编程C .与阵列可编程、或阵列不可编程D .与阵列不可编程、或阵列不可编程 8、最大项和最小项的关系是( )A .i i m M =B .i i m M =C .1i i m M ⋅=D .无关系 三、逻辑函数化简(6分)把(,,,)(0,1,5,14,15)(4,7,10,11,12)F A B C D m d =∑+∑化成最简与—或式 四、分析题(每小题12分,共24分)1、分析图1所示组合逻辑电路① 写出输出函数表达式 ② 列出真值表 ③ 说明电路功能2、分析图2所示脉冲异步时序逻辑电路① 写出输出函数和激励函数表达式 ② 列出次态真值表,作出状态表和状态图 ③ 说明电路功能④ 设初态2100y y =,作出x 输入4个异步脉冲后的状态y 2y 1和输出z 的波形图。

基于CBAM

电气传动2023年第53卷第9期ELECTRIC DRIVE 2023Vol.53No.9摘要:针对直流线路保护和故障测距易受非故障性雷击干扰、传统基于时域和频域特征构造的输电线路雷击干扰识别方法存在阈值难以整定和噪声鲁棒性较差的问题,提出使用深度学习方法实现雷击干扰与短路行波特征自动提取与分类,相模解耦和小波包分解后得到的电流、电压行波分量作为不同通道输入至一维卷积模块注意力模块卷积神经网络(CBAM-CNN )分类模型。

通过仿真和算例分析验证了所提模型相比传统方法具有更高的识别正确率,CBAM 能有效提升CNN 分类模型的噪声鲁棒性,同时验证了4层小波包分解与所提CBAM-CNN 模型的结合具有最佳的性能。

关键词:卷积神经网络;卷积模块注意力模块;小波包分解;直流输电线路;雷击干扰;时频分析中图分类号:TM28文献标识码:ADOI :10.19457/j.1001-2095.dqcd24321Identification Model of Lightning Interference and Short Circuit at HVDC Transmission LineBased on CBAM-CNNLIAO Zhiwei ,ZHUANG Jing ,WANG Bowen ,ZHENG Guangyu ,XIE Xunkai(School of Electric Power ,South China University of Technology ,Guangzhou 510641,Guangdong ,China )Abstract:Aiming at the problems that high voltage direct current (HVDC )transmission line protection and fault location are vulnerable to lightning interference ,and the traditional lightning interference identification methods of transmission line based on time-domain and frequency-domain features exist the problems of difficult threshold setting and poor noise robustness ,a deep learning method was proposed to extract the characteristics of lightning interference and short-circuit traveling wave and classify automatically.After phase mode decoupling and wavelet packet decomposition ,the current and voltage traveling wave components were input into the one-dimensional convolutional block attention module convolutional neural network (CBAM -CNN )classification model as different channels.Through simulation and example analysis ,it is verified that the proposed model shows higher recognition accuracy than the traditional methods ,and the CBAM can effectively improve the noise robustness of CNN classification model.At the same time ,it is verified that the combination of four-layer wavelet packet decomposition and the proposed CBAM -CNN model has the best performance.Key words:convolutional neural network (CNN );convolutional block attention module (CBAM );wavelet packet decomposition (WPD );DC transmission line ;lightning interference ;jonit time-frequency analysis (JTFA )基金项目:国家自然科学基金(52077082)作者简介:廖志伟(1973—),男,博士,副教授,Email :***************.com基于CBAM-CNN 的直流线路雷击干扰与短路识别模型廖志伟,庄竞,王博文,郑广昱,谢汛恺(华南理工大学电力学院,广东广州510641)高压直流输电(high voltage direct current ,HVDC )工程的输电线路较长,雷击和短路故障频发。

《人工智能》课程习题

《人工智能》课程习题第一章绪论1-1. 什么是人工智能?试从学科和能力两方面加以说明。

1-2. 在人工智能的发展过程中,有哪些思想和思潮起了重要作用?1-3. 为什么能够用机器(计算机)模仿人的智能?1-4. 现在人工智能有哪些学派?它们的认知观是什么?1-5. 你认为应从哪些层次对认知行为进行研究?1-6. 人工智能的主要研究和应用领域是什么?其中,哪些是新的研究热点?第二章知识表示方法2-1状态空间法、问题归约法、谓词逻辑法和语义网络法的要点是什么?它们有何本质上的联系及异同点?2-2设有3个传教士和3个野人来到河边,打算乘一只船从右岸渡到左岸去。

该船的负载能力为两人。

在任何时候,如果野人人数超过传教士人数,那么野人就会把传教士吃掉。

他们怎样才能用这条船安全地把所有人都渡过河去?再定义描述过河方案的谓词:L-R(x, x1, y, y1,S):x1个修道士和y1个野人渡船从河的左岸到河的右岸条件:Safety(L,x-x1,y-y1,S’)∧Safety(R,3-x+x1,3-y+y1,S’)∧Boat(L,S)动作:Safety(L,x-x1,y-y1,S’)∧Safety(R,3-x+x1,3-y+y1,S’)∧Boat(R,S’)R-L (x, x1, y, y1,S):x2个修道士和y2个野人渡船从河的左岸到河的右岸条件:Safety(R,3-x-x2,3-y-y2,S’)∧Safety(L,x+x2,y+y2,S’)∧Boat(R,S)动作:Safety(R,3-x-x2,3-y-y2,S’)∧Safety(L,x+x2,y+y2,S’)∧Boat(L,S’)(2) 过河方案Safety(L,3,3,S0)∧Safety(R,0,0,S0)∧Boat(L,S0)L-R(3, 1, 3, 1,S0) L-R(3, 0, 3, 2,S0)Safety(L,2,2,S1)∧Safety(R,1,1,S1)∧Boat(R,S1)Safety(L,3,1,S1’)∧Safety(R,0,2,S1’)∧Boat(R,S1’)R-L (2, 1, 2, 0,S1) R-L (3,0, 1, 1,S1’)Safety(L,3,2,S2)∧Safety(R,0,1,S2)∧Boat(L,S2)L-R(3, 0, 2, 2,S2)Safety(L,3,0,S3)∧Safety(R,0,3,S3)∧Boat(R,S3)R-L (3, 0, 0, 1,S3)Safety(L,3,1,S4)∧Safety(R,0,2,S1)∧Boat(L,S4)L-R(3, 2, 1, 0,S4)Safety(L,1,1,S5)∧Safety(R,2,2,S5)∧Boat(R,S5)R-L (1, 1, 1, 1,S5)Safety(L,2,2,S6)∧Safety(R,1,1,S6)∧Boat(L,S6)L-R(2, 2, 2, 0,S6)Safety(L,0,2,S7)∧Safety(R,3,1,S7)∧Boat(R,S7)R-L (0, 0, 2, 1,S7)Safety(L,0,3,S8)∧Safety(R,3,0,S8)∧Boat(L,S8)L-R(0, 0, 3, 2,S8)Safety(L,0,1,S9)∧Safety(R,3,2,S9)∧Boat(R,S9)R-L (0, 1, 1, 0,S9)Safety(L,1,1,S10)∧Safety(R,2,2,S10)∧Boat(L,S10)2-3利用图2.3,用状态空间法规划一个最短的旅行路程:此旅程从城市A开始,访问其他城市不多于一次,并返回A。

电子信息面试问题大全

电子信息、通信、电类专业将会遇到的面试题大全!精!看了让人大吃一惊...模拟电路1、基尔霍夫定理的内容是什么?(仕兰微电子)基尔霍夫电流定律是一个电荷守恒定律,即在一个电路中流入一个节点的电荷与流出同一个节点的电荷相等.基尔霍夫电压定律是一个能量守恒定律,即在一个回路中回路电压之和为零.2、平板电容公式(C=εS/4πkd)。

(未知)3、最基本的如三极管曲线特性。

(未知)4、描述反馈电路的概念,列举他们的应用。

(仕兰微电子)5、负反馈种类(电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈);负反馈的优点(降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用)(未知)6、放大电路的频率补偿的目的是什么,有哪些方法?(仕兰微电子)7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。

(未知)8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。

(凹凸)9、基本放大电路种类(电压放大器,电流放大器,互导放大器和互阻放大器),优缺点,特别是广泛采用差分结构的原因。

(未知)10、给出一差分电路,告诉其输出电压Y+和Y-,求共模分量和差模分量。

(未知)11、画差放的两个输入管。

(凹凸)12、画出由运放构成加法、减法、微分、积分运算的电路原理图。

并画出一个晶体管级的运放电路。

(仕兰微电子)13、用运算放大器组成一个10倍的放大器。

(未知)14、给出一个简单电路,让你分析输出电压的特性(就是个积分电路),并求输出端某点的rise/fall时间。

(Infineon笔试试题)15、电阻R和电容C 串联,输入电压为R和C之间的电压,输出电压分别为C上电压和R 上电压,要求制这两种电路输入电压的频谱,判断这两种电路何为高通滤波器,何为低通滤波器。

当RC<< period - setup ? hold16、时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。

Application Notes on Direct Time-Domain Noise Analysis using Virtuoso Spectre

Device Noise Models

Device noise models typically have a number of independent noise sources connected to the device terminals or internal nodes. Each noise source is characterized by its noise spectral density, which is a function of bias voltage and/or frequency. Most often used device noise models are: Thermal noise of a resistor with constant spectral density

July 2006 1 Version 1.0

Application Notes on Direct Time-Domain Noise Analysis using Virtuoso Spectre

signal ratio is large, and operating point, or periodic state of interest may be affected by the noise. This is a very costly approach. Device noise models need to be evaluated and random noise sources need to be generated at each times step of transient analysis. Time step is also forced to be uniformly small as noise bandwidth is typically larger than circuit bandwidth. In addition, a large number of repetitive simulations need to be performed, or the simulation has to span large number of periodic cycles in order to draw meaningful statistical characteristics. The necessity of direct noise analysis in time domain has been recognized by various researchers and commercial EDA companies. The key difference is how to model noise sources in time domain that can be easily plugged into transient analysis. Various approaches have been published so far. Bolcato, at al [1] models each noise source as a sum of sinusoids over the frequency range of interest, with random phase, and with amplitude equals to the given noise power spectral density. Recently from [2], it was shown that the magnitude of noise signal in frequency domain is also a random number with Rayleigh probability distribution around given power spectral density, thus random noise spectrum can be properly generated in the frequency domain. However, both noise modeling approaches are CPU intensive -- as the time domain noise signals are obtained using inverse Fourier transformation, and memory intensive -- as all time domain noise sources have to be pre-calculated and stored over the full duration of transient analysis. In the following sections, we will first summarize the typical device noise models -- thermal, shot, flicker, and noise data table. Then we will describe a different way of providing time-domain white noise sources and its extension to handle frequency dependent noise models. Our approach satisfies stricter performance and capacity requirements. As a result, CPU time used for noise signal generation is much less than that for device evaluation, additional allocated memory is much less than that used for devices and matrix solver. Finally and very importantly, device noise code developed in existing Spectre CMI devices and Verilog-A modules is re-used for time-domain noise modeling, no model code change is ever needed.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ACircuitSATSolverWithSignalCorrelationGuidedLearningFengLu,Li-C.Wang,andKwang-TingChengRicC-YHuangDepartmentofElectricalandComputerEngineeringVerplexSystems,Inc.UniversityofCalifornia,SantaBarbara93106-9560,USAMilpitas,California93035,USA

Abstract—BooleanSatistifiabilityhasattractedtremendousresearcheffortinrecentyears,resultinginthedevelopmentsofvariousefficientSATsolverpackages.Basedupontheirdesignar-chitectures,researchershavetriedtodevelopbetterheuristicstofurtherimproveitsefficiency,byeitherspeedinguptheBooleanConstraintPropagation(BCP)procedureorfindingabetterdeci-sionordering(orboth).Inthispaper,weproposeanentirelydif-ferentSATsolverdesignconceptthatiscircuit-based.Oursolverisabletoutilizecircuittopologicalinformationandsignalcorrela-tionstoenforceadecisionorderingthatismoreefficientforsolv-ingcircuit-basedSATprobleminstances.Inparticular,forunsat-isfiablecircuitexamples,oursolverisabletoachievefrom2xuptomorethan75xspeedupoverastate-of-the-artSATsolver.I.IntroductionTheBooleanSatistifiability(SAT)Problemhasbeenextensivelystudiedinrecentyears.PopularSATsolvers[1,2,3,4]areof-tendesignedbasedupontheConjunctiveNormalForm(CNF)rep-resentation.FormanyapplicationsinCAD,applyingSATtosolveacircuit-orientedproblemoftenrequirestransformationofthecircuitgate-levelnetlistintoitscorrespondingCNFformat[5].Inthecircuit-to-CNFtransformation,thetopologicalorderingamongtheinternalsignalsisnolongerthere.Allsignalsbecome(input)variablesintheCNFformat.Forsolvingcircuit-orientedCADproblems,circuitstructuralinfor-mationcanbeveryuseful.Forexample,researchershavedevelopedvariousSATsolversabletoutilizecircuit-relatedinformationtospeedupthestate-of-the-artSATsolverperformance[6,7,8].Inthispaper,wepresentacircuit-basedSATsolverthatutilizessignaltopologicalorderingandsignalcorrelationstoidentifyanef-fectivedecisionorderingintheSATsearchprocess.Oursolverdesignfollowsthreekeyideas:Ifagroupofsignalscanbeidentifiedinadvancethattheyarehighlycorrelated,theninthesolver’sdecisionvariableselec-tion,theyshouldbegroupedtogether.WhensolvingaSATproblemoriginatedfromacircuit,some-timeswecansolvetheproblemmoreeasilybyfollowingthetopologicalstructure.Thismeansthatmoreefficiencygaincanbeobtainedbypre-selectingasetof”proper”signalsinthecir-cuit,andexplicitlyenforcingtheSATsolvingprocesstofollowtheirtopologicalorderingtosolvetheproblem.Whenmakingthedecisionsofvalueassignmentstosignals,itismoreeffectiveforthesolvertoselectthosevaluesthataremorelikelytocauseconflicts.Therefore,ifweknowhowcircuitsignalsarecorrelatedbeforehand,thatinformationcanbeusedtoguidethevalueassignmentsinthesolver.Bycombiningthethreeideasabove,weimplementedacircuit-basedSATsolverwhosedecisionorderingisguidedbywhatwecallthesignalcorrelationlearning.Oursolverincludestwotypesofthesignalcorrelationlearning:implicitlearningandexplicitlearn-ingwhichdifferintheirwaystoaffectthedecisionordering.Inim-plicitlearning,correlatedsignalsaregroupedtogetherinthedeci-sionvariableselection,andcorrelationinformationisusedtoguidethesolvertoassignvaluesthataremorelikelytocauseconflicts.Inexplicitlearning,asetofKsignalss1

sKarepre-selected

baseduponsignalcorrelations.Thedecisionorderingonthesesig-nalsareenforcedbytheirtopologicalorder.Valuesassignmentss1v1skvKarepre-determinedinsuchawaythatsolv-ingeachsub-problem”sivi”(1iK)islikelytocauseconflicts.

Moreover,thesolverstartsbyexplicitlyfollowingthetopologicalor-dertosolveeachsub-problemins1v1

skvK,thenfollowed

bysolvingtheoriginalSATproblem.Wecallthisapproachtheincre-mentallearn-from-conflictstrategy.Forunsatisfiablecircuitexamples,withimplicitlearning,oursolverwasabletoachieveonaverage3-7xspeedupoverthestate-of-the-artSATsolverZChaff[1,2].Withexplicitlearning,thisper-formancegaincouldfurtherbeenhancedfrom13xuptomorethan75x.ForsatisfiablecasesthatcontainCNFformatintheirprobleminputs,ourcircuit-basedsolverwasnotabletotakethefulladvan-tageofthecircuitstructuralinformation.Asaresult,withimplicitlearning,roughly2xspeedupwasobtained,andwithexplicitlearn-ing,onlycomparableresultswereachieved.Wediscussourcircuit-basedsolverimplementationandtheexperimentalresultsintherestofthepaper.Therestofthepaperisorganizedasthefollowing.InSectionII,weexplainthekeyideasinmoredetail.SectionIIIdescribesoursimulation-basedmethodtoidentifysignalcorrelations.SectionIVpresentsthemethodforimplicitlearning.Detailofoursolverim-plementationisalsodiscussedthere.InSectionV,wepresenttheexplicitlearningmethodanddiscussresultsonbothsatisfiableandunsatisfiablecases.SectionVIconcludesthepaper.