The composite DDS-A new direct digital synthesizer architecture,

数字频率合成器的外文翻译

英文原文Modulating Direct Digital Synthesizer In the pursuit of more complex phase continuous modulation techniques, the control of the output waveform becomes increasingly more difficult with analog circuitry. In these designs, using a non-linear digital design eliminates the need for circuit board adjustments over yield and temperature. A digital design that meets these goals is a Direct Digital Synthesizer DDS. A DDS system simply takes a constant reference clock input and divides it down a to a specified output frequency digitally quantized or sampled at the reference clock frequency. This form of frequency control makes DDS systems ideal for systems that require precise frequency sweeps such as radar chirps or fast frequency hoppers. With control of the frequency output derived from the digital input word, DDS systems can be used as a PLL allowing precise frequency changes phase continuously. As will be shown, DDS systems can also be designed to control the phase of the output carrier using a digital phase word input. With digital control over the carrier phase, a high spectral density phase modulated carrier can easily be generated.This article is intended to give the reader a basic understanding of a DDS design, and an understanding of the spurious output response. This article will also present a sample design running at 45MHz in a high speed field programmable gate array from QuickLogic.A basic DDS system consists of a numerically controlled oscillator (NCO) used to generate the output carrier wave, and a digital to analog converter (DAC) used to take the digital sinusoidal word from the NCO and generate a sampled analog carrier. Since the DAC output is sampled at the reference clock frequency, a wave form smoothing low pass filter is typically used to eliminate alias components. Figure 1 is a basic block diagram of a typical DDS system design.The generation of the output carrier from the reference sample clock input is performed by the NCO. The basic components of the NCO are a phase accumulator and a sinusoidal ROM lookup table. An optional phase modulator can also be include in the NCO design. This phase modulator will add phase offset to the output of the phase accumulator just before the ROM lookup table. This will enhance the DDS system design by adding thecapabilities to phase modulate the carrier output of the NCO. Figure 2 is a detailed block diagram of a typical NCO design showing the optional phase modulator.FIGURE 1: Typical DDS System.FIGURE 2: Typical NCO Design.To better understand the functions of the NCO design, first consider the basic NCO design which includes only a phase accumulator and a sinusoidal ROM lookup table. The function of these two blocks of the NCO design are best understood when compared to the graphical representat ion of Euler’s formula ej wt = cos( wt) + jsin( wt). The graphical representation of Euler’s formula, as shown in Figure 3, is a unit vector rotating around the center axis of the real and imaginary plane at a velocity of wrad/s. Plotting the imaginary component versus time projects a sine wave while plotting the real component versus time projects a cosine wave. The phase accumulator of the NCO is analogous, or could be considered, the generator of the angular velocity component wrad/s. The phase accumulator is loaded, synchronous to the reference sample clock, with an N bit frequency word.This frequency word is continuously accumulated with the last sampled phase value by an N bit adder. The output of the adder is sampled at the reference sample clock by an N bit register. When the accumulator reaches the N bit maximum value, the accumulator rolls over and continues. Plotting the sampled accumulator values versus time produces a saw tooth wave form as shown below in Figure 3.FIGURE 3 Euler’s Equation Re presented GraphicallyThe sampled output of the phase accumulator is then used to address a ROM lookup table of sinusoidal magnitude values. This conversion of the sampled phase to a sinusoidal magnitude is analogous to the projection of the real or imaginary component in time. Since the number of bits used by the phase accumulator determines the granularity of the frequency adjustment steps, a typical phase accumulator size is 24 to 32 bits. Since the size of the sinusoidal ROM table is directly proportional to the addressing range, not all 24 or 32 bits of the phase accumulator are used to address the ROM sinusoidal table. Only the upper Y bits of the phase accumulator are used to address the sinusoidal ROM table, where Y < N bits and Y is typically but not necessarily equal to D, and D is the number of output magnitude bits from the sinusoidal ROM table.Since an NCO outputs a carrier based on a digital representation of the phase and magnitude of the sinusoidal wave form, designers have complete control overfrequency, phase, and even amplitude of the output carrier. By adding a phase port and a phase adder to the basic NCO design, the output carrier of the NCO can be M array phase modulated where M equals the number of phase port bits and where M is less than or equal to the Y number of bits used to address the sinusoidal ROM table. For system designs that require amplitude modulation such as QAM, a magnitude port can be added to adjust the sinusoidal ROM table output. Note that this port is not shown in Figure 2 and that this feature is not demonstrated in the sample QuickLogic FPGA design. Finally, frequency modulation is a given with the basic NCO design. The frequency port can directly adjust the carrier output frequency. Since frequency words are loaded into the DDS synchronous to the sample clock, frequency changes are phase continuous.Although DDS systems give the designer complete control of complex modulation synthesis, the representation of sinusoidal phase and magnitude in a non-linear digital format introduces new design complexities. In sampling any continuous-time signal, one must consider the sampling theory and quantization error.To understand the effects of the sampling theory on a DDS system, it is best to look at the DDS synthesis processes in both the time and frequency domain. As stated above, the NCO generates a sinusoidal wave form by accumulating the phase at a specified rate and then uses the phase value to address a ROM table of sinusoidal amplitude values. Thus, the NCO is essentially taking a sinusoidal wave form and sampling it with the rising or falling edge of the NCO input reference sampling clock. Figure 4 shows the time and frequency domain of the NCO processing. Note that this representation does not assume quantization.Based on the loaded frequency word, the NCO produces a set of amplitude output values at a set period. The frequency domain representation of this sinusoid is an impulse function at the specified frequency. The NCO, however, outputs discrete digital samples of this sinusoid at the NCO reference clock rate. In the time domain, the NCO output is a function of the sampling clock edge strobes multiplied by the sinusoid wave form producing a train of impulses at the sinusoid amplitude. In the frequency domain, the sampling strobes of the reference clock produce a train of impulses at frequencies of K times the NCO clock frequency where K = ... - 1, 0, 1, 2 .... Since the sampling clock was multiplied by the sinusoid in the time domain, the frequency domain components of the sinusoid and the sampling clock need to be convolved to produce the frequency domain representation of the NCO output.The frequency domain results are the impulse function at the fundamental frequency of the sinusoid and the alias impulse functions occurring at K times the NCO clock frequency plus or minus the fundamental frequency. The fundamental and alias component occur at:K*Fclk - FoutK*Fclk + FoutWhere K = ... -1, 0 , 1, 2 ..... and K = 0 is the NCO sinusoid fundamental frequencyFout is the specified NCO sinusoid output frequencyFclk is the NCO reference clock frequencyFIGURE 4 NCO Output Representation Time and Frequency DomainThe DAC of the DDS system takes the NCO output values and translates these values into analog voltages. Figure 4 shows the time and frequency domain representations of the DAC processing starting with the NCO output. The DAC output is a sample and hold circuit that takes the NCO digital amplitude words and converts the value into an analog voltage and holds the value for one sample clock period. The time domain plot of the DAC processing is the convolution of the NCO sampled output values with a pulse of one sample clock period. The frequency domain plot of the sampling pulse is a sin(x)/x function with the first null at the sample clock frequency. Since the time domain was convolved, the frequency domain is multiplied. This multiplication dampens the NCO output with the sin(x)/x envelope. This attenuation at the DAC output can be calculated as follows and a sample output spectrum is shown in Figure 5:Atten(F) = 20log[(sin(pF/Fclk)/pF/Fclk)] Where F is the output frequency Fclk is the sample clock frequencyFIGURE 5: DAC Output Representation in Time and Frequency Domain Aside from the sampling theory, the quantization of the real values into digital form must also be considered in the performance analysis of a DDS system. The spurious response of a DDS system is primarily dictated by two quantization parameters. These parameters are the phase quantization by the phase accumulator and the magnitude quantization by the ROM sinusoidal table and the DAC.As mentioned above, only the upper Y bits of the phase accumulator are used to address the ROM lookup table. It should be noted, however, that using only the upper Y bits of the phase accumulator introduces a phase truncation. When a frequencyword containing a non-zero value in the lower (N-Y-1:0) bits is loaded into the DDS system, the lower non-zero bits will accumulate to the upper Y bits and cause a phase truncation. The frequency at which the phase truncation occurs can be calculated by the following:Ftrunc = FW(N-Y- 1:0)/2N-Y* Fclk.A phase truncation will periodically (at the Ftrunc rate) phase modulate the output carrier forward 2p/28 to compensate for frequency word granularity greater than 2Y. The phase jump caused by the accumulation of phase truncated bits produces spurs around the fundamental.These spurs are located plus and minus the truncation frequency from the fundamental frequency and the magnitude of the spurs will be - 20log(2Y)dBc. A sample output of a phase truncation spur is shown in Figure 5.In a typical NCO design, the ROM sinusoidal table will hold a ¼ sine wave (0 , p/2) of magnitude values. The ROM table is generated by taking all possible phase value addresses and map to a real magnitude sine value rounded to the nearest D bits. Thus, the maximum error output is ±- ½ LSB giving a worst case spur of -20log(2D)dBc.Like the NCO ROM table, a DAC quantizes the digital magnitude values. A DAC, however, outputs an analog voltage corresponding to the digital input value. When designing the NCO sinusoidal ROM table, one should take some empirical data on the DAC linearity to better understand the interaction between the ROM table and the DAC. The quantization for a DAC is specified against an ideal linear plot of digital input versus analog output. Two linearity parameters, differential and integral linearity, are used to specify a DAC’s performance.Differential linearity is the output step size from bit to bit. A DAC must guarantee a differential linearity of a maximum 1 LSB. When an input code is increased, the DAC output must increase. If the DAC voltage does not increase versus an increase digital input value, the DAC is said to be missing codes. Thus, a 10 bit DAC that has a differential linearity of greater that 1 LSB is only accurate to 9 or less bits. The number of accurate output bits will specify the DDS spurious performance as -20log(2dl) where dl is the number differential linear bits..Integral linearity is a measure of the DAC’s overall linear performance versus an ideal linear straight line. The straight line plot can be either a “best straight line” where DC offsets are possible at both the min and max outputs of the DAC, or thestraight line can cross the end points of the min and max output values. A DAC will tend to have a characteristic curve that is traversed over the output range. Depending on the shape and symmetry (symmetry about the half way point of the DAC output) of this curve, output harmonics of the DDS fundamental output frequency will be produced. As these harmonics approach and cross the Nyquist frequency of Fclk/2, the harmonics become under sampled and reflect back into the band of interest, 0 to Fclk/2. This problem is best illustrated by setting the NCO output to Fclk/4 plus a slight offset. The third harmonic will fall minus 3 folds the small offset from the fundamental and the second harmonic will cross the Nyquist frequency by 2 folds the small offset leaving a reflected image back in the band of interest A sample plot of this frequency setup is shown in Figure 5.Other DAC characteristic that will produce harmonic distortion is any disruption of the symmetry of the output wave form such as a different rise and fall time. These characteristics can typically be corrected by board components external to the DAC such as an RF transformer, board layout issues, attenuation pads etc.Given the complexities of the DDS system, engineers should consider implementing the design using separate devices for the numerically controlled oscillator, the digital to analog converter, and the low pass filter. This approach allows for signal observation at many points in the system, yet is compact enough to be practical as an end-solution. Alternatively, the discrete implementation can serve as a prototyping vehicle for a single-chip mixed signal ASIC.The author developed a version of the design using a Harris HI5721 evaluation board for the DAC. The NCO at the heart of the DDS design, and a random generator to test signal modulation, was implemented into about 65% of a QuickLogic field programmable gate array (FPGA). This FPGA, a QL16x24B 4000-gate device, was chosen for its high performance, ease-of-use, and powerful development tools.The NCO design included following:Developed in Verilog with the 8 bit CLA adder schematiccaptured and net listed to Verilog32 bit frequency word input32 phase accumulator pipelined over 8 bits8 bit phase moudulation word input8 bit sine ROM look-up tableThe design was described mostly in Verilog, with an 8 bit carry look ahead addermodified from QuickLogic’s macro library netlisted to Verilog. The whole design cycle was less than four days (two days to describe the design and a day and a half to prototype the hardware). Everything worked perfectly the first time, with the design running at an impressive 45MHz as predicted by the software simulation tools.Plots used in the article to illustrate DDS performance parameters were provided from the test configuration.Figure 6 below shows the external IO interface to the NCO design .The function of each signal is described in the following table.Signal Function TableFREQWORD[31:0] This input is the frequency control word to the NCO. This word controls the phase accumulator rate, and thus, the output frequency of the DACOUT sinusoidal wave form. The output carrier frequency is calculated by the following :PHASEWORD[7:0] This input is the phase modulation control word to the NCO. This word controls the phase offset following the phase accumulator. This phase offset is used to phase modulate the output carrier.FWWRN This input is the low asserted frequency word write strobe. This strobe input registers the FREQWORD input on the rising edge. This strobe can be asynchronous to the SYSCLK.SYSCLK This is the reference system clock input to the NCO. This clock is the sampling clock of the output carrier.PNCLK This input is the pseudo-noise generator clock input. This clock sets the data rate of the I and Q data outputs.RESETN This input is a low asserted global reset. When asserted, the internal phase and frequency word registers are cleared stopping the output carrier at 0 radians.DACOUT[7:0] This output is the sinusoidal DAC amplitude word. This word is valid on the rising edge of the DACCLK. The sinusoidal wave form output is represented by the following :f(t) = sin(2pFout(t) + Pout)DACCLK This output is the DAC clock strobe. This clock is the SYSCLK feed back to an output pin compensating for the latency of the NCO IO pins. The DACOUT amplitude words will be valid on the rising edge of the DACCLK.SIN This output is a single bit digital sine wave output. This sine wave output comes from the MSB of the phase accumulator. The output frequency of this pin is controlled by the frequency word input.COS This output is a single bit digital cosine wave output. This cosine wave output comes form the MSB and next most significant bit of the phase accumulator. The output frequency of this pin is controlled by the frequency word input.MSIN This output is a single bit digital sine wave output. This sine wave output comes from the MSB of the phase modulator. The output frequency of this pin is controlled by the frequency word input and phase offset bythe phase word input. This sine wave output is the same as the SIN output with a phase offset of plus 2p/28 * PHASEWORD.MCOS This output is a single bit digital cosine wave output. This cosine wave output comes form the MSB and next most significant bit of the phase modulator. The output frequency of this pin is controlled by the frequency word input and the phase offset by the phase word input. This cosine wave outputis the same as the COS output with a phase offset of plus 2p/28 * PHASEWORD.IDATA This output is a 25 - 1 pseudo noise random pattern. This output is not a functional part of the NCO design but used to demonstrate phasemodulation using the phase port.QDATA This output is a 25 - 1 pseudo noise random pattern. This output is not a functional part of the NCO design but used to demonstrate phase modulation using the phase port.Figure 6: The External IO InterfaceTop Level (dds.v)The top level of the NCO design instantiates the functional blocks of the NCO design and the PN generator block.PN Generator (pngen.v)This module is not part of the NCO design but is used to produce a sample random data pattern to modulate the carrier output. This module uses the PNCLK input to clock two Gold code 5 bit PN generators. The outputs of the PN generators are IDATA and QDATA outputs.The lower level block of this NCO design consist of a synchronous frequencyword input register, a synchronous phase word input register, a 32 bit pipe lined phase accumulator, an 8 bit phase adder, and a sin lockup table. A detailed description of each of the NCO blocks and the PN generator are provided in the following sections.Load Frequency Word (loadfw.v)The load frequency word block is a synchronizing loading circuit. The FREQWORD[31:0] input drives a the data input to the 32 bit fwreg register that is sampled on the rising edge of the FWWRN write strobe. The FWWRN strobe also drives the data input to a metastable flip flop fwwrnm that is used in conjunction with a synchronous register fwwrns to produce a FWWRN rising edge strobe. This rising edge strobe loadp1 is then piped for an additional 3 clock cycles producing the load strobes loadp2, loadp3, and loadp4. The load strobes are used to signal when to update the synchronous pipe line 8 bit registers pipefw1, pipefw2, pipefw3, and pipefw4 to the sampled frequency word content. The pipe line registers are concatenated to produce the 32 bit synchronous frequency word output SYNCFREQ[31:0] that is staggered to compensate for the 32 bit pipe lined phase adder.Phase Word Accumulator (phasea.v)The phase accumulator block is a 32 bit accumulator that is pipe lined in 8 bit sections. This module instanciates a schematic captured carry lock ahead CLA adder that has a carry in and carry out port. The synchronous frequency word, staggered to match the pipe lined accumulator, is loaded into the B input of the CLA adders. The sum output of the CLA adders are registered in the pipe registered with the output tied back to the A input of the CLA adders. The carry output of the CLA adders is registered in the pipec registers with the output tied to the next most significant CLA adder carry input. The most significant sum output register pipe4 is assigned to the PHASE output port giving a phase value quantized to 8 bits. A digital sine and cosine value is also calculated from the pipe4 register and brought out of the chip as SIN and COS.Load Phase Word (loadpw.v)The load phase word block is a synchronizing loading circuit. The PHASEWORD[7:0] input drives the data input to the 32 bit pwreg register that is sampled on the rising edge of the PWWRN write strobe. The PWWRN strobe also drives the data input to a metastable flip flop pwwrnm that is used in conjunction with a synchronous register pwwrns to produce a FWWRN rising edge strobe. This risingedge strobe load is used to signal when to update the synchronous phase word register phswd. The phswd register is assigned to the synchronous phase word output SYNCPHSWD[7:0].Phase Modulator (phasemod.v)The phase modulator block is used to phase offset the phase accumulator 8 bit quantized output with the synchronous phase word from the load phase word block. This module instantiates a CLA adder with the A input tied to the synchronous phase output and the B input tied to the phase accumulator output. The sum output of the adder is registered in the mphsreg register and assigned to the MODPHASE output port. A modulated version of the sine and cosine values are calculated and brought out of the chip as MSIN and MCOS.Sine Lockup (sinlup.v)This module takes the modulated phase value form the phase modulator block and translated the quantized 8 bit value into a sine wave form amplitude value quantized to 8 bits. The translation from phase to amplitude is performed by a sine ROM table that in instantiated in this module. The ROM table is reduced to a ¼ of the symmetrical sine wave form and the MSB of the sine wave form is equivalent to the modulated phase input.This module performs the calculations to reconstruct a complete period of the sine wave form from the ¼ representation of the ROM table and the MSB of the modulated phase input. To better understand the processing of this module, consider the following. The modulated phase value is a 0 to 2p value quantized to 8 bits 2p/28. The quantized value for p/2, p, 3p/2, and 2p are 0x3F, 0x7F, 0xBF, and 0xFF. The amplitude values for 0 to p/2 is stored in the ROM table. The amplitude values for p/2 to p are the ROM table output in the reverse order. The amplitude values for p to 3p/2 are the same output as the amplitude value from 0 to p/2 with the output from the ROM table inverted. Finally the amplitude value for 3p/2 to 2p are the same as for p to 3p/2 with the ROM table accessed in reverse.This module manages the address values to the ROM table and the amplitude outputs to form the complete period of the sine wave form. The first process of generating the sine wave function is the addressing of the ROM table such that phase angles p/2 to p and 3p/2 to 2p are addressed in the reverse order. Reverse addressing is accomplished by simply inverting the ROM table address input vector. The phase modulated address input is inverted when the MODPHASE[6] is one and is then registered in the phaseadd register. The phase address is used to address the ROM sinetable with the output registered in the qwavesin_ff register. To construct the negative amplitude values of the sine wave form, the MSB of the modulate phase word input is registered twice in modphase_msb1_ff and modphase_msb2_ff, compensating for the two cycle latency of the phaseadd and qwavesin_ff registers. The delayed MSB bit is used to invert the ROM table output when one. The altered ROM table output and the invert of the delayed modulated phase word MSB are finally registered in by the dac_ff register and then assigned to the DACOUT output port.Sine ROM Table (romtab.v)This module is the sine wave form ROM table. This table converts the phase word input to a sine amplitude output. To conserve area, only ¼ of the symmetrical sine wave form is stored in the ROM. The sine values stored in this table are the 0 to p/2 unsigned values quantized to 8 bits. Thus, the ROM table requires a 6 bit phase address input and outputs a 7 bit amplitude output. The sinlup module processes the phase and amplitude values to produce a complete sine period.Dan Morelli has over 9 years of design and management experience. His areas of expertise include spread spectrum communications (involving GPS, TDRSS, and 802.11), PC chip set and system architecture, cell library development (for ECL devices) and ASIC development. He has been published and has multiple patents awarded and pending. Dan currently works for Accelent Systems Inc., an electronic design consulting company, where he is a founder and the VP of Engineering.中文译文数字频率合成器在探讨许多复杂的相位连续的调制技术中,对模拟电路中输出波形的控制已经越来越困难。

详细设计方案_DDS

DDS详细设计方案1.DDS简介:DDS同DSP(数字信号处理)一样,是一项关键的数字化技术。

DDS 是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。

与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

一块DDS芯片中主要包括频率控制寄存器、高速相位累加器和正弦计算器三个部分(如Q2220)。

频率控制寄存器可以串行或并行的方式装载并寄存用户输入的频率控制码;而相位累加器根据频率控制码在每个时钟周期内进行相位累加,得到一个相位值;正弦计算器则对该相位值计算数字化正弦波幅度(芯片一般通过查表得到)。

DDS芯片输出的一般是数字化的正弦波,因此还需经过高速D/A转换器和低通滤波器才能得到一个可用的模拟频率信号。

2.DDS规格:Xxx3.实现原理DDS的核心部分是相位累加器,相位累加器有一个累加器和相位寄存器组成,它的作用是再基准时钟源的作用下进行线性累加,当产生溢出时便完成一个周期,即DDS的一个频率周期。

其中频率字的位宽为K位,作为累加器的一个输入,累加器的另一个输入端位宽为N位(N>K),每来一个时钟,频率字与累加器的另一个输入相加的结果存入相位寄存器,再反馈给累加器,这相当于每来一个时钟,相位寄存器的输出就累加一次,累加的时间间隔为频率字的时间,输入加法器的位宽为(N-K)位,它与同样宽度的相位控制字相加形成新的相位,并以此作为查找表的地址。

每当累加器的值溢出一次,输入加法器的值就加一,相应的,作为查找表的地址就加一,而查找表的地址中保存波形的幅度值,这些离散的幅度值经DAC和PLF便课还原为模拟波形。

4.Verilog HDL源代码Verilog HDL代码为:module DDS (//inputsys_clk,sys_rst_n,fword,pword,//outputda_clk,da_data);//input portsinput sys_clk ; //system clock;input sys_rst_n ; //system reset, low is active; input [WIDTH1-1:0] fword ; //输入频率字input [WIDTH2-1:0] pword ; //输入相位字//output portsoutput [SIZE-1:0] da_data ; //DA 数据output da_clk ; //DA 时钟//reg definereg [WIDTH1-1:0] fword_r ;reg [WIDTH2-1:0] pword_r ;reg [WIDTH1-1:0] freq_count ;reg [WIDTH2-1:0] rom_addr ;//wire define//parameter defineparameter WIDTH1 = 32;parameter WIDTH2 = 12;parameter SIZE = 10;/******************************************************************** ************************************* Main Program*********************************************************************** ***********************************/assign da_clk = sys_clk ;always @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginfword_r <= 32'h0000;endelsefword_r <= fword;endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginpword_r <= 12'h0000;endelsepword_r <= pword;endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginfreq_count <= 32'h0000;endelsefreq_count <= freq_count + fword_r; //频率控制器endalways @(posedge sys_clk or negedge sys_rst_n) beginif (sys_rst_n ==1'b0) beginrom_addr <= 32'h0000;endelserom_addr <= freq_count[31:20] + pword_r; //相位控制器endROM DDS_ROM_U0 (.address (rom_addr) ,.clock (sys_clk) ,.q (da_data));endmodule//end of RTL code5.日积月累Xxx6.综合出的电路DDS代码综合出的电路如下:注意:波形文件存在Project\DDS\wave_file下面。

DDS的原理及镜像频谱分析

DDS的原理及镜像频谱分析1.目的:(1)了解DDS的原理。

(2)分析DDS的镜像频谱2.DDS的原理2.1.DDS的概述直接数字式频率综合器DDS(Direct Digital Synthesizer),实际上是一种分频器:通过编程频率控制字对系统时钟进行分频以产生所需要的频率。

DDS 有两个突出的特点,一方面,DDS工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高;另一方面,由于频率控制字的宽度宽(48bit或者更高),频率分辨率高。

图1是DDS的内部结构图,它主要分成3部分:相位累加器(PHASE_ACCMULATOR),相位幅度转换(AMPLITUDE/SINE_CONV.ALGORITHM),数模转换器(D/A_CONVERTER)图1 DDS的结构框图2.2.DDS的组成1、相位累加器:一个正弦波,它的幅度不是线性的,但是它的相位却是线性增加的。

DDS就是利用了这一特点来产生正弦信号。

如图 2,根据DDS的频率控制字的位数N,把360°平均分成了2N等份。

假设系统时钟为Fc,输出频率为Fout。

每次转动一个角度360°/2N,则可以产生一个频率为Fc/2N的正弦波的相位递增量。

那么只要选择恰当的频率控制字M,使得Fout/Fc= M/2N,就可以得到所需要的输出频率Fout=Fc*M /2N。

图2 相位累加器原理2、相位幅度转换:通过相位累加器,我们已经得到了合成Fout频率所对应的相位信息,然后相位幅度转换器把0°~360°的相位转换成相位相应的幅度值。

比如当DDS选择为2Vp-p的输出时,45°对应的幅度值为 0.707V,这个数值则以二进制的形式被送入DAC。

这个相位到幅度的转换是通过查表完成的。

3、数模转换器:的二进制数字信号被送入DAC中,并转换成为模拟信号输出。

★注意★DAC 的位数并不影响输出频率的分辨率。

外文翻译及原文翻译咨询应用工程师33关于直接数字频率合成器的问题

本科毕业设计(论文)外文翻译译文学生姓名:王惠院(系):电子工程学院仪器系专业班级:测控0701指导教师:刘选朝完成日期: 20 11 年 3 月 7 日咨询应用工程师- 33关于直接数字频率合成器的问题作者Eva Murphy]Colm Slattery]什么是直接数字频率合成器?直接数字频率合成器(DDS)是一种产生模拟波形(通常是正弦波)的仪器,这种仪器是生成一个数字形式的时变信号,然后执行数字到模拟的转换。

因为用一个DDS设备操作主要是数字形式,所以它可以提供输出频率之间的快速转换,较高的频率分辨率并且可以在一个宽频带上进行操作。

随着设计和工艺技术的进步,现在的DDS器件都非常小巧,在低功率下也可以工作。

为什么我们要使用直接数字频率合成器(DDS)?难道就没有其他产生频率的简单方法吗?能够准确地产生和控制各种频率和轮廓的波形的能力已成为一个通用于多个行业重要要求。

在通信系统中能否利用良好的杂散性提供低相位噪声可变频率的活跃来源,或仅产生用于工业或生物医学测试设备的应用的频率刺激,便利、简洁和低成本是重要的设计考虑因素。

频率产生的多种可能性对设计师来说是开放的,从锁相回路(PLL)——极高频率合成的基础技术,到以数模转换器(DAC)的动态编制程序输出来产生低频任意波形。

但是DDS技术迅速在解决频率(或波形)产生的通信和工业应用要求上得到接受,因为单芯片集成电路器件可以简单的产生可编程模拟输出波形,具有较高的分辨率和精度。

此外,在这两种工艺技术和设计的不断改进也使得成本和功耗较从前降低了许多。

例如,AD9833——基于DDS的可编程波形发生器(图1)在V的电压下工作工作具有25 MHz的时钟,消耗的最大功率为30毫瓦。

图1 单片波形发生器使用直接数字频率合成器(DDS)的主要优点有哪些?像AD9833 之类的DDS器件都可通过一个高速串行外设接口(SPI)进行编程,并且只需要一个外部时钟来生成简单的正弦波。

FPGA DDS IP核实现_单频 线性调频

FPGA DDS IP 核实现DDS (Direct Digital Synthesizer ),即直接数字频率合成器,本文主要介绍如何调用Xilinx 的DDS IP 核生成某一频率的Sin 和Cos 信号,以及LFM 信号。

1.相关参数的介绍及求解(1)DDS 输出频率输出频率out f 是系统时钟频率clk f 、相位累加器中相位数据位宽)(n B θ和相位增量θ∆的函数。

)(2n B clk out f f θθ∆=因此,要得到输出频率out f ,要求相位增量θ∆为clk Bout f f n )(2θθ=∆如果要采用时分复用的多个通道,则降低每个通道的有效时钟效率。

对于C 个通道,要求相位增量为clk Bout f Cf n )(2θθ=∆(2)频率分辨率频率分辨率f ∆是系统时钟频率clk f 和相位累加器数据位宽)(n B θ的函数。

)(2n B clk f f θ=∆对于时分复用的多通道,频率分辨率随通道数的增加而提高,对于C 个通道:Cf f n B clk )(2θ=∆(3)相位增量相位增量值是无符号的,当相位增量值与相位位宽匹配时,也可以将其看作有符号数。

假设相位增量和相位数据位宽均为N ,如果看成无符号数,范围由0到N 2表示的是(] 3600,的角度范围;如果看成有符号数,则范围变成)1(2--N 到)1(2-N ,相位表示的是[) 180180,-的角度范围。

根据正弦信号的周期性和对称性,两种表示范围内的信号采样是一致的。

相位增量定义了综合其的输出频率。

相位增量是系统时钟频率clk f 、输出频率out f 和相位数据位宽)(n B θ的函数。

clk B out f f n )(2θθ=∆2.线性调频信号线性调频信号的时间函数表达式可表示为2,2[)],2(exp[)(20T T t Kt t f j t s -∈+=ππ其瞬时频率为]2,2[,)(21)(0T T t Kt f t dt d t f -∈+==ϕπ其中,TB K =,B 为信号调频宽度,T 为信号脉宽。

直接数字频率合成器DDS及其性能分析

电子器件工作速度的提高 ,DDS 的输出频率上限 行傅氏变换 ,得到理想 DDS 输出的频谱表达式 :

∞

也s将e 可以提高. 其二 ,DDS 输出的模拟信号中杂

∑ S (ωn) = π S a

·

散寄生分量大 ,其中输出高频尤甚 ,它无法达到

l=- ∞

PLL 频率合成的频谱纯度. 其三 ,DDS 的n功A耗与

其一 ,根据取样定理 ,输出信号基波的最高频率将

低于参考时钟的一半 ,故若要提高输出频率将受

n = 1 ,2 , …

(1)

到器件 (如 DAC、ROM) 的速度限制. 目前输出频 S ( n) 通过 DAC 和低通滤波器 , 得到 DDS 的输出

率达到 450 M Hz 的 DDS 系统已研制成功. 随着 S ( t) ,显然 S ( t) 是连续时间的周期信号. 对它进

第 5 期 高泽溪等 :直接数字频率合成器 (DDS) 及其性能分析

617

mod 运算定义为

0 ≤ t ≤μTc

(9)

pmod q = p - int ( p/ q) q

通过 S′( t) 的傅氏变换 , 可以得到 S′(ω) 的表达

其中 int (·) 代表取整运算.

式 (略) ,对表达式分析说明 ,波形误差信号包含的

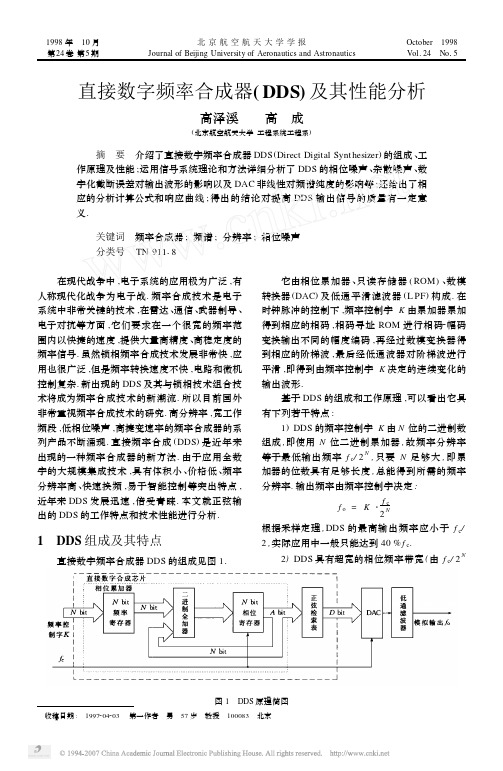

摘 要 介绍了直接数字频率合成器 DDS(Direct Digital Synt hesizer) 的组成 、工 作原理及性能 ;运用信号系统理论和方法详细分析了 DDS 的相位噪声 、杂散噪声 、数 字化截断误差对输出波形的影响以及 DAC 非线性对频谱纯度的影响等 ;还给出了相 应的分析计算公式和响应曲线 ;得出的结论对提高 DDS 输出信号的质量有一定意 义.

dds技术原理

dds技术原理DDS技术原理什么是DDS技术DDS(Direct Digital Synthesis)技术是一种通过数字方式生成连续时间波形的方法。

它是一种基于数字信号处理技术的发展而来的新型波形发生技术。

DDS技术具有高精度、高稳定性、高灵活性等特点,被广泛应用于频率合成、调制解调、信号发生等领域。

DDS技术的原理数字相位累加器DDS技术的核心是数字相位累加器。

相位累加器是一种用于周期性连续时间波形的数字累加器,它以固定的频率递增或递减相位值,从而生成连续时间的波形。

相位值的变化速率由相位增量参数控制,该参数决定了波形的频率。

数字频率控制字DDS技术通过调整相位累加器的相位增量参数来控制波形的频率。

相位增量参数被称为数字频率控制字(Digital Frequency Tuning Word,简称FTW),它决定了相位累加器每个时钟周期中相位值的变化量。

映射函数DDS技术中的映射函数用于将数字频率控制字映射到具体的频率。

映射函数通常由硬件电路或软件程序实现,它将FTW值转换为相应的频率值,通过控制FTW值的变化来实现定制的波形产生。

数字到模拟转换DDS技术生成的是数字信号,为了得到模拟波形,需要进行数字到模拟转换(Digital-to-Analog Conversion,简称DAC)。

DAC将DDS产生的数字波形转换为模拟信号,供系统外部使用。

DDS技术的优势DDS技术相较于传统的信号发生技术具有如下优势:•高精度:DDS技术通过精确控制相位累加器的相位增量值,可以实现非常精确的频率合成,利于高精度的信号发生。

•高稳定性:DDS技术的频率控制依赖于数字控制字,数字控制字的稳定性决定了波形的稳定性,DDS技术具有较高的稳定性。

•高灵活性:DDS技术通过调整数字控制字的值,可以实现各种信号波形的生成,具有较高的灵活性,适应多种应用需求。

结语DDS技术作为一种基于数字信号处理的波形发生技术,具有高精度、高稳定性、高灵活性等优点,被广泛应用于频率合成、调制解调和信号发生等领域。

基于DDS技术的信号发生器的设计与实现_毕业设计(论文)

毕业设计设计题目:基于DDS技术的信号发生器的设计与实现基于DDS技术的信号发生器的设计与实现摘要DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。

与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和快速转换时间等优点,广泛使用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

本设计采用单片机为核心处理器,利用键盘输入信号的参数,控制DDS的AD9850模块产生信号,信号的参数在LCD1602上显示,完成正弦信号和方波信号的输出,用示波器输出验证。

DDS是一种全数字化的频率合成器,由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

时钟频率给定后,输出信号的频率取决于频率控制字,频率分辨率取决于累加器位数,相位分辨率取决于ROM的地址线位数,幅度量化噪声取决于ROM的数据位字长和D/A转换器位数。

与传统的频率合成方法相比,DDS合成信号具有频率切换时间短、频率分辨率高、相位变化连续等诸多优点。

使用单片机灵活的控制能力与AD9850的高性能、高集成度相结合,可以克服传统DDS设计中的不足,从而设计开发出性能优良的信号发生器系统。

关键词:单片机直接数字频率合成AD9850 DDSDesign and Implementation of the SignalGenerator Based on DDS TechnologyAbstractDDS is Direct Digital frequency Synthesizer (Direct Digital Synthesizer) English abbreviations. Compared with the traditional frequency synthesizer, with low cost, DDS low power consumption, high resolution and fast converting speed time and so on, widely used in telecommunications and electronic instruments field, is to realize equipment full digital a key technology.This design uses the single chip processor as the core, using a keyboard input signal parameters, control of DDS AD9850 module produce signals, the signal parameters in LCD1602 show that the complete sine signal and square wave signal output, the output with an oscilloscope validation.DDS is A full digital frequency synthesizer, by phase accumulators, waveform ROM, D/A converter and low pass filter composition. The clock frequency after A given, the output depends on the frequency of the signal frequency control word, the frequency resolution depends on accumulators digits, phase resolution depends on the ROM address line digits, amplitude quantization noise depends on the ROM data A word length and D/A converter digits. And the frequency of the traditional method than the synthesis, DDS synthesis signal has a frequency switching frequency of short time, high resolution and continuous phase changes, and many other advantages. Using single chip microcomputer control of the flexible ability and high performance, high level of integration of the AD9850 combination, can overcome the disadvantage of the traditional DDS design, to design the developed good performance of signal generator system.Key word:MCU; direct digital frequency synthesis;AD9850;DDS目录1 引言 (1)2DDS概要 (2)2.1DDS介绍 (2)2.1.1 DDS结构 (2)2.1.2典型的DDS函数发生器 (3)2.2DDS数学原理 (5)3 总体设计方案 (8)3.1系统设计原理 (8)3.2总体设计框图 (8)4 系统硬件模块的组成 (9)4.1单片机控制模块 (9)4.1.1 STC89C52主要性能 (9)4.1.2 STC89C52功能特性描述 (9)4.1.3 时钟电路 (11)4.1.4复位电路 (11)4.2AD9850模块 (12)4.2.1 AD9850简介 (12)4.2.2 AD9850的控制字与控制时序 (14)4.2.3单片机与AD9850的接口 (15)4.3滤波电路设计 (15)4.4键盘控制模块 (16)4.5LCD显示模块 (16)4.5.1液晶显示器显示原理 (16)4.5.2 1602LCD引脚与时序 (17)4.6A/D转换模块 (20)5 软件设计与调试 (21)5.1程序流程图 (21)5.2软件调试 (22)5.2.1 keil编程工具介绍 (22)5.2.2 STC-ISP下载工具介绍 (23)6 硬件电路制作 (24)6.1原理图的绘制 (24)6.2电路实现的基本步骤 (24)6.3硬件测试波形图 (25)7 结论 (27)谢辞 .............................................................................................. 错误!未定义书签。

直接数字合成器

PIO49

108

freg[3:0]

PIO3-0

freg[7:4]

PIO7-4

phase[3:0]

PIO11-8

phase[7:4]

PIO15-12

out[0]

P94

out[1]

P91

out[2]P82Βιβλιοθήκη out[3]P79

out[4]

P62

out[5]

P61

out[6]

P60

out[7]

P59

out[8]

1、首先感谢两位老师在整个课程设计过程中给予我们的帮助和支持。老师在百忙之中抽出时间来为我们排忧解难,我们大家都很感动。

2、肯定自己在整个设计过程中所做的努力,作为小组负责人,通过资料收集,代码编写,软件的熟悉、上板调试等过程,自身的能力也得到了进一步提高。

3、课程设计是个团队活动,我们运用各自在各方面的优势中和起来,形成了一个团队。通过团队力量,才使设计得以完成。可以说,我们四个人是一个不可或缺的整体,少了任何一个人都是无法完成任务的.

根据设计要求,在FPGA上实现的电路部分见下图。

1、定制ROM

1)Matlab生成sin函数数据

在Matlab主窗口中输入以下命令,生成data.mif文件存储sin函数数据。累加器的宽度为 ,输出数据的宽度为 。

2)Quartus 2生成rom.mif,格式如下图,将Matlab生成的data.mif中数据拷贝到rom.mif中CONTENT BEGIN END之间。

调试时,在FPGA板子上选择模式1,将键7(清零信号)和键8(使能信号)置于高电平。

初始时示波器显示一条直线(如图1),按一下键1产生一个脉冲表示频率控制字加1,按一下键2表示频率控制字加0001_0000,图2图3分别表示按了一次和两次键1之后得示波器图形,图4、5、6是按了多次键1键2之后示波器的波形图。

基于FPGA的直接数字频率合成器的设计本科设计

基于FPGA的直接数字频率合成器的设计本科设计毕业设计论文基于FPGA的直接数字频率合成器的设计摘要在频率合成领域,常用的频率合成技术有直接模拟合成、模拟锁相环、小数分频锁相环等,直接数字频率合成(Direct Digital Frequency Synthesis ,DDFS,简称DDS)是近年来的新的频率合成技术。

本文介绍了直接数字频率合成器的基本组成及设计原理,给出了基于FPGA的具体设计方案及编程实现方法。

仿真结果表明,该设计简单合理,使用灵活方便,通用性好,可写入各种FPGA 芯片,最高可将频率提高100万倍。

具有良好的性价比。

关键词直接数字频率合成器(DDS) FPGADesign of direct digital frequency synthesizer based on FPGAAbstract In Frequency domain, the common Synthesis technology has Direct simulation, phase lock loop simulation, decimal Frequency and phase lock loop, Direct Digital Frequency Synthesis (as some DDFS, Digital, referred to as spurious bio-synthesis) in recent years is the new Frequency Synthesis technology. The structure and principles of Direct Digital Frequency Synthesizer is introduced. Also a detailed design and the method of program realization based on FPGA are introduced. The result of simulation shows that the design is simple and feasible, convenient and flexible, high universality, writeable various FPGA chip, the highest frequency can be 100 million times. Ratiofor quality to price.Keywords Direct Digital frequency Synthesizer(DDS) FPGA前言在频率合成领域,常用的频率合成技术有直接模拟合成、模拟锁相环、小数分频锁相环等,直接数字频率合成(DDS)是近年来的新的频率合成技术。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1993 IEEE INTERNATIONAL FREQUENCY CONTROL SYMPOSIUM

The Composite DDS - A New Direct Digital Synthesizer Architecture Lawrence J. Kushner Lincoln Laboratory Massachusetts Institute of Technology Lexington, MA 02173-9108

Abstract-A new, low-power, high-speed, Direct Digital Synthesizer (DDS) architecture is presented, called the Composite DDS (CDDS). A low-speed, high-resolution DDS is combined with a high-speed, low-resolution phase accumulator and phase shifter via the serrodyne modulation technique. The low-speed circuitry provides the fine tuning while the high-speed circuitry provides coarse tuning. By minimizing the amount of circuitry required to clock at high-speeds, dc power is conserved. The results from numeric simulations and a low-frequency proof-of-concept breadboard are presented. Progress on our 800 MHz CDDS development effort is described, followed by proposed enhancements to the CDDS architecture which promise improved performance. Introdlh(;tipn LTHOUGH Direct Digital Synthesizers (DDSs) were A invented decades ago [l], they did not come to play a dominant role in wideband frequency generation until recent years. Initially, DDSs were limited to producing narrow bands of closely spaced frequencies, due to the limitations of digital logic and Digital-to-Analog Converter (DAC) technologies. Larger bandwidths were generated by other means, such as phaselock loops, direct analog synthesis, or frequency multiplication, using the DDS to generate the fine resolution. For applications requiring fast tuning, these Y c 8 a 0 n 14 12 10 8 6 4 2 Figure 1 - DDS Power Consumption vs. Clock Speed. Data points based on references [4] - [lo], and Lincoln /Texas Instruments projections (dates). F19628-90-0002 This wok was sponsored by the US Army under Air Force Conhad approaches resulted in expensive, complex, power-hungry, frequency generators. Due to the rapid advance of digital technology, there is now an alternative approach. Direct Digital Synthesizers clocking at 1 GHz have recently become available [2].

Most, if not all, of the needed bandwidth can be generated by the DDS, resulting in reduced system complexity, size, and weight. While it is likely that DDS technology will continue to improve as digital technology advances, Figure

1 illustrates a key tradeoff that will remain: the faster the clock rate, the higher the dc power consumption.

While dc power may be unimportant in some systems, it is of utmost concern in many applications, such as portable, battery-powered communications equipment, and satellites. Additionally, even systems with power to bum may still have difficulty removing the heat generated by a high-power DDS .

Figure 2 - Direct Digital Synthesizer Architecture. (Typical data-path widths shown)

The high-level architecture of a conventional DDS is shown in Figure 2. Since the frequency resolution of a DDS is equal to fclOck/(ZN), where N is the number of bits in the phase accumulator, the greater the clock frequency, the more bits are needed to maintain a given resolution. 32-bit wide phase accumulators are commonly used in today's commercial DDSs. For a 1.6 GHz clock, 32 bits yields 0.37 Hz resolution.

The problem with this conventional approach is that on every clock cycle, the phase accumulator has to accumulate, the ROM has to produce a new value, and the DAC must convert another sample from digital to analog. All of this high-speed activity results in high dc power consumption.

255 0-7803-0905-7/93 $3.00 0 1993 IEEE Composite Direct D-r (CDDS1 In contrast, the Composite DDS [l l] uses a new

architecture (Figure 3), allowing it to achieve high speed and low power consumption simultaneously. Instead of clocking the entire circuit at the maximum clock rate, the CDDS partitions the circuitry into a small, high-speed circuit that generates coarse frequency steps, and a larger,

low-speed circuit to generate the fine frequency resolution. The Fie-resolution frequency (fl) is upconverted by the coarse-resolution frequency (f2) via the serrodyne modulation technique (Figure

4).

.. 50 MHz 12.5 MHz BW, 550 MHz BW.

0.01 Hz RESOLUTION 0.01 M RESOLUTION

.. . . . . .

I i

SERR~DYNE I

FREQUENCY COMMAND i MODULATOR

I

I IC U ,,.- t---

1.6 GHz* *PROJECTED 1995

Figure 3 - Composite DDS Architecture (nominal clock frequencies and data-path widths shown for clarity).

t

Figure 4 - Serrodyne Modulation Principle [12]-[14]. Since its inception in the late 1950's. the serrodyne principle has been used in radar applications to chirp fmed,