第1章 CPLD建模

CPLD结构与原理

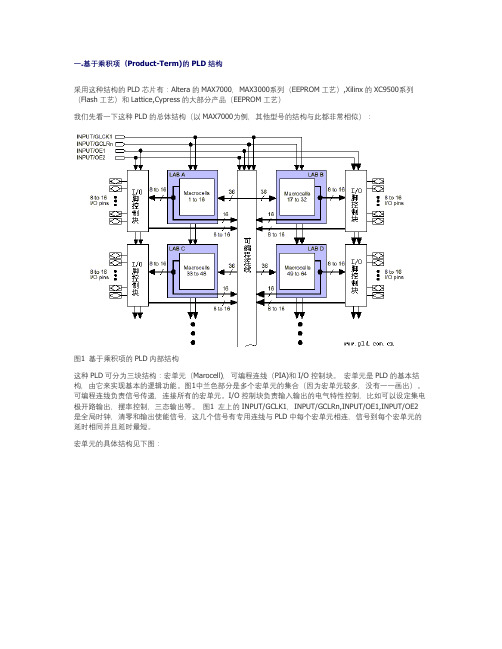

一.基于乘积项(Product-Term)的PLD结构采用这种结构的PLD芯片有:Altera的MAX7000,MAX3000系列(EEPROM工艺),Xilinx的XC9500系列(Flash工艺)和Lattice,Cypress的大部分产品(EEPROM工艺)我们先看一下这种PLD的总体结构(以MAX7000为例,其他型号的结构与此都非常相似):图1 基于乘积项的PLD内部结构这种PLD可分为三块结构:宏单元(Marocell),可编程连线(PIA)和I/O控制块。

宏单元是PLD的基本结构,由它来实现基本的逻辑功能。

图1中兰色部分是多个宏单元的集合(因为宏单元较多,没有一一画出)。

可编程连线负责信号传递,连接所有的宏单元。

I/O控制块负责输入输出的电气特性控制,比如可以设定集电极开路输出,摆率控制,三态输出等。

图1 左上的INPUT/GCLK1,INPUT/GCLRn,INPUT/OE1,INPUT/OE2 是全局时钟,清零和输出使能信号,这几个信号有专用连线与PLD中每个宏单元相连,信号到每个宏单元的延时相同并且延时最短。

宏单元的具体结构见下图:图2 宏单元结构左侧是乘积项阵列,实际就是一个与或阵列,每一个交叉点都是一个可编程熔丝,如果导通就是实现“与”逻辑。

后面的乘积项选择矩阵是一个“或”阵列。

两者一起完成组合逻辑。

图右侧是一个可编程D触发器,它的时钟,清零输入都可以编程选择,可以使用专用的全局清零和全局时钟,也可以使用内部逻辑(乘积项阵列)产生的时钟和清零。

如果不需要触发器,也可以将此触发器旁路,信号直接输给PIA或输出到I/O脚。

二.乘积项结构PLD的逻辑实现原理下面我们以一个简单的电路为例,具体说明PLD是如何利用以上结构实现逻辑的,电路如下图:图3假设组合逻辑的输出(AND3的输出)为f,则f=(A+B)*C*(!D)=A*C*!D + B*C*!D ( 我们以!D表示D的“非”)PLD将以下面的方式来实现组合逻辑f:图4A,B,C,D由PLD芯片的管脚输入后进入可编程连线阵列(PIA),在内部会产生A,A反,B,B反,C,C反,D,D反8个输出。

电力电子建模课件 DC-DC变换器DCM的动态建模

End of Review

Averaged switch model: DCM buck-boost example

Original circuit

Averaged model

vg(t)Ts

i1(t) Ts fi ( v1 Ts , v2 Ts ) i2(t) Ts

v1(t) Ts -

Re (d1) + vL L

We need equivalent circuits that model both the steady-state and small signal ac models of converters operating in DCM.

Buck converter

CCM

Then DCM mode DCM

1

vL (t) Ts Ts

t Ts t

vLdt

1 Ts

tTs L di dt L [i

tdtTst Nhomakorabea Tsi(t)]

Solve for d2:

Average switch network port voltages

Average v1(t) waveform:

d1 d2 d3 1

where

Output port: Averaged equivalent circuit

Power balance in lossless two-port networks

In a lossless two-port network without internal energy storage: instantaneous input power is equal to instantaneous output power.

LDA模型

LDA(主题模型)算法&&概念:首先引入主题模型(Topic Model)。

何谓“主题”呢?望文生义就知道是什么意思了,就是诸如一篇文章、一段话、一个句子所表达的中心思想。

不过从统计模型的角度来说,我们是用一个特定的词频分布来刻画主题的,并认为一篇文章、一段话、一个句子是从一个概率模型中生成的。

LDA可以用来识别大规模文档集(document collection)或语料库(corpus)中潜藏的主题信息。

它采用了词袋(bag of words)的方法,这种方法将每一篇文档视为一个词频向量,从而将文本信息转化为易于建模的数字信息。

LDA(Latent Dirichlet Allocation)是一种文档主题生成模型,也称为一个三层贝叶斯概率模型,包含词、主题和文档三层结构。

所谓生注:每一篇文档代表了一些主题所构成的一个概率分布,而每一个主题又代表了很多单词所构成的一个概率分布。

备注:流程(概率分布):→→许多(单)词某些主题一篇文档/**解释:LDA生成过程*对于语料库中的每篇文档,LDA定义了如下生成过程(generativeprocess): *1.对每一篇文档,从主题分布中抽取一个主题;*2.从上述被抽到的主题所对应的单词分布中抽取一个单词;*3.重复上述过程直至遍历文档中的每一个单词。

**/把各个主题z在文档d中出现的概率分布称之为主题分布,且是一个多项分布。

把各个词语w在主题z下出现的概率分布称之为词分布,这个词分布也是一个多项分布。

&&深入学习:理解LDA,可以分为下述5个步骤:1.一个函数:gamma函数2.四个分布:二项分布、多项分布、beta分布、Dirichlet分布3.一个概念和一个理念:共轭先验和贝叶斯框架4.两个模型:pLSA、LDA(在本文第4 部分阐述)5.一个采样:Gibbs采样本文便按照上述5个步骤来阐述,希望读者看完本文后,能对LDA有个尽量清晰完整的了解。

Multisim简介(累计第1、2课时)

一、Multisim发展

1、Multisim发展简介

加拿大EWB(Electrical Workbench)

EWB4.0

EWB5.0

EWB6.0

Multisim2001

Multisim 7

Multisim 8

美国国家仪器(NI)有限公司

Multisim 9

Multisim 10

Multisim 11

(1)――模数电路仿真

(2)——单片机仿真

(3)――FPGA、PLD、CPLD仿真

(4)――通信系统分析与设计

(5)――32层PCB设计

NI Multisim仿真的内容:

(1)器件建模及仿真:模拟器件(二极管,三极管,功率管等);数字器件(74系列,COMS系列,PLD,CPLD等);FPGA器件。

Lab view:虚拟仪器原理及仿真

二、Multisim的主窗口

1、界面。

界面由多个区域构成:菜单栏,各种工具栏,电路输入窗口,状态条,列表框等。通过对各部分的操作可以实现电路图的输入、编辑,并根据需要对电路进行相应的观测和分析。用户可以通过菜单或工具栏改变主窗口的视图内容。

师生问好

跟随老师的思路,慢慢把注意力集中到课堂上。

学生需要认真听讲,做好笔记。

学生练习

教师巡视,辅导

Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。

教学重点:

了解Multisim的背景与功能

教学难点:

了解Multisim的功能

教学准备:

机房

教学内容及教师活动

学生活动

教学过程

教学过程

1_3 EDA设计方法与流程

芯 片 投 片 、

电子系统EDA设计方法流程图

7

1. EDA技术设计方法

(3)传统设计方法与EDA设计方法的区别

设计方法

传统设计方法

自下至上 (Bottom to Up)

EDA设计方法

自上至下 (Top to Down)

实现载体

通用的逻辑元件

可编程逻辑器件PLD

调试方法 设计途径

硬件设计的后期 仿真和调试

《EDA技术应用》

EDA设计方法与流程

1

目录

1 2 3 4

EDA技术设计方法 IP核与SOC设计 EDA开发流程 EDA技术设计的优势

2

1. EDA技术设计方法

举例1:矩形波发生器电路设计。

传统数字设计方法

CPU MCU

8254

EDA技术设计方法

FPGA/CPLD

控制部分

波形产生

3

1. EDA技术设计方法

C、ASM... 程序

软件程序编译器 COMPILER

CPU指令代码 01001000010

15

3. EDA开发流程

(3)适配

适配是将网表文件转换为适应于特定PLD器件下载的最终文件, 适配结果与器件的内部 结构相关。

16

3. EDA开发流程

(4)仿真

功能仿真:直接对VHDL、原理图描述或其他描述形式的逻辑功能进行测 试模拟,以了解其实现的功能是否满足原设计的要求的过程,仿真过程不 涉及任何具体器件的硬件特性(如延时特性)。

硬件电路原理图ቤተ መጻሕፍቲ ባይዱ

系统设计的早期 仿真和修改

多种设计文件, 以 HDL描述文件为主

实现方法

手工实现

自动实现

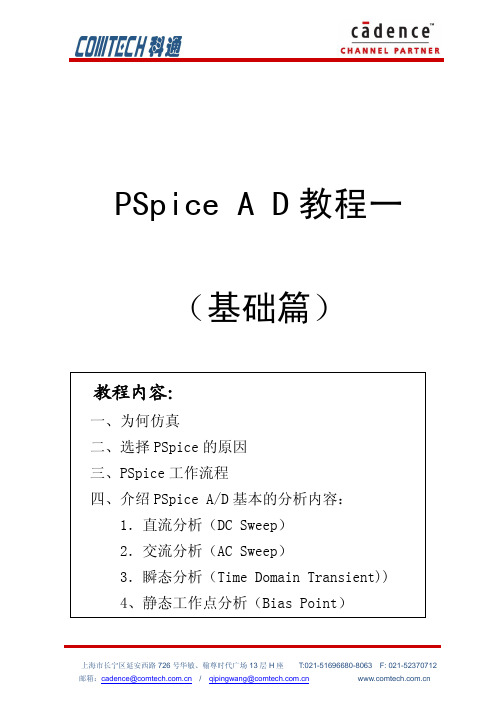

PSpice16.5教程一(基本分析)

(基础篇)

教程内容:

一、为何仿真 二、选择 PSpice 的原因 三、PSpice 工作流程 四、介绍 PSpice A/D 基本的分析内容:

1.直流分析(DC Sweep) 2.交流分析(AC Sweep) 3.瞬态分析(Time Domain(Transient)) 4、静态工作点分析(Bias Point)

三、PSpice 的工作流程图

四、PSpice A/D 基本的分析内容

在选择分析方法前需要绘制电路原理图,OrCAD 统一由 Capture 窗口进行输入和调 用 PSpice 分析。在使用 PSpice 时绘制原理图应该注意的地方。

1、 新建 Project 时应选择 Analog or Mixed-signal Circuit 2、 调用的器件必须有 PSpice 模型 首 先 , 调 用 OrCAD 软 件 本 身 提 供 的 模 型 库 , 这 些 库 文 件 存 储 的 路 径 为 Capture\Library\pspice,此路径中的所有器件都有提供 PSpice 模型,可以直接调用。 其次,若使用自己的器件,必须保证*.olb、*.lib 两个文件同时存在,而且器件属 性中必须包含 PSpice Template 属性。 3、 原理图中至少必须有一条网络名称为 0,即接地。 4、 必须有激励源。 原理图中的端口符号并不具有电源特性,所有的激励源都存储在 Source 和 SourceTM 库中。

图 1-6 放置元件的窗口

如图 1-6,我们选择输入“R”,找到在 analog.lib 下的电阻器件,双击它就可 以放置到绘图窗口中了。

接下来我们作个简单例子来了解一下仿真的工程。当然这里先进行的是直流扫描 分析(DC Sweep)

第十届冯如杯获奖作品

E1602002 E1602030 G1602001 D1602016 D1602017 D1602019 D1602020 D1602023 D1602024 D1602026 D1602027 D1602028 D1602031 D1602032 D1602033 D1602034 D1602036 D1602038 D1602040 D1602042 D1602043 D1602045 D1602052 D1602060 E1602005 E1602009 E1602015

龚亚信 三等奖

第十二届“冯如杯”获奖人员名单:

项目名称

第一作者 获奖等级

手动发电电筒

邢大海 二等奖

多用户电话录音系统

袁炜 二等奖

座舱多功能显示器飞行员操作程序一体化设计与评估系 统

魔方

夏雄 何锋

二等奖 二等奖

光控百叶窗

李健 三等奖

行人自控交通灯系统

邵佳蕊 三等奖

基于电力网的分布式电话系统

何岷 三等奖

三维可视化虚拟北航校园

董旭 三等奖

自动识别解说仪

马贤芳 三等奖

应用于公交系统的自助寻路装置

林研斯 三等奖

便携式可调直流稳压电源

马拂晓 三等奖

无人公交报站系统

陈治科 三等奖

光控自动调光台灯

闫夏莉 三等奖

简易汽车防盗报警器

周丽娜 三等奖

公交线路效率提升系统

张正文 三等奖

全功能通用家电遥控器

陈立江 三等奖

新一代信息标识技术市场营销与产品推广方案 冯洪涛 二等奖

Baby—Care 全方位婴儿监控照料系

冀婷 二等奖

多功能盲人用电子手杖

屠宁杰 三等奖

CFD建模

• 大空间网格的绘制

– 偷懒的方式vs精致的绘制

• 检查网格质量• 设置体类型 Nhomakorabea• 设置边界面类型

• 输出网格文件

导入Fluent进行设置

• Read Case

• 调整scale

• 选择求解器

• 打开能量方程

• 选择粘度方程

• 选择热辐射方程

• 定义材料

• 设置操作条件

• 设置边界条件-加热面

Fluent计算平翅片散热器

——Fluent使用简介

沈惬

主要内容

研究对象

使用Gambit绘制网格

导入Fluent进行设置

初步计算结果

研究对象

使用Gambit绘制网格

• 绘制1/4对称单元

• 绘制大空间

– 同样使用split命令 – 注意:不能有重复的面, 不能有重复的体

• 绘制散热器的网格

• 设置边界条件-空气入口

• 控制求解

• 监视器

• 保存Case • 初始化并开始计算

计算结果

用tecplot进行处理

第3章EDA设计流程及其工具

3.5 常用EDA工具软件

一、EDA工具大致可分为如下五个模块: 1、 设计输入编辑器。 2、仿真器。 3、HDL综合器。 4、适配器(或布局布线器)。 5、下载器。

二、 MAX+plusII概述

具有一定的典型性和一般性 MAX+plusII是Altera提供的FPGA/CPLD开发集成 环境,Altera是世界最大可编程逻辑器件供应商 之一。MAX+plusII界面友好,使用便捷,被誉 为业界最易用易学的EDA软件。

四、IP的发展: 1、初级阶段:免费使用,扩大营业

IC生产厂(Foundry) 扩大业务,提供精心设计并经过工 艺验证的标准单元,吸引IC设计公司(Fabless,无生产 线IC公司)成为他的客户,向客户提供相关的数据资料。 IC设计师十分乐于使用成熟、优化的单元完成自己的设 计,可提高效率,又可减少设计风险。一旦完成设计, 自然必须到这家Foundry去做工艺流片,这就使Foundry 达到了的目的。标准单元使用者与Foundry签订标准单 元数据不扩散协议,无须交单元库的使用费,没直接获 取IP的收益,扩大营业间接收到单元库的IP效益。

2、半定制或全定制ASIC 统称为掩模(MASK)ASIC,或直接称ASIC。 特点:用户设计IC,IC 厂家生产 三种级别: A、半导体元件、连线的大小与尺寸,电路全定 制 B、片内晶体管固定,用户设计连线 半定制 C、库内含标准单元,如SSI逻辑块、MSI逻辑 块、数据通道模块、存储器、IP,乃至系统级模 块。用户在EDA工具上进行开发/粘贴。

特点是必须首先关注并致力于解决系统最底层硬件 的可获得性,以及它们的功能特性方面的诸多细 节问题;在整个逐级设计和测试过程中,始终必 须顾及具体目标器件的技术细节。在这个设计过 程中的任一时刻,最底层目标器件的更换,或某 些技术参数不满足总体要求,或缺货,或由于市 场竞争的变化,临时提出降低系统成本,提高运 行速度等等不可预测的外部因素,都将可能使前 面的工作前功尽弃,工作又得重新开始。 结论:是一种低效、低可靠性、费时费力、且成本 高昂的设计方法。

Petrel中的属性建模流程简介讲课稿

P e t r e l中的属性建模流程简介属性建模:一、相模型的建立:1、测井曲线离散化双击:Process ——Proerty modelding——Scall up well logs;弹出对话框:在Select里选择需要离散化的相曲线数据 facies(input到wells的沉积相数据),点击all可以对需要离散的井进行选择,剔除没有曲线或者曲线数据不正确的井)。

在相模型建立时:Average选择“most of”、method选择“Simple”。

单击“Apply”或“OK”确定。

完成沉积相数据的离散化,离散化后,沉积相数据赋给井轨迹所通过的网格。

离散化后models里的properties里新增了沉积相属性“facies”,可在3D视图里进行查看。

2、沉积相模型建立;双击:Process ——Proerty modelding——Facies modeling。

弹出对话框:对话框右上角选择离散化后的沉积相数据,依次选择各小层(zone)进行属性控制;点击解锁进行编辑控制。

目前的沉积相建模算法很多;通常,纵向上细分网格后用序贯高斯的算法,纵向上未细分用经典算法(此处的“纵向细分“是指layering里把zone细分为不同个数的网格。

⑴、序贯高斯的算法;“Method for zone /facie”选项单击下拉菜单,选择序贯高斯算法:“Sequential indicator simula”,在左侧选择该小层所以相类型(可从左侧出现的百分比统计中看出)单击箭头,相类型移动到右侧。

下侧空白区域新增两个选项卡“Variogram”,“Fraction”,点击按钮,弹出对话框:点击解锁,点击后如图:点击按钮:点击“OK”确定;自动返回之前属性设置界面。

单击“红圈”按钮,点亮其功能,点亮后按钮会变为淡红底色。

在“Variogram”选项卡将Range:里三个值“1000,1000,10”设置为默认值“0.1、0.1、0.1”(注意:每个相类型都需设置,包括M)。