复旦光华之gh-硬件设计流程图

fpga 设计流程

fpga 设计流程

FPGA 设计流程一般包括以下几个步骤:

1. 确定系统需求:确定设计所需的功能和性能要求,并对系统进行需求分析和架构设计。

2. RTL 设计:使用硬件描述语言(如VHDL 或Verilog)编写Register Transfer Level(RTL)代码,描述设计的功能和行为。

3. 验证和仿真:使用仿真工具对RTL 代码进行功能验证和时序验证,确保设计符合预期。

4. 综合与优化:使用综合工具将RTL 代码转换为逻辑综合网表,并进行优化以减小电路规模、降低功耗或提高性能。

5. 时序约束:根据设计需求和目标硬件平台,设定时序约束以确保设计能够满足时序要求。

6. 物理设计:基于综合后的网表,使用布局工具进行物理布局和布线,生成布局后的电路结构。

7. 验证与仿真:对物理设计后的电路结构进行验证和时序仿真,确保布局布线

后的电路满足时序约束和设计要求。

8. 配置位流生成:根据物理设计结果和目标FPGA 设备,生成相应的配置位流文件,用于配置FPGA 设备。

9. 配置位流下载与调试:将配置位流文件下载到FPGA 设备中,并进行硬件调试和验证。

10. 系统集成与测试:将FPGA 设备与其他系统组件进行集成,进行系统级测试和验证。

以上是FPGA 设计常见的流程步骤,可能会根据具体项目需求和开发流程的差异而有所调整。

EDA课件EDA设计流程

其他HDL仿真器

2.3.5 下载器

2.4 QuartusII 简介

图形或 HDL编辑

设计 输入

Analysis & Synthesis (分析与综合)

综合或 编译

Filter (适配器)

Assembler (编程文件汇编)

适配器件

Timing Analyzer (时序分析器)

仿真

图1-9 Quartus II设计流程

2.1 设计流程

图2-1 应用于FPGA/CPLD的EDA开发流程

2.1 设计流程

2.1.1 设计输入(原理图/HDL文本编辑) 1. 图形输入

状态图输入

波形图输入

原理图输入

2. HDL文本输入

在EDA软件的图形编辑界面上绘 制能完成特定功能的电路原理图

将使用了某种硬件描述语言(HDL)的电路设计文本, 如VHDL或Verilog的源程序,进行编辑输入。

2.3.2 HDL综合器

FPGA Compiler II、DC-FPGA综合器、 Synplify Pro综合器、LeonardoSpectrum综合 器和Precision RTL Synthesis综合器

2.3.3 仿真器 2.3.4 适配器

VHDL仿真器 Verilog仿真器

Mixed HDL仿真器

数字 ASIC

数模

混合 模拟 ASIC ASIC

图2-2 ASIC分类

2.2 ASIC及其设计流程

2.2.1 ASIC设计方法

ASIC 设计方法

全定制法

半定制法

门阵列法 标准单元法 可编程逻辑器件法

图2-3 A设计的流程

系统规范说明

clk resetL

集成电路设计与制造的主要流程图

否 否

否

3

引言

半导体器件物理基础:包括PN结的物理机制、双极管、 MOS管的工作原理等

器件

小规模电路

大规模电路

超大规模电路

甚大规模电路

电路的制备工艺:光刻、刻蚀、氧化、离子注入、扩散、 化学气相淀积、金属蒸发或溅射、封装等工序

集成电路设计:另一重要环节,最能反映人的能动性

✓ 高度复杂电路系统的要求 ✓ 什么是分层分级设计? 将一个复杂的集成电路系统的设计问题分解为复杂性较低的设 计级别,这个级别可以再分解到复杂性更低的设计级别;这样 的分解一直继续到使最终的设计级别的复杂性足够低,也就是 说,能相当容易地由这一级设计出的单元逐级组织起复杂的系 统。一般来说,级别越高,抽象程度越高;级别越低,细节越 具体

集成电路 设计与制造的主要流程

1

集成电路设计与制造的主要流程框架

系 统 需 求 设计

掩膜版

芯片制造 过程

芯片检测

封装 测试

单晶、外 延材料

2

集成电路的设计过程:

设计创意 +

仿真验证

功能要求 行为设计(VHDL)

行为仿真 是

综合、优化——网表

时序仿真 是

布局布线——版图

—设计业—

后仿真 是

Sing off

没有单元库支持:对各单元进行电路设计,通过电

路模拟与分析,预测电路的直流、交流、瞬态等特性, 之后再根据模拟结果反复修改器件参数,直到获得满 意的结果。由此可形成用户自己的单元库

21

单元库:一组单元电路的集合

经过优化设计、并通过设计规则检查和反复工艺验证, 能正确反映所需的逻辑和电路功能以及性能,适合于工 艺制备,可达到最大的成品率。

简要叙述软硬件协同设计的基本流程

简要叙述软硬件协同设计的基本流程英文回答:Basic Flow of Software-Hardware Co-Design:The basic flow of software-hardware co-design involves the following steps:1. Requirement Analysis and Specification: Determine the system requirements, including both hardware and software components.2. System Architecture Design: Partition the system into hardware and software subsystems, considering performance, cost, and feasibility constraints.3. Hardware Architecture Design: Design the hardware architecture, including processors, memory, and I/O interfaces.4. Software Architecture Design: Design the software architecture, including software components, communication protocols, and data structures.5. Co-Simulation and Validation: Simulate the hardware and software systems together to verify their interaction and functionality.6. Integration and Testing: Integrate the hardware and software components and test their overall performance and compliance with requirements.7. Deployment and Maintenance: Deploy the system and provide ongoing maintenance and updates.中文回答:软硬件协同设计的基本流程:软硬件协同设计的基本流程包括以下步骤:1. 需求分析与规范,明确系统需求,包括硬件和软件组件。

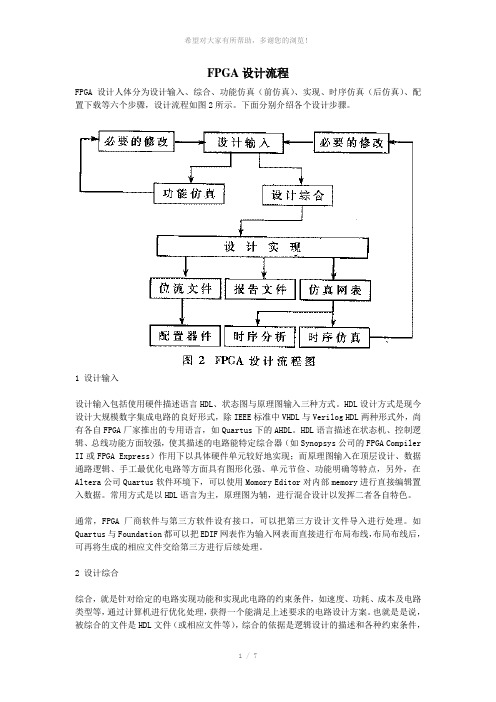

FPGA设计流程

FPGA设计流程FPGA设计人体分为设计输入、综合、功能仿真(前仿真)、实现、时序仿真(后仿真)、配置下载等六个步骤,设计流程如图2所示。

下面分别介绍各个设计步骤。

1 设计输入设计输入包括使用硬件描述语言HDL、状态图与原理图输入三种方式。

HDL设计方式是现今设计大规模数字集成电路的良好形式,除IEEE标准中VHDL与Verilog HDL两种形式外,尚有各自FPGA厂家推出的专用语言,如Quartus下的AHDL。

HDL语言描述在状态机、控制逻辑、总线功能方面较强,使其描述的电路能特定综合器(如Synopsys公司的FPGA Compiler II或FPGA Express)作用下以具体硬件单元较好地实现;而原理图输入在顶层设计、数据通路逻辑、手工最优化电路等方面具有图形化强、单元节俭、功能明确等特点,另外,在Altera公司Quartus软件环境下,可以使用Momory Editor对内部memory进行直接编辑置入数据。

常用方式是以HDL语言为主,原理图为辅,进行混合设计以发挥二者各自特色。

通常,FPGA厂商软件与第三方软件设有接口,可以把第三方设计文件导入进行处理。

如Quartus与Foundation都可以把EDIF网表作为输入网表而直接进行布局布线,布局布线后,可再将生成的相应文件交给第三方进行后续处理。

2 设计综合综合,就是针对给定的电路实现功能和实现此电路的约束条件,如速度、功耗、成本及电路类型等,通过计算机进行优化处理,获得一个能满足上述要求的电路设计方案。

也就是是说,被综合的文件是HDL文件(或相应文件等),综合的依据是逻辑设计的描述和各种约束条件,综合的结果则是一个硬件电路的实现方案,该方案必须同时满足预期的功能和约束条件。

对于综合来说,满足要求的方案可能有多个,综合器将产生一个最优的或接近最优的结果。

因此,综合的过程也就是设计目标的优化过程,最后获得的结构与综合器的工作性能有关。

FPGA设计流程

FPGA设计流程FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可在设计和制作期间进行重新配置。

FPGA设计流程包括以下几个主要步骤:1.确定设计需求:在开始FPGA设计流程之前,需要明确设计的需求和目标。

这包括所需的功能、性能要求和资源限制等。

同时,还需要对设计所需的外部接口和通信协议进行了解。

2.选择FPGA平台:根据设计需求,选择合适的FPGA平台。

不同的FPGA平台具有不同的资源和性能特征,因此选择适合设计需求的平台非常重要。

3.构建设计框架:根据设计需求,构建设计框架,确定所需的输入输出端口和电源供应等。

设计框架通常包括主要模块的结构和通信方式的定义。

4. 设计功能模块:根据设计需求,设计和实现各个功能模块。

功能模块可以使用硬件描述语言(如VHDL或Verilog)进行描述,并使用综合工具将其转换为逻辑网表。

5.进行综合和优化:将设计转换为逻辑网表后,可以使用综合和优化工具对其进行优化。

综合工具将逻辑网表转换为FPGA的配置文件,优化工具可以帮助进一步提高性能和减少资源占用。

6.进行布局布线:在综合和优化之后,需要进行布局布线。

布局布线工具将逻辑元素放置在FPGA芯片上,并确定它们之间的连线,以满足时序要求和资源限制。

7.进行时序分析:完成布局布线之后,可以进行时序分析,以验证设计是否满足时序要求。

时序分析工具可以帮助检测潜在的时序问题,并提供优化建议。

8.进行仿真和验证:在时序分析之后,可以进行仿真和验证,以确保设计的正确性和功能性。

仿真工具可以模拟设计与外部环境的交互,并验证其行为是否符合预期。

9.进行测试和调试:在完成仿真和验证之后,可以进行测试和调试。

测试工具可以生成测试向量,并验证设计在不同输入条件下的行为。

调试工具可以帮助定位和解决设计中的问题。

11.进行性能评估:在部署和配置之后,可以进行性能评估,以确保设计满足性能要求。

性能评估工具可以测量设计的时序和功耗等重要指标。

(完整版)IC设计流程

设计流程IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计.前端设计的主要流程:1、规格制定芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。

2、详细设计Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。

3、HDL编码使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码.4、仿真验证仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格.看设计是否精确地满足了规格中的所有要求。

规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码.设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。

仿真验证工具Mentor公司的Modelsim,Synopsys的VCS,还有Cadence的NC—Verilog均可以对RTL级的代码进行设计验证,该部分个人一般使用第一个—Modelsim.该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。

5、逻辑综合――Design Compiler仿真验证通过,进行逻辑综合.逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist.综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。

逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。

所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。

一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)逻辑综合工具Synopsys的Design Compiler,仿真工具选择上面的三种仿真工具均可。

电气硬件设计流程

电气硬件设计流程全文共四篇示例,供读者参考第一篇示例:电气硬件设计流程是指在电子产品的开发过程中,对硬件部分进行系统的设计、实施和验证的过程。

这个过程通常包括概念设计、详细设计、原型制作、验证和验证测试等多个阶段,需要贯穿整个产品开发的过程。

下面就让我们来详细了解一下电气硬件设计流程的具体步骤吧。

一、概念设计阶段概念设计是电气硬件设计流程中的第一步,其目的是确定产品的功能和性能指标,以及制定初步的设计方案。

在这个阶段,设计师需要与产品经理、市场人员等合作,了解产品需求,并将这些需求转化为初步的电气硬件设计方案。

需要考虑产品的系统架构、传感器选择、电源管理、接口设计等方面的问题。

在方案确定之后,还需要进行电路原理图的绘制,以及产品结构和外形设计的确定。

在概念设计确定之后,就进入了详细设计阶段。

在这个阶段,设计师需要深入设计每一个功能模块的电路原理图和PCB布局,确定电路拓扑结构,选择合适的元器件。

要考虑电路的抗干扰能力、功耗、散热等方面的问题,并进行相关计算。

还需要进行信号完整性分析、功率分析,以及EMI/EMC测试等工作。

最终,要生成详细的电路原理图和PCB布局设计文档,为后续的原型制作做准备。

三、原型制作阶段原型制作是电气硬件设计流程中的重要环节,通过原型制作,可以验证设计方案的可行性,并发现潜在的问题。

在这个阶段,设计师需要将详细设计文档转化为实际的电路板,进行焊接、组装等工艺流程。

还需要进行原型板的调试、验证测试等工作,确保产品的功能和性能都符合要求。

在这个阶段,设计师可能需要多次修改电路原理图和PCB布局,以满足产品的实际需求。

四、验证阶段在原型制作完成之后,就进入了验证阶段。

在这个阶段,设计师需要进行各项验证测试,包括电路功能测试、性能测试、可靠性测试等。

通过这些测试,可以评估产品的质量和稳定性,并发现潜在的问题。

在这个阶段,设计师可能需要不断优化设计方案,以提高产品的性能和可靠性。

最终,要生成验证报告,为产品的量产和上市做准备。

软件硬件产品设计与开发详细流程

对产品进行初步设计:总体

方案设计/研究试验/绘制总

图(草图)/

方案设计说明书

研究试验大纲

研究试验报告

产品开发小组

O

2.2

技木设计

正式展开技术设计,首先初步完成产品总体结构设计

(包括产品外型及内部结构),包括绘制初步结构图、自制零件图、电路原理图等,找出关键技术的解决办法;

研究试验大纲/研究试

验报告/计算书/技术经

济分析报告/技术设计

说明书

产品开发小组

O

2.3

技木设计评审

应对关键设计进行评审

技术设计评审报告

产品开发小组

O

序号

工作项目

说明

形成文件

责任部门

备注

2.4

图样设计

正式设计、绘制全部零部件

图样及编制设计文件

《试制图样》

产品开发小组

■

2.5

图样评审卜发

组织相关人员对设计图纸

进行评审;

《图纸会审纪录》

确认;

《过程流程图》

产品开发小组

•

4.7

编制生产控制上2

对生产制造工艺进行修订

与确认;

《-L2卡》

《控制计划》

产品开发小组

•

4.8

配套体系确认

编制完善的合格供方名单

《合格供方名单》

产品开发小组

•

4.9

成本核算

由财务部负责进行产品详

细的成本核算,确定产品价

格与目标成本;

《成本核算报告》

产品开发小组

•

序号

图纸确认内容:

图纸;

样件制造工艺;

材料清单;

产品标准(初步)

fpga硬件设计流程

fpga硬件设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!按照[fpga硬件设计流程]为主题,以实际应用情况写一篇流程,回答要求步骤详细,回答字数不少于800字。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硬件设计流程图1整个产品的开发步骤,从宏观来看还是遵循从设计到初样到用户试用到改进到产品定型的过程(具体见下图),从阶段上讲是从研发到中试的过程,最后产品技术定型,生产工艺基本定型。

流程各阶段事件说明如下:I.阶段A以上是按照公司的相关流程,如《产品识别程序》、《项目计划编写规范》、《系统设计程序》、《配置管理计划编写规范》等完成,(由部门经理、项目经理等组织完成)II.阶段B(产品、系统整体设计方案)该阶段对于纯粹的软件产品(不涉及硬件)则相当于阶段D1(软件部分概要设计),完成软件的概要设计,这时阶段D1可以忽略;对于纯粹的硬件产品(不涉及软件及电路开发),则直接走外包外协或采购的流程;对于含电路开发的产品(不含软件),则相当于阶段C1(硬件部分概要设计),这时阶段C1可以忽略。

对于软硬件结合的产品,结合《需求规格说明》在《设计方案》中将软硬件的界限,达到的性能要求划分清楚,同时要提出更详细的进度计划和人员安排,若有外形要求也需加入,外形设计直接走外协外包方式。

(由项目经理组织由项目主管设计师、产品结构设计工程师、电路设计工程师和软件设计工程师完成,形成《产品(项目) 系统整体设计报告》)III.阶段C1(硬件部分概要设计)包括行为动作设计,结构设计,框图设计及简单逻辑设计,(根据单位成本和开发时间来具体决定系统结构),若硬件简单,可以省略阶段C2(硬件部分详细设计),(由硬件设计工程师组织完成,《硬件部分概要设计》)IV.阶段C2(硬件部分详细设计)包括细化结构框图,详细的框图与框图之间接口,及完整的逻辑设计,芯片基本定型,并要详细说明涉及的需采购或外包的电路模块。

(由硬件设计工程师组织完成,《硬件部分详细设计》)V.阶段C3(设计实现阶段)完成电路原理图设计,包括可能的软件仿真设计,完成电路板制作和焊接及元器件采购,这里涉及到印刷电路板的外协生产,焊接外协和器件采购等,所有需外协的要求及图纸,均需在项目主管设计师处电子文挡备案,同时需将图纸等打印出来,并要有设计工程师签字,然后由项目主管设计师签字认可,最后由项目经理签字,最后走外协流程;对于采购,也是由设计工程师上报,然后由项目主管设计师签字,最后由项目经理签字,最后走采购流程。

若需采购的数量、单价金额比较小时,也可以经商务授权由部门直接采购。

(由项目主管设计师、电路设计工程师、电路设计辅助工程师等完成,《硬件设计生产资料汇总》含电路原理图、印刷电路板图、元器件清单),这里有版本控制问题,需由项目经理控制。

VI.阶段C4(硬件部分基本单元功能性能测试)对硬件基本的单元模块主要进行功能测试,视情况决定是否进行性能测试,用到需软件测试的部分,可以联合软件底层编写人员一起测试,若简单的测试用例也可以由硬件开发人员自己编写测试。

若电路简单,可跳过阶段C5和阶段C6 。

(由电路设计师,电路设计辅助工程师完成,《硬件部分基本单元功能、性能测试报告》)。

若测试不合格,根据《变更管理控制》,修改相应设计。

VII.阶段C5(硬件部分基本模块功能性能测试)对硬件由单元模块构成的基本模块进行功能测试,视情况决定是否进行性能测试,用到需软件测试的部分,可以联合软件底层编写人员一起测试,若简单的测试用例也可以由硬件开发人员自己编写测试。

若电路不复杂,可跳过阶段C6 。

(由电路设计师,电路设计辅助工程师完成,《硬件部分基本模块功能、性能测试报告》)。

若测试不合格,根据《变更管理控制》,修改相应设计。

VIII.阶段C6(硬件部分系统功能性能测试)对硬件由基本模块构成的系统进行功能测试,视情况决定是否进行性能测试,用到需软件测试的部分,可以联合软件底层编写人员一起测试,若简单的测试用例也可以由硬件开发人员自己编写测试。

(由项目主管设计师,电路设计师,电路设计辅助工程师完成,《硬件部分基本系统功能、性能测试报告》)。

若测试不合格,根据《变更管理控制》,修改相应设计。

IX.阶段D1(软件部分概要设计),若软件不复杂,可以跳过阶段D2。

对基于成熟操作系统的软件开发,基本上遵循《软件概要设计说明书编写规范》编写完成《软件部分概要设计》,没有的项可以省略;对于没有操作系统支持或非成熟操作系统支持的,需在《软件部分概要设计》中,主要描述总体技术方案,系统框架(包括流程图,功能模块),接口设计(模块之间,和硬件的接口,用户接口),运行设计,数据结构设计,数据维护与数据结构升级,可参照《软件概要设计说明书编写规范》部分内容。

(主要由软件设计工程师,软件设计辅助工程师组织完成)X.阶段D2(软件部分详细设计)若软件不复杂,本阶段可以忽略;对基于成熟操作系统的软件开发,基本上遵循《软件详细设计说明书编写规范》编写完成《软件部分详细设计》,没有的项可以省略;对于没有操作系统支持或非成熟操作系统支持的,需在《软件部分详细设计》中主要描述界面详细设计,详细模块设计等,相关内容可参考《软件详细设计说明书编写规范》部分内容。

(主要由软件设计工程师,软件设计辅助工程师组织完成)XI.阶段D3(设计实现阶段)根据《软件部分概要设计》和《软件部分详细设计》进行代码实现,需要外包的根据软件外包流程外包。

这里涉及到程序版本问题,由项目经理控制。

XII.阶段D4(软件部分单元功能性能测试)若软件不复杂,可以跳过阶段D5、D6。

对基于成熟操作系统的软件开发,基本上遵循《软件测试规范》操作。

若和硬件有关联,需和硬件一起联合测试。

对于没有操作系统支持或非成熟操作系统支持的,直接按《设计规范》中划分的模块进行测试。

测试后完成《软件部分基本单元功能、性能测试报告》。

(主要由项目主管设计师,软件设计师工程师,软件设计辅助工程师完成)。

若测试不合格,根据《变更管理控制》,修改相应设计。

XIII.阶段D5(软件部分模块功能性能测试)若软件不复杂,可以跳过阶段D6。

对基于成熟操作系统的软件开发,基本上遵循《软件测试规范》操作。

若和硬件有关联,需和硬件一起联合测试。

对于没有操作系统支持或非成熟操作系统支持的,直接按《设计规范》中划分的模块进行测试。

测试后完成《软件部分基本模块功能、性能测试报告》。

(主要由项目主管设计师,软件设计师工程师,软件设计辅助工程师完成)。

若测试不合格,根据《变更管理控制》,修改相应设计。

XIV.阶段D6(软件部分系统功能性能测试)对基于成熟操作系统的软件开发,基本上遵循《软件测试规范》操作。

若和硬件有关联,需和硬件一起联合测试。

对于没有操作系统支持或非成熟操作系统支持的,直接按《设计规范》中划分的模块进行测试。

测试后完成《软件部分基本系统功能、性能测试报告》。

(主要由项目主管设计师,软件设计师工程师,软件设计辅助工程师完成)。

若测试不合格,根据《变更管理控制》,修改相应设计。

XV.阶段E1和F1分别为采购和外包流程,走相应的商务采购流程和外包流程。

XVI.阶段G((软硬件集成)产品、项目整体系统性能、功能测试)对项目或产品进行整体性能、功能测试,若系统测试不合格,根据《变更管理控制》,修改相应设计。

在内部测试完成后,需完成《用户使用手册》,若有必要,可以送第三方测试,获取权威检测报告。

(主要由项目经理组织完成《产品(项目)功能、性能测试报告》)。

XVII,阶段H(产品、项目安装调试)到现场安装调试,若是产品,每个产品都必须带有《产品检验单》,用户收到到产品后,填写《用户签收单》,若安装人员和产品非同时到,则在安装人员完成安装调试后,填写《产品钥匙交接表》,还需填写《用户信息单》,对需产品培训的用户,需填写《用户培训记录》。

若在安装调试阶段出现问题上门服务后,需填写《产品(项目)安装调试记录》。

用户对产品有意见需填写《产品(项目)用户反馈意见表》。

以后不定期的上门服务,需填写《产品(项目)轮检记录》。

若是售后服务阶段,须填写售后服务部的报修单。

(主要由安装维护人员操作,项目经理协调)XVIII.阶段I(产品、项目用户试用)对于项目客户若没有这要求可以忽略;对于产品主要是解决产品定型问题。

经过一段时间的运行来发现问题。

用户在试用完后,出具一份《用户试用报告》。

在使用期间有问题,可填写《产品(项目)用户反馈意见表》。

(主要由安装维护人员操作,项目经理协调)XIX.阶段J(用户试用反馈信息收集并修正)将《产品(项目)用户反馈意见表》和《产品(项目)安装调试记录》收集到的信息汇总分析完成《产品(项目)用户反馈意见统计分析报告》,根据这报告,同时根据《变更管理控制》,修改相应设计。

(项目经理组织,以项目主管设计师为主完成)XX.阶段K(项目结束)完成《产品(项目)成本分析报告》,《产品(项目)外来文件资料汇总》,对于项目移交相应的文档(根据《项目文挡交付清单》),完成《项目文档清单》,《项目总结报告》,具体依照《项目结项程序》(由项目经理组织,以项目主管设计师为主完成)XXI.阶段L(产品定型)经过一定时间试用及试生产,产品定型,完成《硬件设计生产资料汇总》和《产品(项目)成本分析报告》需要的话,要召开专家论证会或产品定型会,需出具检测报告和用户使用报告。

同时若需要包装的话,完成包装设计,产品信息反馈表,产品装箱清单等。

(由项目经理组织,以项目主管设计师为主完成)XXII.阶段M(生产、销售)根据市场反映量生产销售,或是项目中需要批量,则按生产流程生产,每个产品需检测(若非成规模流水线生产则每个产品需添写《产品检验单》,若规模生产检验方法另行规定)。

各阶段驱动关系说明如下:i.从阶段A—>阶段B按公司流程对《项目计划》进行评审,至少需得到部门经理签字认可。

ii.从阶段B—>阶段C1,D1,E1,F1完成《产品(项目) 系统整体设计评审报告》,由部门经理组织完成(需包括委托方代表)。

iii.从阶段C1—>阶段C2完成《硬件部分概要设计评审》,由项目经理组织完成。

(视合同决定是否需委托方代表)。

iv.从阶段C2—>阶段C3完成《硬件部分详细设计评审》,由项目经理组织完成。

(视合同决定是否需委托方代表)。

v.从阶段C4—>阶段C5《硬件部分基本单元功能、性能测试报告》上至少需要项目经理签字认可方可继续,若测试不通过需修正相应设计,若实在达不到要求,按项目失败退出程序走。

vi.从阶段C5—>阶段C6《硬件部分基本模块功能、性能测试报告》上至少需要项目经理签字认可方可继续,若测试不通过需修正相应设计,若实在达不到要求,按项目失败退出程序走。

vii.从阶段C6—>阶段G《硬件部分基本系统功能、性能测试报告》上至少需要项目经理签字认可方可继续,若测试不通过需修正相应设计,若实在达不到要求,按项目失败退出程序走。

viii.从阶段D1—>阶段D2《软件部分概要设计评审》由项目经理组织完成。