中继卫星系统信道模拟器硬件电路设计

GLONASS卫星信号模拟器设计与实现

2 . S h e n z h e n To j o i n C o mmu n i c a t i o n Te c h n o l o g y Co . , Lt d ,S h e n z h e n 5 1 8 0 0 0 ,C h i n a )

A b s t r a c t : I n o r d e r t O s o l v e t h e p r o b l e m o f t h e s p e c i a l GLONAS S e p h e me r i s ,a n d t h e g e n e r a l 2 - o r d e r d i g i t a l{ r e q u e n c y s y n t h e s i s me t h o d i s d i f f i c u l t t o me e t t h e p r e c i s i o n o f s a t e l l i t e s i g n a l s i mu l a t o r ,t h e o v e r a l l s t r u c t u r e o f GLONAS S s a t — e l l i t e s i g n a l s i mu l a t o r i s d e s c r i b e d o n t h e b a s e o f a n a l y z i n g GI ONAS S s i g n a l s t r u c t u r e a n d p r o p a g a t i o n mo d e 1 . A d e — s i g n i s i n v o l v e d i n c l u d e s Th e s a t e l l i t e p o s i t i o n i s c a l c u l a t e d u s i n g 4 - o r d e r Ru n g e - Ku t t a n u me r i c a l i n t e g r a t i o n e x t r a p o l a — t i o n,t h e s i mu l a t o r s i g n a l i s g e n e r a t e d u s i n g h i g h - o r d e r d i g i t a l f r e q u e n c y s y n t h e s i s t e c h n o l o g y . Ex p e r i me n t a l r e s u l t s s h o w t h e s a t e l l i t e p o s i t i o n p r e c i s i o n i s hi g h u s i n g 4 - o r d e r Ru n g e — Ku t t a n u me r i c a l i n t e g r a t i o n e x t r a p o l a t i o n . Ke y wo r d s : s i g n a l s i mu l a t o r ;o r b i t i n t e g r a t i o n ;p r e c i s e p s e u d o r a n g e ;mu l t i - o r d e r DDS

cmt2310a电路设计

cmt2310a电路设计CMT2310A是一种常见的电路设计,广泛应用于数码设备、通信设备和汽车电子等领域。

本文将从电路设计的基本原理、功能分析以及一些常见问题解决方案等方面进行详细介绍,以期帮助读者更好地理解和应用CMT2310A电路设计。

首先,CMT2310A电路设计的基本原理是基于模拟电路的工作原理。

它的基本功能是处理模拟信号,对输入信号进行放大、滤波、调节和输出等处理。

这种电路设计一般包括输入端、放大器、滤波器、调节器和输出端等组成部分。

其次,对于CMT2310A电路设计的功能分析,我们可以从以下几个方面进行详细说明:1.输入端:CMT2310A电路设计的输入端是接收外部信号的地方。

它通常包括一个输入电路,负责将外部信号进行输入处理,并将其传递给放大器。

这样可以保证输入信号的稳定性和可靠性。

2.放大器:CMT2310A电路设计中的放大器是非常关键的部分。

它负责将输入信号放大到所需的幅度,以便后续电路对其进行处理。

放大器一般分为直流放大器和交流放大器,根据具体的应用需求选择合适的类型。

3.滤波器:CMT2310A电路设计中的滤波器可以对输入信号进行频率选择性滤波。

这对于许多应用来说十分重要,比如对输入信号进行陷波滤波或者带通滤波等。

滤波器的设计需要根据具体的应用需求和频率范围来选择。

4.调节器:CMT2310A电路设计中的调节器用于对输出信号进行电平调节或者其他电性参数的调节。

这能够确保输出信号满足特定的要求,尤其在一些需要精确控制的应用中非常重要。

5.输出端:CMT2310A电路设计的输出端通常是将处理后的信号输出到其他设备或者传输线路。

输出端需要确保输出信号的质量和稳定性,以便后续设备能够准确地接收和处理。

最后,对于CMT2310A电路设计的一些常见问题解决方案,我们可以从以下几个方面进行介绍:1.信噪比问题:在CMT2310A电路设计中,信噪比是一个重要的指标。

为了提高信号的品质,需要合理设计和选择放大器、滤波器等器件,并采取一些降噪措施,如增加滤波器的带宽或者增加滤波器的阻尼。

无线电硬件电路的设计与调试

无线电硬件电路的设计与调试摘要:与前面两次一样,作为通讯的“第3次”革命,软件无线电技术的产生也给通讯带来了巨大的冲击,使通讯的通讯更加便利。

软件无线电技术主要是使用一个通用的、开放的硬件平台,通过程序设计,来完成不同的工作,从而达到一种装置的多用途的目的,这样就可以大大地提升通讯装置的使用,从而提升通讯的效能。

文章着重对无线电的硬件线路的设计和调整作了一定的分析和讨论。

关键词:无线电;硬件电路;调试引言硬件线路是电路工作的根本,适当的硬件线路设计和正确的调试,能极大地提高电路工作的通畅性,最大限度地减轻电路工作负荷,确保电路工作的稳定性。

由此可以看出,在无线通信系统中,无线通信系统的硬件电路的开发和调试对其正常工作有着举足轻重的影响。

下面就是具体的无线电的硬件电路的设计和调试作了说明。

1无线电路的设计1.1系统框架结构而在此背景下,利用计算机的优势,对广播系统的各个功能进行了设计和开发。

与常规的无线通讯技术不同,它仅仅是以硬件为基础,通过灵活多变的程序设计来完成多种功能。

但是,要想达到这些目的,硬件平台是不可或缺的,所以,我们必须要建立一个开放的、通用的硬件平台,再之后,我们才可以为这个硬件平台进行软件程序的开发,来实现我们所要做的工作,比如:调制解调类型、加密模式、通信协议等,从而推动通信设备的一机多用。

毫无疑问,软件无线电技术将会让这种新型的无线电通讯装置可以在各种环境下,满足各种不同的通讯要求,从而大大地提升了装置的使用效率,让通讯变得更加有效。

在设计与之配套的硬件时,要特别留意几个关键点。

1.2主控与接口单元设计在无线通信系统中,主控制器和界面模块的设计是一个关键环节,它直接关系到整个通信系统的正常工作,以及整个通信系统的正常工作。

嵌入式的系统设计被用于这种新型无线电通信系统的主控单元中,服务模式的加载与调度是通过CPU来完成的,并且还能给予VGA视频输出、USB、音频红外线等。

在必须要安装一台高性能CPU之外,FPGA芯片也是不可或缺的一部分。

卫星链路延时模拟器设计与实现

卫星链路延时模拟器设计与实现吕朋泽;乔庐峰;陈庆华;陈倩;梅立春【摘要】Satellite communication,as compared with other communication systems,has its unique advantages.However,satellite communication system has fairly long end-to-end propagation delay,and this would challenge the protocol design of satellite communication network.A satellite link delay simulator for satellite IP network protocol design,test and verification is presented in this paper.The delay simulator is implemented on a Xilinx xc5vlx50t FPGA platform with dual 100 M Ethernet interfaces.The user data and corresponding control information are stored in an external DDR2 SDRAM and read out after a certain delay set by the user.DDR2 SDRAM is used as a large buffer to ensures sufficient delay under the throughput of 100Mb/s.The maximum delay is 1 000 ms and the delay control accuracy is 0.5 ms.%卫星通信作为信息时代重要的通信手段,具有独特的优势与其他通信手段不可替代的地位.然而,卫星通信系统相较于其他通信方式而言,却具有较长的端到端传播时延,将对卫星通信网络的协议设计带来挑战.课题的研究目标是设计一款卫星链路延时模拟器,用于卫星IP网络的协议设计与实际测试验证.使用Xi1inx xc5vlx50t FPGA平台和双端口100 M以太网扩展板,实现该延时模拟器.被延时的用户数据和对应的控制信息存储在外接DDR2 SDRAM中,保证了在100 Mb/s通信带宽下提供足够延时,最大延时为1 000 ms,延时控制精度为0.5 ms.【期刊名称】《通信技术》【年(卷),期】2017(050)004【总页数】6页(P826-831)【关键词】卫星通信;延时;DDR2;描述符;FPGA【作者】吕朋泽;乔庐峰;陈庆华;陈倩;梅立春【作者单位】中国人民解放军理工大学通信工程学院,江苏南京210007;中国人民解放军理工大学通信工程学院,江苏南京210007;中国人民解放军理工大学通信工程学院,江苏南京210007;中国人民解放军理工大学通信工程学院,江苏南京210007;中国人民解放军理工大学通信工程学院,江苏南京210007【正文语种】中文【中图分类】TP393;TN915.05卫星通信是一种利用人造卫星作为中继站转发无线电波,从而实现两个或多个地球站之间信息交互的通信方式。

无线信道模拟器的研究与设计

第7期2018年4月No.7April,20181 无线通信技术发展概述近年,无线通信技术在蓬勃发展。

任何一种新的无线通信技术都需要在实际的信道中测试验证通过后方可商用。

而目前,随着许多频段陆续商用,实地的信道测试会对正常通行用户造成干扰。

取而代之的则是采用计算机仿真验证的形式,其实现方式简单、容易监测,被广泛采用,但其仿真速度往往与计算机性能有很大关系,并且存在计算机与实际设备的兼容性等问题。

无线信道模拟器的出现可以弥补计算机仿真的不足,将信道模型从计算机上转移到可编程芯片上,利用高速的FPGA 芯片实现并行高速仿真,界面友好可观,调试方便。

2 信道模型通常多径信道采用延时抽头结构模型,多条单路径衰落经过相对时延求和,得到总的信道响应[1-4],即:()()()()()10*()l L j t l l l y t s t h t A t e s t ϕτ−===−∑(1)式(1)中s (t )是输入信号,h (t )是信道冲击响应A l (t )表示幅度响应,φl (t )表示相位响应,τl 是第l 路的时延,共L 条路径。

每条单路径信道选用通信信道中常见的瑞利衰落信道,其特点是瑞利概率分布的包络和均匀分布的相位。

单路径衰落信道建模为窄带随机过程,一般有3种建模方法:(1)时域滤波法;(2)频域变换法;(3)Jakes 算法。

方法1适合多普勒频率、滤波器带宽较窄的衰落信道建模,但其利用到时域卷积,计算量大;方法2将时域卷积转换到频域相乘,比方法1降低了复杂度,但是其不适合窄带、多普勒频移较小的情形。

方法3最为理想,也是本文所采用的,可以对任意多普勒频移的情形进行建模[1-4]。

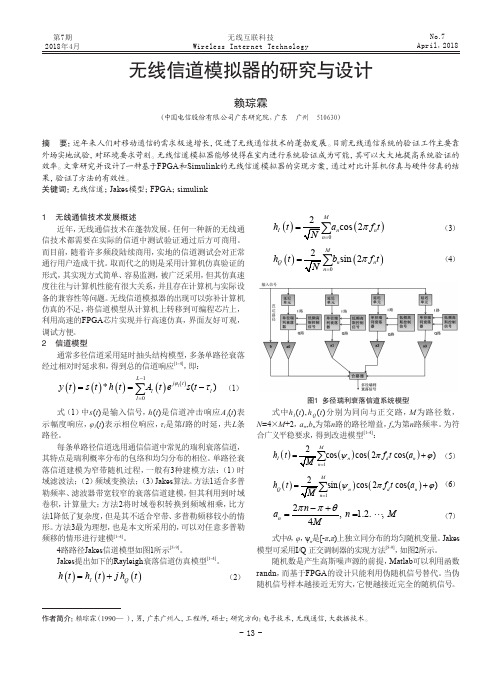

4路路径Jakes 信道模型如图1所示[5-9]。

Jakes 提出如下的Rayleigh 衰落信道仿真模型[1-4]。

()()() I Q h t h t j h t =+(2)()()0cos 2MI nnn h t a f t π==(3)()()sin 2MQ n n n h t b f t π==(4)图1 多径瑞利衰落信道系统模型式中h I (t ),h Q (t )分别为同向与正交路,M 为路径数,N =4×M +2,a n ,b n 为第n 路的路径增益,f n 为第n 路频率。

G通信信号模拟器系统软件设计

软件设计目标

实现G通信信号模拟功能 提高模拟器的性能和稳定性 优化用户界面,提高用户体验 保证软件的可扩展性和可维护性

软件设计原则

模块化设计:将系统划分为独立的模块,便于维护和扩展 面向对象设计:采用对象导向编程思想,提高软件的可重用性和可维护性 易用性设计:软件界面友好,操作简单,便于用户快速上手 安全性设计:保证数据安全,防止非法访问和数据泄露

05

软件测试与验证

测试环境搭建

测试环境:模拟器系统软件测试所需的环境,包括硬件和软件配置 搭建步骤:准备测试工具、安装测试软件、配置测试环境参数等 测试环境要求:满足软件测试需求,保证测试结果的准确性和可靠性 测试环境搭建的意义:为软件测试与验证提供必要条件,确保软件质量与稳定性

功能测试

测试目的:验证 软件是否符合需 求规格

02

系统架构设计

系统架构概述

系统架构设计采用分层架构思想,分为应用层、中间件层和设备驱动层。 应用层负责实现各种业务功能,包括信号模拟、信号处理和用户界面等。

中间件层提供各种通用服务,如数据传输、消息队列和定时器等,方便应用层调用。

设备驱动层与硬件设备直接交互,负责控制硬件设备的操作和数据采集。

04

用户界面设计

界面布局设计

主界面:显示 信号模拟器的 状态和主要功

能选项

设置界面:用 于调整模拟器 的参数和设置

信号界面:展 示信号的实时 变化和历史数

据

帮助界面:提 供操作说明和

系统信息

控件功能设计

控件类型:包括按钮、文本框、下拉框等常用控件 控件功能:实现用户与模拟器系统的交互操作,如输入参数、启动停止等 控件布局:根据用户需求和操作习惯,合理布局控件位置,提高用户体验 控件样式:根据系统风格和用户喜好,设计控件的样式和外观,如颜色、字体等

高效硬件模拟器与仿真器的设计与实现

高效硬件模拟器与仿真器的设计与实现近年来随着人工智能、区块链等技术的不断发展,硬件仿真和模拟技术的应用越来越广泛,可以在很大程度上降低开发成本和加速产品上市速度。

为此,高效硬件模拟器和仿真器的设计与实现成为了当前硬件技术领域的热门话题。

一、硬件模拟器的设计与实现硬件模拟器是一种能够模拟特定电路的软件,仿真的结果可以与物理电路的实际运行结果一致。

通常情况下硬件模拟器可以实现的功能非常全面,如波形采集、仿真测试等。

设计和实现高效硬件模拟器需要满足以下几个方面的要求:1.高效性高效性是硬件模拟器最基本的要求。

设计和实现高效硬件模拟器需要考虑诸如仿真算法、仿真精度等因素。

同时,需要使用高性能计算机和专用硬件,如FPGA 等,以提高仿真效率。

2.可靠性可靠性是硬件模拟器的核心,其母板是数据的准确性与模拟精度。

在硬件模拟器的设计和实现过程中,需要考虑如何降低误差率、提高仿真精度等因素,以提高其可靠性。

3.可扩展性可扩展性是硬件模拟器一个必备的特性。

当电路规模扩大时,硬件模拟器需要能够满足不断增长的资源需求。

因此,需要设计可扩展的硬件模拟器,以满足不断扩增的电路规模。

二、硬件仿真器的设计与实现硬件仿真器是一种能够模拟特定电路的软件,仿真的结果也可以与物理电路的实际运行结果一致。

需要与硬件模拟器区分开来的是,硬件仿真器只考虑电路的逻辑功能,不涉及电路的物理特性。

设计和实现高效硬件仿真器需要满足以下几个方面的要求:1.高效性设计和实现高效硬件仿真器需要考虑的因素与硬件模拟器相似,如仿真算法、仿真效率等因素。

但是不同的是,硬件仿真器更侧重于对电路逻辑功能的模拟和测试。

2.可靠性可靠性也是硬件仿真器不可忽视的因素。

设计和实现可靠的硬件仿真器需要考虑逻辑功能是否正确、仿真是否准确等因素。

3.易用性易用性是硬件仿真器的一个重要特性。

需要设计和实现易于使用的硬件仿真器,以方便初学者或不熟悉电路的技术人员快速上手。

三、技术的发展趋势随着硬件技术和计算机技术的不断发展,硬件模拟器和仿真器的设计和实现也在不断演进。

单片机硬件电路设计(二)2024

单片机硬件电路设计(二)引言概述:单片机硬件电路设计是嵌入式系统开发中非常重要的一环。

本文将介绍单片机硬件电路设计的相关内容,包括输入输出接口设计、时钟电路设计、电源电路设计、存储器电路设计和外围电路设计。

正文:1. 输入输出接口设计- 确定需要的输入输出接口类型,如GPIO、UART、SPI等。

- 根据系统需求,选择合适的IO器件,如电平转换芯片、阻抗匹配电路等。

- 进行引脚分配,保证输入输出信号的正常传输。

- 根据实际使用情况,添加辅助电路,如防抖电路、滤波电路等。

2. 时钟电路设计- 根据单片机型号和需求,选择适当的时钟源。

- 设计时钟电路,包括晶振、时钟源输入电路以及相应的滤波电路。

- 考虑时钟信号的稳定性和可靠性,添加必要的降噪电路。

- 若需要系统时钟分频,设计合适的时钟分频电路。

3. 电源电路设计- 确定单片机的供电方式,如直流电源、稳压电源等。

- 设计电源输入电路,包括滤波电路、过压保护电路等。

- 根据单片机工作电压要求,选择适当的稳压电源或降压电路。

- 添加电池电压监测电路,实时监测供电电压并预警。

4. 存储器电路设计- 根据系统需求,选择合适的存储器类型,如RAM、ROM、Flash等。

- 设计存储器接口电路,包括地址线、数据线和控制信号的连接电路。

- 根据存储器的读写速度要求,设计合适的使能信号和时序电路。

- 添加存储器保护电路,防止意外写入或读取。

5. 外围电路设计- 根据系统需求,设计外围电路,如LCD显示屏驱动电路、按键输入电路等。

- 考虑外围电路与单片机的接口和兼容性。

- 通过添加电平转换器和驱动器等电路,保证外围设备的正常工作。

- 添加外围电路检测电路,实时监测外围设备的状态。

总结:单片机硬件电路设计是嵌入式系统开发中必不可少的环节,涉及到输入输出接口、时钟电路、电源电路、存储器电路和外围电路的设计。

通过合适的硬件电路设计,可以提高系统性能和稳定性,实现项目的顺利运行。

GPS卫星信号模拟器中频信号处理与实现

摇 基金项目: 国家自然科学基金资助项目(60027001) ; 北京市科技新星计划资助项目 摇 作者简介: 李保柱(1967-) , 男, 江苏连云港人, 博士生,leebz285712@ tom. com.

812

号

[2]

北 京 航 空 航 天 大 学 学 报摇 摇 摇 摇 摇 摇 摇 摇 摇 摇 摇

好的抗混叠、 抗镜像功能, 运算效率高、 节省硬件 资源. 一 般 单 速 率 数 字 FIR ( Finite Impulse Re鄄 sponse) 滤波器抽头数由下式决定: y( k) = a( n) x( k - n) 摇 移 n=0

N -1

利用内插方法实现的数字低通滤波器具有良

钟周期数 L 值为 4,取样速率为 37 . 5 MHz. 达到抗 混叠、 抗镜像功能. 滤波器的并行处理位数越多, 需要利用的 FPGA 资源越多. 滤波器的取样速率 取合适的参数,达到数字滤波目的. 与系统时钟频率 f clk 、 输入取样数据比特位宽 B 、

经低通数字滤波器 h ( n2 T2 ) 滤去镜像频谱,

^

2 基带数字信号到中频模拟信号实现

个采样点插入 I -1 个零点,得到内插信号. 应用内 插理论能够在较低的采样速率产生较高频率的中 频信号,降低整个系统的基带处理频率,降低对微 处理器和 FPGA( Field Programmable Gate Arrays) 运算速度的要求,提高时域分辨率. 对数字信号进 行内插、数字滤波,D / A( Digital / Analog) 变换和模 拟滤波, 实现中频信号的频率变换, 得到 GPS 模 拟器中频模拟信号. GPS 模拟器基带数字信号变 换为中频模拟信号实现原理见图 2. 对基带数字信号进行 I 倍零内插, 即每隔 1

卫星导航接收机低噪放电路模块设计

卫星导航接收机低噪放电路模块设计摘要:卫星导航接收机的低噪声放大电路是卫星接收机的主要部件,主要包括滤波器和低噪声放大器。

该电路是系统的射频前端,天线除外。

有效地完成射频前端的设计可以优化接收机的性能,从而提高卫星导航接收机的灵敏度等指标。

随着市场和产品小型化的需求不断增加,模块化电路构建成为一种趋势。

电路的模块化设计可以有效地控制设计成本,减少设计错误。

模块的反复使用确保了设计方案的成熟。

本文设计的射频放大电路主要由两级滤波器、低噪声放大器芯片和π型阻尼器组成。

最后,该方案的可行性由模拟确定。

关键词:卫星导航;低噪;电路模块设计引言近些年来,随着通信系统的快速发展和兴盛繁荣,射频电路得到了极大的推动,其应用也日益广泛,微波射频技术也因此变得越来越重要,从而在通信领域占有了非常重要的地位,各种各样的放大器也应运而生。

以接收机为例,低噪声放大器都处于它的第一部分,它的好坏对于接收机的性能会产生非常重要的影响,所以低噪声放大器的设计充满挑战,必须要严谨且规范。

通常接收机收到的天线信号功率都非常小,通常从-100dBm到-70dBm,但信号处理器对于这样的微弱信号都无法接收到,所以一般要先进行放大,这里就需要具有一定增益的低噪声放大器。

低噪声放大器只有增益还不能满足系统的要求,它必须还要有足够小的噪声,不影响传输信号的信噪比。

低噪声放大器的传输系统中,信号进入系统后先经过低噪声放大器将信号的功率进行放大,同时又尽可能的避免噪声的引入。

因为放大器处于前端,所以系统的噪声几乎就由其决定了。

随着卫星导航的需求,对低噪声放大器的性能要求也随之增加,对于不同频段的卫星信号,如何保证不失真的接收且滤除干扰正是本文研究的重点。

1国内外研究现状通信技术的发展不仅包括产品性能的进步,同时一起发展进步的还要有生产和加工工艺,那么低噪声放大器的发展同样也需要基础工艺的支撑。

工业技术的不断发展和生产工艺的不断提高,微波晶体管在频率、噪声、功率等方面得到了很大的改善和提高,同时小型化和重量轻的放大器也变得越来越被需要,所以有了微波混合集成电路的产生,系统集成中,这些工艺就变得尤为重要,再后来出现了微波单片集成电路(MMIC),放大器芯片也就应运而生,从而放大器产品在噪声性能,高频率、大功率等方面发展更加迅速。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

中继卫星系统信道模拟器硬件电路设计李炜;马乐;段世刚;孙向聚【摘要】For the design and implementation of channel simulator for relay satellite system,and based on the study for simu-lation principle and working process of the channel simulator,the IF signal processing board card,receiving and transmitting board cards of the channel simulator were designed in detail for hardware circuits in combination with the practical application. The configuration program of the high-speed DA chip was designed based on FPGA platform,and simulated with Modelsim to verify the correctness of its functions. The hardware of the board card is tested,and the test results show that the designed hardware cir-cuit is completely in conformity with the operating requirements in testing of the channel simulator for relay satellite system.%结合实际应用,针对中继卫星系统信道模拟器的设计和实现,在对信道模拟器的模拟原理和工作流程进行研究的基础上,从信道模拟器的硬件电路入手,对信道模拟器的中频信号处理板卡、接收及发射板卡进行了详细的设计.基于FPGA平台对高速DA芯片的配置程序进行设计,并对该配置程序进行ModelSim仿真,验证其功能的正确性.最后对板卡进行了硬件测试,测试结果表明,设计的硬件电路完全符合中继卫星系统信道模拟器在测试中的使用要求.【期刊名称】《现代电子技术》【年(卷),期】2016(039)001【总页数】5页(P68-71,75)【关键词】信道模拟;DDR2;SPI;高速信号采集【作者】李炜;马乐;段世刚;孙向聚【作者单位】国网甘肃省电力公司信息通信公司,甘肃兰州 730050;国网甘肃省电力公司信息通信公司,甘肃兰州 730050;国网甘肃省电力公司信息通信公司,甘肃兰州 730050;国网甘肃省电力公司信息通信公司,甘肃兰州 730050【正文语种】中文【中图分类】TN95-34随着空间技术的发展,现有的地面测控网已不能满足要求,而中继卫星可以大幅提高测控网的性能[1]。

因此,许多国家目前都在积极地对其进行研究,其中美国、俄罗斯等国家均已建成完善的中继卫星系统[2],我国也已开始建设自己的中继卫星系统。

然而中继卫星的测试过程受地理环境和天气因素的影响也较大,现场试验的方法并不能满足实际需求。

信道模拟器作为评估通信系统性能的有效手段,是通信系统性能测试的重要工具。

当前对卫星信道的传输特性已经进行了较为深入的理论研究,并已经得出一些具有实际意义的理论成果和仿真模型[3],但是国内基于这些仿真模型的硬件信道模拟器产品较为少见。

基于这种需求,设计研制中继卫星系统信道模拟器具有重大的工程和实践意义。

本文根据模拟器系统组成及工作流程,首先对模拟器硬件电路进行总体设计,如图1所示。

考虑实现难度及各方面因素,将模拟器硬件电路分为接收及发射板卡、中频信号处理板卡两块板卡分别进行设计。

其中,接收及发射板卡包括接收单元、频综模块、发射单元。

中频信号处理板卡主要包括模拟信号调理电路、A/D转换电路、D/A转换及幅度调整电路、FPGA功能电路、DSP功能电路、PLL时钟倍频电路、时钟整形分配电路、复位管理电路、大容量数据缓存电路、电源转换及排序电路。

硬件电路总体设计方案确定后,需要对电路设计中的关键芯片进行选型分析,主要包括:FPGA,ADC,DAC,DSP及大容量存储器。

设计中FPGA主要负责模拟功能的实现,从乘法器资源需求分析以及I/O管脚需求分析,并考虑一定的资源裕量,选用Xilinx公司的Virtex⁃6系列XC6VSX315T⁃FFG1156。

其乘法器资源为1 344个、可用管脚600个,均满足本设计要求。

考虑现有器件及前期成熟的A/D转换电路设计,量化位数选为12 b。

为了保证信号质量,模拟输入信号及时钟信号均采用差分形式,因此模/数转换芯片必须具备差分输入接口[4]。

因此,ADC芯片采用TI公司的ADS5463。

在本设计中,数/模转换芯片选用ADI公司的AD9735,其分辨率为12位、更新速率最高可达1.2 GS/s,其无杂散动态范围达77 dBc (fout=100 MHz),满足使用要求。

另外,DSP用于实现上位机与板间的实时通信[5],故需要选择处理速度高的DSP芯片,综合考虑后选用TI公司推出的TMS320C6455芯片。

最后,设计中选用大规模可编程器件FPGA控制高速DDR 来构建虚拟FIFO以满足延迟存储深度要求。

2.1 接收及发射板卡设计根据实际功能需求,设计接收及发射板卡,该板卡的功能框图如图2所示,包括接收单元、频综模块、发射单元。

接收单元对模拟输入信号的幅度进行调理,使其满足中频板A/D采样电路幅度要求。

输入信号频率范围为(140±25)MHz,功率范围为-50~0 dBm。

为保证模拟信号质量,在进行AGC增益控制之前,需对该信号进行带通滤波。

带通滤波器设计指标:中心频率为140 MHz,3 dB带宽为60 MHz,带内平坦度小于0.2 dB,带外抑制大于47 dBc@ fo±45 MHz。

滤波后的信号受衰减控制量控制,使中频板输入信号的幅度保持恒定。

AGC增益控制电路输出幅度最大能够达到10dBm。

在默认状态下,考虑器件的安全运作,AGC对模拟输入信号功率进行全衰。

频综模块为中频信号处理板卡提供工作时钟,频率范围为100~550 MHz,由输出频率控制信号对频率选择,频率分辨率为1 MHz。

为便于调试,频综模块的时钟输出频率可通过拨码开关进行控制[6]。

发射单元对中频信号处理板卡模拟输出信号幅度进行控制,使其电平保持在-80~0 dBm范围之内。

为保证信号质量,信号幅度调整以后需要进行带通滤波,带通滤波的设计指标:中心频率为140 MHz,3 dB带宽为60 MHz,带内平坦度小于0.2 dB,带外抑制大于45 dBc@ fo±45 MHz。

2.2 中频信号处理板卡设计结合中频信号处理电路功能需求,中频信号处理电路由模拟信号调理电路、A/D转换电路、D/A转换及幅度调整电路、FPGA功能电路、DSP功能电路、时钟整形分配电路、复位管理电路、大容量数据缓存电路、电源转换及排序电路组成。

为了将模拟信号变换为数字信号,在数字域对信号进行模拟信息的叠加,实现模拟器的模拟功能,本设计采用变压器进行A/D模拟前端设计和AC耦合的变压器耦合方式。

模拟输入信号电平要求:满量程输入为2.2 VPP,共模电压为2.4 V。

AIN_I+和AIN_I-是经模拟调理电路调理后的信号,幅度为2 VPP,满足A/D转换幅度要求。

考虑冗余设计,将VREF管脚输出的2.4 V电压用于共模电压偏置。

选定A/D芯片后需要进行A/D模拟前端调理电路的设计。

模拟信号调理电路接收经接收及发射板卡幅度调整后的模拟信号,此信号幅度约为2 VPP,已满足A/D转换电路输入电平的要求(ADS5463满量程输入为2.2 VPP)。

参考ADS5463评估版,为提高A/D前端幅频响应性能并考虑到变压器的幅相平衡特性,设计双变压器级联形式的调理电路。

由于A/D采样时的量化位数为12 b,则D/A芯片位数至少为12 b,并考虑前期成熟电路设计,D/A转换芯片选用ADI公司的AD9735,D/A输出满量程电流为10 mA,通过外接25 Ω电阻将输出电流转换为电压信号,幅度约为0.5 VPP。

因为AD9735的输出信号为差分的模拟电流信号,需要将其转换为单端信号,采用National Semi⁃conductor公司的高速运放LMH6738进行调整。

LMH6738的放大倍数设为2.51,故运放输出的模拟信号幅度为1.25 VPP。

时钟分配之前需要将时钟输入信号进行单端转差分,结合前期成熟电路设计,时钟分配芯片选用Semiconductor Components公司的MC100LVEP111。

MC100LVEP111的时钟输入端既可采用单端形式也可采用差分形式,而差分时钟抗干扰能力强,因此本设计采用差分形式。

基于对硬件乘法器、逻辑资源及通用I/O管脚数量的需求分析,由于FPGA的输入接口LVDS_25电平标准兼容A/D数据输出端口的LVDS电平标准,故两者可以无缝对接。

AD9735的数据输入端口LVDS电平标准为:摆幅最大为750 mV,共模电压典型值为1.2 V,故芯片AD9735的数据输入端口LVDS标准兼容LVDS_25的标准,两者可以无缝连接。

FPGA与DSP的EMIF接口电路的bank电压标准为2.5 V,而DSP芯片TMS320C6455ZTZD 的EMIF接口电压标准为3.3 V,因此在两者之间进行数据传输时需要电平转换,这里采用驱动芯片SN74AVC32T245GKER进行转换。

在本次设计中,大容量数据缓存电路采用DDR2实现。

DSP数据处理电路选用TI 公司的定点数字信号处理器TMS320C6455ZTZ,该款芯片兼容33 MHz/66MHz 的PCI总线速率,可更好地保证后期的扩展需求。

DSP功能电路的外围接口电路如图3所示。

设计中,复位电路对DSP进行监控,由DSP控制FPGA进行复位。

复位管理电路采用MAXIM公司的MAX706ARESA。

板卡上电后,由TPS3808G01输出一个20 ms的低脉冲至DSP的POR管脚,控制DSP进行上电加载,同时FPGA进行自动加载。

当DSP和FPGA分别加载成功后,FPGA的DONE管脚输出高电平信号至DSP,当DSP检测到该信号后再对FPGA进行软件复位。

电源转换电路将CPCI机箱供电转换为板卡需要的电源,电源排序电路是将电源转换电路输出的电源进行排序,使其满足板卡电源要求。