内存对齐的目的和原理

cuda 内存对齐要求

cuda 内存对齐要求

CUDA内存对齐要求是指在进行CUDA编程时,数据在内存中的存储位置需要满足一定的对齐条件,以保证程序的正确性和性能。

具体来说,CUDA要求全局内存中的数据类型大小必须是1、2、4、8或16字节,并且数据的起始地址必须是该数据类型大小的整数倍,即满足自然对齐。

如果数据不满足这些对齐要求,可能会导致访问效率下降,甚至产生错误的结果。

此外,CUDA还提供了内置的向量化类型,如float2、float4等,这些类型的对齐要求自动满足。

对于结构体等复合类型,可以通过使用对齐说明符(如__align__(8)或

__align__(16))来强制满足对齐要求。

在进行CUDA编程时,需要注意数据的对齐要求,并尽可能保证数据满足这些要求,以提高程序的性能和稳定性。

同时,CUDA也提供了一些工具和方法来检测和处理内存对齐问题,如cudaMemcpy、cudaMalloc等函数。

STM32--内存对齐

STM32--内存对齐

举例吧:

u8 array[n]; // 这是1字节对齐的,与n取值无关。

u16 array[n]; // 这是2字节对齐的,与n取值无关。

u32 array[n]; // 这是4字节对齐的,与n取值无关。

你把u16型数组的长度改为256可用,那仅仅是连接器的偶然,知识要严谨不能依赖偶然;既然整个数组的起始地址不能保证是4字节对齐,你在此数组的52索引处也同样不能保证4字节对齐。

而你定义的结构体必须4字节对齐,因为其成员是float类型。

keilmdk中,你要查看一下__align()的用法,这是解决你问题的关键字;

iarewarm中,你查看一下#pragma data_alignment的用法,这是解决你的问题的关键;

楼主依据以上知识点去实验,了解对齐的知识;真理不怕检验。

只能说楼主的知识储备不过关,不怪编译器不行。

float型数据是4字节的,但你定义u16的数组,要对齐完全靠运气,如果换成u32,那就不会有对不齐的问题了。

stm32的密集存储节省了不少内存呢,arm9不管u8、u16还是u32,都是要占用4字节的空间,地址值是能被4整除的。

或者,你把结构体和你的数组用一个共用体包起来,就不担心对齐的问题了,这样保证数组的开始的地址是能被4整除的。

结构体对齐

关于 C 语言中的结构体对齐(1)什么是字节对齐一个变量占用 n 个字节,则该变量的起始地址必须能够被n 整除,即: 存放起始地址 % n = 0 ,对于结构体而言,这个 n 取其成员种的数据类型占空间的值最大的那个。

(2)为什么要字节对齐内存空间是按照字节来划分的,从理论上说对内存空间的访问可以从任何地址开始,但是在实际上不同架构的 CPU 为了提高访问内存的速度,就规定了对于某些类型的数据只能从特定的起始位置开始访问。

这样就决定了各种数据类型只能按照相应的规则在内存空间中存放,而不能一个接一个的顺序排列。

举个例子,比如有些平台访问内存地址都从偶数地址开始,对于一个 int 型( 假设 32 位系统 ),如果从偶数地址开始的地方存放,这样一个读周期就可以读出这个 int 数据,但是如果从奇数地址开始的地址存放,就需要两个读周期,并对两次读出的结果的高低字节进行拼凑才能得到这个 int 数据,这样明显降低了读取的效率。

(3)如何进行字节对齐每个成员按其类型的对齐参数 (通常是这个类型的大小 )和指定对齐参数 ( 不指定则取默认值 ) 中较小的一个对齐,并且结构的长度必须为所用过的所有对齐参数的整数倍 ,不够就补空字节。

这个规则有点苦涩,可以把这个规则分解一下,前半句的意思先获得对齐值后与指定对齐值进行比较 ,其中对齐值获得方式如下:1. 数据类型的自身对齐值为:对于 char 型数据,其自身对齐值为 1 ,对于 short 型为2 ,对于 int, long, float 类型,其自身对齐值为 4 ,对于 double 类型其自身对齐值为8 ,单位为字节。

2. 结构体自身对齐值:其成员中自身对齐值最大的那个值。

其中指定对齐值获得方式如下:#pragma pack (value) 时的指定对齐值 value 。

未指定则取默认值。

后半句的意思是主要是针对于结构体的长度而言,因为针对数据类型的成员,它仅有一个对齐参数,其本身的长度、于这个对齐参数,即 1 倍。

结构体对齐方式

结构体对齐方式摘要:1.结构体对齐方式的概念2.结构体对齐方式的原因3.结构体对齐方式的优缺点4.结构体对齐方式的编程实践正文:结构体对齐方式是计算机程序设计中的一种数据结构布局策略。

在结构体中,各个成员变量按照一定的对齐方式进行排列,以提高数据访问的效率。

在32 位系统下,结构体对齐方式通常为4 字节对齐,而在64 位系统下,则为8 字节对齐。

结构体对齐方式的主要原因是内存访问的局部性原理。

由于计算机内存访问的时间复杂度远高于CPU 处理数据的时间复杂度,因此,通过优化内存访问的方式,可以提高程序的整体性能。

结构体对齐方式就是利用内存访问局部性原理的一种具体实现。

结构体对齐方式的优点主要体现在访问效率的提高上。

由于结构体对齐方式使得成员变量在内存中的位置固定,因此,CPU 在访问结构体成员时,只需要访问一次内存,就可以取得连续的成员数据,这大大提高了访问效率。

然而,结构体对齐方式也有其缺点。

首先,对齐方式可能会导致内存的浪费。

例如,如果一个结构体只有一个字节的空间,但是由于对齐要求,可能需要浪费7 个字节的内存空间。

其次,对齐方式可能会使得结构体的长度不固定,这对于一些需要固定结构体长度的场景来说,可能会有影响。

在编程实践中,我们可以通过预编译指令来控制结构体的对齐方式。

例如,在C 语言中,可以使用#pragma pack 指令来指定结构体的对齐方式。

在C++中,则可以使用alignas 和alignof 关键字来实现对齐方式的控制。

总的来说,结构体对齐方式是一种在内存布局上优化程序性能的方法,虽然它有一些缺点,但是,在大多数情况下,它的优点足以弥补这些缺点。

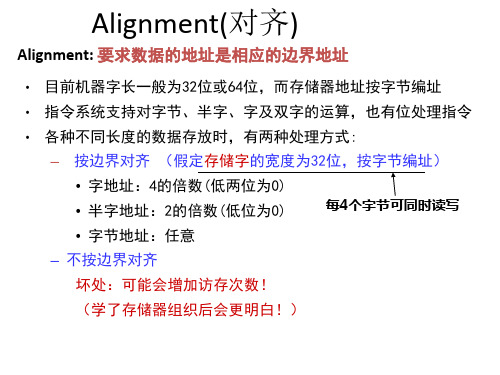

Alignment(对齐)

●为什么要对齐? • 简化了处理器与内存之间传输系统的设计 • 可以提升读取数据的速度,现代存储系统 都采用许多并行的存储芯片来提高读取效 率。

• 比如在32位机上每次读都是从偶地址开始,如果一个 int型存放在偶地址(4的倍数)开始的地方,那么一 个读周期就可以读出。而如果存放在奇地址开始的地 方,就可能会需要2个读周期,并对两次读出的结果 的高低字节进行拼凑才能得到该int数据。显然在读取 效率上下降很多。

0

i

c

4

j

8

S2:

0

i

4

j

c

8

实际上S2占用了 只需要9个字节 12字节

对于“struct S2 d[4]”,只分配9个字节能否满足对齐要求?不能!

S2:

i

j

c

X X X

也需要12个字节

● 结构体模数

结构体模数是#pragma pack指定的数值和 结构体内部最大的基本数据类型成员长度中 数值较小者。结构体的长度应该是该模数的 整数倍。

Alignment(对齐) 举例

例如,考虑下列两个结构声明: struct struct S1 { int i; char c; int j; };

};

在要求对齐的情况下,哪种结构声明更好?

0 4 8

X X X

S2 { int int char

i; j; c;

S2比S1好 需要12个字节

S1:

每4个字节可同时读写

● 什么是对齐? 许多实际的计算机系统对基本类型数据在内存中 存放的位置有限制,它们会要求这些数据的起始 地址的值是某个数k的倍数,这就是所谓的内存对 齐,而这个k则被称为该数据类型的对齐模数 (alignment modulus)。

arm32位的cpu对齐方式

arm32位的cpu对齐方式

ARM 32位CPU的对齐方式是指数据在内存中的存储位置。

对齐

是指数据在内存中的起始地址是否符合一定的规则。

ARM架构中,

数据对齐通常指的是按照数据的大小将数据存储在内存中的起始地址,以提高数据访问的效率和性能。

在ARM 32位架构中,数据对齐通常遵循以下规则:

1. 字节对齐,8位数据的起始地址可以是任意地址;16位数据

的起始地址必须是2的倍数;32位数据的起始地址必须是4的倍数。

2. 半字对齐,16位数据的起始地址必须是2的倍数;32位数

据的起始地址必须是4的倍数。

3. 字对齐,32位数据的起始地址必须是4的倍数。

对齐的好处在于可以提高内存访问的速度,因为处理器可以更

快地访问对齐数据。

如果数据没有按照规定的对齐方式存储,处理

器可能需要多次访问内存,降低了访问效率,甚至可能导致错误或

异常。

总的来说,ARM 32位CPU的对齐方式是按照数据的大小将数据存储在内存中的起始地址,以提高数据访问的效率和性能。

这种对齐方式是为了充分利用处理器的特性,提高数据访问的效率。

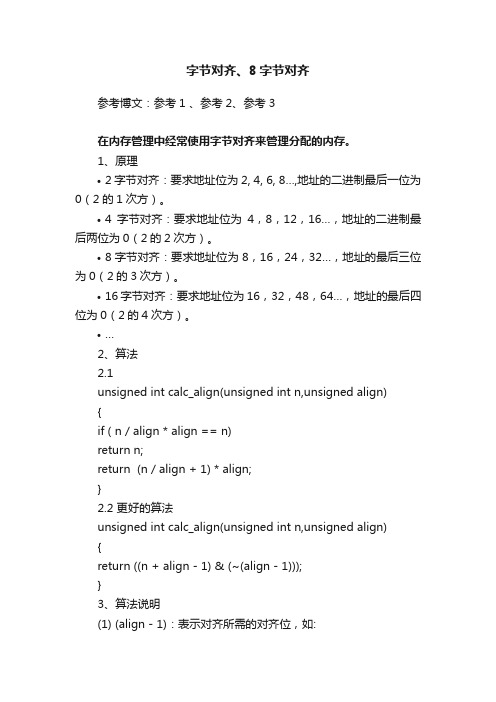

字节对齐、8字节对齐

字节对齐、8字节对齐参考博文:参考1 、参考2、参考3在内存管理中经常使用字节对齐来管理分配的内存。

1、原理•2字节对齐:要求地址位为2, 4, 6, 8…,地址的二进制最后一位为0(2的1次方)。

•4字节对齐:要求地址位为4,8,12,16…,地址的二进制最后两位为0(2的2次方)。

•8字节对齐:要求地址位为8,16,24,32…,地址的最后三位为0(2的3次方)。

•16字节对齐:要求地址位为16,32,48,64…,地址的最后四位为0(2的4次方)。

•…2、算法2.1unsigned int calc_align(unsigned int n,unsigned align){if ( n / align * align == n)return n;return (n / align + 1) * align;}2.2 更好的算法unsigned int calc_align(unsigned int n,unsigned align){return ((n + align - 1) & (~(align - 1)));}3、算法说明(1) (align - 1):表示对齐所需的对齐位,如:•2字节对齐位为1;•4字节对齐位为11;•8字节对齐位111;•16字节对齐位为1111;•…(2) (n + align - 1):表示n补齐对齐所需数据。

(3) &(~(align - 1)):表示去除由于补齐造成的多余数据。

(4) (n + align - 1) & (~(align - 1)):表示对齐后的数据。

对对齐(alignment)的一些认识

对对齐(alignment)的一些认识关于内存地址对齐,尤其是struct中成员的对齐导致的struct的size问题很多人(包括我:()似乎都没有一个比较清晰的认识,所以产生了整理这方面思路和帖子的想法,下面的文字是资料、文档、实验和推测的混合体,有错误是肯定的:)。

能给您提供一点帮助,是我最大的愿望。

(有点麻了)引:struct s {char c;int i;}; 在sizeof(char)=1 sizeof(int)=4的情况下sizeof(struct s)为什么经常是8不是5?这个就是对齐(alignment)的缘故。

那么什么是对齐?现代计算机中内存空间都是按照byte划分的,从理论上讲似乎对任何类型的变量的访问可以从任何地址开始,但实际情况是在访问特定变量的时候经常在特定的内存地址访问,这就是对齐。

为什么呢?msdn for vc6中有这么一段:This principle is especially important when you write code for porting to multiple processors. A misaligned 4-byte data member, which is on an address that is not a multiple of four, causes a performance penalty with an 80386 processor and a hardware exception with a MIPS® RISC processor. In the latter case, although the system handles the exception, the performance penalty is significantly greater.大意是:1.某些硬件平台只能在某些地址处取某些特定类型的数据,否则抛出硬件异常。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目的:

1. 提高内存访问效率。

由于CPU在读取内存时,一次性会以固定长度(如4个字节、8个

字节等)读取数据,而不是一个一个的字节读取。

如果将多个变量连续分配在内存中而不

进行对齐处理的话,就会造成CPU在读取数据时出现“半包”情况。

此时CPU必须要做2

次内存访问才能得到所有的数据,显然效率低了很多。

2. 减少内存占用量。

当使用对齐方式来分布各个变量时,有些余留出来的空间是浪费的。

但是通过使用对其方式来分布各个变量也能避免上文中所说的“半包”情况出现从而大大

减少 CPU 读取数据所浪费的时间和功耗

原理:

1. 对齐原理是将物理地址向上舍入到最近的能被对齐因子(Alignment Factor) 整除的

倍数,例如 4 字(32bit) 要 4 字(32bit) 对齐, 8 字 (64bit) 要 8 字 (64bit) 对齐;

2. 由于 CPU 大部分都是 32 bit 或 64 bit 系统,因此通常要 4 byte 或 8 byte 相应

地对齐;

3. 有些 CPU 要求 16 byte 的对齐,例如 Intel Pentium Pro/II/III/IV ,AMD K6-2/K7 Athlon ;

4. 有些 CPU 要 32 byte 的对齐 ,例如 AMD Opteron / Athlon 64 .。