PIC单片机的BCD码加法程序

bcd码 标准

bcd码标准

BCD码,也称二-十进制编码,是一种数字编码方式,用4位二进制码的组合代表十进制数的0,1,2,3,4,5,6,7,8,9十个数符。

最常用的BCD码称为8421BCD 码,8、4、2、1分别是4位二进数的位取值。

BCD码的转换方式如下:

BCD码与十进制数的转换:若将BCD码1000 0101.0101转换为十进制数如:(1000 0101.0101)BCD=85.5。

BCD码的加法运算:以8421BCD码为例,若要计算38+49,首先将38和49分别转换为二进制码(0010 0100 1000)和(0010 0100 1001),然后进行加法运算,(0010 0100 1000) + (0010 0100 1001) = (0100 1001 0001),这就是38+49的8421BCD码结果。

另外,BCD码也广泛应用于计算机科学、通信工程、电子工程等领域。

在计算机科学中,BCD码被用于表示和存储十进制数,以提高数据的可读性和精度。

在通信工程中,BCD码被用于数据的传输和编码,以确保数据的准确性和可靠性。

在电子工程中,BCD 码被用于数字电路的设计和实现,以提高电路的可靠性和稳定性。

4位BCD码加法

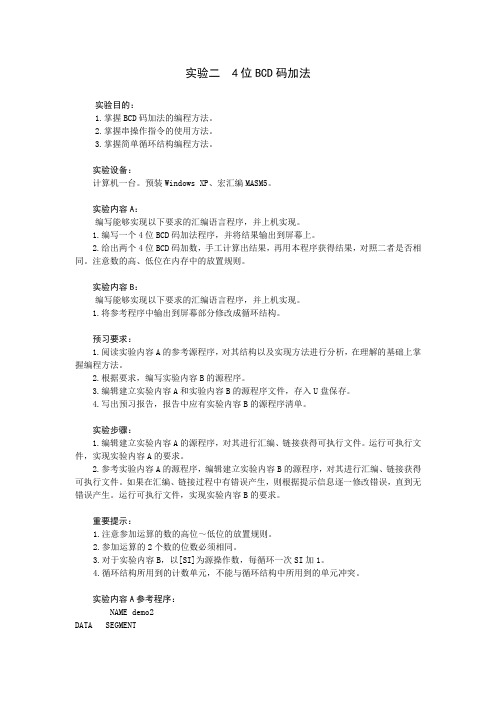

实验二 4位BCD码加法实验目的:1.掌握BCD码加法的编程方法。

2.掌握串操作指令的使用方法。

3.掌握简单循环结构编程方法。

实验设备:计算机一台。

预装Windows XP、宏汇编MASM5。

实验内容A:编写能够实现以下要求的汇编语言程序,并上机实现。

1.编写一个4位BCD码加法程序,并将结果输出到屏幕上。

2.给出两个4位BCD码加数,手工计算出结果,再用本程序获得结果,对照二者是否相同。

注意数的高、低位在内存中的放置规则。

实验内容B:编写能够实现以下要求的汇编语言程序,并上机实现。

1.将参考程序中输出到屏幕部分修改成循环结构。

预习要求:1.阅读实验内容A的参考源程序,对其结构以及实现方法进行分析,在理解的基础上掌握编程方法。

2.根据要求,编写实验内容B的源程序。

3.编辑建立实验内容A和实验内容B的源程序文件,存入U盘保存。

4.写出预习报告,报告中应有实验内容B的源程序清单。

实验步骤:1.编辑建立实验内容A的源程序,对其进行汇编、链接获得可执行文件。

运行可执行文件,实现实验内容A的要求。

2.参考实验内容A的源程序,编辑建立实验内容B的源程序,对其进行汇编、链接获得可执行文件。

如果在汇编、链接过程中有错误产生,则根据提示信息逐一修改错误,直到无错误产生。

运行可执行文件,实现实验内容B的要求。

重要提示:1.注意参加运算的数的高位~低位的放置规则。

2.参加运算的2个数的位数必须相同。

3.对于实验内容B,以[SI]为源操作数,每循环一次SI加1。

4.循环结构所用到的计数单元,不能与循环结构中所用到的单元冲突。

实验内容A参考程序:NAME demo2DATA SEGMENTSTRI1 DB 1,7,5,2 ;第1个加数,注意低位在前STRI2 DB 3,8,1,4 ;第2个加数,注意应与第1个加数位数相同COUNT EQU $-STRI2 ;加数的位数DATA ENDSSTACK SEGMENT PARA STACK 'STACK'DB 100 DUP(?)STACK ENDSCODE SEGMENTASSUME CS:CODE,SS:STACK,DS:DATA,ES:DATASTART PROC FARPUSH DSMOV AX,0PUSH AXGO: MOV AX,DATAMOV DS,AX ;设置源串段基址MOV ES,AX ;设置目的串段基址MOV SI,OFFSET STRI1 ;设置源串首地址MOV DI,OFFSET STRI2 ;设置目的串首地址MOV CX,COUNT ;设置串长度;CLC ;为多字节加法预清进位标志CYCLE: MOV AL,[SI]ADC AL,[DI]AAAMOV [DI],ALINC SIINC DILOOP CYCLEMOV SI,OFFSET STRI2MOV DL,[SI+3] ;输出千位ADD DL,30HMOV AH,2INT 21HMOV DL,[SI+2] ;输出百位ADD DL,30HMOV AH,2INT 21HMOV DL,[SI+1] ;输出十位ADD DL,30HMOV AH,2INT 21HMOV DL,[SI+0] ;输出个位ADD DL,30HMOV AH,2INT 21HRETSTART ENDPCODE ENDSEND START实验B参考程序DATA SEGMENTSTRI1 DB 1,7,5,2 ;第1个加数,注意低位在前STRI2 DB 3,8,1,4 ;第2个加数,注意应与第1个加数位数相同COUNT EQU $-STRI2 ;加数的位数DATA ENDSSTACK SEGMENT PARA STACK 'STACK'DB 100 DUP(?)STACK ENDSCODE SEGMENTASSUME CS:CODE,SS:STACK,DS:DATA,ES:DATASTART PROC FARPUSH DSMOV AX,0PUSH AXGO: MOV AX,DATAMOV DS,AX ;设置源串段基址MOV ES,AX ;设置目的串段基址MOV SI,OFFSET STRI1 ;设置源串首地址MOV DI,OFFSET STRI2 ;设置目的串首地址MOV CX,COUNT ;设置串长度;CLC ;为多字节加法预清进位标志CYCLE: MOV AL,[SI]ADC AL,[DI]AAAMOV [DI],ALINC SIINC DILOOP CYCLEMOV SI,OFFSET STRI2mov bx,4lp1: MOV DL,[SI+3] ADD DL,30HMOV AH,2INT 21Hdec SIdec bxjnz lp1RETSTART ENDPCODE ENDSEND START。

2421bcd码加法和的电路设计

2421bcd码加法和的电路设计

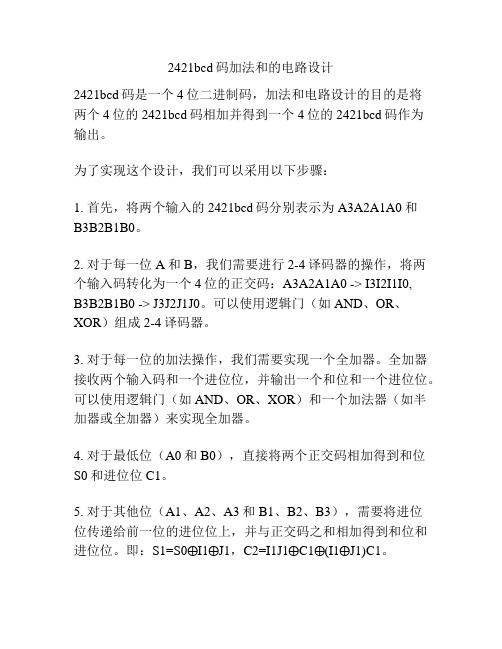

2421bcd码是一个4位二进制码,加法和电路设计的目的是将

两个4位的2421bcd码相加并得到一个4位的2421bcd码作为

输出。

为了实现这个设计,我们可以采用以下步骤:

1. 首先,将两个输入的2421bcd码分别表示为A3A2A1A0和

B3B2B1B0。

2. 对于每一位A和B,我们需要进行2-4译码器的操作,将两个输入码转化为一个4位的正交码:A3A2A1A0 -> I3I2I1I0,

B3B2B1B0 -> J3J2J1J0。

可以使用逻辑门(如AND、OR、XOR)组成2-4译码器。

3. 对于每一位的加法操作,我们需要实现一个全加器。

全加器接收两个输入码和一个进位位,并输出一个和位和一个进位位。

可以使用逻辑门(如AND、OR、XOR)和一个加法器(如半加器或全加器)来实现全加器。

4. 对于最低位(A0和B0),直接将两个正交码相加得到和位

S0和进位位C1。

5. 对于其他位(A1、A2、A3和B1、B2、B3),需要将进位

位传递给前一位的进位位上,并与正交码之和相加得到和位和进位位。

即:S1=S0⨁I1⨁J1,C2=I1J1⨁C1⨁(I1⨁J1)C1。

6. 最后,将和位连接起来得到4位的2421bcd码输出。

总结,通过逻辑门和全加器的组合,可以实现2421bcd码加法和的电路设计。

BCD码指令

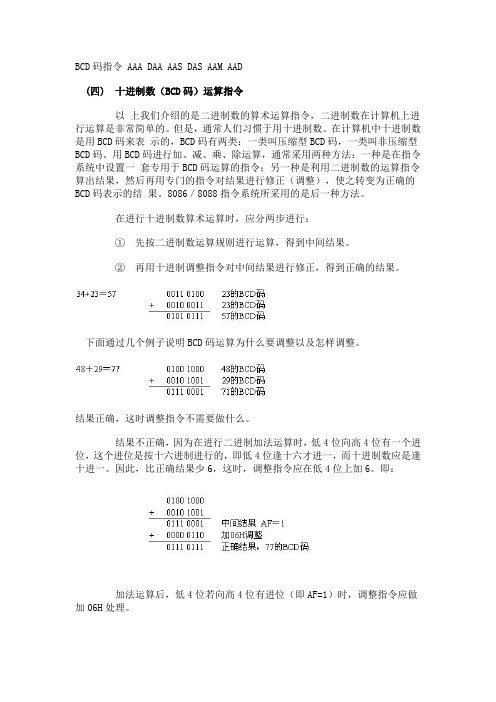

BCD码指令 AAA DAA AAS DAS AAM AAD(四) 十进制数(BCD码)运算指令以上我们介绍的是二进制数的算术运算指令,二进制数在计算机上进行运算是非常简单的。

但是,通常人们习惯于用十进制数。

在计算机中十进制数是用BCD码来表示的,BCD码有两类:一类叫压缩型BCD码,一类叫非压缩型BCD 码。

用BCD码进行加、减、乘、除运算,通常采用两种方法:一种是在指令系统中设置一套专用于BCD码运算的指令;另一种是利用二进制数的运算指令算出结果,然后再用专门的指令对结果进行修正(调整),使之转变为正确的BCD码表示的结果。

8086/8088指令系统所采用的是后一种方法。

在进行十进制数算术运算时,应分两步进行:①先按二进制数运算规则进行运算,得到中间结果。

②再用十进制调整指令对中间结果进行修正,得到正确的结果。

下面通过几个例子说明BCD码运算为什么要调整以及怎样调整。

结果正确,这时调整指令不需要做什么。

结果不正确,因为在进行二进制加法运算时,低4位向高4位有一个进位,这个进位是按十六进制进行的,即低4位逢十六才进一,而十进制数应是逢十进一。

因此,比正确结果少6,这时,调整指令应在低4位上加6。

即:加法运算后,低4位若向高4位有进位(即AF=1)时,调整指令应做加06H 处理。

加法运算后,低4位>9时,调整指令需做加06H处理;高4位>9时,调整指令需做加60H处理。

加法运算后,当CF=1(有进位产生)时,调整指令应做加60H处理。

前面我们已经详细地介绍了二进制数的算术运算指令,下面主要介绍十进制数(BCD码)的调整指令。

⒈十进制加法的调整指令根据BCD码的种类,对BCD码加法进行十进制调整的指令有两条AAA和DAA。

⑴非压缩型BCD码加法调整指令AAA (ASCII Adjust for Addition)指令格式:AAAAAA也称为加法的ASCII调整指令。

指令后面不写操作数,但实际上隐含累加器操作数AL和AH。

(完整版)BCD码指令

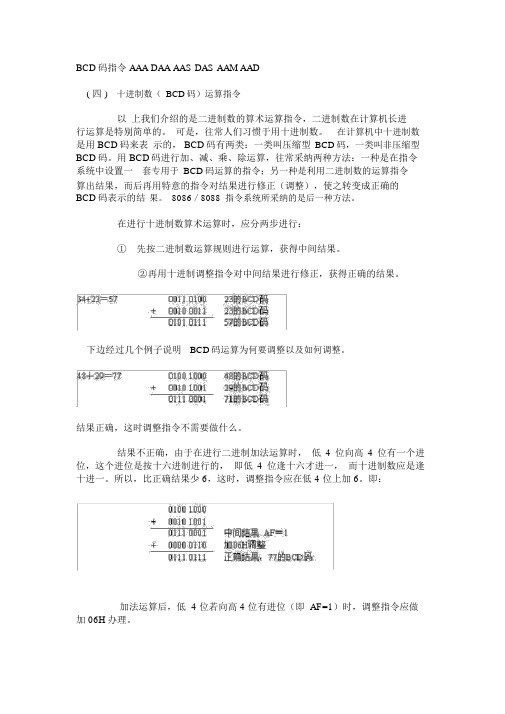

BCD码指令 AAA DAA AAS DAS AAM AAD( 四 )十进制数(BCD码)运算指令以上我们介绍的是二进制数的算术运算指令,二进制数在计算机长进行运算是特别简单的。

可是,往常人们习惯于用十进制数。

在计算机中十进制数是用 BCD码来表示的, BCD码有两类:一类叫压缩型BCD码,一类叫非压缩型BCD码。

用 BCD码进行加、减、乘、除运算,往常采纳两种方法:一种是在指令系统中设置一套专用于BCD码运算的指令;另一种是利用二进制数的运算指令算出结果,而后再用特意的指令对结果进行修正(调整),使之转变成正确的BCD码表示的结果。

8086/8088指令系统所采纳的是后一种方法。

在进行十进制数算术运算时,应分两步进行:①先按二进制数运算规则进行运算,获得中间结果。

②再用十进制调整指令对中间结果进行修正,获得正确的结果。

下边经过几个例子说明BCD码运算为何要调整以及如何调整。

结果正确,这时调整指令不需要做什么。

结果不正确,由于在进行二进制加法运算时,低4 位向高4 位有一个进位,这个进位是按十六进制进行的,即低4 位逢十六才进一,而十进制数应是逢十进一。

所以,比正确结果少 6,这时,调整指令应在低 4 位上加 6。

即:加法运算后,低 4 位若向高 4 位有进位(即 AF=1)时,调整指令应做加 06H办理。

加法运算后,低4位 >9时,调整指令需做加 06H 办理;高4位 >9时,调整指令需做加 60H办理。

加法运算后,当CF=1(有进位产生)时,调整指令应做加60H办理。

前方我们已经详尽地介绍了二进制数的算术运算指令,下边主要介绍十进制数( BCD码)的调整指令。

⒈十进制加法的调整指令依据 BCD码的种类,对 BCD码加法进行十进制调整的指令有两条AAA 和 DAA。

⑴非压缩型 BCD码加法调整指令AAA (ASCII Adjust for Addition)指令格式:AAAAAA也称为加法的 ASCII 调整指令。

一位十进制BCD码加法器设计

一位十进制BCD码加法器设计计科1001班2010310200523初昌禹2012年3月30日实验目的:熟悉基于EDA平台的电路设计,掌握MAXPLUS的使用,并运用MAXPLUS设计电路图,模拟其工作环境实验原理:MAXPLUS软件能够模拟电路工作的实际情况,给电路设计带来方便实验内容:使用MAXPLUS设计一位十进制BCD码的加法器部件的逻辑原理图:一位全加器FA的逻辑图:实验电路图:图三:波形图:实验步骤:分析一位BCD码进行加分运算的情况,进位或者不进位分成两种情况,而进位又分为两种情况:1)若不进位,则结果直接相加即若仅为信号为0,则不进行其他操作2)若进位,则要进行分析,BCD码只能表示0~9之间的数字,若超过9则要进行进位,而当BCD码之和超过15(16~18)超过四位二进制的表示范围,也要进行进位考虑○1当和的范围是10~15时:画卡洛图得到的表达式是F=S3S Z¬S0+S1S0,依据表达式得到电路图添加到上图中,表达式的逻辑图如图三,当二者和超过10时,例如当和为12时,二进制表示:1100,对其加6修正,修正后结果是1(溢出)0010②当和的范围超过了16时,超过四位二进制的表示范围,这需要对结果进行修正,例如:二者和超过17时,二进制结果是1(溢出)0001,对结果进行修正,这结果是1(溢出)0111,若对结果修正,也要对结果加0110实验的测试数据及测试结果:实验小结:用BCD码表示的十进制加法要对其进行详细分析:①当二者和小于等于9时,无需进位,不用进行其他的任何处理,直接进行加法运算;②当和大于等于10小于等于15时,要对其进行加6修正(+0110)③当合大于等于16时,超过了四位二进制的表时范围对于其结果也要进行加6修正,由于②、③的情况不能同时发生,因此二者的信号不能合并实验中遇到的问题及解决方法:①判断冗余位:1010、1011、1100、1101、1110、1111是冗余位,用卡洛图,判断,卡洛图得到了表达式:F=S3S Z¬S0+S1S0②当和大于等于16时超出四位二进制表示范围,不可能存在冗余位,从而当和大于16时要进行另外的处理实验过程中对波形图文件的编辑还不够熟练,很难正确的画出满足仿真所需要的波形心得体会:通过这此的实验设计大致明白了如何用MAXPLUS,绘制电路图,但是对于电路的仿真多少还是有一些问题,可能是软件的兼容问题,或许下次可以使用其他的仿真软件,同时我也了解了如何去设计加法器,同时对于BCD码也有了进一步的了解。

BCD 码和DA调整指令

• • • • •

•

•

当A=# 9AH的时候的情况是不会存在的,严格的说是 没有意义的! 而且DA A指令只用于十进制BCD码加法指令以后,否则 是没有实际意义的! 计算机中只有2进制,不存在16进制或是10进制。 BCD码的规则是用4位2进制数的低10位数(0000~1001)来 一一对应0~9,大于1001的值不使用。 按照这个规则, 0000'1000B + 000'00011B == 08D + 03D == 11D == 0001'00 01B。 而实际上在二进制运算中, 0000'1000B + 0000'0011B == 0000'1011B ,其大小超过了 1001 DA指令的作用就是在用ADD指令(或ADDC)得 到 0000'1011B 后,将其转换为0001'0001,以符合BCD码 的规则。

3、BCD码的加减运算

• 由于编码是将每个十进制数用一组4位二进制 数来表示,因此,若将这种BCD码直接交计算 机去运算,由于 • 计算机总是把数当作二进制数来运算,所以结 果可能会出错。例:用BCD码求38+49。 • 解决的办法是对二进制加法运算的结果采用" 加6修正,这种修正称为BCD调整。即将二进制 加法运算的结果修正为BCD码加法运算的结果, 两个两位BCD数相加时,对二进制加法运算结果 采用修正规则进行修正。修正规则:

• 于是就出现了DA调整指令! • 现在12H+39H,将12H放于A中,执 行 ADD A,#39H指令,则结果为4BH, 这不是我们希望的51H的数据形式!! 这时执行DA A 指令后,就会将A中的 数据调整为51H(具体调整过程和原理 你可以详细看书,如果单片机书中讲 的不详细,那么微机原理中一定说的 非常详细),而我们按照BCD码规则 就将其看为51D,符合我们的要求! • 也就是说加数和被加数都是BCD码的 形式,最大也只可能是99H,也就是我 们十进制数中的99,只有这样才会D数相加的结果向高一 位无进位,若得到的结果小于或等于9,则该不需 修正;若得到的结果大于9且小于16时,该位进行加6 修正。 • (2)如果任何两个对应位BCD数相加的结果向高一 位有进位时(即结果大于或等于16),该位进行加6修 正. • (3)低位修正结果使高位大于9时,高位进行加6修正。 • 下面通过例题验证上述规则的正确性。

BCD码运算1

1 ;BCD码运算ORG 0000HMOV A,#78HADD A,#69HDA A ;强制加66SJMP $END2 ORG 0000H ;程序的起始地址MOV A,#127;把一个数存放在变量AADD A,#126;加法指令SJMP $;结束END3 ORG 0000HMOV DPTR,#0030HMOV A,#70H;MOVX @DPTR,ASJMP $END4 ORG 0000HMOV R3,#5AJMP ABC;长调用SJMP $;ORG 0EFffHABC:MOV A,R3;子程序RL AMOV R3,A; RET;子程序最后一条指令,叫子程序返回指令END5 ORG 0000HMOV A,#5AA:NOPDEC ACJNE A,#3,AASJMP $END6 ORG 0000HMOV 3FH,#3AA:NOPDJNZ 3FH,AASJMP $END7 ORG 0000HABC:MOV DPTR,#TAB ;前面红字指的是标号,表示指令的第一个单元MOV A,#5a11:MOVC A,@A+DPTRSJMP $TAB:DB 0,1,4,9,16,25 ;平方表END8ORG 0000HMOV DPTR,#ABCMOV A,#0JMP @A+DPTRSJMP $ABC: AJMP PR0AJMP PR1AJMP PR2AJMP PR3Pr0: SJMP $;子程序最后一条指令,叫子程序返回指令Pr1: SJMP $Pr2: SJMP $Pr3: SJMP $END9 A1 EQU 95HORG 0000HMOV A,#A1 ;7401 --->Mcs_51JNZ ABC ;7002SJMP $ABC: AJMP PR0AJMP PR1AJMP PR2AJMP PR3Pr0: SJMP $;子程序最后一条指令,叫子程序返回指令Pr1: SJMP $Pr2: SJMP $Pr3: SJMP $DB 95H,96H,97HEND10 ORG 0000HMOV R3,#5LCALL ABC;长调用SJMP $ABC:MOV A,R3;子程序RL AMOV R3,ARET;子程序最后一条指令,叫子程序返回指令END11 ORG 0000HABC:MOV DPTR,#TAB ;前面红字指的是标号,表示指令的第一个单元MOV A,#5ADD A,#2a11:MOVC A,@A+PCSJMP $ ;PC是程序指针PUSH ACCTAB:DB 90,91,94,93,96,95 ;成绩表END12 PUBLIC _delay0DE SEGMENT CODERSEG DE_delay0:delay2:MOV R6,#250delay1:NOPNOPDJNZ R6,delay1DJNZ R7,delay2RETEND13 //4_10 用P1.0产生周期为4ms的方波, //同时用P1.1产生周期为8ms的方波#include<reg51.h>sbit P1_0=P1^0;//定义针脚sbit P1_1=P1^1;//void delay0(char);//声明延时函数(在汇编语言)void main(){while(1){P1_0=0;delay0(2);//4是由R7传递的P1_0=1;delay0(2);P1_1=~P1_1;}}14 //4_10 用P1.0产生周期为4ms的方波, //同时用P1.1产生周期为8ms的方波#include<reg51.h>//sbit P1_0=P1^0;//定义针脚//sbit P1_1=P1^1;//void delay0(char);//声明延时函数(在汇编语言)void main(){ char a=0; //定义的P1.1的时间周期while(1){P2=0xff;delay0(2);//4是由R7传递的#pragma asmCPL P1.0#pragma endasma++;{a=0; //#pragma asmCPL P1.1#pragma endasm}}}15 #include<reg51.h> //特殊寄存器文件#include<absacc.h>#include<math.h>void main(void){char code tab[6]={0,1,4,9,16,25};char *p1,*p2; //@R0,@R1p1=0x30;p2=0x40;*p1=*p2;#pragma asmmov p3,#99H#pragma endasmDWORD[0x20]=sin(*p1);*p2=exp(2);while(1);//等价于sjmp $}16 ;显示所有的数字ORG 0000HMOV DPTR,#D_7SEG_TABMOV A,#9MOVC A,@A+DPTR ;查表SJMP $D_7SEG_TAB:DB 0C0H,0F9H,0A4H,0B0H,99H,92H,82HDB 0F8H,80H,90H,88H,83H,0c6H,0A1H,86H,8EH ;数码管表END17 //显示所有的数字#include<reg51.h>char code s7tab[]={0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8,0x80,0x90,0x88,0x83,0xc6,0xA1,0x86,0x8E}; sbit POW_0=P2^0;sbit POW_1=P2^1;void delay1(char);//延时函数,延时250msvoid main(){do{POW_0=1; //供电线POW_1=0;P1=s7tab[6];delay1(1);POW_0=0; //供电线POW_1=1;P1=s7tab[7];delay1(1);}while(1);}18 ;8个数码管,P0送出字形码,P2送出电源ORG 0000HMOV R2,#0;显示的数字MOV R3,#0FEH ;电源控制11111110-->11111101MOV DPTR,#D_7SEG_TABAA:MOV A,R2MOVC A,@A+DPTR ;查表字形码MOV P2,R3ACALL delay1INC R2MOV A,R3RL AMOV R3,ACJNE R2,#08,AAMOV R2,#0SJMP AAD_7SEG_TAB:DB 0C0H,0F9H,0A4H,0B0H,99H,92H,82HDB 0F8H,80H,90H,88H,83H,0c6H,0A1H,86H,8EH ;数码管表delay1:MOV R6,#25DELAY3:MOV R5,#25DELAY2:NOPNOPDJNZ R5,DELAY2DJNZ R6,DELAY3RETENDPUBLIC _delay1DE SEGMENT CODERSEG DE_delay1:MOV R6,#250DELAY3:MOV R5,#250DELAY2:NOPNOPDJNZ R5,DELAY2DJNZ R6,DELAY3DJNZ R7,_delay1RETEND19 #include<reg51.h>char code s7tab[]={0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8, 0x80,0x90,0x88,0x83,0xc6,0xA1,0x86,0x8E};char code key_tab[]={0xEE,0xde,0xbe,0x7e,0xed,0xdd,0xbd,0x7d, 0xeb,0xdb,0xbb,0x7b,0xe7,0xd7,0xb7,0x77};void main(){char i,j;do{P2=0x0F;//行值i=P2;P2=0xF0;//列值i=i+P2;//获取键值(行加列)for(j=0;j<16;j++){if(i==key_tab[j]){i=j;break;}//查找按键的序号}if((i<16)&&(i>=0))P1=s7tab[i];else P1=0xFF;}while(1);}20 ;数码管ORG 0000HMOV P1,#8EHSJMP $END21 ORG 0000HLA:mov a,#01HLB: mov P1,ARL ANOPcjne a,#10,LBsjmp laendPUBLIC _delay0DE SEGMENT CODERSEG DE_delay0:delay2:MOV R6,#250delay1:NOPNOPDJNZ R6,delay1DJNZ R7,delay2RETEND22 #include<reg51.h> void delay0(char);void timer0_1(void);void main(){char i, a;TMOD=0x01; //00000001 do{a=0xfe;//11111110for(i=0;i<8;i++){ P1=a;delay0(200);a=a<<1|1;}while(1);}timer0_1(){char j;for(j=0;j<20;j++){TH0=0x3c;TL0=0xb0;TR0=1while(TF0==0);TF0=0;}}[文档可能无法思考全面,请浏览后下载,另外祝您生活愉快,工作顺利,万事如意!]。

BCD加法器程序

8421BCD 码加法器一、实验目的1、学习基于VHDL 语言设计组合逻辑。

2、学习VHDL 语言的编程规范,初步养成良好的编程习惯。

二、实验平台微机一台(Windows XP 系统、安装Quartus Ⅱ等相关软件)、CPLD学习板一块、5V 电源线一个、下载线一条。

三.思路分析:8421BCD 码加法器与一般二进制加法器的运算规则一样,不同的是,需要对相加以后的结果进行变换,保证相加之后的结果仍然为8421BCD 码。

实现可以分两步完成:首先将两个BCD 码按照二进制相加,然后将得到的二进制数转换为8421BCD 码。

上述过程可以用VHDL 设计实现。

四。

程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity fulladd isport(a,b:in std_logic_vector(3 downto 0);g:out std_logic_vector(3 downto 0);s:out std_logic);end fulladd;architecture add of fulladd issignal sint,sint1:std_logic_vector(4 downto 0); signal aa,bb:std_logic_vector(4 downto 0);beginprocess(a,b)beginaa<='0'&a(3 downto 0);bb<='0'&b(3 downto 0);sint<=aa+bb;if sint<="01001"theng(3 downto 0)<=sint(3 downto 0);s<='0';elseif sint<="10010"thensint1<=sint+"00110";g(3 downto 0)<=sint1(3 downto 0);s<='1';elseg(3 downto 0)<="1111";s<='1';end if;end if;end process;end add; 五.实验结果:仿真结果:。

BCD数调整指令

2、BCD数减法调整:放于减法指令后 DAS 压缩型BCD数减法调整指令 AAS 非压缩型BCD数减法调整指令 操作数隐含为al寄存器。 例:mov al,37h sub al,19h ;al=1eh,af=1,cf=0 das 指令执行后(al)=18h af=1 调整规则:若AL的低4位大于9或AF=1,则AL的 低4位减6调整,且AF=1; • 若AL的高4位大于9或CF=1,则AL减60H调整,且 CF=1. • 其他情况不调整。

• 如:7+9=16 • mov al,’7’ ;al=37h • add al,’9’ ;al=70h,af=1,cf=0 • aaa ;al=06h,cf=af=1 • 调整规则:如果AL中的低4位小于9且AF=0, 则不调整; • 否则加6调整,且让AF=1,AL的高4位清0.

• • • • • • • • •

4、非压缩型BCD数除法调整指令

• 格式:AAD • 功能:放于除法指令前,把BCD码表示的被除数转 为与真值对应的机器数。 • 调整规则:AH×10+AL--AL • 0---AH • 例:15÷3=5 • MOV AH,1 • MOV AL,5 • MOV BL,3 • AAD ;AL=0FH • DIV BL ;AL=05H,AH=0H

?daa压缩型bcd数加法调整指令?aaa非压缩型bcd数加法调整指令?操作数隐含为al寄存器放于加法指令后

BCD数调整指令

1、BCD数加法调整指令:

• • • • • • • • • DAA 压缩型BCD数加法调整指令 AAA 非压缩型BCD数加法调整指令 操作数隐含为AL寄存器,放于加法指令后。 例如:mov al,39h mov bl,17h add al,bl ;al=50h,af=1,cf=0 daa 指令执行后:(al)=56h af=1 调整规则:若AL的低4位大于9或AF=1,则AL的低 4位加6调整,且AF=1; • 若AL的高4位大于9或CF=1,则AL加60H调整,且 CF=1. • 其他情况不调整。