差分运放误差分析

差分运放误差分析

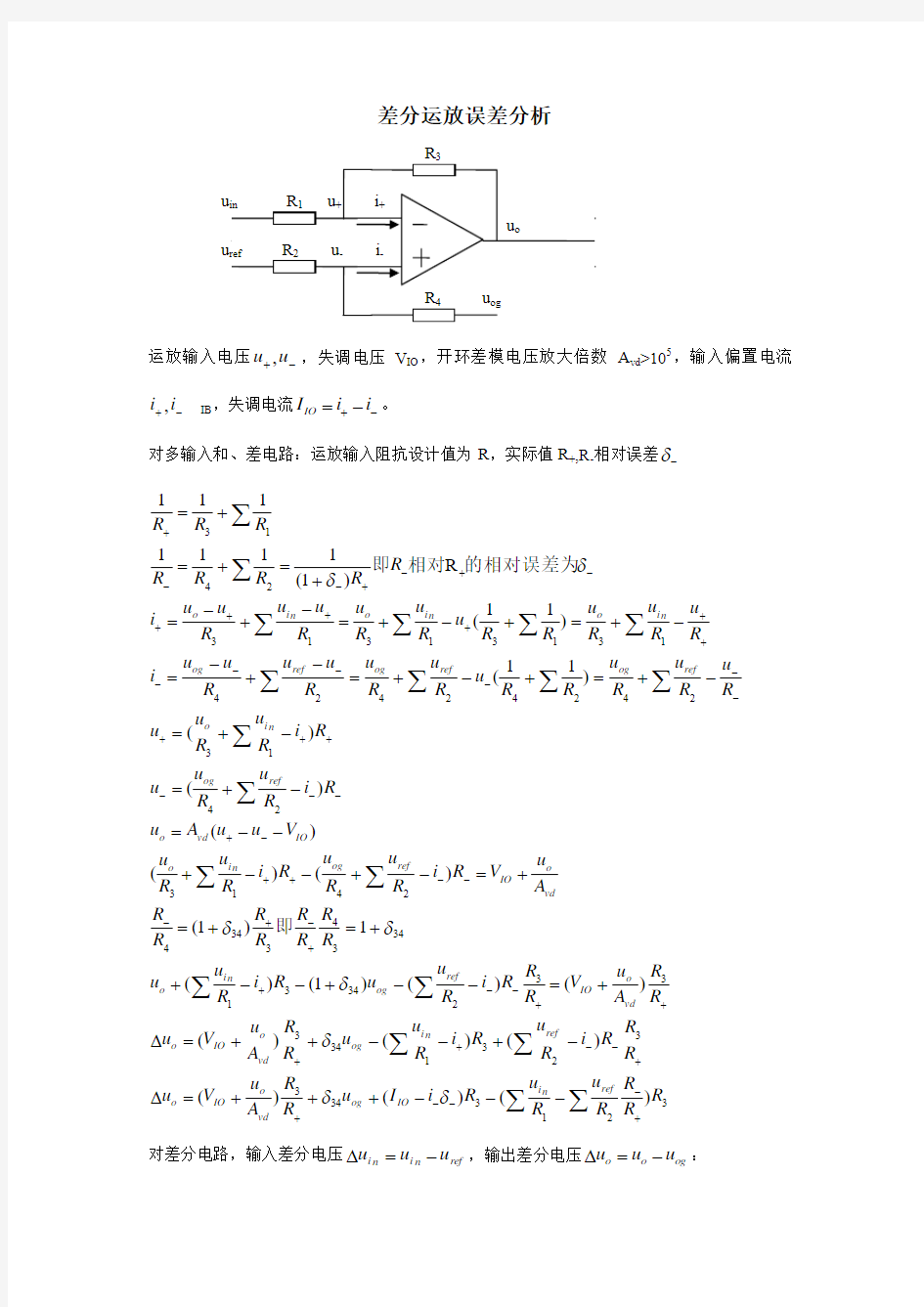

运放输入电压-+u u ,,失调电压V IO ,开环差模电压放大倍数 A vd >105,输入偏置电流

-+i i ,

对多输入和、差电路:运放输入阻抗设计值为R ,实际值R +,R -相对误差-δ

3

213343

323134333234313434334424132

4

1324242

4

2

4

131********

3)()()()()()()()()1()(1)1()()()

()(

)()11(

)11(R )1(1111111R R R R u R u R i I u R R A u V u R R

R i R u R i R u u R R A u V u R R

A u V R R R i R u u R i R u u R R

R R R R R R A u V R i R u R u R i R u R u V u u A u R i R u R u u R i R u R u u R u

R u R u R R u R u R u R u u R u u i R u

R u R u R R u R u R u R u u R u u i R R R R R R R R ref n i IO og vd o IO o ref n i og vd o IO o vd o IO ref og n i o vd o IO ref og n i o IO vd o ref og n i o

ref og ref og ref og n i o n i o n i o +

---++

--+++

+--++-+---++-+-

--+++-

---

-

-++

++++-+-+--+∑∑∑∑∑∑

∑∑∑∑∑∑∑∑∑∑∑∑∑∑---+++=?-+--++

=?+=--+--++=+=+=-+--+--=-+=-+=-+=+-+=-+-=

-+=+-+=-+-=+=+=+=δδδδδδδδ即的相对误差为相对即

对差分电路,输入差分电压ref n i n i u u u -=?,输出差分电压og o o u u u -=?:

ref IB IO og vd o IO ref IO og vd o IO n i o ref n i IO og vd o IO o ref n i IO og vd o IO o u K R I I u R R A u V u K R i I u R R A u V u K u u u K R i I u R R A u V u R R

R R K R R R R R R K R R R R u R u R i I u R R A u V u 21133343

21133343

1321133343

21

211321231

3

133

213343

)()()()()()()(1)1()()()(δδδεδδδεε

δδδδδδδ+++++

≤+-+++=+?-=?-?--+++

=?+=+==

---+++=?-+

--+

--+

+-+-+---+即 对普通共地运放,u og =u ref =0,

33

)()(R I I R R A u V IB IO vd o IO -+

+++

≤δε 当电阻精度为δ,则δδδδδδ4,4,22134≤≤≤-

ref IB IO og vd o IO u K R I I u R R A u V δδδε1333

4)2(4)(+++++

≤+

选择R3=R4,R1=R2为相同温度系数的电阻,相同偏大或偏小方向的阻值,且保持温度一致,则δδδδδδ≤≤≤-2134,,

ref IB IO og vd o IO u K R I I u R R A u V δδδε1333

)()(+++++

≤+

ref IO og IO

IO vd

o

IO IB u K R I u R R V V A u I I i 21133343

δδεδδ+++≤≤+

---《《

例:LM224运放,V IO =7mV ,I IO =0.1uA ,I IB =0.3uA ,R1=R2=2040K ,R3=R4=10K, u ref =310V, u og =0V, u o =0V ,R +=R -=9.95K ,K13=0.49%

mV V K uA mV 3.23310*01.0*%49.010*1.0005.1*7=++≤ε

δδδδδδδδδ)(1

)()(1)(1

)()1)(()()()1()()(2

4213

34242143241334331343313134331343∑∑∑

∑∑∑∑∑-+-+-+

+

+--

++

--++-++++=-+-?-++++=-+--++=++-+++++-+?-=?++-+-++

=?i R u R u I R K u V R u R u R u u i R u R u I R K u V R u R u R u R u i I R K u V R u R u R u R u u R R

K u V u K R R R i i u K u u K R R R i i u K u R R K u V u ref og os o os ref n i og

o ref og os o os ref n i og o os o os ref og n i o og o os ref n i o ref n i og o os o

24132424131324

13213

3424213

341

3

4342121

)()1)(()1)((

1

)()(1

)(),1(),1(δδδδδδδδ

δδδ-+-+-+-+++=++-++-+++=-+-?-++++=-+-?=+=+=∑∑∑i i I R

K u V R u R u R u R u i i I R

K u V R u R u R u u i R u R u I R K u V R u R u R u u R R K R R R R os o os ref og n i o os o os ref n i og

o ref og os o os ref n i og

o r

ref IO og vd o IO IO

IB o os og ref o n

i o os og ref o n i o os og ref o

n i og ref og ref o n i o n i u K R I u R R A u V I I i R K u V i R u R u i R u R u K u

V R i R u R u R i R u R u K

u V u u R i R u R u u R i R u R u u R u R u R u R u u R u u i R u R u R u R u u R u u i R R R R R R R R

R R R R R R R R 21133343

2442133124421331244

2

1331244

2

4

213313143432424131324421331)(/)()1(*)()1(*)()1(**)()1(**)()1(**)(

)1(**)()

1(*)1(*)1()1(1)1(1111)1(1111)1(*)11()1(*)11(1δδεδδδδδδδδδδδδδδδδ++++

≤≤+=+-+-+-++=+-+-+-++=-+-+

=+-+=+-

+=-+-=

+-

+=-+-=+=+=+=+=+=+=++=++=+

----+-+-+--++-

-

-

-+

++

++-+∑∑《

运放差分放大电路

差分放大电路 一. 实验目的: 1. 掌握差分放大电路的基本概念; 2. 了解零漂差生的原理与抑制零漂的方法; 3. 掌握差分放大电路的基本测试方法。 二. 实验原理: 1. 由运放构成的高阻抗差分放大电路 图为高输入阻抗差分放大器,应用十分广泛.从仪器测量放大器,到特种测量放大器,几乎都能见到其踪迹。 从图中可以看到A1、A2两个同相运放电路构成输入级,在与差分放大器A3串联组成三运放差分防大电路。电路中有关电阻保持严格对称,具有以下几个优点: (1)A1和A2提高了差模信号与共模信号之比,即提高了信噪比; (2)在保证有关电阻严格对称的条件下,各电阻阻值的误差对该电路的共模抑制比K CMRR 没有影响; (3)电路对共模信号几乎没有放大作用,共模电压增益接近零。 因为电路中R1=R2、 R3=R4、 R5=R6 ,故可导出两级差模总增益为: 3 5P 1p i2i1o vd R R R 2R R u u u A ???? ??+-=-= 通常,第一级增益要尽量高,第二级增益一般为1~2倍,这里第一级选择100倍,第二级为1倍。则取R3=R4=R5=R6=10K Ω,要求匹配性好,一般用金属膜精密电阻,阻值可在10K Ω~几百K Ω间选择。则 A vd =(R P +2R 1)/R P 先定R P ,通常在1K Ω~10K Ω内,这里取R P =1K Ω,则可由上式求得R 1=99R P /2=49.5K Ω 取标称值51K Ω。通常R S1和R S2不要超过R P /2,这里选R S1= R S2=510,用于保护运放输入级。 A1和A2应选用低温飘、高K CMRR 的运放,性能一致性要好。 三. 实验内容 1. 搭接电路 2. 静态调试

差分放大器的结构、特点及作用

1. 差分放大器的结构、特点及作用 特点: 差分信号作为输出可以增大最大输出压摆。 差分工作模式,能很好抑制环境噪声(如电源噪声),即所谓的共模抑制。虽然这是以电路面积为代价的,但对于在单端模式时采用其它的方法来抑制环境噪声的干扰的电路面积而言还是较小的。 差分电路还具有偏置电路简单和线性度高等优点。 结构: 应用: 2. 基本差分对中的尾电流源的作用 为差分对提供一个电流源I S ,以使差分对具有固定的尾电流,从而产生独立于输入共模信号V ic 的电流I D1+I D2。 在共模输入时差分对管的工作电流I D1=I D2= I S /2,并且保持恒定; 同理,其共模输出电平也保持恒定,且其值为V DD -RI S /2(R 为负载等效电阻)。 解决了由于差分对管在共模输入时的工作电流变化引起非线性及输出信号失真等。 V i1 V i2 V i1V i2

3. 各类差分放大器的增益(共模增益、差模增益)、输入输出共模电平范围、 线性增益区的范围(对所给电路图分析计算) 双端输入双端输出时的差模电压增益 双端输入单端输出差模电压增益 在理想情况下,由于电路的完全对称性,则当输入共模信号时,由于引起差分对管的每边的输出电压的变化量相等,双端输出的电压为0,故电压增益为0。 理想情况下,单端输出共模小信号增益也为0。 4. 各类差分放大器的失调分析(失调的表示方式、原因,减小失调的方法) P83 减小由于输入差分对管不对称所引起的输入失调电压a 、减小输入差分对管MOS 管的阈值电压差,一种有效的方法就是采用离子注入工艺,使输入差分对管的阈值电压一致性较好。b 、减小失调误差的另一种方法是减小由于差分对管的几何尺寸的不对称引入的误差,这可以增大差分对管的尺寸,从而减小ΔW/W 与ΔL/L 的值(但这会造成输入差分对管具有大的寄生电容)来实现,并且通过提高光刻精度以减小ΔW/W 与ΔL/L 的误差值。 5. 差分放大器共模抑制能力的表示方式 R g V V V m i o o -=-)2)(121R g m 2 1 -

采用折叠式结构的两级全差分运算放大器的设计

目录 1. 设计指标 (1) 2. 运算放大器主体结构的选择 (1) 3. 共模反馈电路(CMFB)的选择 (1) 4. 运算放大器设计策略 (2) 5. 手工设计过程 (2) 5.1 运算放大器参数的确定 (2) 5.1.1 补偿电容Cc和调零电阻的确定 (2) 5.1.2 确定输入级尾电流I0的大小和M0的宽长比 (3) 5.1.3 确定M1和M2的宽长比 (3) 5.1.4确定M5、M6的宽长比 (3) 5.1.5 确定M7、M8、M9和M10宽长比 (3) 5.1.6 确定M3和M4宽长比 (3) 5.1.7 确定M11、M12、M13和M14的宽长比 (4) 5.1.8 确定偏置电压 (4) 5.2 CMFB参数的确定 (4) 6. HSPICE仿真 (5) 6.1 直流参数仿真 (5) 6.1.1共模输入电压范围(ICMR) (5) 6.1.2 输出电压范围测试 (6) 6.2 交流参数仿真 (6) 6.2.1 开环增益、增益带宽积、相位裕度、增益裕度的仿真 (6) 6.2.2 共模抑制比(CMRR)的仿真 (7) 6.2.3电源抑制比(PSRR)的仿真 (8) 6.2.4输出阻抗仿真 (9) 6.3瞬态参数仿真 (10) 6.3.1 转换速率(SR) (10) 6.3.2 输入正弦信号的仿真 (11) 7. 设计总结 (11) 附录(整体电路的网表文件) (12)

采用折叠式结构的两级全差分运算放大器的设计 1. 设计指标 5000/ 2.5 2.551010/21~22v DD SS L out dias A V V V V V V GB MHz C pF SR V s V V ICMR V P mW μ>==?== >=±=?≤的范围 2. 运算放大器主体结构的选择 图1 折叠式共源共栅两级运算放大器 运算放大器有很多种结构,按照不同的标准有不同的分类。从电路结构来看, 有套筒 式共源共栅、折叠式共源共栅、增益提高式和一般的两级运算放大器等。本设计采用的是如图1所示的折叠式共源共栅两级运算放大器,采用折叠式结构可以获得很高的共模输入电压范围,与套筒式的结构相比,可以获得更大的输出电压摆幅。 由于折叠式共源共栅放大器输出电压增益没有套筒式结构电压增益那么高,因此为了得到更高的增益,本设计采用了两级运放结构,第一级由M0-M10构成折叠式共源共栅结构,第二级由M11-M14构成共源级结构,既可以提高电压的增益,又可以获得比第一级更高的输出电压摆幅。 为了保证运放在闭环状态下能稳定的工作,本设计通过米勒补偿电容Cc 和调零电阻Rz 对运放进行补偿,提高相位裕量! 另外,本文设计的是全差分运算放大器,与单端输出的运算放大器相比较,可以获得更高的共模抑制比,避免镜像极点及输出电压摆幅。 3. 共模反馈电路(CMFB )的选择 由于采用的是高增益的全差分结构,输出共模电平对器件的特性和失配相当敏感,而且不能通过差动反馈来达到稳定,因此,必须增加共模反馈电路(CMFB )来检测两个输出端

全差分运算放大器设计

全差分运算放大器设计 岳生生(200403020126) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11 1357 113 51 3 57 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=-+ 第二级增益 9 2 2 9112 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- + 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r = = ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

电位差计的原理和使用

实验八 电位差计的原理和使用 【实验目的】 1.掌握电位差计的工作原理和正确使用方法,加深对补偿法测量原理的理解和运用。 2.训练简单测量电路的设计和测量条件的选择。 【实验仪器】 UJ31型直流电位差计、SS1791双路输出直流稳压电源、标准电池、标准电阻、AC15/5灵敏电流计、FJ31型直流分压箱、滑线变阻器、直流电阻箱、待校验电表、待测干电池、待测电阻、开关和导线等。 【实验原理】 如图5.8.1所示,电位差计的工作原理是根据电 压补偿法,先使标准电池E n 与测量电路中的精密电阻R n 的两端电势差U st 相比较,再使被测电势差(或电压)E x 与准确可变的电势差U x 相比较,通过检流计G 两次指零来获得测量结果。电压补偿原理也可从电势差计的“校准”和“测量”两个步骤中理解。 校准:将K 2打向“标准”位置,检流计和校准电路联接,R n 取一预定值,其大小由标准电池E S 的电动势确定;把K 1合上,调节R P ,使检流计G 指零,即E n = IR n ,此时测量电路的工作电流已调好为 I = E n /R n 。校准工作电流的目的:使测量电路中的R x 流过一个已知的标准电流I o ,以保证R x 电阻盘上的电压示值(刻度值)与其(精密电阻R x 上的)实际电压值相一致。 测量:将K 2打向“未知”位置,检流计和被测电路联接,保持I o 不变(即R P 不变),K 1合上,调节R x ,使检流计G 指零,即有E x = U x = I o R x 。 由此可得x n n x R R E E = 。由于箱式电位差计面板上的测量盘是根据R x 电阻值标出其对应的电压刻度值,因此只要读出R x 电阻盘刻度的电压读数,即为被测电动势E x 的测量值。 所以,电位差计使用时,一定要先“校准”,后“测量”,两者不能倒置。 【实验装置】 1. UJ31型电位差计 UJ31型箱式电位差计是一种测量低电势的电位差计,其测量范围为 mV .V 1171-μ(1K 置1?档)或mV V 17110-μ(1K 置10?档)。使用 图5.8.1 电位差计的工作原理 图5.8.2 UJ31型电位差计面板图 + - -++- + -标准 检流计 5.7-6.4V 未知1 未知2 K 1 R P2 R P3 R P1 R n K 2 I II III 1.01×10 ×1 未知1 未知2 标准断断粗 中 细 ×1 ×0.1 ×0.001 粗细短路

差分运放

差分接法:差分放大电路(图3.8a.4)的输入信号是从集成运放的反相和同相输入端引入,如果反馈电阻RF等于输入端电阻R1 ,输出电压为同相输入电压减反相输入电压,这种电路也称作减法电路。 图3.8a.4 差分放大电路 差分放大器 如图所示,通过采用两个输入,该差分放大器产生的输出等于U1和U2之差乘以增益系数

运算放大器的单电源供电方法 梦兰 大部分运算放大器要求双电源(正负电源)供电,只有少部分运算放大器可以在单电源供电状态下工作,如LM358(双运放)、LM324(四运放)、CA3140(单运放)等。需要说明的是,单电源供电的运算放大器不仅可以在单电源条件下工作,也可在双电源供电状态下工作。例如,LM324可以在、+5~+12V单电源供电状态下工作,也可以在+5~±12V双电源供电状态下工作。 在一些交流信号放大电路中,也可以采用电源偏置电路,将静态直流输出电压降为电源电压的一半,采用单电源工作,但输入和输出信号都需要加交流耦合电容,利用单电源供电的反相放大器如图1(a)所示,其运放输出波形如图1(b)所示。 该电路的增益Avf=-RF/R1。R2=R3时,静态直流电压Vo(DC)=1/2Vcc。耦合电容Cl和C2的值由所需的低频响应和电路的输入阻抗(对于C1)或负载(对于C2)来确定。Cl及C2可由下式来确定:C1=1000/2πfoRl(μF);C2=1000/2πfoRL(μF),式中,fo是所要求最低输入频率。若R1、RL单位用kΩ,fO用Hz,则求得的C1、C2单位为μF。一般来说,R2=R3≈2RF。 图2是一种单电源加法运算放大器。该电路输出电压Vo=一RF(V1/Rl十V2/R2十V3/R3),若R1=R2=R3=RF,则Vo=一(V1十V2十V3)。需要说明的是,采用单电源供电是要付出一定代价的。它是个甲类放大器,在无信号输入时,损耗较大。

影响运放电路的误差的几个主要参数(精)

影响运放电路的误差的几个主要参数(KCMR,VIO,Iib,Iio等) 1. 共模抑制比KCMR为有限值的情况 集成运放的共模抑制比为有限值时,以下图为例讨论。 VP=Vi VN=Vo 共模输入电压为: 差摸输入电压为: 运算放大器的总输出电压为:vo=AVDvID+AVCvIC 闭环电压增益为:

可以看出,Avd和Kcmr越大,Avf越接近理想情况下的值,误差越小。 2.输入失调电压VIO 一个理想的运放,当输入电压为0时,输出电压也应为0。但实际上它的差分输入级很难做到完全对称。通常在输入电压为0时,存在一定的输出电压。 解释一:在室温25℃及标准电源电压下,输入电压为0时,为使输出电压为0,在输入端加的补偿电压叫做失调电压。 解释二:输入电压为0时,输出电压Vo折合到输入端的电压的负值,即VIO=- VO|VI=0/AVO 输入失调电压反映了电路的对称程度,其值一般为±1~10mV 3.输入偏置电流IIB BJT集成运放的两个输入端是差分对管的基极,因此两个输入端总需要一定的输入电流IBN和IBP。输入偏置电流是指集成运放输出电压为0时,两个输入端静态电流的平均值。 输入偏置电流的大小,在电路外接电阻确定之后,主要取决于运放差分输入级BJT的性能,当它的β值太小时,将引起偏置电流增加。偏置电流越小,由于信号源内阻变化引起的输出电压变化也越小。其值一般为10nA~1uA。 4.输入失调电流IIO 在BJT集成电路运放中,当输出电压为0时,流入放大器两输入端的静态基极电流之差,即IIO=|IBP-IBN| 由于信号源内阻的存在,IIO会引起一个输入电压,破坏放大器的平衡,使放大器输出电压不为0。它反映了输入级差分对管的不对称度,一般约为 1nA~0.1uA。 5.输入失调电压VIO、输入失调电流IIO不为0时,运算电路的输出端将产生误差电压。 设实际的等效电路如下图大三角符号,小三角符号内为理想运放,根据VIO和IIO的定义画出。

差分运算放大器基本知识

一.差分信号的特点: 图1 差分信号 1.差分信号是一对幅度相同,相位相反的信号。差分信号会以一个共模信号 V ocm 为中心,如图1所示。差分信号包含差模信号和公模信号两个部分, 差模与公模的定义分别为:Vdiff=(V out+-V out- )/2,Vocm=(V out+ +V out- )/2。 2.差分信号的摆幅是单端信号的两倍。如图1,绿色表示的是单端信号的摆 幅,而蓝色表示的是差分信号的摆幅。所以在同样电源电压供电条件下,使用差分信号增大了系统的动态范围。 3.差分信号可以抑制共模噪声,提高系统的信噪比。In a differential system, keeping the transport wires as close as possible to one another makes the noise coupled into the conductors appear as a common-mode voltage. Noise that is common to the power supplies will also appear as a common-mode voltage. Since the differential amplifier rejects common-mode voltages, the system is more immune to external noise. 4.差分信号可以抑制偶次谐波,提高系统的总谐波失真性能。 Differential systems provide increased immunity to external noise, reduced even-order harmonics, and twice the dynamic range when compared to signal-ended system. 二.分析差分放大器电路 图2.差分放大器电路分析图

电位差法测量电动势

电位差计测电动势 电位差计是利用补偿原理和比较法精确测量直流电位差或电源电动势的常用仪器,它准确度高、使用方便,测量结果稳定可靠,还常被用来精确地间接测量电流、电阻和校正各种精密电表。在现代工程技术中电子电位差计还广泛用于各种自动检测和自动控制系统。线式电位差计是一种教学型板式电位差计,通过它的解剖式结构,可以更好地学习和掌握电位差计的基本工作原理和操作方法。 【实验目的】 1. 了解电位差计的结构,正确使用电位差计; 2. 理解电位差计的工作原理--补偿原理; 3. 掌握线式电位差计测量电池电动势的方法; 4. 熟悉指针式检流计的使用方法。 【实验仪器】 ?? 板式电位差计、检流计、滑线变阻器、电阻箱、标准电池、待测电池、稳压电源、单刀开关、单刀(双刀)双掷开关 图1电位差计实物图 【实验原理】 电源的电动势在数值上等于电源内部没有净电流通过时两极件的电压。如果直接用电压表测量电源电动势,其实测量结果是端电压,不是电动势。因为将电压表并联到电源两端,就有电流I 通过电源的内部。由于电源有内阻0r ,在电源内部不可避免地存在电位降0Ir , 因而电压表的指示值只是电源的端电压( 0Ir E U -=)的大小,它小于电动势。显然,为 了能够准确的测量电源的电动势,必须使通过电源的电流I 为零。此时,电源的端电压U 才等于其电动势E 。怎样才能使电源内部没有电流通过而又能测定电源的电动势呢? 1. 补偿原理 ?? 如图2所示,把电动势分别为 s E 、x E 和检流计G 联成闭合回路。当s E

加法器及差分放大器项目实验报告

加法器及差分放大器项目实验报告 一、项目内容和要求 (一)、加法器 1、任务目的: (1)掌握运算放大器线性电路的设计方法; (2)理解运算放大器的工作原理; (3)掌握应用仿真软件对运算放大器进行仿真分析的方法。 2、任务内容: 2.1 设计一个反相加法器电路,技术指标如下: (1)电路指标 运算关系:)25(21i i O U U U +-=。 输入阻抗Ω≥Ω≥K R K R i i 5,521。 (2)设计条件 电源电压Ec=±5V ; 负载阻抗Ω=K R L 1.5 (3)测试项目 A :输入信号V U V U i i 5.0,5.021±=±=,测试4种组合下的输出电压; B :输入信号V KHz U V U i i 1.0,1,5.021为正弦波±=信号,测试两种输入组合情况下的输出电 压波形。 C :输入信号V U i 01=,改变2i U 的幅度,测量该加法器的动态范围。 D :输入信号V U i 01=,V U i 1,2为正弦波,改变正弦波的频率,从1kHz 逐渐增加,步长为 2kHz ,测量该加法器的幅频特性。 2.2 设计一个同相加法器电路,技术指标如下: (1)电路指标 运算关系:21i i O U U U +=。 (2)设计条件 电源电压Ec=±5V ; 负载阻抗Ω=K R L 1.5 (3)测试项目 A :输入信号V U V U i i 1,121±=±=,测试4种组合下的输出电压; B :输入信号V KHz U V U i i 1,1,121为正弦波±=信号,测试两种输入组合情况下的输出电压 波形。 (二)、差分放大器 1、任务目的: (1)掌握运算放大器线性电路的设计方法; (2)理解运算放大器的工作原理; (3)掌握应用仿真软件对运算放大器进行仿真分析的方法。 2、任务内容 2.1 设计一个基本运放差分放大器电路,技术指标如下: (1)电路指标 运算关系:)(521i i O U U U --=。 输入阻抗Ω≥Ω≥K R K R i i 5,521。 (2)设计条件

全差分套筒式运算放大器设计

全差分套筒式运算放大器设计 1、设计内容 本设计基于经典的全差分套筒式结构设计了一个高增益运算放大器,采用镜像电流源作为偏置。为了获得更大的输出摆幅及差模增益,电路采用了共模反馈及二级放大电路。 本设计所用到的器件均采用SMIC 0.18μm的工艺库。 2、设计要求及工艺参数 本设计要实现的各项指标和相关的工艺参数如表1和表2所示:

3、放大器设计 3.1 全差分套筒式放大器拓扑结构与实际电路 图1 全差分套筒式放大器拓扑结构 图2 最终电路图

3.2 设计过程 在图1中,Mb1和M9组成的恒流源为差放提供恒流源偏置,且M1,M2完全一样,即两管子所有参数均相同。Mb2、M7和M8构成了镜像电流源,M5、M6和M7、M8构成了共源共栅电流源,M1、M2、M3、M4构成了共源共栅结构,可以显著提高输出阻抗,提高放大倍数(把M3的输出阻抗提高至原来的(gm3 + gmb3)ro2倍。但同时降低了输出电压摆幅。为了提高摆幅,控制增益,在套筒式差分放大器输出端增加二级放大。 本设计中功率上限为10mW,可以给一级放大电路分配3mA的电流。设计要求摆幅为3V,所以图1中M1、M3、M5、M9的过驱动电压之和不大于1.8-3/2=0.3V。我们可以平均分配每个管子的过驱动电压。根据漏电计算流公式(1)(考虑沟道长度调制效应),可以计算出每个管子的宽长比。 I D=1 2μn C ox W L (V GS?V TH)2(1+λV DS)(1) 其中,C ox等于ε/t ox,μn和t ox可以从工艺库中查找。 4、仿真结果 经过调试优化之后的仿真结果如以下各图所示: 图3 增益及相位裕度 从图中可以看出,本设计的低频增益达到了74.25dB,达到了预期要求。3dB 带宽为35kHz左右,比较小,可见设计还有改进的余地。 当CL为2pF时,相位裕度: PM=180°+∠βH(ω)=180°?125.5°=54.5° 电源电压为1.8V时,输出摆幅如下图所示,达到了3V。

全差分运算放大器设计

全差分运算放大器设计 岳生生(0126) 一、设计指标 以上华CMOS 工艺设计一个全差分运算放大器,设计指标如下: 直流增益:>80dB 单位增益带宽:>50MHz 负载电容:=5pF 相位裕量:>60度 增益裕量:>12dB 差分压摆率:>200V/us 共模电压:(VDD=5V) 差分输入摆幅:>±4V 运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的 ,DSAT N V 之和小于,输出端的所有PMOS 管的 ,DSAT P V 之和也必须小于。对于单 级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 性能指标分析 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 1 1 1 3 5 7 1 1 3 5 1 3 5 7 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=- +P 第二级增益9 2 2 9 11 2 9 9 11 ()m o o o m m o o g g G A R r r g g =-=-=-+P 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r == ≥++ 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR : 1)、输入级: max 1max |2| Cc out DS C C d SR dt I v I C C = = = 单位增益带宽1m u C g C ω= ,可以得到 1m C u g C ω =

电位差计的误差分析

电位差计的误差分析 电位差计是精密测量应用极广的仪器,可以用来精确测定电动势、电压、电流、电阻等电学量,还可以用于校准精密电表和直流电桥等直读式仪表,在非电量(如温度、压力、位移等)的电测法中也占有重要地位。电位差计不仅准确度等级高,而且测量结果稳定可靠。它不从被测对象中取用电流,因此测量时不会使被测对象改变原来的数值。电位差计可直接用来精密测量电池电动势及电位差。 箱式电位差计的工作原理图都采用图1所示的线路,包括三个部分: (1)工作电流调节回路,主要由E、Rn、R1、R、K。等组成; (2)校正工作电流回路:主要由Es、RS、K1、K2等组成; (3)待测回路:主要由EX、RX、G、K1、K2组成。 当电位差计达到平衡(实现补偿)时,有 (1) 电位差计虽是一种测量电池电动势及电位差等的精密仪器,但其本身也有一定的误差存在。 1 元件误差 元件误差是指因元件问题而产生的仪器误差。根据(1)式,可得相对误差公式:

(2) 因是标准电池,故属量具误差。通常处理量具误差的办法是选用准确 度等级足够高的量具,使该项误差成微小误差而可以忽略不计。“足够高”是指标准电池的电动势的相对变化不超过0.1a%。a为电位差计的准确度等级,0.1是由微小误差分配原则确定的。因此量具的准确度等级应比仪器的准确度等级高一个数量级,这样就能使该项误差忽略不计。这样电位差计的元件误差就为: (3) 若这两部分误差的大小和符号都相同,就可以互相抵消。因此在设计、制造电位差计时,和这两组电阻总是尽量选用时间稳定性和温度稳定性以及误差符 号(正或负)都相同的电阻。在使用电位差计时,应合理选择量限而使全部读数盘都用到。这不仅能保证足够多的有效位数,而且可使上述两部分元件误差得到比较充分的抵消。 一般说,元件误差是电位差计各种误差因素中影响最大的一项,约占总误差的一半。只要使用电阻来调节和的比例,这一项误差就总是存在。电阻元件的准确度、电阻的时间稳定性和温度稳定性限制了电位差计的准确度等级。 2温差电动势产生的误差 不同金属相接触(如焊接点、电键、电刷、接线端钮等)时,将产生接触电位差。当各接触点温度不同时,则产生温差电动势,简称热电势。对于精密电位差计,特别在被测量很小时,热电势的影响不容忽视。此外,因测量回路的热电势直接与被测电动势(或电位差)相串接,其影响最大。为了减小这项误差,在设计、制造电位差计时,应尽量选用彼此接触电位差小的金属元件和导线;在测量回路中应尽量减少焊接点、电键、电刷等;采用较小的工作电流,以减小元件的升温等。在使用时应注意,不要靠近冷源或热源(例如在直射阳光下进行测量)。当要求较高时,要采用恒温措施。

运放差分放大电路原理知识介绍

差分放大电路 (1)对共模信号的抑制作用 差分放大电路如图所示。 特点:左右电路完全对称。 原理:温度变化时,两集电极电流增量相等,即C2C1I I ?=?,使集电极电压变化量相等,CQ2CQ1V V ?=?,则输出电压变化量0C2C1O =?-?=?V V V ,电路有效地抑制了零点漂移。若电源电压升高时,仍有0C2C1O =?-?=?V V V ,因此,该电路能有效抑制零漂。 共模信号:大小相等,极性相同的输入信号称为共模信号。 共模输入:输入共模信号的输入方式称为共模输入。 (2)对差模信号的放大作用 基本差分放大电路如图。 差模信号:大小相等,极性相反的信号称为差模信号。 差模输入:输入差模信号的输入方式称为差模输入。 在图中, I 2I 1I 2 1 v v v = -=, 放大器双端输出电压 差分放大电路的电压放大倍数为 可见它的放大倍数与单级放大电路相同。 (3)共模抑制比 共模抑制比CMR K :差模放大倍数d v A 与共模放大倍数c v A 的比值称为共模抑制比。 缺点:第一,要做到电路完全对称是十分困难的。第二,若需要单端输出,输出端的零点漂移仍能存在,因而该电路抑制零漂的优点就荡然无存了。 改进电路如图(b )所示。在两管发射极接入稳流电阻e R 。使其即有高的差模放大 倍数,又保持了对共模信号或零漂强抑制能力的优点。 在实际电路中,一般都采用正负两个电源供电,如图所示(c )所示。 差分放大电路 一. 实验目的: 1. 掌握差分放大电路的基本概念; 2. 了解零漂差生的原理与抑制零漂的方法; 3. 掌握差分放大电路的基本测试方法。 二. 实验原理: 1. 由运放构成的高阻抗差分放大电路 图为高输入阻抗差分放大器,应用十分广泛.从仪器测量放大器,到特种测量放大器,几乎都能见到其踪迹。

差分放大器仿真

《电子技术计算机绘图基础》 设 计 报 告 题目:差分放大器仿真 学院:通信与信息工程学院 专业班级:电子信息工程 学号: 学生姓名: 指导教师:

差分放大器的仿真 一、设计描述 1、设计目的和任务 1).熟悉差分放大器的工程估算,掌握差分放大器静态工作点的调整与测试方法。 2).能够掌握差分放大器性能指标的测试方法。 3).能够掌握multisim 和protel 的基本用法,做出Multisim 仿真图、Protel 原理图、PCB 板,从而加深理解差分放大器的性能特点。 4).熟悉常用电子器件的类别、型号、规格、性能及其使用范围,能查阅有关的电子器件图书。 2、原理分析 (1)基本原理 差分放大器是一种特殊的直接耦合放大器,它能有效的抑制零点漂移;它的基本性能是放大差模信号、抑制共模信号;常用共模抑制比来表征差分放大器对共模信号的抑制能力;稳流电阻的增加可以提高共模抑制比;但稳流电阻不能太大,因此采用恒流源取代稳流电阻,从而进一步的提高共模抑制比。 (2)静态工作点的调整 实验电路通过调节电位器R p 使两个三极管的集电极电压相等来调节电路的对称性,完成电路的调零。 (3)静态工作点的测量 静态工作点的测量就是测出三极管各电极对地直流电压V BQ 、V EQ 、V CQ ,从而计算得到V CEQ 和V BEQ 。而测量直流电流时,通常采用间接测量法测量,即通过直流电压来换算得到直流电流。这样即可以避免更动电路,同时操作也简单。 EQ CQ CEQ V V V -= EQ BQ BEQ V V V -= e EQ EQ R V I = C CQ CC CQ )(R V V I -= (4)电压放大倍数的测量 差分放大器有差模和共模两种工作模式,因此电压放大倍数有差模电压放大倍数和共模电压放大倍数两种。 在差模工作模式下,差模输出端U od1是反相输出端,U od2是同相输出端,则差模电压放大倍数为: ud2 ud1ud A A A += ud2 i od2i od1ud1 A U U U U A -=- == 在共模工作模式下,共模输出端U oc1、U oc2均为反相输出端,则共模电压放大倍数为: uc2 uc1uc A A A -= uc2 i oc2i oc1uc1 A U U U U A == = 电路的共模抑制比K CMR 为:

全差分运算放大器设计说明

全差分运算放大器设计 岳生生(6) 一、设计指标 以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下: ?直流增益:>80dB ?单位增益带宽:>50MHz ?负载电容:=5pF ?相位裕量:>60度 ?增益裕量:>12dB ?差分压摆率:>200V/us ?共模电压:2.5V (VDD=5V) ?差分输入摆幅:>±4V 二、运放结构选择

运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。如图2所示;(b )折叠共源共栅,folded-cascode 。如图3所示;(c )共源共栅,telescopic 。如图1的前级所示。本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT N V 之和小于0.5V ,输出端的所有PMOS 管的 ,DSAT P V 之和也必须小于0.5V 。对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该 要求,因此我们采用两级运算放大器结构。另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。 三、性能指标分析 1、 差分直流增益 (Adm>80db) 该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益 1 3 5 11135711 3 5 1 3 5 7 5 3 ()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r =-=-=- +P 第二级增益 9 2 291129 9 11 ()m o o o m m o o g g G A R r r g g =-=-=- +P 整个运算放大器的增益: 4 1 3 5 9 1 2 1 3 5 7 5 3 9 11 (80)10m m m m overall o o o o m m o o dB g g g g A A A g g g g r r r r == ≥++ 2、 差分压摆率 (>200V/us ) 转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。 定义转换速率SR :

差分运放运算放大器

图3.8a.4 差分放大电路 差分放大器 如图所示,通过采用两个输入,该差分放大器产生的输出等于U1和U2之差乘以增益系数 运算放大器的单电源供电方法 大部分运算放大器要求双电源(正负电源)供电,只有少部分运算放大器可以在单电源供电状态下工作,如LM358(双运放)、LM324(四运放)、CA3140(单运放)等。需要说明的是,单电源供电的运算放大器不仅可以在单电源条件下工作,也可在双电源供电状态下工作。例如,LM324可以在、+5~+12V单电源供电状态下工作,也可以在+5~±12V双电源供电状态下工作。 在一些交流信号放大电路中,也可以采用电源偏置电路,将静态直流输出电压降为电源电压的一半,采用单电源工作,但输入和输出信号都需要加交流耦合电容,利用单电源供电的反相放大器如图1(a)所示,其运放输出波形如图1(b)所示。 该电路的增益Avf=-RF/R1。R2=R3时,静态直流电压Vo(DC)=1/2Vcc。耦合电容Cl和C2的值由所需的低频响应和电路的输入阻抗(对于C1)或负载(对于C2)来确定。Cl及C2可由下式来确定:C1=1000/2πfoRl(μF);C2=1000/2πfoRL(μF),式中,fo是所要求最低输入频率。若R1、RL单位用kΩ,fO用Hz,则求得的C1、C2单位为μF。一般来说,R2=R3≈2RF。 图2是一种单电源加法运算放大器。该电路输出电压Vo=一RF(V1/Rl十V2/R2十V3/R3),若R1=R2=R3=RF,则Vo=一(V1十V2十V3)。需要说明的是,采用单电源供电是要付出一定代价的。它是个甲类放大器,在无信号输入时,损耗较大。 思考题(1)图3是一种增益为10、输入阻抗为10kΩ、低频响应近似为30Hz、驱动负载为1kΩ的单电源反相放大器电路。该电路的不失真输入电压的峰—峰值是多少呢?(提示:一般运算放大器的典型输入、输

差动放大电路_实验报告

实验五差动放大电路 (本实验数据与数据处理由果冻提供,仅供参考,请勿传阅.谢谢~) 一、实验目的 1、加深对差动放大器性能及特点的理解 2、学习差动放大器主要性能指标的测试方法 二、实验原理 R P用来调节T1、T2管的静态工作点, V i=0时, V O=0。R E为两管共用的发射极电阻,它对差模信号无负反馈作用,不影响差模电压放大倍数,但对共模信号有较强的负反馈作用,可以有效抑制零漂。 差分放大器实验电路图 三、实验设备与器件 1、±12V直流电源 2、函数信号发生器 3、双踪示波器 4、交流毫伏表 5、直流电压表 6、晶体三极管3DG6×3, T1、T2管特性参数一致,或9011×3,电阻器、电容器若干。 四、实验内容 1、典型差动放大器性能测试 开关K拨向左边构成典型差动放大器。 1) 测量静态工作点 ①调节放大器零点

信号源不接入。将放大器输入端A 、B 与地短接,接通±12V 直流电源,用直流电压表测量输出电压V O ,调节调零电位器R P ,使V O =0。 ②测量静态工作点 再记下下表。 2) 测量差模电压放大倍数(须调节直流电压源Ui1=0.1V ,Ui2=-0.1V) 3) 测量共模电压放大倍数 理论计算:(r be =3K .β=100. Rp=330Ω) 静态工作点: E3 BE EE CC 212 E3 C3R V )V (V R R R I I -++≈≈=1.153mA I c Q =I c 3/2=0.577mA, I b Q =I c /β=0.577/100=5.77uA U CEQ =V cc-I c R c+U BEQ =12-0.577*10+0.7=6.93V 双端输出:(注:一般放大倍数A 的下标d 表示差模,下标c 表示共模,注意分辨) P be B C i O d β)R (12 1 r R βR △V △V A +++- ===-33.71 A c 双 =0.

采用折叠式共源共栅结构实现高速CMOS全差分运算放大器的设计

采用折叠式共源共栅结构实现高速CMOS全差分运算放 大器的设计 “随着数/模转换器(DAC)、模/数转换器(ADC)的广泛应用,高速运算放大器作为其 部件受到越来越广泛的关注和研究。速度和 是模拟集成电路的2个重要指标,然而速度的提高取决于运放的单位增益带宽及单极点特性并相互制约,而 则与运放的直流增益密切相关。在实际应用中需要针对运放的特点对这2个指标要进行折衷考虑。 1运放结构与选择 根据需要,本文设计运算放大器需要在较低的电压下能有大的转换速率、快的建立时间,同时要折衷考虑增益与频率特性及共模抑制比(CMRR)和电源抑制比(PSRR)等性能。 常见的用于主运放设计的结构大致可分3种:两级式(TwoStage)结构、套简式共源共栅(TelescopicCascode)结构及折叠式共源共栅(FoldCascode)结构。两级式结构的第1级可提供高的直流增益,而第2级提供大的输出摆幅。但由于第2级电流很大,故使得运放功耗大大增加,同时由于级联而多产生一个非主极点,速度及带宽都有所降低,需进行频率补偿,这样不仅增加的设计复杂度还会大大影响运放的速度;套简式共源共栅结构由于只有2条支路,功耗为三者 ,频率特性 ,但由于需要层叠多级管子,导致输出摆幅很低,在低电压工作下很难正常工作,并且输入输出端不能短接;而折叠式共源共栅结构的各参数特性介于前两者之间,增益基本与套简式共源共栅相同而低于两级运放,虽为4条支路,功耗及频率特性均远好于两级运

放,输出摆幅大于套筒式共源共栅结构,输入输出可以短接且输入共模电平更容易选取并可接近电源供给的一端电压。经综合考虑,本设计采用折叠式共源共栅结构作为主运放。 2主运放分析 2.1全差分折叠式共源共栅 全差分运放即指输入和输出都是差分信号的运放,其优点为能提供更低的噪声,较大的输出电压摆幅和共模抑制比,可较好地抑制谐波失真的偶数阶项等。虽然NMOS管中载流子迁移率较大,作为输入器件可达到更高的增益,但付出的代价是折叠点上的极点更低而导致相位裕度下降且噪声更大。综合考虑,本设计采用PMOS管为输入管的共源共栅结构。如图1所示,PMOS管M0为偏置电流源,输入管M1,M2将在M0提供的固定偏置电流作用下,将差分输入电压转化为差分电流,经过共源共栅管M5,M6的作用下再产生差分输出电压Vout1与Vout2。而层叠的PMOS对管M7,M8与M9,M10起到了稳定输出电平与提高增益的作用。

电位差计校准电表实验报告(完整版)

电位差计校准电流表

3 、电位差计的标准 要想使回路的工作电流等于设计时规定的标准值I O ,必须对电位差计进行校准。方法如图所示。E S 是已知的标准电动势,根据它的大小,取cd 间电阻为R cd ,使R cd =E S /I O ,将开关K 倒向E S ,调节R 使检流计指针无偏转,电路达到补偿,这时I O 满足关系I O = E S /R cd ,由于已知的E S 、R cd 都相当准确,所以I O 就被精确地校准到标准值,要注意测量时R 不可再调,否则工作电流不再等于I O 。 4﹑电流表的校准 校正电流表的电路如图5-20-4所示,图中毫安表为被校准电流表,R 为限流器,s R 为标准电阻,有4个接头,上面两个是电流接头,接电流表,下面两个是电压接头,接电位差计。电位差计可测出s R 上的电压s U ,则流过s R E R a b c d Es Ex K 图5-20-4 电位差计校正电流表电路

中电流的实际值为s s R U I /0= 在毫安表上读出电流指示值I ,与0I 进行比较,其差值0I I I -=?称为电流表指示值的绝对误差。找出所测值中的最大绝对误差m I ?,按式(0-0-1)确定电流表级别。 %100??= 量限 m I a (0-0-1) 电路实物图: 五、实验内容及步骤 1、校准学生式电位差计 使用电位差计之前,先要进行校准,使电流达到规定值。先放好R A 、R B 和R C ,使其电压刻度等于标准电池电动势,取掉检流计上短路线,用所附导线将K 1、K 2、K 3、G 、R 、R b 和电位差计等各相应端钮间按原理线路图进行连接,经反复检查无误后,接入工作电源E ,标准电池E S 和待测电动势E X ,R b 先取电阻箱的最大值,(使用时如果检流计不稳定,可将其值调小,直到检流计稳定为止),合上K 1、K 3,将K 2推向E S (间歇使用),并同时调节R ,使检流计无偏转(指零),为了增加检流计灵敏度,应逐步减少R b ,如此反复开、合K 2 ,确认检流计中无电流流过时,则I O 已达到规定值。