集成电路技术概况 - 半导体集成电路技术是现代

集成电路技术概况

陈岚

摘要本文介绍了集成电路技术的分工,指出在集成电路技术的各部分中集成电路设计技术对集成电路产品的性能、可靠性、成品率及成本等起着举足轻重的作用,并最终决定一个产品的竞争力,分析了集成电路设计技术与系统设计的关系。

关键词 集成电路设计技术,系统设计,半导体技术

前言

半导体集成电路技术是现代信息技术的核心。近几十年集成电路技术的快速发展带动了整个信息技术行业的飞速发展,使电子信息产业超过了以汽车、石油、钢铁为代表的传统工业成为第一大产业, 同时也成为改造和拉动传统产业迈向数字时代的强大引擎和雄厚基石。可以说半导体技术的发展造就了今天信息化、网络化的数字时代。美国耶鲁大学著名半导体专家马佐平教授提出从集成电路技术规模化生产能力形成的20世纪70年代开始,人类社会进入了“硅器时代”。这形象说明了集成电路技术对现代社会的巨大推动作用。据资料统计,1999年全球集成电路的销售额为1250亿美元,以集成电路为核心的电子信息产业的世界贸易总额约占世界GNP的3%。每l~2美元的集成电路产值将带动10美元左右电子工业产值的形成, 进而带动了100美元GDP的增长[5]。预计未来10年内,世界集成电路销售额将以年平均15%的速度增长, 2010年将达到6000~8000亿美元。我国集成电路市场的产量和销售在最近几年更是以30%的速度增长。产业规模从2000年到2004年的四年中扩大了3倍,在全球集成电路产业中所占份额由2000年的1.2%提高到3.7%,成为全球集成电路产业发展最快的地区。

集成电路技术涉及半导体器件物理、微电子学、电子学、无线电、光学以及信息学等学科领域的知识。从产业分工角度可以分为集成电路加工、集成电路设计以及集成电路测试封装等几方面。

集成电路加工技术

集成电路加工主要是通过物理或化学手段在硅材料上生成半导体器件(比如场效应管)以及器件之间的物理互连。这些器件以及器件之间的互连构成的电路功能要符合系统设计要求。集成电路加工技术涉及的知识包括半导体器件物理、精密仪器、光学等领域,具体应用在工艺流程中,包括注入、掺杂、器件模型、工艺偏差模型、成品率分析以及工艺过程设计等。按照使用的加工材料可以分为CMOS1工艺、SiGe2工艺、AsGa3工艺以及双极工艺等。由于可规模化生产技术的水平和价格等多方面因素,目前最常用的是CMOS工艺以及双极型工艺。衡量CMOS加工技术的主要技术指标是硅基上MOS器件的沟道长或者是1/2 metal pitch(metal pitch = 一条金属连线允许的最小宽+金属连线之间允许的最小间距)或者1/2poly pitch(poly pitch = 一条多晶允许的最小宽+多晶体之间允许的最小间距)[1]。

在近十几年的时间里,集成电路加工工艺水平一直按照摩尔(Moore)定律在快速发展。目前国际上主要的集成电路代工厂可规模化生产的加工水平已经到0.13μm,像Intel、TI以及IBM等IDM4公司的加工工艺水平已经达到90nm。按照ITRS[3]的预计到今年,80nm(1/2 pitch)的逻辑工艺可以达到规模化加工水平,到2008年逻辑工艺水平可以达到57nm 1/2 pitch[1]。

集成电路测试、封装技术

集成电路测试包括完成在硅基上产生符合功能要求的电路后对裸片硅的功能和性能的测试(中测)以及封装后的测试(成品测试)。集成电路封装是指为了防止空气中的杂质对芯片电路的腐蚀造成电气性能下降,为保证集成电路产品长期有效工作,为便于保存、运输以及在PCB上安装而在裸片外部加上的与自然环境隔离的保护措施。在行业中通常把测试和封装统称为集成电路后道工

1 Complementary Metal Oxide Semiconductor,互补金属氧化物半导体

2 Silicon Germanium 硅锗

3 Gallium Arsenide 砷化镓

4 Integrated Device Manufacturers集成器件制造商

序。

随着芯片加工工艺的进步,单芯片集成度的大幅度提高,对测试技术提出了越来越高的要求。除了机台上测试技术的研究,目前在测试技术方面针对集成电路可测性和易测性的设计技术(DFT5),从验证平台到测试平台的测试矢量转换等成为集成电路测试技术研究的热点和方向。

在集成电路封装方面,按照封装使用的管壳材料可以分为塑料封装和陶瓷封装;按照管壳形状以及管脚分布和特征又可以分为DIP、PQFP、TSOP、TSSOP、 PGA、BGA、QFP、TQFP等封装形式。由于集成电路芯片的工作频率越来越高,功耗越来越大,对封装技术,比如管壳的散热、寄生参数、电磁兼容等特性提出了更高要求。

集成电路设计技术

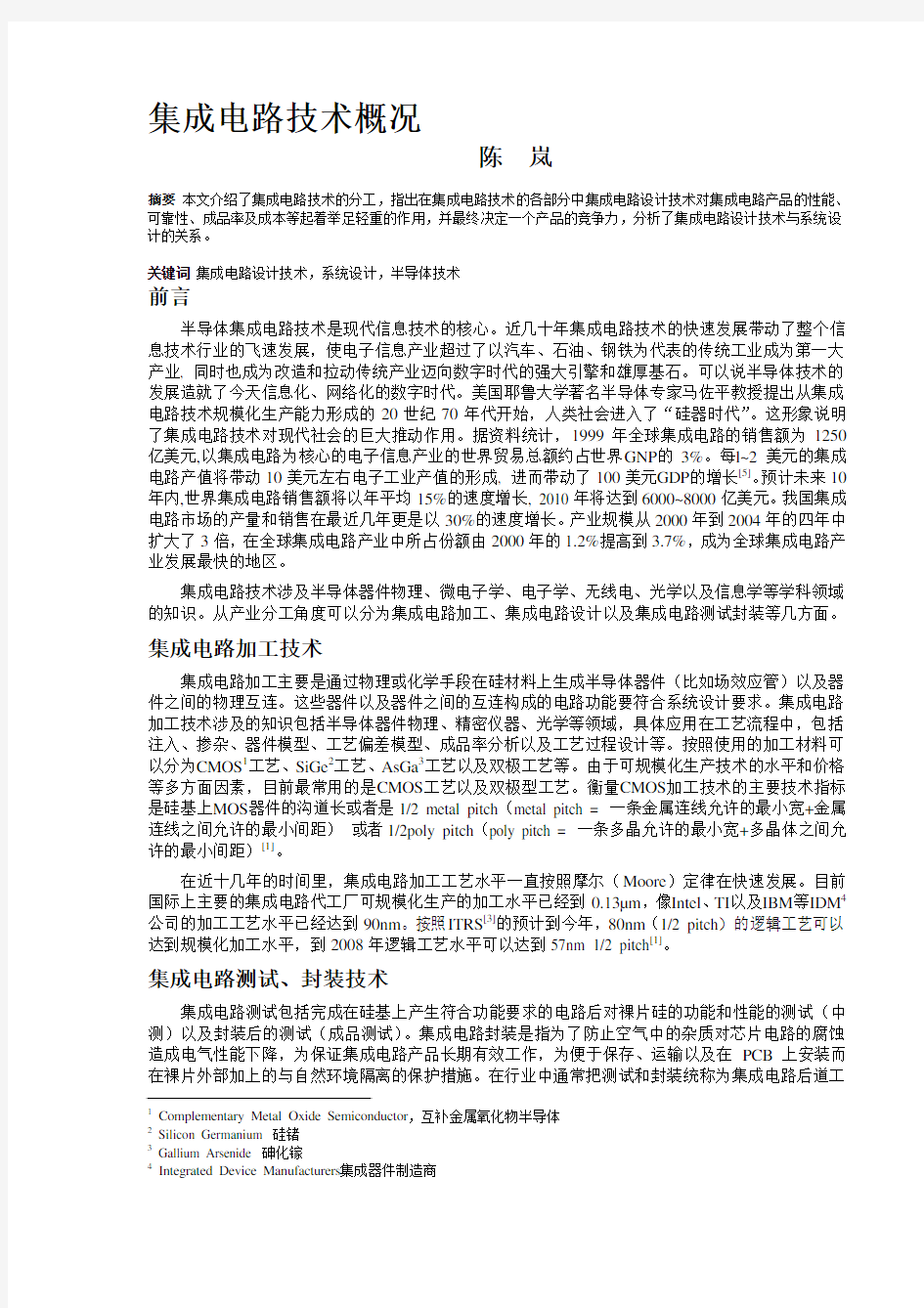

集成电路设计技术是集成电路技术中的软性技术,同时也是附加值最高的技术。经过集成电路设计,一片实现了特定功能的圆片(wafer)价格依据其实现的产品功能将比裸圆片的价格上升几十倍甚至上百倍。然而在集成电路产品的总成本中集成电路设计部分的成本却不是最大的开销。图1是集成电路产品从系统定义经过集成电路设计到芯片加工、封测再到产品的一个流程。

集成电路设计的任务是把系统应用定义的抽象描述转换成符合硅器件工作原理的电路结构实现(circuitry )并生成用于集成电路加工的数据(layout data)。集成电路设计技术实现的是一个核心的转换:把通讯、计算机等学科领域知识通过微电子技术转换成提高人类现实生活质量的电子类产品。如果说集成电路技术推动了整个信息技术领域的快速发展和繁荣。那么作为核心的集成电路设计技术是把现代信息技术与微电子技术结合起来的桥梁和关键。

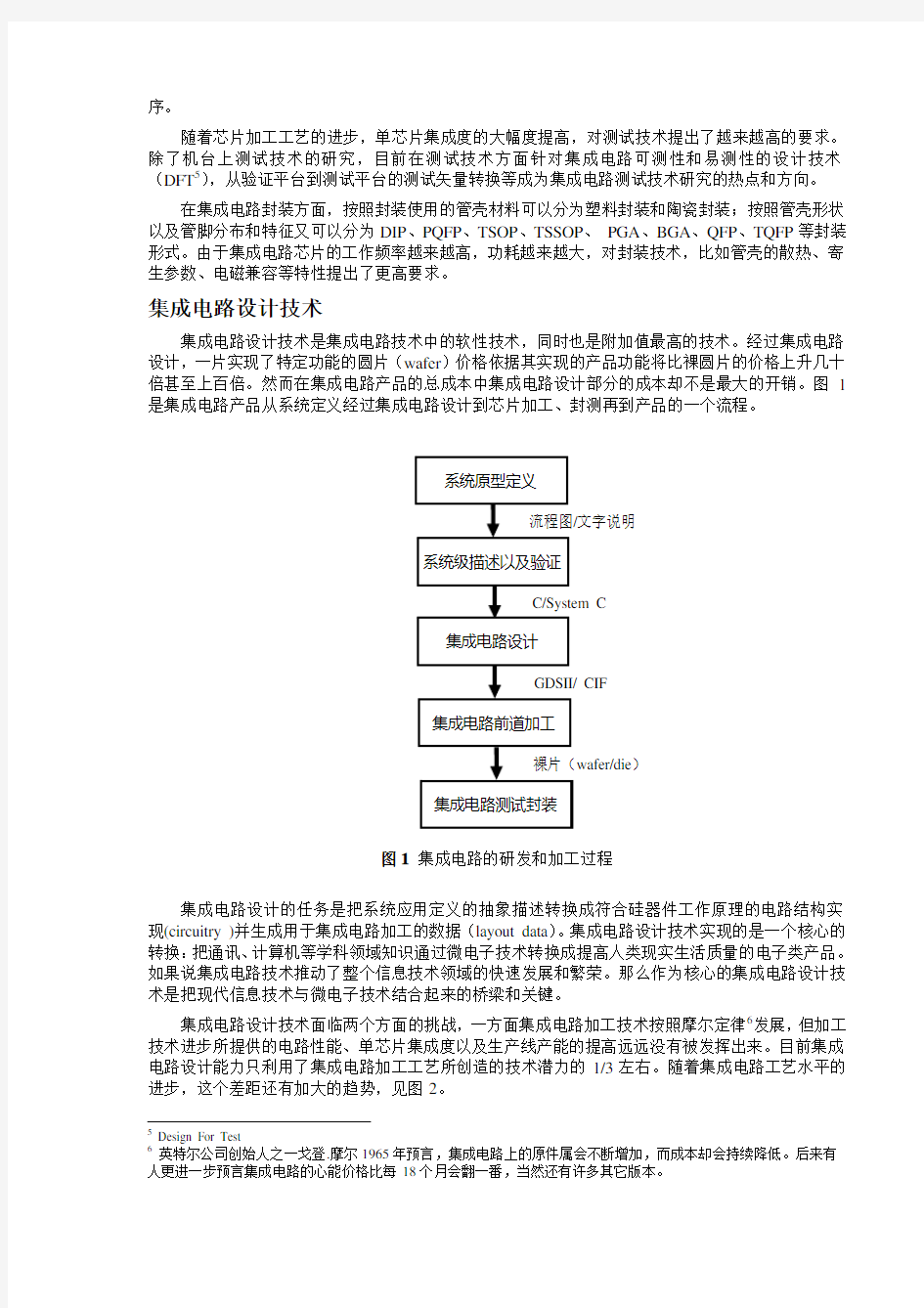

集成电路设计技术面临两个方面的挑战,一方面集成电路加工技术按照摩尔定律6发展,但加工技术进步所提供的电路性能、单芯片集成度以及生产线产能的提高远远没有被发挥出来。目前集成电路设计能力只利用了集成电路加工工艺所创造的技术潜力的1/3左右。随着集成电路工艺水平的进步,这个差距还有加大的趋势,见图2。

5 Design For Test

6英特尔公司创始人之一戈登.摩尔1965年预言,集成电路上的原件属会不断增加,而成本却会持续降低。后来有人更进一步预言集成电路的心能价格比每18个月会翻一番,当然还有许多其它版本。

另外一方面,由于通讯、多媒体以及网络技术的发展,电子系统完成的功能越来越复杂。近十多年系统复杂度提高了几个数量级,电子系统无论从功能设计还是性能设计的复杂度都大幅度提高,对集成电路设计技术提出了巨大的挑战。过去的系统规模可能只有几万个到几十万个晶体管,芯片面积只有几个到几十个平方毫米。现在一个系统规模可能达到几亿个晶体管甚至十几亿个晶体管;片面积甚至达到了几个平方厘米;单芯片上全局连线的长度达到了十几厘米。这给集成电路设计技术带来许多新的课题。

集成电路设计是结合信息技术和半导体技术的一个桥梁,具有很强的综合性。我国集成电路设计技术水平的提高必须走与系统技术相结合的道路。计算所作为系统大所有着开展集成电路设计技术研究需求牵引。下面介绍集成电路设计与系统设计相辅相成的关系,以及目前集成电路设计技术发展状况。

集成电路设计技术与系统领域的关系

集成电路设计技术使系统设计者得以利用微电子系统实现其设计概念、性能要求并最终保证系统有效性[2]。通过集成电路设计技术可以充分发挥半导体加工制造技术创造的潜能,提高电子系统的性能,降低其成本[2]。集成电路设计技术把描述系统设计的高层数据转换成用于微电子加工的数据;同时分析和解决微电子工艺中电特性问题。图3示意集成电路设计技术与系统设计与加工技术的关系。

集成电路加工图3.集成电路设计技术与系统设计和加工技术的关系

由图3,系统级设计完成相关的系统功能定义、系统软硬件分工以及接口设计。硬件设计和软件设计可以相对独立开发。系统级硬件设计包括系统硬件功能定义、系统级功能验证、功能定义的算法设计和验证。在用硬件描述语言对符合系统功能定义的算法进行描述时需要集成电路设计和系统设计同时协同完成。

图4.集成电路设计技术与系统设计的配合

图4中系统模块的划分以及模块的算法设计都需要由集成电路设计人员参与并考虑硅实现复杂度以及电特性。在用硬件描述语言描述设计的时候,更多的要考虑电路结构特性对系统性能的影响,在描述中可以突出对硅器件实际电路结构的设计,以保证系统的功能和性能。这是与用C语言编写验证和行为模型最大的不同之处。

现代集成电路设计技术在复杂数字系统设计技术方面的最大进步是综合技术(synthesis technology)的应用和发展。综合技术(逻辑综合和物理综合)利用了类似高级语言编译的思想,用抽象的类高级语言(硬件描述语言)对电路系统行为、时序以及拓扑结构进行形式化描述,大大提高了集成电路设计人员对系统复杂度的控制能力。硬件描述语言提供在不同设计层次--行为级、寄存器传输级(RTL级)和拓扑结构(门级)--进行描述的功能。从行为级到寄存器传输级再到门级的描述是一个从较高抽象级向硅器件底层物理结构实现接近的具体化过程,直至最后产生可以直接用于制版的图形数据(GDSII或者CIF)。这很像高级语言转换成汇编直至微指令代码的编译过程。因此,综合技术在九十年代初也被称为硅编译技术(silicon compile)。

为了达到系统设计指标并且充分利用硅器件特性达到最优的性价比,在进行系统设计时,系统模块的划分以及模块算法设计需要考虑物理实现时的特性。物理实现特性包含几方面的含义:一方面,大部分采用综合技术实现的系统需要基本单元库和IP库的支持,算法的选择和模块的划分要能够充分利用基本单元库和IP库的特征和优势。另一方面,算法设计和模块划分时,需要考虑采

用的集成电路加工工艺的技术特点。比如采用深亚微米工艺时,全局连线对性能和器件可靠性的影响比微米工艺有数量级的增加,因此在模块划分时减少互连线成为更重要的考虑因素,系统模块划分有可能是面向互连的划分而不是传统面向功能的划分。第三方面,系统设计中可能存在不适合综合技术实现的功能。综合技术对于规则的具有可重复性的结构有很好的优化和实现策略,但是对于某些电路,特别是在系统对性能或者对性价比有很高要求的时候,需要电路级的直接设计。这时候硬件描述语言编写的非拓扑结构的代码只起到功能验证和功能说明的作用。比如,为了提高速度采用动态电路结构时,弥补CMOS电路延迟不对称性和提高CMOS电路速度而采用的伪NMOS结构、DCVSL结构以及C2MOS结构用目前的综合技术是无法处理和设计的。

因此,在一个系统芯片的研制过程中,系统设计和集成电路设计有很长一个阶段需要协同工作,系统方案以及算法的设计必须考虑具体实现的物理特性;同时物理实现部分必须提供准确的电气特性以及丰富的基本单元库和IP资源,甚至专门为系统设计定制单元库。

数字系统的集成电路设计分自顶向下(top down)和自底向上(bottom up)两种层次化设计方法。自顶向下的设计方法从系统设计以及系统划分和算法设计出发,以现有的物理资源为基础,设计的主导思想和主要着眼点是在满足系统需求的前提下根据现有的物理资源以及物理实现方案选择最佳的系统设计方案。而自底向上的设计方法则是以系统达到的目标为主导,如果需要就定制实现资源,而不局限于已有的单元库。随着行业设计资源的积累和丰富、硅加工成本的降低、加工工艺可以提供的单元库性能日益增强以及系统设计规模日益扩大,自顶向下的设计方法越来越多地被使用。在少数对性能有特殊要求的复杂数字系统中会用到自顶向下和自底向上相结合的办法。

集成电路设计是为系统设计服务的,必须充分考虑系统需求;而系统设计必须考虑电路设计的约束,只有通过电路设计才能充分利用硅技术提供的潜能。二者良性互动才能实现优化的设计。

集成电路设计技术研究状况

集成电路设计技术作为微电子三大技术(设计、加工、测试)之一,是技术密集度最高,也是最具有增值效应的技术。如前所述,长期以来设计技术发展远远落后于加工技术。据预测到2008年加工工艺可以达到57nm水平,集成电路设计技术将面临纳米级工艺的设计技术、功耗设计技术、可验证系统设计技术等一系列技术难题。

集成电路设计按照其所设计电路系统功能信号的特征可以分为模拟电路和数字电路两种类型。模拟电路包括各种A/D,D/A转换电路;驱动电路;射频(RF)电路;微波器件;传感器;光电器件;功率器件等。各类模拟电路使用的设计方法大的流程基本相同,不同的是对分析和计算的模型的选择以及分析精度的要求。由于SoC技术的发展,数字电路往往遇到数模混合电路设计问题,因此,下面主要以复杂系统为讨论对象。

2005年,集成电路加工行业已经推出了可以规模化生产的90nm加工工艺,集成电路技术已经进入纳米时代。在纳米工艺条件下,目前集成电路设计技术研究方向之一是可生产问题(DFM-Design For Manufacture)。DFM在微米和深亚微米级主要是针对提高成品率的设计优化技术。到了纳米级,工艺偏差等在过去工艺条件下可以忽略或不居主要地位的因素已经变成可能影响性能甚至功能的因素,需要在设计中重点考虑,如工艺偏差的建模(modeling)、考虑DFM的EDA7以及针对工艺偏差的优化设计技术等。

其次是互连技术的研究。一方面晶体管沟道尺寸的缩小降低了晶体管的延迟,互连线延迟在系统中所占比例越来越大;另外,由于集成度的提高,使全局连线越来越长,造成传输线效应越来越严重;第三,高速情况、长传输以及新材料使用情况下,需要研究新的互连线行为分析技术和尽可能的缩短互连线长度的新设计方法。

第三是电路设计可靠性问题。主要是建立针对短沟道器件的准确电学模型以保证设计结果与加工结果相符。还要在器件的电学模型中考虑电磁兼容以及亚阈值问题。这些在微米级工艺水平下可以忽略的问题,在纳米级条件下成了影响电路系统功能和性能的重要因素。

集成度的提高带给集成电路设计的另外一大问题是系统复杂性,由此产生了三个新课题:一是7 Electronic Design Automatic,电子设计自动化

功耗,二是复杂系统的系统设计技术,还有一个是复杂系统的验证和可验证性设计。

在集成度提高的情况下,功耗问题日益突出的原因在于:单颗芯片上晶体管数量的增加使单芯片功耗大大增加,功耗密度接近或突破硅片承受极限,使发热成为突出问题;同时目前移动计算的应用越来越多,移动环境对器件功耗要求更为苛刻。这就使得降低功耗的优化设计以及芯片上供电网络的设计技术成为研究的热点

伴随集成度的提高,系统规模的扩大,为了降低设计成本,降低设计风险,使用第三方IP和设计复用技术的SoC技术成为必然趋势,从而产生了许多新的研究内容。比如数模混合信号的设计、IP模块的开发和模型化技术、软硬件协同设计等。

系统日益复杂,验证系统正确性的难度越来越大,验证技术也越来越重要,从设计后验证演化到在设计开始就考虑可验证,易验证,以大大提高验证的效率,降低系统验证的难度。

目前,最先进的集成电路设计技术研究主要还是集中在美国和欧洲的大学以及研究机构。比如DFM作为一个很新的研究方向是由卡耐基梅隆大学电机(EE)系主任斯托杰沃茨(Strojwas)教授开创。许多最新的研究成果也出自斯托杰沃茨教授的研究小组。纳米级集成电路设计技术研究的最大特点是由于研究对象复杂度大大提高,对研究条件和背景提出了更高的要求。比如,DFM研究需要有集成电路加工厂的配合,而能够提供纳米级加工能力的硅加工厂世界上屈指可数,研究成本可想而知。其他的比如可验证设计技术,低功耗设计技术等都是如此。

集成电路设计技术最终表现形态

集成电路设计技术是一种方法学,主要解决将某种功能用硅器件实现时,要解决的与硅器件特性相关的电学、电磁学、几何学、光学等方面的问题。集成电路设计技术的表现形态可以是一套设计规则,设计流程,IP以及EDA工具。

EDA工具在目前的集成电路设计中承担了非常重要的角色。随着集成度和设计复杂度越来越高,要解决上千万甚至上亿晶体管的互联,使用人工的方法是不可想象的。而且,在深亚微米工艺条件下,对器件和电路的电学特性、互联线上信号行为、器件模型、时序以及功耗的分析也越来越复杂,离开EDA就无法进行。计算机辅助集成电路设计的发展历程经历了三个阶段。从简单的辅助版图设计的图形编辑和版图验证软件(CAD),到辅助布局布线、具有电学仿真等功能的CAE(Computer Aided Engineer)以至现在的基于硅编译技术、逻辑综合技术的电子系统设计自动化EDA(Electronic System Design Automation)。

EDA技术发展今天,已经成为承载集成电路设计方法学的一个重要和主要的载体。许多最先进的集成电路设计方法学都将以EDA工具的最终形式表现并被业界应用。比如在高速复杂数字电路设计中使用的信号完整性分析方法;可以高速处理体现亚阈值寄生效应的器件模型运算的仿真方法;静态时序分析方法等,都可以通过算法、计算机辅助设计技术以EDA工具的方式表现并应用于实际的设计中。

在一个全流程的EDA工具包中包含实现和验证两个领域的方法学。实现方法包括逻辑综合、物理综合、布局布线、版图设计等技术。验证方法包括功能验证、动态仿真、静态时序分析、寄生参数提取、信号完整性分析、功耗分析、物理验证等技术和可靠性分析。目前借助EDA工具提供的设计方法学已经可以解决大部分集成电路芯片设计的80%到90%的设计问题。对作为系统验证手段的集成电路芯片,其设计和验证借助EDA工具,使用这80%到90%的设计方法学也就足够了。但是,作为产品的集成电路芯片的设计验证,仅靠EDA工具提供的方法学就显得不够,特别是在可靠性、可生产性以及可测试性方面。用于发现和定位生产造成的故障的可测试性设计方法学的研究已经有多年,目前一些成果已被抽象成为一定的设计规范集成到EDA工具中。比如mentor graphic 的TestKompress, Fastscan, MbistArchitect;Synopsys公司的DFT compiler等工具。

对于在纳米工艺下的可生产性问题,以及大面积芯片和高速芯片设计中遇到的可靠性设计问题,目前还主要靠具体的设计方法,借助EDA工具作分析来完成。而可测试性、可靠性以及可生产性是衡量一款集成电路芯片产品的一个重要的方面。也就是说这剩下的20%到10%的技术决定了一款产品是否成功。

在这里要强调,对于芯片设计来说,量产和试流片生产是完全不同的概念,二者对于集成电路

设计技术的要求是有所区别的。芯片的试流片主要是用来验证芯片的功能和部分性能是否符合设计指标,不太考虑成品率和可靠性的问题,也可以不考虑芯片设计的鲁棒性,但是对于量产,这些都是必须重点考虑的。成品率直接影响产品的成本。提高芯片生产的成品率除了对工艺一致性要考虑之外,有时候需要从电路结构设计上进行原始创新,来增加电路对工艺偏差以及仪器设备误差的容忍。很多情形下芯片的寿命和工作的稳定性可以决定产品的生命力。芯片产品的寿命和工作稳定性取决于芯片噪声容限、电迁移(EM8)、电磁兼容、电源供电网的设计。目前EDA工具只提供了这一部分问题相应的分析手段,设计方法主要还是通过经验完成。一款芯片产品的竞争力是由多个方面的技术水平决定,应用领域采用的新技术、先进的算法决定了产品在功能和性能方面的竞争力,集成电路设计技术则在芯片产品的性能、成本方面起到决定性作用。目前我国的集成电路设计行业缺乏的正是影响芯片产品竞争力的降低成本,提高可靠性方面的设计技术。

结束语

集成电路设计技术是现代信息技术的基础,从前面的论述中也能看到,集成电路技术和各类信息应用技术相辅相成,应用技术的发展需要集成电路技术作为基础技术,反过来,集成电路技术的发展需要应用技术需求的牵引。要使我国信息技术特别是集成电路技术健康持续发展,系统技术领域与集成电路领域的人员必须加强合作。

参考文献:

[1]ITRS 2002 design;

[2]ITRS 2003update design;

[3]ITRS 2004update overview and summaries;

[4]王阳元,21世纪硅微技术展望;

[5]关于呈送《关于加快我国微电子产业发展的建议》的报告

作者简介:

陈岚: 博士,中国科学院计算技术研究所研究员。计算所苏州分部副总经理

集成电路IC设计完整流程详解及各个阶段工具简介

IC设计完整流程及工具 IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。 前端设计的主要流程: 1、规格制定 芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。 2、详细设计 Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。 3、HDL编码 使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。 4、仿真验证 仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。看设计是否精确地满足了规格中的所有要求。规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。仿真验证工具Mentor公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL级的代码进行设计验证,该部分个人一般使用第一个-Modelsim。该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。 5、逻辑综合――Design Compiler 仿真验证通过,进行逻辑综合。逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。逻辑综合需要基于特定的综合库,不同的库中,门电路基

各种集成电路简介

各种集成电路简介 转帖]三.(精华)各种集成电路简介第一节三端稳压IC 电子产品中常见到的三端稳压集成电路有正电压输出的 78××系列和负电压输出的79××系列。故名思义,三端IC是指这种稳压用的集成电路只有三条引脚输出,分别是输入端、接地端和输出端。它的样子象是普通的三极管,TO-220的标准封装,也有9013样子的TO-92封装。用78/79系列三端稳压IC来组成稳压电源所需的外围元件极少,电路内部还有过流、过热及调整管的保护电路,使用起来可靠、方便,而且价格便宜。该系列集成稳压IC型号中的78或79后面的数字代表该三端集成稳压电路的输出电压,如7806表示输出电压为正6V,7909表示输出电压为负9V。78/79系列三端稳压IC有很多电子厂家生产,80年代就有了,通常前缀为生产厂家的代号,如TA7805是东芝的产品,AN7909是松下的产品。(点击这里,查看有关看前缀识别集成电路的知识)有时在数字78或79后面还有一个M或L,如78M12或79L24,用来区别输出电流和封装形式等,其中78L调系列的最大输出电流为 100mA,78M系列最大输出电流为1A,78系列最大输出电流为1.5A。它的封装也有多种,详见图。塑料封装的稳压电路具有安装容易、价格低廉等优点,因此用得比较多。

79系列除了输出电压为负。引出脚排列不同以外,命名方法、外形等均与78系列的相同。因为三端固定集成稳压电路的使用方便,电子制作中经常采用,可以用来改装分立元件的稳压电源,也经常用作电子设备的工作电源。电路图如图所示。注意三端集成稳压电路的输入、输出和接地端绝不能接错,不然容易烧坏。一般三端集成稳压电路的最小输入、输出电压差约为2V,否则不能输出稳定的电压,一般应使电压差保持在4-5V,即经变压器变压,二极管整流,电容器滤波后的电压应比稳压值高一些。在实际应用中,应在三端集成稳压电路上安装足够大的散热器(当然小功率的条件下不用)。当稳压管温度过高时,稳压性能将变差,甚至损坏。当制作中需要一个能输出1.5A以上电流的稳压电源,通常采用几块三端稳压电路并联起来,使其最大输出电流为N个1.5A,但应用时需注意:并联使用的集成稳压电路应采用同一厂家、同一批号的产品,以保证参数的一致。另外在输出电流上留有一定的余量,以避免个别集成稳压电路失效时导致其他电路的连锁烧毁。第二节语音集成电路电子制作中经常用到音乐集成电路和语言集成电路,一般称为语言片和音乐片。它们一般都是软包封,即芯片直接用黑胶封装在一小块电路板上。语音IC一般还需要少量外围元件才能工作,它们可直接焊到这块电路板上。别看语音IC应用电路很简单,但是它确确实实是一片含有成千上万个晶体管芯的

常用集成电路的型号及功能说明

型号功能 ACP2371NI 多制式数字音频信号处理电路ACVP2205 梳状滤波、视频信号处理电路 AN5071 波段转换控制电路 AN5195K 子图像信号处理电路 AN5265 伴音功率放大电路 AN5274 伴音功率放大电路 AN5285K 伴音前置放大电路 AN5342K 图像水平轮廓校正、扫描速度调制电路AN5348K AI信号处理电路 AN5521 场扫描输出电路 AN5551 枕形失真校正电路 AN5560 50/60Hz场频自动识别电路 AN5612 色差、基色信号变换电路 AN5836 双声道前置放大及控制电路 AN5858K TV/AV切换电路 AN5862K(AN5862S) 视频模拟开关 AN5891K 音频信号处理电路 AT24C02 2线电可擦、可编程只读存储器 AT24C04 2线电可擦、可编程只读存储器 AT24C08 2线电可擦、可编程只读存储器 ATQ203 扬声器切换继电器电路 BA3880S 高分辨率音频信号处理电路 BA3884S 高分辨率音频信号处理电路 BA4558N 双运算放大器 BA7604N 梳状切换开关电路 BU9252S 8bitA/D转换电路 CAT24C16 2线电可擦、可编程只读存储器 CCU-FDTV 微处理器 CCU-FDTV-06 微处理器 CD54573A/CD54573CS 波段转换控制电路 CH0403-5H61 微处理器 CH04801-5F43 微处理器 CH05001(PCA84C841) 微处理器 CH05002 微处理器 CH7001C 数字NTSC/PAL编码电路 CHT0406 微处理器 CHT0803(TMP87CP38N*) 8bit微处理器 CHT0807(TMP87CP38N) 8bit微处理器 CHT0808(TMP87CP38N) 8bit微处理器 CHT0818 微处理器 CKP1003C 微处理器 CKP1004S(TMP87CK38N) 微处理器 CKP1006S(TMP87CH38N) 微处理器

半导体集成电路习题及答案

第1章 集成电路的基本制造工艺 1.6 一般TTL 集成电路与集成运算放大器电路在选择外延层电阻率上有何区别?为什么? 答:集成运算放大器电路的外延层电阻率比一般TTL 集成电路的外延层电阻率高。 第2章 集成电路中的晶体管及其寄生效应 复 习 思 考 题 2.2 利用截锥体电阻公式,计算TTL “与非”门输出管的CS r 2.2 所示。 提示:先求截锥体的高度 up BL epi mc jc epi T x x T T -----= 然后利用公式: b a a b WL T r c -? = /ln 1ρ , 2 1 2?? =--BL C E BL S C W L R r b a a b WL T r c -? = /ln 3ρ 321C C C CS r r r r ++= 注意:在计算W 、L 时, 应考虑横向扩散。 2.3 伴随一个横向PNP 器件产生两个寄生的PNP 晶体管,试问当横向PNP 器件在4种可能 的偏置情况下,哪一种偏置会使得寄生晶体管的影响最大? 答:当横向PNP 管处于饱和状态时,会使得寄生晶体管的影响最大。 2.8 试设计一个单基极、单发射极和单集电极的输出晶体管,要求其在20mA 的电流负载下 ,OL V ≤0.4V ,请在坐标纸上放大500倍画出其版图。给出设计条件如下: 答: 解题思路 ⑴由0I 、α求有效发射区周长Eeff L ; ⑵由设计条件画图 ①先画发射区引线孔; ②由孔四边各距A D 画出发射区扩散孔; ③由A D 先画出基区扩散孔的三边; ④由B E D -画出基区引线孔; ⑤由A D 画出基区扩散孔的另一边;

⑥由A D 先画出外延岛的三边; ⑦由C B D -画出集电极接触孔; ⑧由A D 画出外延岛的另一边; ⑨由I d 画出隔离槽的四周; ⑩验证所画晶体管的CS r 是否满足V V OL 4.0≤的条件,若不满足,则要对所作 的图进行修正,直至满足V V OL 4.0≤的条件。(CS C OL r I V V 00 ES += 及己知 V V C 05.00ES =) 第3章 集成电路中的无源元件 复 习 思 考 题 3.3 设计一个4k Ω的基区扩散电阻及其版图。 试求: (1) 可取的电阻最小线宽min R W =?你取多少? 答:12μm (2) 粗估一下电阻长度,根据隔离框面积该电阻至少要几个弯头? 答:一个弯头 第4章 晶体管 (TTL)电路 复 习 思 考 题 4.4 某个TTL 与非门的输出低电平测试结果为 OL V =1V 。试问这个器件合格吗?上 机使用时有什么问题? 答:不合格。 4.5 试分析图题4.5所示STTL 电路在导通态和截止态时各节点的电压和电流,假定各管的 β=20, BEF V 和一般NPN 管相同, BCF V =0.55V , CES V =0.4~0.5V , 1 CES V =0.1~0.2V 。 答:(1)导通态(输出为低电平) V V B 1.21= , V V B 55.12= ,V V B 2.13= ,V V B 5.04= ,V V B 8.05= ,

集成电路的介绍

概述集成电路是一种采用特殊工艺,将晶体管、电阻、 电容等元件集成在硅基片上而形成的具有一定功能的器件,英 文为缩写为IC,也俗称芯片。集成电路是六十年代出现的, 当时只集成了十几个元器件。后来集成度越来越高,也有了 今天的P-III。 分类 集成电路根据不同的功能用途分为模拟和数字两大派 别,而具体功能更是数不胜数,其应用遍及人类生活的方方 面面。集成电路根据内部的集成度分为大规模中规模小规模 三类。其封装又有许多形式。“双列直插”和“单列直插” 的最为常见。消费类电子产品中用软封装的IC,精密产品 中用贴片封装的IC等。 对于CMOS型IC,特别要注意防止静电击穿IC,最好也不要 用未接地的电烙铁焊接。使用IC也要注意其参数,如工作电压, 散热等。数字IC多用+5V的工作电压,模拟IC工作电压各异。 集成电路有各种型号,其命名也有一定规律。一般是由前缀、数 字编号、后缀组成。前缀表示集成电路的生产厂家及类别,后缀 一般用来表示集成电路的封装形式、版本代号等。常用的集成电 路如小功率音频放大器LM386就因为后缀不同而有许多种。 LM386N是美国国家半导体公司的产品,LM代表线性电路,N代表 塑料双列直插。 集成电路型号众多,随着技术的发展,又有更多的功能更强、集成度更高的集成电路涌现,为电子产品的生产制作带来了方便。在设计制作时,若没有专用的集成电路可以应用,就应该尽量选用应用广泛的通用集成电路,同时考虑集成电路的价格和制作的复杂度。在电子制作中,有许多常用的集成电路,如NE555(时基电路)、LM324(四个集成的运算放大器)、TDA2822(双声道小功率放大器)、KD9300(单曲音乐集成电路)、LM317(三端可调稳压器)等。 这里有些集成电路的样子:

《半导体集成电路》考试题目及参考答案(DOC)

第一部分考试试题 第0章绪论 1.什么叫半导体集成电路? 2.按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写? 3.按照器件类型分,半导体集成电路分为哪几类? 4.按电路功能或信号类型分,半导体集成电路分为哪几类? 5.什么是特征尺寸?它对集成电路工艺有何影响? 6.名词解释:集成度、wafer size、die size、摩尔定律? 第1章集成电路的基本制造工艺 1.四层三结的结构的双极型晶体管中隐埋层的作用? 2.在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响?。 3.简单叙述一下pn结隔离的NPN晶体管的光刻步骤? 4.简述硅栅p阱CMOS的光刻步骤? 5.以p阱CMOS工艺为基础的BiCMOS的有哪些不足? 6.以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法。 7. 请画出NPN晶体管的版图,并且标注各层掺杂区域类型。 8.请画出CMOS反相器的版图,并标注各层掺杂类型和输入输出端子。 第2章集成电路中的晶体管及其寄生效应 1.简述集成双极晶体管的有源寄生效应在其各工作区能否忽略?。 2.什么是集成双极晶体管的无源寄生效应? 3. 什么是MOS晶体管的有源寄生效应? 4. 什么是MOS晶体管的闩锁效应,其对晶体管有什么影响? 5. 消除“Latch-up”效应的方法? 6.如何解决MOS器件的场区寄生MOSFET效应? 7. 如何解决MOS器件中的寄生双极晶体管效应? 第3章集成电路中的无源元件 1.双极性集成电路中最常用的电阻器和MOS集成电路中常用的电阻都有哪些? 2.集成电路中常用的电容有哪些。 3. 为什么基区薄层电阻需要修正。 4. 为什么新的工艺中要用铜布线取代铝布线。 5. 运用基区扩散电阻,设计一个方块电阻200欧,阻值为1K的电阻,已知耗散功率为20W/c㎡,该电阻上的压降为5V,设计此电阻。 第4章TTL电路 1.名词解释

几种常见集成电路的电路结构图及说明解读

几种常见集成电路的电路结构图及说明 本文简单介绍了四种基本集成电路。 数字电路 数字电路处理的是离散的非连续的电信号(称为数字信号)。研究数字电路就是要研究数字信号的产生,放大、整形、传送、控制、记忆和计数等问题。数字电路主要有以下两个特点:第一,数字电路的工作信号是不连续的数字信号,它在电路中只表现为信号的有、无或电平的高,低。所以,数字电路中的晶体管多工作在开关状态,即晶体管要么是"饱和",要么是"截止",而"放大"只是过渡状态。由于数字电路工作时只要求能可靠地判别信号的有、无或电平的高、低两种状态,因此电路对精度的要求不高,适于集成化。第二,数字电路研究的对象是电路的输出与输入之间的逻辑关系,其处理的主要波形如下图: 模拟电路 模拟电路是研究在时间上数值大小其过程是连续的一种物理量。主要应用在完成信号放大处理的驱动终端负载等领域。主要方法是工作点的设置。工具有图解法及结算法。通过对模拟电路的设计又以完成对各种信号的处理需求:如宇宙飞船发回的信号进行数万倍的放大,其要处理波形如下图: 微分电路 电路结构如图,微分电路可把矩形波转换为尖脉冲波,此电路的输出波形只反映输入波形的突变部分,即只有输入波形发生突变的瞬间才有输出。而对恒定部分则没有输出。输出的尖脉冲波形的宽度与R*C有关(即电路的时间常数),R*C越小,尖脉冲波形越尖,反之则宽。此电路的R*C必须远远少于输入波形的宽度,否则就失去了波形变换的作用,变为一般的RC耦合电路了,一般R*C少于或等于输入波形宽度的1/10就可以了。

积分电路 电路结构如图,积分电路可将矩形脉冲波转换为锯齿波或三角波,还可将锯齿波转换为抛物波。电路原理很简单,都是基于电容的冲放电原理,这里就不详细说了,这里要提的是电路的时间常数R*C,构成积分电路的条件是电路的时间常数必须要大于或等于10倍于输入波形的宽度。

半导体集成电路制造PIE常识

Question Answer & PIE

PIE 1. 何谓PIE? PIE的主要工作是什幺? 答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。 2. 200mm,300mm Wafer 代表何意义? 答:8吋硅片(wafer)直径为200mm , 直径为300mm硅片即12吋. 3. 目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺?未来北京的Fab4(四厂)采用多少mm的wafer工艺? 答:当前1~3厂为200mm(8英寸)的wafer, 工艺水平已达0.13um工艺。未来北京厂工艺wafer将使用300mm(12英寸)。 4. 我们为何需要300mm? 答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加2.25倍,芯片数目约增加2.5倍 5. 所谓的0.13 um 的工艺能力(technology)代表的是什幺意义? 答:是指工厂的工艺能力可以达到0.13 um的栅极线宽。当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。 6. 从0.35um->0.25um->0.18um->0.15um->0.13um 的technology改变又代表的是什幺意义? 答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。从0.35um -> 0.25um -> 0.18um -> 0.15um -> 0.13um 代表着每一个阶段工艺能力的提升。 7. 一般的硅片(wafer)基材(substrate)可区分为N,P两种类型(type),何谓N, P-type wafer? 答:N-type wafer 是指掺杂negative元素(5价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂positive 元素(3价电荷元素, 例如:B、In)的硅片。 200mm300mm 8〞12〞

各种集成电路介绍

第一节三端稳压IC 电子产品中常见到的三端稳压集成电路有正电压输出的78××系列和负电压输出的79××系列。故名思义,三端IC是指这种稳压用的集成电路只有三条引脚输出,分别是输入端、接地端和输出端。它的样子象是普通的三极管,TO-220的标准封装,也有9013样子的TO-92封装。 用78/79系列三端稳压IC来组成稳压电源所需的外围元件极少,电路内部还有过流、过热及调整管的保护电路,使用起来可靠、方便,而且价格便宜。该系列集成稳压IC型号中的78或79后面的数字代表该三端集成稳压电路的输出电压,如7806表示输出电压为正6V,7909表示输出电压为负9V。 78/79系列三端稳压IC有很多电子厂家生产,80年代就有了,通常前缀为生产厂家的代号,如TA7805是东芝的产品,AN7909是松下的产品。(点击这里,查看有关看前缀识别集成电路的知识) 有时在数字78或79后面还有一个M或L,如78M12或79L24,用来区别输出电流和封装形式等,其中78L调系列的最大输出电流为100mA,78M系列最大输出电流为1A,78系列最大输出电流为1.5A。它的封装也有多种,详见图。塑料封装的稳压电路具有安装容易、价格低廉等优点,因此用得比较多。79系列除了输出电压为负。引出脚排列不同以外,命名方法、外形等均与78系列的相同。 因为三端固定集成稳压电路的使用方便,电子制作中经常采用,可以用来改装分立元件的稳压电源,也经常用作电子设备的工作电源。电路图如图所示。 注意三端集成稳压电路的输入、输出和接地端绝不能接错,不然容易烧坏。一般三端集成稳压电路的最小输入、输出电压差约为2V,否则不能输出稳定的电压,一般应使电压差保持在4-5V,即经变压器变压,二极管整流,电容器滤波后的电压应比稳压值高一些。 在实际应用中,应在三端集成稳压电路上安装足够大的散热器(当然小功率的条件下不用)。当稳压管温度过高时,稳压性能将变差,甚至损坏。 当制作中需要一个能输出1.5A以上电流的稳压电源,通常采用几块三端稳压电路并联起来,使其最大输出电流为N个1.5A,但应用时需注意:并联使用的集成稳压电路应采用同一厂家、同一批号的产品,以保证参数的一致。另外在输出电流上留有一定的余量,以避免个别集成稳压电路失效时导致其他电路的连锁烧毁。 第二节语音集成电路 电子制作中经常用到音乐集成电路和语言集成电路,一般称为语言片和音乐片。它们一般都是软包封,即芯片直接用黑胶封装在一小块电路板上。语音IC一般还需要少量外围元件才能工作,它们可直接焊到这块电路板上。

常用集成电路功能

鹏运发科技有限公司收音机用集成电路 序号产品型号功能与用途封装形式境外同类产品 1 YD1000 DTS用AM/FM单片立体声收音机电路 TSSOP24 DTS是数字化影院系统 2 YD1191 AM/FM单片收音机电路 SOP28 CXA1191 3 YD1600 AM单片收音机电路 SIP9 LA1600 4 YD1619 AM/FM单片收音机电路 SOP28/SDIP30 CXA1619 5 YD1800 AM/FM单片收音机电路 SDIP22 LA1800 6 YD2003 AM/FM单片收音机电路 DIP16 TA2003 7 YD2111 AM/FM单片立体收音机电路 SDIP24/SSOP24 TA2111 8 YD2149 DTS用AM/FM单片立体声收音机电路 SDIP24/SSOP24 TA2149 9 YD7088 FM自动搜索单片收音机电路 SOP16 TDA7088T 10 YD72130 AM/FM频率锁相环 SDIP24 LC72130 11 YD72131 AM/FM频率锁相环 SDIP22 LC72131 12 YD7343 FM立体声解调电路 SIP9 TA7343 13 YD7640 AM/FM单片收音机电路 DIP16 TA7640 音频功率放大集成电路 序号产品型号功能与用途封装形式境外同类产品 1 YD1001 720mW单声道音频功放电路 DIP8 2 YD1006 18W单声道音频功放电路 TO-220B 3 YD1008 22W单声道音频功放电路 TO-220B 4 YD1026 具有待机、静音功能的25W双声道音频功放电路 FZIP12 5 YD131 6 2W双声道音频功放电路 FDIP14 μPC1316C 6 YD1519 具有待机、静音功能的6W双声道音频功放电路 FSIP9 TDA1519 7 TDA2003 10W单声道音频功放电路 TO-220B TDA2003 8 YD2025 2.3W单声道音频功放电路 DIP16 TEA2025B 9 YD2025A 2.4W单声道音频功放电路 DIP16 TEA2025B 10 YD2025H 2.4W单声道音频功放电路 HDIP12 11 YD2030 18W单声道音频功放电路 TO-220B TDA2030 12 YD2030A 20W单声道音频功放电路 TO-220B TDA2030A

半导体集成电路制造PIE常识讲解

Question & PIE Answer

PIE 1. 何谓PIE? PIE 的主要工作是什幺? 答:Process Integration Engineer(工艺整合工程师), 主要工作是整合各部门的资源, 对工艺持续进行改善, 确保产品的良率(yield)稳定良好。 2. 200mm,300mm Wafer 代表何意义? 答:8吋硅片(wafer)直径为200mm , 直径为300mm硅片即12吋. 目前中芯国际现有的三个工厂采用多少mm的硅片(wafer)工艺?未来北京3.的Fab4(四厂)采用多少mm的wafer 工艺? 答:当前1~3 厂为200mm(8 英寸)的wafer, 工艺水平已达0.13um 工艺。 未来北京厂工艺wafer 将使用300mm(12 英寸)。 4. 我们为何需要300mm? 答:wafer size 变大,单一wafer 上的芯片数(chip)变多,单位成本降低200→300 面积增加2.25倍,芯片数目约增加2.5 倍 5. 所谓的0.13 um 的工艺能力(technology)代表的是什幺意义?答:是指工厂的工艺能力可以达到0.13 um 的栅极线宽。当栅极的线宽做的越小时,整个器件就可以变的越小,工作速度也越快。 从0.35um->0.25um->0.18um->0.15um->0.13um 的technology改变又代表的是什幺意义? 答:栅极线的宽(该尺寸的大小代表半导体工艺水平的高低)做的越小时,工艺的难度便相对提高。从0.35um -> 0.25um -> 0.18um -> 0.15um -> 0.13um 代表着每一个阶段工艺能力的提升。 一般的硅片(wafer)基材(substrate)可区分为N,P 两种类型(type),何谓N, P-type wafer? 答:N-type wafer 是指掺杂negative 元素(5 价电荷元素,例如:P、As)的硅片, P-type 的wafer 是指掺杂positive 元素(3 价电荷元素, 例如:B、 In)的硅片。 8. 工厂中硅片(wafer)的制造过程可分哪几个工艺过程(module)?答:主要有四个部分:DIFF (扩散)、TF(薄膜)、PHOTO (光刻)、ETCH (刻蚀)。其中

集成电路技术应用专业简介

集成电路技术应用专业简介 专业代码610120 专业名称集成电路技术应用 基本修业年限三年 培养目标 本专业培养德、智、体、美、劳全面发展,具有良好职业道德和人文素养,掌握微电子工艺和集成电路设计领域相关专业理论知识,具备微电子工艺管理、集成电路设计及应用等能力,从事微电子制造和封装测试工艺维护管理、集成电路辅助逻辑设计、版图设计和系统应用等方面工作的高素质技术技能人才。 就业面向 主要面向半导体制造、集成电路设计等企事业单位,在微电子工艺技术员、集成电路逻辑和版图设计助理工程师、系统应用工程师等岗位,从事微电子工艺制造和封装测试、集成电路逻辑设计、版图设计、FPGA开发与应用、芯片应用方案开发等工作。主要职业能力 1.具备对新知识、新技能的学习能力和创新创业能力; 2.掌握半导体器件、集成电路的基础理论知识; 3.具备微电子工艺加工及相关设备操作能力; 4.具备集成电路逻辑设计及仿真能力; 5.具备集成电路版图设计与验证的能力;

6.具备FPGA开发与应用的能力; 7.具备芯片应用方案开发能力。 核心课程与实习实训 1.核心课程 半导体器件物理、集成电路制造工艺、半导体集成电路、VerilogHDL应用、集成电路版图设计技术、系统应用与芯片验证。 2.实习实训 在校内进行集成电路制造工艺、半导体集成电路项目、项目化版图设计与验证等实训。 在集成电路企业及相关科研院所进行实习。 衔接中职专业举例 电子与信息技术电子技术应用 接续本科专业举例 电子科学与技术微电子科学与工程 声明:此资源由本人收集整理于网络,只用于交流学习,请勿用作它途。如有侵权,请联系,删除处理。

常用的集成电路

常用的集成电路 集成电路是采用半导体制作工艺,在一块较小的单晶硅片上制作上许多晶体管及电阻器电容器等元器件,并按照多层布线或隧道布线的方法将各元器件组合成完整的电子电路。它在电路中用字母“IC”(也有用“N”等)表示。 电子制作中常用的集成电路有稳压集成电路、运放集成电路、语音集成电路、数字集成电路和时基集成电路等。 1.数字集成电路 数字集成电路可分为TTL数字集成电路、CMOS数字集成电路和ECL数字集成电路,它们的逻辑电平不同。较常用的是TTL数字集成电路和CMOS数字集成电路。图1是几种常用数字集成电路外形图。

图 1 TTL数字集成电路 TTL电路是晶体管-晶体管逻辑电路的英文缩写。TTL数字集成电路属于双极型晶体管集成电路,它又分为N-TTL、LS-TTL、ALS-TTL、AS-TTL、S-TTL等多种,其工作频率低于100MHz。 常用的TTL数字集成电路有74LS××系列、74S××系列、74ALS××系列、74AS××系列和74F××系列等。 COMS数字集成电路

CMOS电路是互补型金属氧化物半导体电路的英文缩写。CMOS数字集成电路属于单极型晶体管集成电路,其工作频率低于100kHz。它有多种类型,但最常见的是门电路。CMOS门电路中的逻辑门有非门、与门、与非门、或非门、或门、异或门、异或非门(同或门)、施密特触发门、缓冲器、驱动器等。 常用的CMOS数字集成电路有4000B系列、40H××系列(TC40H××、LR40H××、LS40H××、CC40H××)、74HC××系列等。 2.遥控集成电路 遥控集成电路包括红外线遥控集成电路、无限遥控集成电路和超声波遥控集成电路。 红外线遥控集成电路 红外线遥控集成电路分为红外线遥控发射集成电路和红外线遥控接收集成电路。 红外线遥控发射集成电路的作用是将代表各种指令的编码信号调制在红外线载体(红外线发光二极管)上,通过发射驱动电路向外辐射包含指令的红外光波。常用的红外线遥控发射集成电路有MN6014W、M3004LAB1 红外线遥控接收集成电路的作用是将光敏管接收的红外光波(已调制的含有控制指令的红外光波)转换为电信号,再将其解调还原为编码信号,送到译码电路译码后得到各种控制指令。常用的红外线遥控接收集成电路有AN5020、AN5026、CX20106A、KA2182、KA2183、μPC1373、μPC1490HA、LA7224、MC3373、TA8141、TC9134P、TC9149、TC9150、TDA2320、TDA3048等型号。 无线遥控集成电路 无线遥控电路是用无线电波作为载体来传输控制指令的。无线遥控集成电路也分为无线遥控发射集成电路和无线遥控接收集成电路。 无线遥控发射集成电路内部通常由射频振荡器、缓冲器、可控振荡器等组成。常用的无限遥控发射集成电路型号有T630、TDC1808、MC2831A、MC2833P、BA1404等。 常用的无线遥控接收集成电路有SL517、T631、M303R、TDC1809、μPC1651、C1676、MC3362、MC3363、MC3367、MC3372、TDA7021等型号。 超声波遥控集成电路 超声波遥控是利用超声波来传送控制指令的。 超声波接收集成电路内部由放大电路、检波电路、整形电路和双稳态电路等组成,常用的型号有NYKD 等。 超声波发射集成电路内部由振荡器、单脉冲放大器等组成。常用的型号有NYKO等。NYKO通常与NYKD配合使用。 3.语音集成电路 语音集成电路也称语音掩膜ROM或语音合成集成电路,其内部有存储器等电路,是一种大规模CMOS 集成电路,分为语言集成电路和音乐集成电路。厂家在生产语音集成电路时,将语言或音乐等信息以数字代码形式储存固化在集成电路内部,当该集成电路受到触发时,即可输出所储存的信息。

常用集成电路及主要参数

1 附录四、常用集成电路及主要参数 4.1 常用集成电路的引线端子识别及使用注意事项 4.1.1 集成电路引出端的识别 使用集成电路前,必须认真查对和识别集成电路的引线端,确认电源、地、输入、输出及控制端的引线号,以免因错接损坏元器件。 贴片封装(A、B)型,如附图4.1-1所示,识别时,将文字符 号正放,定位销向左,然后,从左下角起,按逆时针方向依次 为1、2、3……。 扁形和双列直插型集成电路:如附图 4.1-2(b)所示,识别 时,将文字符号标记正放,由顶部俯视,其面上有一个缺口或 小圆点,附图4.1-1贴片型,有时两者都有,这是“1”号引线 端的标记,如将该标记置于左边,然后,从左下角起,按逆时 针方向依次为1、2、3……。 一般圆型和集成电路:如附图4.1-2(a)所示,识别时,面向引出端,从定位销顺时针依次为1、2、3……。圆形多用于模拟集成电路。 (a) 园形外型(b)扁平双列直插型 附图4.1-2 集成电路外引线的识别 4.1.2 数字集成电路的使用 数字集成电路按内部组成的元器件的不同又分为:TTL电路和CMOS电路。不论哪一种集成电路,使用时,首先应查阅手册,识别集成电路的外引线端排列图,然后按照功能表使用芯片,尤其是牛规模的集成电路,应注意使能端的使用,时序电路还应注意“同步”和“异步”功能等。 使用集成路时应注意以下方面的问题。 1、TTL电路 (1)电源 ①只允许工作在5V±10%的范围内。若电源电压超过5.5V或低于4.5V,将使器件损坏或导致器件工作的逻辑功能不正常。 ②为防止动态尖峰电流造成的干扰,常在电源和地之间接人滤波电容。消除高频干扰的滤波电容取0.01~0.1PF,消除低频干扰取10—50/uF ③不要将“电源”和“地”颠倒,例如将741S00插反,缺口或小圆点置于右面,则电源的引线端与“地”引线端恰好颠倒,若不注意,这种情况极易发生,将造成元器件的损坏。 ④TTL电路的工作电流较大,例如中规模集成TTL电路需要几十毫安的工作电流,因此使用干电池长期工作,既不经济,也不可靠。 (2)输出端 ①不允许直接接地或接电源,否则将使器件损坏。 ②图腾柱输出的TTL门电路的输出端不能“线与”使用,OC门的输出端可以

硅集成电路基本工艺流程简介

硅集成电路基本工艺流程简介 近年来,日新月异的硅集成电路工艺技术迅猛发展,一些新技术、新工艺也在不断地产生,然而,无论怎样,硅集成电路制造的基本工艺还是不变的。以下是关于这些基本工艺的简单介绍。 IC制造工艺的基本原理和过程 IC基本制造工艺包括:基片外延生长、掩模制造、曝光、氧化、刻蚀、扩散、离子注入及金属层形成。 一、硅片制备(切、磨、抛) 1、晶体的生长(单晶硅材料的制备): 1) 粗硅制备: SiO2+2H2=Si+2H2O99% 经过提纯:>99.999999% 2) 提拉法 基本原理是将构成晶体的原料放在坩埚中加热熔化,在熔体表面接籽晶提拉熔体,在受控条件下,使籽晶和熔体的交界面上不断进行原子或分子的重新排列,随降温逐渐凝固而生长出单晶体.

2、晶体切片:切成厚度约几百微米的薄片 二、晶圆处理制程 主要工作为在硅晶圆上制作电路与电子元件,是整个集成电路制造过程中所需技术最复杂、资金投入最多的过程。 功能设计à模块设计à电路设计à版图设计à制作光罩 其工艺流程如下: 1、表面清洗 晶圆表面附着一层大约2um的Al2O3和甘油混合液保护之,在制作前必须进行化学刻蚀和表面清洗。 2、初次氧化 有热氧化法生成SiO2 缓冲层,用来减小后续中Si3N4对晶圆的应力 氧化技术 干法氧化Si(固) + O2 àSiO2(固) 湿法氧化Si(固) +2H2O àSiO2(固) + 2H2 3、CVD法沉积一层Si3N4。 CVD法通常分为常压CVD、低压CVD 、热CVD、电浆增强CVD及外延生长法(LPE)。 着重介绍外延生长法(LPE):该法可以在平面或非平面衬底上生长出十分完善的和单晶衬底的原子排列同样的单晶薄膜的结构。在外延工艺中,可根据需要控制外延层的导电类型、电阻率、厚度,而且这些参数不依赖于衬底情况。 4、图形转换(光刻与刻蚀) 光刻是将设计在掩模版上的图形转移到半导体晶片上,是整个集成电路制造流程中的关键工序,着重介绍如下: 1)目的:按照平面晶体管和集成电路的设计要求,在SiO2或金属蒸发层上面刻蚀出与掩模板完全对应的几何图形,以实现选择性扩散和金属膜布线。 2)原理:光刻是一种复印图像与化学腐蚀相结合的综合性技术,它先采用照相复印的方法,将光刻掩模板上的图形精确地复印在涂有光致抗蚀剂的SiO2层或金属蒸发层上,在适当波长光的照射下,光致抗蚀剂发生变化,从而提高了强度,不溶于某些有机溶剂中,未受光照的部分光致抗蚀剂不发生变化,很容易被某些有机溶剂融解。然后利用光致抗蚀剂的保护作用,对SiO2层或金属蒸发层进行选择性化学腐蚀,然后在SiO2层或金属蒸发层得到与掩模板(用石英玻璃做成的均匀平坦的薄片,表面上涂一层600 800nm厚的Cr层,使其表面光洁度更高)相对应的图形。 3)现主要采有紫外线(包括远紫外线)为光源的光刻技术,步骤如下:涂胶、前烘、曝光、显影、坚模、腐蚀、去胶。 4)光刻和刻蚀是两个不同的加工工艺,但因为这两个工艺只有连续进行,才能完成真正意义上的图形转移。在工艺线上,这两个工艺是放在同一工序,因此,有时也将这两个工艺步骤统称为光刻。 湿法刻蚀:利用液态化学试剂或溶液通过化学反应进行刻蚀的方法。 干法刻蚀:主要指利用低压放电产生的等离子体中的离子或游离基(处于激发态的分子、原子及各种原子基团等)与材料发生化学反应或通过轰击等物理作用而达到刻蚀的目的。 5) 掺杂工艺(扩散、离子注入与退火) 掺杂是根据设计的需要,将需要的杂质掺入特定的半导体区域中,以达到改变半导体电学性质,形成PN结、电阻欧姆接触,通过掺杂可以在硅衬底上形成不同类型的半导体区域,构成各种器件结构。掺杂工艺的基本思想就是通过某种技术措施,将一定浓度的三价元素,如硼,或五价元素,如磷、砷等掺入半导体衬底,掺杂方法有两种:

最新常用集成电路功能简介:2

常用集成电路功能简 介:2

IAP722 调频高放、混频集成电路 IFC380HC 图像中频放大集成电路 IN065 二本振压控振荡集成电路 IN706 数字混响延时集成电路 IR2112 半桥式变换驱动集成电路 IR2E01 发光二极管五位显示驱动集成电路IR2E02 发光二极管七位显示驱动集成电路IR3N06 调频中频放大集成电路 IR3R15 音频前置放大集成电路 IR3R18 双声道前置放大集成电路 IR3R20A 自动选曲集成电路 IR3R49 伺服控制集成电路 IR3Y29AM 色度解码集成电路 IRT1260 红外遥控信号发射集成电路 IS61C256AH-15N 存储集成电路 IS93C46 存储集成电路 IX0035CE 场扫描输出集成电路 IX0040AG 音频功率放大集成电路 IX0040TA 音频功率放大集成电路

IX0042CE 伴音制式切换6MHZ集成电路 IX0052CE 伴音中频放大、鉴频及前置放大集成电路IX0062CE 图像中频放大、视频放大集成电路 IX0064CE 图像中频放大、检波、视频放大集成电路IX0096CE 伴音信号处理集成电路 IX0101SE 微处理集成电路 IX0113 图像中频放大、检波、预视放集成电路 IX0113CEZZ 图像中频放大、检波及预视放集成电路IX0118CE 视频放大集成电路 IX0129CE 色度解码集成电路 IX0132CE 液晶显示解码集成电路 IX0147CE 电子选台集成电路 IX0162GE 伺服控制集成电路 IX0195CE 色度信号处理集成电路 IX0203GE 频段转换集成电路 IX0205CE 开关电源稳压集成电路 IX0211CE 图像中频放大、视频信号处理集成电路IX0212G 高频、中频放大集成电路 IX0214CE 音频控制集成电路

电子元件基础认识第三章:各种集成电路简介

电子元件基础认识第三章:各种集成电路简介 电子元件基础认识(三) [作者:华益转贴自:本站原创点击数:7832 更新时间:2005-3-27 文章录入:华益] 第三章:各种集成电路简介 第一节三端稳压IC ? ? 电子产品中常见到的三端稳压集成电路有正电压输出的78××系列和负电压输出的79××系列。故名思义,三端IC是指这种稳压用的集成电路只有三条引脚输出,分别是输入端、接地端和输出端。它的样子象是普通的三极管,TO-220的标准封装,也有9013样子的TO-92封装。 ? ? 用78/79系列三端稳压IC来组成稳压电源所需的外围元件极少,电路内部还有过流、过热及调整管的保护电路,使用起来可靠、方便,而且价格便宜。该系列集成稳压IC型号中的78或79后面的数字代表该三端集成稳压电路的输出电压,如7806表示输出电压为正6V,790 9表示输出电压为负9V。 ? ? 78/79系列三端稳压IC有很多电子厂家生产,80年代就有了,通常前缀为生产厂家的代号,如TA7805是东芝的产品,AN7909是松下的产品。(点击这里,查看有关看前缀识别集成电路的知识) ? ? 有时在数字78或79后面还有一个M或L,如78M12或79L24,用来区别输出电流和封装形式等,其中78L调系列的最大输出电流为10 0mA, 78M系列最大输出电流为1A,78系列最大输出电流为1.5A。它的封装也有多种,详见图。塑料封装的稳压电路具有安装容易、价格低廉等优点,因此用得比较多。 79系列除了输出电压为负。引出脚排列不同以外,命名方法、外形等均与78系列的相同。 ? ? 因为三端固定集成稳压电路的使用方便,电子制作中经常采用,可以用来改装分立元件的稳压电源,也经常用作电子设备的工作电源。电路图如图所示。 ? ? 注意三端集成稳压电路的输入、输出和接地端绝不能接错,不然容易烧坏。一般三端集成稳压电路的最小输入、输出电压差约为2V,否则不能输出稳定的电压,一般应使电压差保持在4-5V,即经变压器变压,二极管整流,电容器滤波后的电压应比稳压值高一些。 ? ? 在实际应用中,应在三端集成稳压电路上安装足够大的散热器(当然小功率的条件下不用)。当稳压管温度过高时,稳压性能将变差,

(整理)常用集成电路简介61675

常用集成电路简介 张庆双 集成电路是采用半导体制作工艺,在一块较小的单晶硅片上制作上许多晶体管及电阻器电容器等元器件,并按照多层布线或隧道布线的方法将各元器件组合成完整的电子电路。它在电路中用字母“IC”(也有用“N”等)表示。 电子制作中常用的集成电路有稳压集成电路、运放集成电路、语音集成电路、数字集成电路和时基集成电路等。 1.数字集成电路 数字集成电路可分为TTL数字集成电路、CMOS数字集成电路和ECL数字集成电路,它们的逻辑电平不同。较常用的是TTL数字集成电路和CMOS数字集成电路。图1是几种常用数字集成电路外形图。 图 1

TTL数字集成电路 TTL电路是晶体管-晶体管逻辑电路的英文缩写。TTL数字集成电路属于双极型晶体管集成电路,它又分为N-TTL、LS-TTL、ALS-TTL、AS-TTL、S-TTL等多种,其工作频率低于100MHz。 常用的TTL数字集成电路有74LS××系列、74S××系列、74ALS××系列、74AS××系列和74F××系列等。

COMS数字集成电路 CMOS电路是互补型金属氧化物半导体电路的英文缩写。CMOS数字集成电路属于单极型晶体管集成电路,其工作频率低于100kHz。它有多种类型,但最常见的是门电路。CMOS门电路中的逻辑门有非门、与门、与非门、或非门、或门、异或门、异或非门(同或门)、施密特触发门、缓冲器、驱动器等。 常用的CMOS数字集成电路有4000B系列、40H××系列(TC40H××、LR40H××、LS40H××、CC40H ××)、74HC××系列等。 2.遥控集成电路 遥控集成电路包括红外线遥控集成电路、无限遥控集成电路和超声波遥控集成电路。 红外线遥控集成电路 红外线遥控集成电路分为红外线遥控发射集成电路和红外线遥控接收集成电路。 红外线遥控发射集成电路的作用是将代表各种指令的编码信号调制在红外线载体(红外线发光二极管)上,通过发射驱动电路向外辐射包含指令的红外光波。常用的红外线遥控发射集成电路有MN6014W、M3004LAB1 、M50462AP、SAA1250、SAA3004、SAA3006、SAA3007、SAA3009、SAA3049、TC9012F、TC9012F、TC9028、TC9132P、TC9148等型号。 红外线遥控接收集成电路的作用是将光敏管接收的红外光波(已调制的含有控制指令的红外光波)转换为电信号,再将其解调还原为编码信号,送到译码电路译码后得到各种控制指令。常用的红外线遥控接收集成电路有AN5020、AN5026、CX20106A、KA2182、KA2183、μPC1373、μPC1490HA、LA7224、MC3373、TA8141、TC9134P、TC9149、TC9150、TDA2320、TDA3048等型号。 无线遥控集成电路 无线遥控电路是用无线电波作为载体来传输控制指令的。无线遥控集成电路也分为无线遥控发射集成电路和无线遥控接收集成电路。 无线遥控发射集成电路内部通常由射频振荡器、缓冲器、可控振荡器等组成。常用的无限遥控发射集成电路型号有T630、TDC1808、MC2831A、MC2833P、BA1404等。 常用的无线遥控接收集成电路有SL517、T631、M303R、TDC1809、μPC1651、C1676、MC3362、MC3363、MC3367、MC3372、TDA7021等型号。 超声波遥控集成电路 超声波遥控是利用超声波来传送控制指令的。 超声波接收集成电路内部由放大电路、检波电路、整形电路和双稳态电路等组成,常用的型号有NYKD