PCI总线数据采集系统的设计

基于PCI-E总线的多功能同步数据采集卡设计

基于PCI-E总线的多功能同步数据采集卡设计基于PCI-E总线的多功能同步数据采集卡设计摘要:随着科技的不断发展和应用领域的不断扩展,对高性能、多功能的数据采集卡的需求也越来越大。

本文提出了一种基于PCI-E总线的多功能同步数据采集卡设计方案,采用高速数据传输和同步采样技术,实现了对多种信号的高清晰度采集和处理。

1. 引言数据采集卡是一种广泛应用于各个领域的电子设备,用于采集和处理各种信号,如模拟信号、数字信号、视频信号等。

随着科技的发展和应用领域的不断扩展,人们对数据采集卡的需求也越来越高。

本文基于PCI-E总线的数据采集卡设计,旨在实现高性能、高可靠性和多功能的数据采集和处理功能。

2. 系统设计2.1 总体架构本系统的总体架构由PCI-E接口模块、时钟同步模块、高速数据采集模块、FPGA数据处理模块等组成。

PCI-E接口模块将数据采集卡与主机之间的数据传输实现,时钟同步模块用于实现各个模块之间的同步采样,高速数据采集模块负责高速采集各种信号,FPGA数据处理模块用于对采集到的数据进行处理和分析。

2.2 PCI-E接口模块PCI-E接口模块是数据采集卡与主机之间的数据传输通道,通过PCI-E总线实现高速数据传输。

在设计中,选择了PCI-E 3.0 x4作为数据采集卡的接口标准,以满足高速数据传输的需求。

2.3 时钟同步模块为了实现各个模块之间的同步采样,需要设计一个时钟同步模块。

该模块主要包括一个高精度的时钟源和时钟分频模块。

通过时钟源产生的时钟信号,经过分频模块分频后,分别作为各个模块的时钟输入。

通过时钟同步模块,实现了数据采集模块和数据处理模块之间的同步采样。

2.4 高速数据采集模块高速数据采集模块是数据采集卡的核心模块,负责采集各种信号。

该模块包括模拟信号采集电路和数字信号采集电路两部分。

模拟信号采集电路使用高精度的ADC芯片,能够实现高清晰度的模拟信号采集。

数字信号采集电路使用高速采样芯片,能够实现高速的数字信号采集。

基于PCI总线的数据采集模块设计

基于P I 要 :本设计针对 当今 工业现 场数据采集需求提 出 了一种基于P I C 总线的4 通道 高性 能并行数据采 集与处理

系统 方案 。给 出 了软 硬 件 功 能 划 分 和 实现 方 法 。 本 系统 中采 用 了P I0 4 为P I 口 芯 片;每 个 通 道 的采 样 频 C95作 C接 率为5H ,采样精度 l位 ;经实验 测试表 明,整个 系统工作稳定可靠。 kz 6 关键 词 :P I 线 ;P I0 4 C总 C9 5 #数据 采 集

、

1 、信号调理 。信号输入为4 通道单端 3V。每一路 0 信号都有单独的信号调理电路 ,包括分压电路 、信号放 大 、滤波。经调理后的信号送入1 ̄ADc 6 进行采样、转 换 。2 、高速A/ D。高速A/ 芯片采用德州仪器公司( ) D TI 的11 AR逐次逼近型) 6  ̄S ( 模数转换器( ) 70 ,该 ADCADS 89 芯片具有10 Hz 0k 的的采样速率 ,串行输出采样值 ,真正 实现 了l位无丢失码的高精度高速数据转换。本方案采 6 用ADS 4 1 80 的单端输入方式。3 、可编程器件。本方案 中 采用AL TERA公司的E C1Q 4 。可编程器件主要完 P1 2 2 0 成AD 的控制、数据缓存以及-P i  ̄ C 桥接芯片P I04 c 95的交 互 。内部逻辑用V DL H 开发主要包括时序发生器、存储 三 、结论 本系统实现了采样频率5 Hz k ,采样精度1位的4 6 通道 高速并行采样。存储器控制单元为每个通道设计了一个 位宽为1bt 6i ,深度为4 的F F 。当采到数据后 ,由内部 并行数据采集。经实验测试表明,整个系统工作稳定可 K IO 逻辑控制,将数据送人FF I O中。FF 被设计成 自身循环 靠 ,配合上层专用软件能很好的完成对工业现场的状态 I0 覆盖形式,作为采样数据的一级缓存 ,工作过程中上层 信息 的采 集 、分析 、处 理。 作者单位 :段 纯爽 四川师范大学成都 学院 应用软件对F F I O中数据个数进行查询 ,并及时将数据读 任 娟 慧 成都 航 空职 业技 术 学 院 电 子 工程 系 出,以保证系统高速高效的工作。4 、PC 接 口。目前实 I 文建钦 成都恩菲特 科技 有限公 司 现P 口的方法分为两种 :使用可编程逻辑器件和使用 I c接 参考文献 : 专用总线接 口器件 。采用可编程器件实现PC接 口比较灵 I [ 祝常红 . 1 1 数据采集与处理技术[ . M】 北京 : 电子工业 出版社 ,0 8 20 . 活,但 由于PC 总线协议的复杂陛,这种方法难度较大, I 【 李贵 山. C局部总线开发者指南n 西安 : 2 】 PI 州, 电子科技大学 出版社.

基于PCI总线模块的多通道串行数据采集系统设计

0 引 言

目前 市 面上 有多 种数 据 采集 卡 ,但 其 应用 都

具 有 一 定 的局 限 性 ,不 可 能 完 全 满 足 用 户 的 需

寄存 器 有 :供 应 商 代 码 ( e d r D V n o )寄 存 器用 于 I

标 明设 备 制造 商) ,设 备代 码 ( e i )寄 存器 D v eI c D ( 于指 明特 定 的设 备 ,它 由供 应 商 分 配) 用 ,版本

平 触发 ,P I 备 为低 电平触 发 ( vlSliv) C设 1 e—elt e。 e si P I 线 上 有 4条 中 断 请 求 信 号 线 : I A 、 C总 NT # IT # IT # N D N B 、 N C 、I T #, 中 断 引 脚 寄 存 : 值 器的

( 入/ 出)空 间 和 配置 空 间3 输 输 种地 址 空 间 ,并 具 有 两 种 工 作模 式 :其 中 主模 式 下 的P I 备 具 有 C设 总 线控 制权 ,可 以实 现D MA传输 :而被 主设备 控 制进 行 通信 的称 为从 模式 (A E ) T RG T。

PI C 总线 是 一 种 高 性 能 的局 部 总 线 ,具 有 3 2

位可 升级 到 6 位 的 、独立 于 C U的总 线 结构 。工 4 P

基 地址 寄存 器 。另外 ,若要 实 现 中断 ,还必 须设

置 中断 引 脚 ( tr p i)寄 存 器 和 中 断线 ( — I er t n n u P I n

t rp Ln 1寄存 器 。 e u t ie r 1 P I 线的 中断 机 制 . 2 C总

P I 线 的 硬 件 中 断 方 式 分 为 边 沿 触 发 和 电 C总

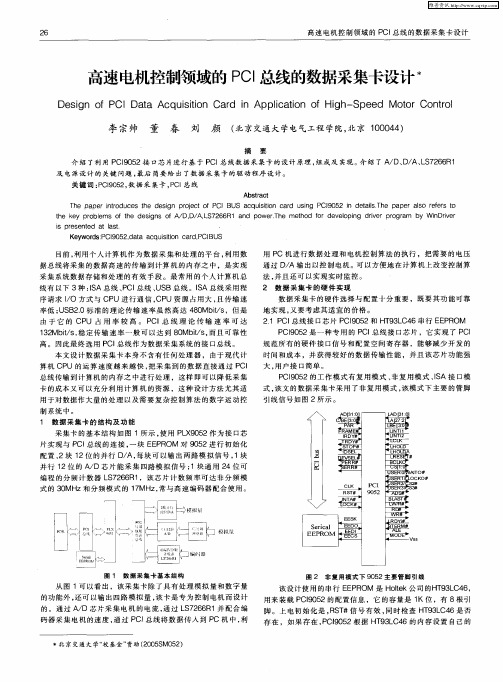

高速电机控制领域的PCI总线的数据采集卡设计

地实 现 , 又要 考 虑 其 适 宜 的 价 格 。

21 P 总线 接 口芯 片 P 9 5 CI CIO 2和 H 9 L 6串行 E P OM T 3 C4 E R

P 95 CI0 2是 一 种 专 用 的 P 总 线 接 口芯 片 ,它 实 现 了 P CI CI 规范 所 有 的硬 件 接 口信 号 和 配置 空间 寄存 器 ,能 够 减 少 开 发 的 时 间 和成 本 ,并 获得 较好 的数 据 传 输 性 能 ,并 且 该 芯 片 功 能 强 大 , 户接 口简 单 。 用 P 95 CI 2的工 作 模 式 有 复用 模 式 、 复 用 模 式 、 A 接 口模 0 非 I S 式 , 文 的数 据 采 集 卡 采 用 了 非 复 用 模 式 , 模 式 下 主要 的管 脚 该 该

引线 信 号 如 图 2所 示 。

/ 、、

采 集 卡 的 基本 结构 如 图 1所 示 , 用 P ) O 2作 为 接 口芯 使 L( 5 9

片实 现 与 P 总 线 的 连 接 , 块 E P OM 对 9 5 CI 一 E R 0 2进 行 初 始 化

益霹

兽

。

掰

’ R

维普资讯

高 速 电 机控 制 领 域 的 P 总线 的数 据 采 集 卡设 计 CI

高速电机控制领域的 P C 总线的数据采集卡设计 I

De in o CI sg f P Daa Ac ust n t q iio Ca d i i r n App ia in o gh l t f Hi -Sp e Mo o n r c o ed t r Co t o

i prs t l t s e ened at as .

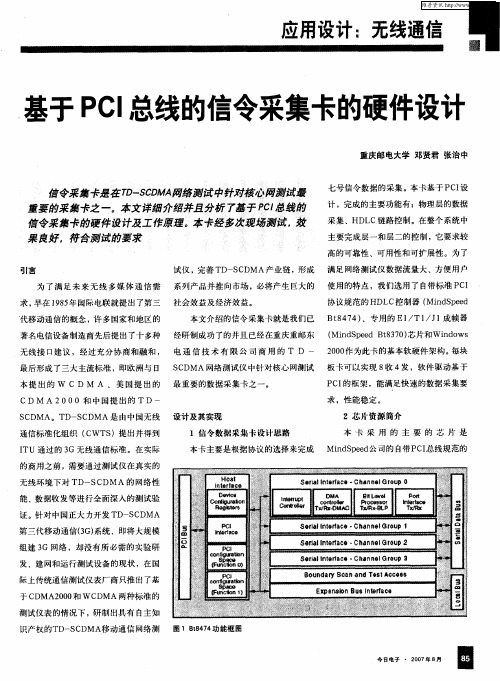

基于PCI总线的信令采集卡的硬件设计

总线是一种不依附于某个具 体处理器的

( )一个主接 口( s n efc ) 1 Ho tItra e:

局部总线 ,基于 P 的系统 不受处理 器 主接 口又 由四个部分组成 :设备配置寄 CI 升级的影响 。每个典型 的PC 可以支持 存器、P I I C 功能 0 的配置空 间、 I PC 功能 大约 1 个 电气负载。它支持 3 位或 6 1 0 2 4 的配置空 间、 C 接 口。主接 口主要提 P I 位 的 总 线 宽 度 , 支 持 的 工 作 频 率 为 供 B 4 4 P T8 7 与 C之间的接 口, 完成设备

果 良好 .符合测 试 的要求

弓 害 l

七号信令数据 的采集 。本卡基于 PC 设 I

计 ,完成 的主 要功 能有 :物 理层的数据

采集 、HDL C链路控制 。在 整个系统 中 主要完成层一和层二 的控制 ,它要求较 高 的可靠性 、可用性 和可扩展性 。为了

试仪 ,完善 T S DMA产业链 ,形成 满足 网络 测试 仪数据流量大 、方 便用户 D— C

图 2 B8 7 的 串口功能设计原 理图 t4 4

完成和其他设备之 间的通信控制 。 ( 2)接 收 / 发送 线 性 接 口单 元 ( I T I 。 RL U/ L U) 数 字发送 器 ( XMT 。 R) 数据接收 器 ( VR) RC 。 发送 系统总线 ( S 。 T B) 接收 系统总线 ( B) RS 。 时钟 速率 适配器 ( AD) CL 。 边界 扫描 接 口 (T J AG) 。 其功能 图如 图 3 、图 4 所示 。

维普资讯

应用设计 无线通信

基于 P I C 总线的信令采集卡的硬件设计

重庆邮 电大学 邓贤君 张治 中

基于PCI总线的心电信号数据采集系统的设计

对于心 电信 号而言 , 采集 的信号属于差模信号 , 因而选用仪 用放大器作 为输入级信 号放 大 电路 。仪用放 大器 的特点是 : 输 入阻抗高 , 偏置 电流低 , 共模抑制 比高。图 2为仪用放大器 的电

路原理 图。

治具有现实 意义 。早 些 时候 心 电信 号 的传输 主要 依 靠 IA 总 S

s fwa e i l de h o fg ai n o ot r ncu st e c n ur to fE2 i PROM n he d v c i r d sg fPCIbu a d t e i e dve e i n o s

.

Ke od : C ( l t adogah ; C u; 2 R M, P A yw r sE G e c ocri rp ) P I sE P O F G er b

滤波的处理 。

图 2 仪用 放 大器

仪用放大器 的第 1级是两 个 同相放大器 , 2级是 一 差分 第 放大器 。图 中, 1 U u 和 2构成差 动输 入差 动输 出 , 3为基本 型 u 差动输入 , 单端 输 出。总 的电压增 益 等于 两级增 益 之积 。第 1

级采用 同相输 入 , 平衡对 称的 电路结构使输入级共模 抑制 比高 ,

为 0 0 20 H , . 5— 5 z并且大部分 信号集中在 1 7 , 4~ 5Hz幅值 为 1 O V~5m V。而且人体是 导 电体 , 外 的电场 、 体 磁场 感应都 会 在

人体 内形成 噪声 , 加上人体 本身 各器 官的功 能活 动都会影 响心 电信号 的采集 。针对 心电信号的这些特点 , 必须对它进行 放大 、

1 12 光 电耦 合 器 构 成 的 隔 离放 大 器 ..

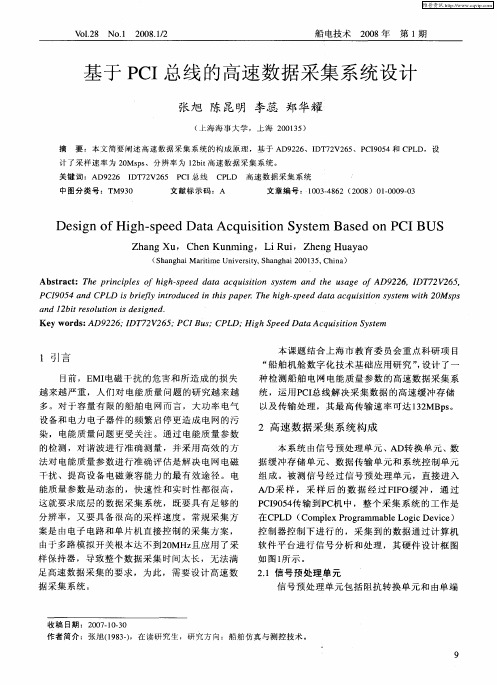

基于PCI总线的高速数据采集系统设计

控 制 器 控 制 下 进 行 的 ,采 集 到 的数 据 通 过 计 算机 软 件 平 台进 行 信 号 分 析 和 处 理 ,其 硬 件 设 计 框 图

如 图1 示 。 所

样 保 持器 , 导致 整 个 数 据 采 集 时 间 太长 ,无 法 满 足 高 速 数据 采 集 的要 求 ,为 此 , 需 要 设计 高速 数

Zha g Xu, Che n i n n Ku m ng, LiRu , Zhe a a i ng Hu y o

( h n h i aii ie st, h n h i2 01 5 Ch n ) S a g a rt M meUn v riy S a g a 0 3 , i a

多 。对 于容 量 有 限 的船 舶 电 网而 言 ,大 功率 电气 设 备和 电力 电子 器 件 的频 繁 启停 更造 成 电 网 的污 染 , 电能质 量 问题 更 受 关 注 。通 过 电能质 量 参 数 的检 测 ,对 谐 波进 行 准确 测量 , 并采 用 高 效 的方 法对 电 能质 量 参 数进 行准 确 评 估 是解 决 电 网 电磁 干扰 、提 高 设 备 电磁 兼 容 能力 的最 有 效 途 径 。 电 能质 量 参 数 是 动 态 的 ,快速 性 和 实 时性 都 很 高 , 这就 要 求底 层 的 数据 采 集 系 统 , 既要 具 有 足 够 的 分辨 率 ,又 要 具备 很 高 的采 样 速 度 。常 规 采 集 方 案 是 由 电子 电路 和 单 片 机 直 接 控 制 的采 集 方 案 ,

Ab ta t h rn lso ih se d d t c us in sse a d te u a e o sr c:T ep ic e f hg — e aa a q i t y t p io m n h sg AD9 2 ,I 7 6 , f 2 6 DT 2 2 5 V

基于PCI总线的视频采集系统设计

总第173期2008年第11期舰船电子工程Ship Electronic Enginee ring Vol.28No.11158 基于PCI 总线的视频采集系统设计3陈东旭1) 席泽敏1) 盛成明2) 李汉钊1)(海军工程大学1) 武汉 430033)(海军702厂2) 上海 210000)摘 要 主要介绍了基于P CI 总线的视频采集系统的硬件实现;通过VFW 软件开发包,探讨了视频采集及用MP EG 4压缩编码中的编程设置。

关键词 PCI 总线;视频采集系统;V FW;MP EG 4中图分类号 TP368.1Desi gn of Video Cap tu re Syst em Based on PCI BusC he nD ongxu 1) Xi Ze min 1) Sheng C he ngmi ng 2) L i Ha nzhao 1)(Naval Unive rsity of Engineering 1),Wuha n 430033)(702Factor y of Navy 2),Sha nghai 210000)Abs tra ct The paper introduces hardwa re realization of video capture syste m on PCI bus.Progra mming of the video capture and M P EG 4compr ession code is discussed by using VFW s oft ware development tools.Ke y w ords PC I Bus ,video capt ur e system ,V FW ,M P EG 4Class N umber TP368.11 引言为了采集记录雷达情报,以便脱离雷达装备和本系统在通用计算机上检索回放,设计了一种同步实时记录综合显示器画面的高速视频采集系统。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

理 论 与 方 法2008年3月第27卷 第3期中国科技核心期刊PCI 总线数据采集系统的设计梁新全 李 智(桂林电子科技大学电子工程学院 桂林 541004)摘 要:本文介绍了一种双通道PCI 总线高速数据采集系统,可单独或同时对2个输入通道的信号进行采集。

为简化接口电路的设计过程,采用接口芯片PCI9030来实现系统的P CI 总线接口功能,结合可编程逻辑器件CPL D 来实现系统的控制逻辑。

最后还介绍了在开发工具W indr iver 下,该数据采集系统驱动程序的开发。

实际应用表明,该设计满足了系统对信号采样实时性和高速数据传输性能的要求。

关键词:P CI 总线;数据采集;PCI9030中图分类号:T P336 文献标识码:ADesign of data acquisition system based on PCI busL iang X inquan L i Zhi(School of Electronic Engineering,Guilin University of Electronic Technology,Guilin 541004)Abstract:T his paper intro duces a t wo channel data acquisition system based on PCI bus.T he system can sample the sig nal from either,o r both of t he channels at o ne t ime.T o simplify the difficulty in the dev elopment of inter face circuit,the PCI9030is used to implement the perfo rmance of PCI bus int erface,and CP LD is to implement the contro l lo gic.T he art icle also discusses the dev elopment o f the device dr iv er prog ram based on Windriv er.Application in practice show s that the sy s tem meets the requirements o f real t ime sample and high speed tr ansfer.Keywords:PCI bus;data acquisition;P CI9030作者简介:梁新全(1979 ),男,硕士研究生,主要从事自动测试总线与系统方面的研究。

0 引 言在实现工业自动化测控过程中,通常需要对被测对象的一些参数进行采集、分析和处理。

随着科学技术的发展,对电子测量仪器的测试速度、测量精度、数据存储容量和数据高速传输等方面的要求越来越高。

通用型高速数据采集系统价格比较昂贵,难以广泛应用。

在实际应用中,工程工作者更多的是需要一种性能优良而价格低廉的数据采集系统。

PCI 总线是一种高性能的32/64位地址数据复用总线[1]。

支持突发传输,最大传输速率可达132M b/s;同时具有较好兼容性、存取延时小、成本低等优点。

本文介绍了基于PCI 总线的数据采集系统,具有2个模拟信号采样通道,可单独或同时对2个通道的信号进行采集。

采集信号输入电压范围为 10V ,12位数据采集精度,单通道采集速率最高可达500ksps 。

1 系统硬件结构PCI 总线数据采集系统的硬件结构框图如图1所示,主要由信号采集电路、数据存储电路和PCI 总线接口电路等部分组成。

信号采集电路为双输入通道,用于对输入模拟信号进行A/D 转换。

转换结果送入FIF O 储存器中,当FIF O 存储器中的数据量达到半满时,将数据通过PCI 总线接口送往主控计算机进行处理。

可编程逻辑器件CP L D 主要用于对信号采集、数据存储和传输过程进行监控。

图1 数据采集系统硬件结构框图162008年3月第27卷 第3期理 论 与 方 法中国科技核心期刊1.1 信号采集电路信号采集电路为双通道输入,可分别单独或同时对2个通道的信号进行采集。

输入模拟信号经过电压跟随器后送到A /D 转换器的输入端,电压跟随器由AD822集成运算放大器构成,用于输入阻抗的匹配。

A /D 转换器采用ADI 公司的A D7892 1芯片。

A D7892 1是一种低功耗、高速的12位A /D 转换器;有1个模拟信号输入通道,信号输入端有过压保护功能;芯片内部提供2.5V 参考电压,最高采样速率可达500ksps;信号输入电压范围可设定为 5V 或 10V,转换结果可以采用串行或并行方式输出。

根据要求,本系统的输入电压范围设定为 10V ,数据选用并行方式输出,采用芯片提供的内部2.5V 参考电压。

1.2 数据存储电路数据存储电路主要由2片F IFO 存储器IDT 7207构成。

IDT 7207是一种低功耗、高速的双端口先进先出存储器,单片存储容量为32K !9b 。

存储器的读、写操作是相互独立的,而且芯片会根据存入的数据量自动产生满、半满和空标志信号,所以操作起来比较方便。

2片IDT 7207经宽度扩展后构成容量为32k !18bit 的FIF O 存储器。

模拟信号经过A/D 转换后,先送入F IFO 存储器中,当存储器中的数据量达到半满时,将数据送往计算机进行处理,从而实现信号采样的实时性。

1.3 总线接口电路PCI 总线接口可以采用可编程逻辑器件或专用接口芯片来实现[2]。

由于PCI 总线协议比较复杂,而且还需要实现各类配置寄存器、地址译码和逻辑校验等功能,采用可编程逻辑器件方式难度比较大,且开发周期长。

本系统采用专用接口芯片PCI9030来实现总线接口功能。

PCI9030是P LX 公司推出的高性能PCI 总线目标接口芯片,符合PCI2.2规范。

芯片提供了PCI 总线接口信号、本地总线接口信号和串行EEPRO M 接口信号,内部还设置有各类配置寄存器。

采用专用接口芯片可以大大的简化设计难度,只需将PCI 插槽相关的地址、数据和控制信号与接口芯片PCI9030的PCI 总线接口信号进行连接即可。

PCI9030可以将复杂的P CI 总线控制逻辑简化为相对简单的本地总线控制逻辑,从而使PCI 总线接口功能的设计简化为本地总线控制逻辑的实现。

串行EEPRO M 采用93CS56芯片,用于存放PCI9030的重要配置信息,如厂商ID 、器件型号ID 、局部空间基地址、局部空间大小及映射类型、中断控制和响应等信息。

当系统上电时,这些配置信息将被自动加载到PCI9030的PCI 配置寄存器和本地配置寄存器中,用于对系统进行初始化。

主控计算机将根据PCI9030内部相关配置寄存器的内容分配系统所需要的资源。

本系统的PCI 总线接口结构图如图2所示,涉及的PCI 总线接口信号主要有[3 4]:RST #、FR AM E #、AD [31:0]、C/BE[3:0]#、IR DY#、PCL K 、T RDY #、DEV SEL #和IN T A #;串行EEP ROM 接口信号有:EE CS 、EEDI 、EESK 和EED O;本地总线接口信号有A DS #、BL A ST #、CS0#、L A [5:2]、L W/R #、L RESET o #、REA DY#和LI NT i1。

由于接口芯片符合PCI 总线规范,PCI9030的PCI 总线接口信号和串行EEPRO M 接口信号只需要分别连接到P CI 总线插槽和93CS56芯片对应的引脚即可,而本地总线信号则要根据系统设计的需要进行选择。

本系统涉及的本地总线信号及其用法如下:图2 PCI 总线接口结构图(1)L A [5:2]:本地地址总线,用于地址译码。

(2)A DS#:地址选通信号,有效则表明一个新的总线访问开始。

(3)BL AST #:突发传送结束信号,有效则表明当前进行的是本次总线访问的最后一个数据的传送。

(4)CS0#:片选信号,当本地总线访问的地址在设定的范围内时有效,该信号用作A D7892的片选信号。

(5)REA DY #:∀准备好#信号,有效则表明目标设备已准备好,P CI9030可以对目标设备进行读/写操作。

(6)LW /R #:读/写状态信号,进行读操作时为低电平,写操作时为高电平。

(7)L IN T i1:本地总线中断信号,该信号有效会引起IN T A #引脚产生P CI 中断。

(8)L RESET o#:本地总线复位信号,当P CI9030被复位时有效,也可以通过软件对配置寄存器CN T R L 的软件复位位置∀1#来产生该复位信号。

1.4 CPLD 逻辑控制单元本系统采用A LT ERA 公司的可编程逻辑器件EPM 7128作为本地总线逻辑控制单元[5],其主要作用是监控信号采集和数据存储的过程。

其工作过程如下:根据本地总线信号指令,给指定通道的A D7892芯片的/CON V ST 引脚产生1个低脉冲信号,开始对指定通道的信号进行采集;同时监控/EOC 信号的状态,/EOC 信号为低电平表明A /D 转换已经完成;当/EO C 信号变为低电平时,产生1个低脉冲送到A D7892的片选端/CS 和数据读取端/RD,将转换结果读出,同时将1个低脉冲信号送至2片F IFO 存储器IDT 7207的写允许端/W,将数据存放到FIF O 存储器中;在进行信号采集和数据存储的同时,监控IDT 7207的半满标志信号/HF ,当为低电平时驱动本地总线中断信号L IN T i1有效,产生P CI 总线中断,将F IFO 存17理 论 与 方 法2008年3月第27卷 第3期中国科技核心期刊储器中的数据送往主控计算机进行处理。

2 设备驱动程序设计设备驱动程序是指一系列用于控制硬件设备的函数,是应用程序访问计算机硬件的软件接口。

在W indo ws 操作系统下,用户态应用程序被禁止直接访问硬件,对硬件的操作只能由运行在核心态下的驱动程序或操作系统来完成。

这就需要借助驱动开发工具来开发设备的驱动程序,实现对硬件的操作。

本系统采用JU N GO 公司提供的开发工具Windriver 来进行驱动程序的开发。

Windriver 提供了在用户态下访问硬件的途径,开发者既使不熟悉操作系统的内核,也可以完成驱动程序的开发,大大简化了设备驱动程序的开发过程,缩短了开发周期。

使用Windr iver 开发PCI 总线设备驱动程序有2种方法。

一种是使用开发工具自带的Driver W izar d 来分析硬件卡,然后自动生成驱动程序的框架代码。