分频器的使用问题

预分频和后分频

预分频和后分频分频器一般都是跟计数单元一起结合使用。

预分频比是在计数单元值发生变化之前起作用(假如不用预分频时,计数器在每个上升沿到来时加1,而现在使用分频比为1:2的预分频器的话,那么必须等到两个上升沿的到来,计数器才会加1)后分频器与预分频器功能一样,只不过是在计数器值发生改变后起作用。

像TMR2的后分频器,如果不使用,计数器一但发生溢出,将立即置位标志为TMR2IF,但是如果有1:2的后分频器的话,必须两次溢出后才会置位。

定时器的“预分频”就是把CPU的时钟信号分频以后作为定时器的计时信号。

不同的分频比例,当然定时器计时的快慢就不一样了。

《简爱》是一本具有多年历史的文学着作。

至今已152年的历史了。

它的成功在于它详细的内容,精彩的片段。

在译序中,它还详细地介绍了《简爱》的作者一些背景故事。

从中我了解到了作者夏洛蒂.勃郎特的许多事。

她出生在一个年经济困顿、多灾多难的家庭;居住在一个远离尘器的穷乡僻壤;生活在革命势头正健,国家由农民向工业国过渡,新兴资产阶级日益壮大的时代,这些都给她的小说创作上打上了可见的烙印。

可惜,上帝似乎毫不吝啬的塑造了这个天才们。

有似乎急不可耐伸出了毁灭之手。

这些才华横溢的儿女,都无一例外的先于父亲再人生的黄金时间离开了人间。

惜乎,勃郎特姐妹!《简爱》这本小说,主要通过简。

爱与罗切斯特之间一波三折的爱情故事,塑造了一个出生低微、生活道路曲折,却始终坚持维护独立人格、追求个性自由、主张人生平等、不向人生低头的坚强女性。

简。

爱生存在一个父母双亡,寄人篱下的环境。

从小就承受着与同龄人不一样的待遇:姨妈的嫌弃,表姐的蔑视,表哥的侮辱和毒打。

然而,她并没有绝望,她并没有自我摧毁,并没有在侮辱中沉沦。

所带来的种种不幸的一切,相反,换回的却是简。

爱的无限信心,却是简。

爱的坚强不屈的精神,一种可战胜的内在人格力量。

不幸,在学习生活中,简。

爱仍然是承受着肉体上的受罚和心灵上的催残。

学校的施主罗可赫斯特不但当着全校师生的面诋毁她,而且把她置于耻辱台上示众。

fpga 分频时钟的使用方法

fpga 分频时钟的使用方法

FPGA(现场可编程门阵列)的分频时钟使用方法可以根据具体

的应用和FPGA型号而有所不同,但一般的步骤如下:

1. 确定分频比,首先要确定需要的分频比,即输入时钟频率与

输出时钟频率的比值。

这决定了分频器的工作方式和参数设置。

2. 实例化分频器,在FPGA的设计工具中,需要实例化一个分

频器模块。

具体的名称和参数设置取决于所使用的FPGA型号和设计

工具。

3. 设置分频参数,根据所需的分频比,设置分频器模块的参数。

这通常包括输入时钟频率、输出时钟频率、分频比等。

4. 连接时钟信号,将输入时钟信号和分频器模块连接起来,确

保输入时钟信号正确地输入到分频器模块中。

5. 生成输出时钟,根据FPGA的时钟管理资源,将分频后的时

钟信号连接到需要的逻辑模块或输出引脚上,以供其他电路使用。

在实际应用中,还需要考虑时钟的相位对齐、时序约束等问题,以确保分频后的时钟信号能够满足设计的时序要求。

此外,不同的FPGA厂家和型号可能有特定的时钟分频器资源和设置方法,因此在

具体设计时需要参考相应的FPGA手册和设计工具文档。

总的来说,FPGA的分频时钟使用方法包括确定分频比、实例化

分频器、设置分频参数、连接时钟信号和生成输出时钟等步骤,需

要根据具体情况进行详细的设置和调整。

高级pwm分频输出频率不准确的原因

高级pwm分频输出频率不准确的原因高级PWM分频输出频率不准确的原因引言:高级PWM(Pulse Width Modulation,脉宽调制)技术在现代电子设备中广泛应用,用于控制电机转速、调节电压等。

然而,有时候我们会发现高级PWM分频输出的频率并不准确,出现了一定的误差。

本文将探讨这个问题的原因,并提出一些解决方法。

一、高级PWM技术简介高级PWM技术是一种通过改变脉冲的占空比来调节输出电压或电流的技术。

它可以实现精确的电压或电流控制,具有调节范围广、效率高等优点。

高级PWM技术通常通过分频器来控制输出频率,从而满足不同应用的需求。

二、高级PWM分频输出频率不准确的原因1. 系统时钟精度不足:高级PWM技术通常需要使用系统时钟来进行频率计算和控制。

如果系统时钟的精度不足,就会导致PWM分频输出的频率不准确。

2. 分频器的误差:分频器是高级PWM技术中的关键组件,用于将系统时钟的频率降低到所需的输出频率。

然而,分频器本身存在一定的误差,特别是在高分频比的情况下,误差可能会进一步放大,导致输出频率不准确。

3. 温度变化:温度的变化会对电子元件的性能产生影响,包括分频器。

当环境温度发生变化时,分频器的工作频率可能会发生偏移,导致PWM输出频率不准确。

4. 器件老化:随着使用时间的增加,电子器件会逐渐老化,性能可能会发生变化。

分频器作为一个电子元件,也会受到老化的影响,从而导致PWM输出频率不准确。

三、解决高级PWM分频输出频率不准确的方法1. 使用更精确的系统时钟:通过使用更精确的系统时钟,可以提高PWM分频输出频率的准确性。

可以选择使用高精度的晶振或者外部时钟源,来替代系统原有的时钟。

2. 校准分频器误差:通过对分频器进行校准,可以减小误差,提高PWM输出频率的准确性。

可以通过软件或硬件方式进行校准,根据实际情况选择合适的方法。

3. 温度补偿:对于受温度影响较大的分频器,在设计时可以考虑加入温度补偿电路,通过监测环境温度来调整分频器的工作频率,从而保持PWM输出频率的稳定性。

均衡器参数详解1、均衡器的调整方法:超低..

均衡器参数详解1、均衡器的调整方法:超低..均衡器参数详解1、均衡器的调整方法:超低音: 20Hz-40Hz,适当时声音强而有力。

能控制雷声、低音鼓、管风琴和贝司的声音。

过度提升会使音乐变得混浊不清。

低音: 40Hz-150Hz,是声音的基础部份,其能量占整个音频能量的70%,是表现音乐风格的重要成份。

适当时,低音张弛得宜,声音丰满柔和,不足时声音单薄,150Hz,过度提升时会使声音发闷,明亮度下降,鼻音增强。

中低音: 150Hz-500Hz,是声音的结构部分,人声位于这个位置,不足时,演唱声会被音乐淹没,声音软而无力,适当提升时会感到浑厚有力,提高声音的力度和响度。

提升过度时会使低音变得生硬,300Hz处过度提升3-6dB,如再加上混响,则会严重影响声音的清晰度。

中音: 500Hz-2KHz,包含大多数乐器的低次谐波和泛音,是小军鼓和打击乐器的特征音。

适当时声音透彻明亮,不足时声音朦胧。

过度提升时会产生类似电话的声音。

中高音: 2KHz-5KHz,是弦乐的特征音(拉弦乐的弓与弦的摩搡声,弹拔乐的手指触弦的声音某)。

不足时声音的穿透力下降,过强时会掩蔽语言音节的识别。

高音: 7KHz-8KHz,是影响声音层次感的频率。

过度提升会使短笛、长笛声音突出,语言的齿音加重和音色发毛。

极高音: 8KHz-10KHz合适时,三角铁和立*的金属感通透率高,沙钟的节奏清晰可辨。

过度提升会使声音不自然,易烧毁高频单元。

2、平衡悦耳的声音应是:150Hz以下(低音)应是丰满、柔和而富有弹性;150Hz-500Hz(中低音)应是浑厚有力百不混浊;500Hz-5KHz(中高音)应是明亮透彻而不生硬;5KHz以上(高音)应是纤细,园顺而不尖锐刺耳。

整个频响特性平直时:声音自然丰满而有弹性,层次清晰园顺悦耳。

频响多峰谷时:声音粗糙混浊,高音刺耳发毛,无层次感扩声易发生反馈啸叫。

3、频率的音感特征:30~60Hz 沉闷如没有相当大的响度,人耳很难感觉。

HT49 MCU 的可编程分频器( PFD)使用介绍 - HT49 MCU

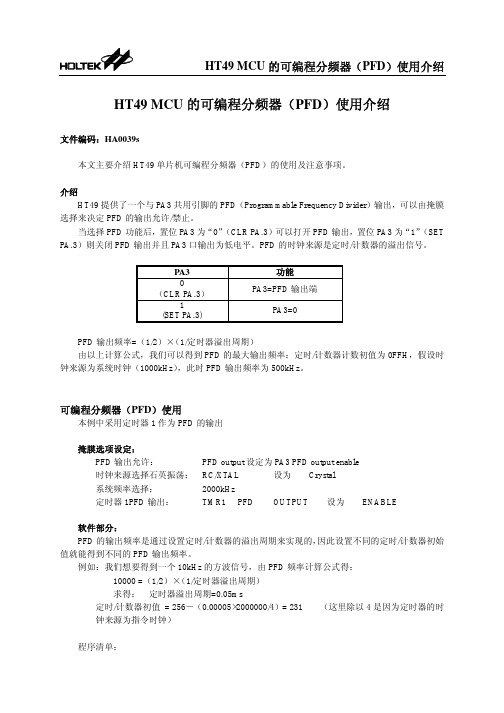

HT49 MCU的可编程分频器(PFD)使用介绍文件编码:HA0039s本文主要介绍HT49单片机可编程分频器(PFD)的使用及注意事项。

介绍HT49提供了一个与PA3共用引脚的PFD(Programmable Frequency Divider)输出,可以由掩膜选择来决定PFD的输出允许/禁止。

当选择PFD功能后,置位PA3为“0”(CLR PA.3)可以打开PFD输出,置位PA3为“1”(SET PA.3)则关闭PFD输出并且PA3口输出为低电平。

PFD的时钟来源是定时/计数器的溢出信号。

PA3 功能PA3=PFD输出端(CLR PA.3)1PA3=0(SET PA.3)PFD输出频率=(1/2)×(1/定时器溢出周期)由以上计算公式,我们可以得到PFD的最大输出频率:定时/计数器计数初值为0FFH,假设时钟来源为系统时钟(1000kHz),此时PFD输出频率为500kHz。

可编程分频器(PFD)使用本例中采用定时器1作为PFD的输出掩膜选项设定:output设定为PA3 PFD output enablePFD输出允许: PFD时钟来源选择石英振荡: RC/XTAL 设为 Crystal系统频率选择: 2000kHzOUTPUT 设为 ENABLE 定时器1PFD输出: TMR1 PFD软件部分:PFD的输出频率是通过设置定时/计数器的溢出周期来实现的,因此设置不同的定时/计数器初始值就能得到不同的PFD输出频率。

例如:我们想要得到一个10kHz的方波信号,由PFD频率计算公式得:10000 =(1/2)×(1/定时器溢出周期)求得:定时器溢出周期=0.05ms定时/计数器初值 = 256-(0.00005×2000000/4)= 231 (这里除以4是因为定时器的时钟来源为指令时钟)程序清单:include ht49r50a-1.inc;-------------------------------------------code .section at 0 'code'00horgjmpstart;-------------------------------------------start:clrintc0intc1clr定时/计数器时钟来源为系统时钟/4;mova,0a0h设置定时/计数器为时间模式movtmr1c,a ;a,(256-25) ;设置定时器的初值movtmr1,amov打开PFD输出pa.3 ;clrtmr1c.4 ;打开定时/计数器set$jmp;-------------------------------------------该程序执行结果,在PA.3引脚上用示波器测量可得到10kHz的方波。

电子分频器如何使用

电子分频器如何使用

在一套音响系统中提到分频器一般来说是指能将:20Hz--20000Hz频段的音频信号分成合适的、不同的几个频率段,然后分别送给相应功放,用来推动相应音箱的一种音响周边设备。

下面介绍一下分频器的调节方法。

电子分频器中各功能旋钮的介绍

不同的电子分频器会有不同的调整旋钮和参数,下面以:RANE(莱恩)AC22电子分频器为例作下简单介绍:

RANE(莱恩)AC22电子分频器是一台立体声分频器,每单通道从左到右有6个按钮或旋钮,依次为:

1、MASTER-LEVEL:通道信号输入电平。

可以调节输入信号的电平大小。

2、LOW-LEVEL:低音输出的音量调整旋钮。

可以调节低音输出信号电平的大小。

Xilinx中DCM的问题解决方案

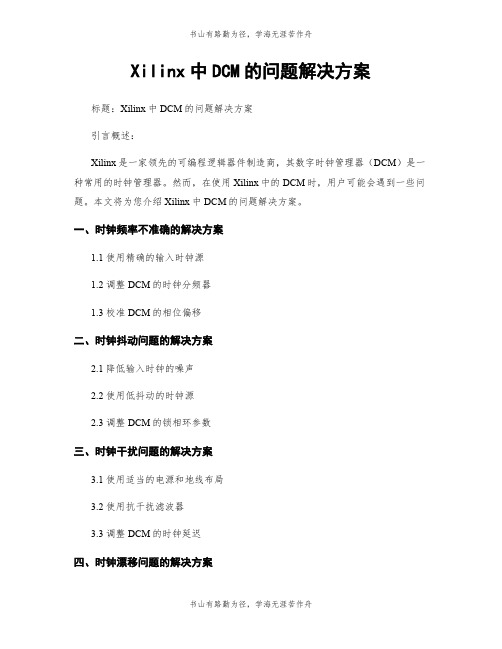

Xilinx中DCM的问题解决方案标题:Xilinx中DCM的问题解决方案

引言概述:

Xilinx是一家领先的可编程逻辑器件制造商,其数字时钟管理器(DCM)是一种常用的时钟管理器。

然而,在使用Xilinx中的DCM时,用户可能会遇到一些问题。

本文将为您介绍Xilinx中DCM的问题解决方案。

一、时钟频率不准确的解决方案

1.1 使用精确的输入时钟源

1.2 调整DCM的时钟分频器

1.3 校准DCM的相位偏移

二、时钟抖动问题的解决方案

2.1 降低输入时钟的噪声

2.2 使用低抖动的时钟源

2.3 调整DCM的锁相环参数

三、时钟干扰问题的解决方案

3.1 使用适当的电源和地线布局

3.2 使用抗干扰滤波器

3.3 调整DCM的时钟延迟

四、时钟漂移问题的解决方案

4.1 使用温度稳定的时钟源

4.2 定期校准DCM的时钟频率

4.3 调整DCM的自动校准参数

五、时钟相位问题的解决方案

5.1 使用相位锁定环(PLL)来处理相位问题

5.2 调整DCM的相位校准参数

5.3 使用外部时钟触发器来同步时钟信号

总结:

Xilinx中的DCM是一种强大的时钟管理器,但在使用过程中可能会遇到一些问题。

通过使用精确的输入时钟源、调整DCM的参数以及采取适当的电路设计措施,可以解决时钟频率、抖动、干扰、漂移和相位等问题。

通过掌握这些问题的解决方案,用户可以更好地应对Xilinx中DCM的挑战,并确保系统的时钟管理工作正常运行。

电子技术应用实验(数字电路综合实验)_电子科技大学中国大学mooc课后章节答案期末考试题库2023年

电子技术应用实验2(数字电路综合实验)_电子科技大学中国大学mooc课后章节答案期末考试题库2023年1.用数字示波器双踪测量不同频率的相关信号时,应选哪个信号为触发源?参考答案:频率低的信号2.约束文件中“set_property PULLDOWN true [get_ports {col[3]}]”是?参考答案:将第3列下拉至低电平3.若工程中只使用矩阵键盘中的一个按键,则参考答案:可以不需要按键扫描4.在本次实验示例中,将行列式键盘的行值定义为参考答案:输出信号5.如果要求不仅能显示16进制数,还要包括"-",那么显示译码器接收的数据至少应为参考答案:5位6.实现6位数码管动态显示16进制数时,可以不改写哪部分的代码?参考答案:显示译码器部分7.如果你要在一个工程中添加自定义的IP核,首先应在Project manager中点击参考答案:Settings8.IP核的意思是参考答案:知识产权核9.如果实现5位数码管动态显示,则电路中计数器的位数至少为参考答案:310.所介绍的555多谐振荡器电路中,振荡周期的改变与()有关。

参考答案:电容C_电阻R2_电阻R111.所介绍的555多谐振荡器电路中,占空比的改变与()无关。

参考答案:电容C12.对于本次实验中的多谐振荡器电路,若要实现其输出矩形波的振荡频率约为160Hz,占空比约为89%。

所选择的电阻R1和R2的比值约为()。

参考答案:7:113.对于本次实验中的多谐振荡器电路,若要实现其输出矩形波的振荡频率约为4700Hz,可供选择的电阻R1和R2值约为10千欧姆,则电容C应选取()。

参考答案:0.01微法14.所介绍的555多谐振荡器电路中,当VCC(引脚8端)为9V,电压控制端(引脚5)悬空,则该多谐振荡器Vc(2、6脚)处三角波的幅度大约为()。

参考答案:3V15.用视频中介绍的方法产生占空比为50%的分频信号输出,将50MHz信号分频为2KHz,如果计数器计数值从0依次加一到999循环,那么输出频率为?参考答案:25KHz16.假如clr是清零端,通过语句always@(posedge CP or posedge clr),可以知道clr是哪一种清零?参考答案:异步清零17.在过程块中哪种赋值语句必须按照编写顺序依次执行?参考答案:阻塞式赋值18.非阻塞式赋值的赋值运算符是?参考答案:<=19.在always块中,应该采用哪种赋值?参考答案:过程赋值20.在verilog语言中,下面哪个符号不能用作设计源文件或约束文件里的注释符号?参考答案:*21.本实验中门电路构成的单稳触发器输出信号的脉冲幅度和以下哪些因素有关?参考答案:门电路的电源电压_最后一个与非门的器件类型22.根据实验电路中给出的参数,这个单稳触发器最大定时时间可能是?参考答案:约4uS23.本实验中门电路构成的单稳触发器电路对输入信号的触发条件为?参考答案:下降沿触发24.施密特触发器和单稳态触发器都可以对脉冲实现整形,这两种电路对脉冲整形后,那种电路可以得到相同的脉宽?参考答案:单稳态触发器25.在Verilog语言中关于if-else语句说法不正确的是?参考答案:有一条if语句就有一条对应的else语句26.实验开发板的时钟为50MHZ,实验中要求设计的计数器时钟为5HZ,则分频器的分频比应为多少?采用实验介绍的分频方法,verilog语句中的分频计数范围应设为多少?参考答案:10M, 0~499999927.在本实验内容一的顶层模块连接图中,对应模块u2正确的例化语句应该是?参考答案:counter10 u2(。