第3章 触发器

第1章_逻辑代数的基础知识

(1-7)

概述

一、 数字信号和模拟信号

模拟信号:在时间和幅值上均是连续变化的信号, 即时间上的连续,量上的连续的信号。如水位,电压, 电流,温度,亮度,颜色等。在自然环境下,大多数 物理信号都是模拟量。如温度是一个模拟量,某一天 的温度在不同时间的变化情况就是一条光滑、连续的 曲线:

(2AE.4)16=2×162+10×161+14×160+4×16-1=(686.25)10

把各个非十进制数按权展开求和即可。

(1-17)

2、十进制数转换成二进制数:

十进制数转换成二进制数时,将整数部分和小数 部分分别进行转换。整数部分采用除2取余法转换, 小数部分采用乘2取整法转换。转换后再合并。 除2取余法:将十进制整数N除以2,取余数记为 K0;再将所得商除以2,取余数记为K1依此类推,直 至商为0,取余数记为Kn-1为止。即可得到与N对 应的n位二进制整数Kn-1 · · · · · ·K1 K0。 乘2取整法:将十进制小数N乘以2,取整数部分 记为K-1;再将其小数部分乘以2,取整数部分记为 K-2 ; · · · · · · 依此类推,直至其小数部分为0或达到 规定的精度要求,取整数部分记为K-m为止。即可 得到与N对应的m位二进制小数0.K-1 K-2· · · · · ·K-m。

22 „„„ 0=K0 11 „„„ 0=K1 5 „„„ 1=K2 2 „„„ 1=K3 1 „„„ 0=K4 0 „„„ 1=K5 高位

高位

低位

所以:(44.375)10=(101100.011)2

(1-19)

十进制数转换成二进制数的另一种方法是降幂比较法。如果熟 记20~210的数值是1~1024,2-1~2-4的数值是0.5~0.0625,那 么用降幂比较法,便可很容易地获得一个十进制数的二进制数转

jk触发器的工作原理及工作过程

jk触发器的工作原理及工作过程

JK触发器是数字电路中的一种基本触发器,由两个交叉耦合

的门电路组成。

它们的工作原理和工作过程如下:

工作原理:

1. J (Set) 输入信号:当J输入为高电平时,会将Q输出置为高

电平。

2. K (Reset) 输入信号:当K输入为高电平时,会将Q输出置

为低电平。

3. Q 输出信号:JK触发器的输出Q与输入J、K信号以及时

钟信号有关。

4. 时钟信号:时钟信号用于控制JK触发器的工作。

在上升沿

或下降沿(取决于电路的设计)时,JK触发器根据输入信号

的状态更新输出。

工作过程:

1. 初始状态:JK触发器的初始状态由上电时输入信号的状态

确定。

当J=K=0时,Q为先前状态的保持,即保持原来的值。

2. J=1,K=0:当J为高电平而K为低电平时,触发器会被置

入Set状态,即Q被置为高电平。

3. J=0,K=1:当J为低电平而K为高电平时,触发器会被置

入Reset状态,即Q被置为低电平。

4. J=1,K=1:当J和K均为高电平时,触发器处于反转状态。

当时钟信号的边沿到来时,Q的状态将发生改变,即Q的原

始值被翻转。

5. J=0,K=0:当J和K均为低电平时,触发器继续保持前一

个状态,即Q的值不变。

6. 更新输出:无论何时发生状态的改变,输出Q都会立即更新为新的状态。

总结起来,JK触发器根据输入信号和时钟信号的组合,可以实现保持状态、置高状态、置低状态和翻转状态四种操作。

它是许多复杂数字系统以及时序逻辑电路的重要组成部分。

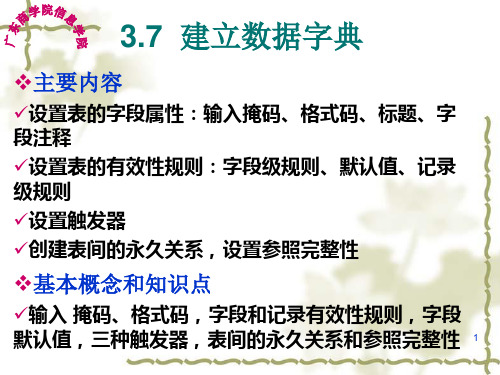

第3章 VFP 6.0数据库及其操作(4)

3.7.1 设置表的字段属性

3. 标题

字段标题将作为该字段在浏览窗口中的列标题, 字段标题将作为该字段在浏览窗口中的列标题,以 浏览窗口中的列标题 及表单表格中的默认标题名称 默认标题名称。 及表单表格中的默认标题名称。 为了在浏览窗口、 为了在浏览窗口、表单或报表中显示时让人更容易 了解该字段所代表的含义, 了解该字段所代表的含义,可以为字段指定一个字符 作为显示时的标题文字。 串,作为显示时的标题文字。如果没有为字段设置标 就显示相应的字段名。 题,就显示相应的字段名。 注意:字段标题仅仅改变在浏览窗口、 注意:字段标题仅仅改变在浏览窗口、表单或报表 显示表记录时字段名称栏所显示的文字内容, 中,显示表记录时字段名称栏所显示的文字内容,在 程序中引用该字段变量时仍应该用其字段名。 程序中引用该字段变量时仍应该用其字段名。

11

3.7.2 设置表的有效性规则

3. 表的有效性规则(即记录级规则) 表的有效性规则(即记录级规则)

控制用户输入到记录中的信息类型, 控制用户输入到记录中的信息类型,检验输入的整 条记录是否符合要求。 条记录是否符合要求。 字段级有效性规则只对应一个字段, 字段级有效性规则只对应一个字段,记录级有效性 规则通常用来比较同一条记录中的两个或两个以上 两个或两个以上字 规则通常用来比较同一条记录中的两个或两个以上字 段值,确保它们遵守在数据库中建立的有效性规则。 段值,确保它们遵守在数据库中建立的有效性规则。 注意: 注意:记录的有效性规则通常在输入或修改记录时 被激活,在删除记录时一般不起作用。 被激活,在删除记录时一般不起作用。

3

3.7.1 设置表的字段属性

2. 格式

实质上就是一种输出掩码,决定了字段在表单、 实质上就是一种输出掩码,决定了字段在表单、浏 览窗口或报表中的显示方式 显示方式。 览窗口或报表中的显示方式。 例:在“课程”表中,如果要求凡是课程名中带字 课程”表中, 母的必须一律显示为大写字母,则格式可定义为20个 母的必须一律显示为大写字母,则格式可定义为 个 )。这样在输入 “!”(假设课程名的数据宽度为 )。这样在输入 ” 假设课程名的数据宽度为20)。 课程名数据时,只要遇到小写字母, 课程名数据时,只要遇到小写字母,系统就会自动转 换为大写字母。 换为大写字母。 常用的掩码及其含义:课本 常用的掩码及其含义:课本P95 表3.7。 。

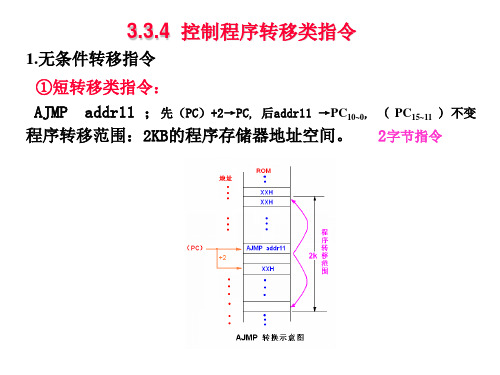

第3章.指令系统控制程序转移类指令new下

;3字节指令

同样地,使用时,可以将rel理解成标号,即: CJNE A,#data, 标号 CJNE A,direct,标号 CJNE Rn,#data,标号 CJNE @Ri,#data,标号

⑵比较(不相等)转移指令

① CJNE A,#data,rel

;先(PC)+3→PC

若(A)>#data,则(PC)+rel→PC,且0→CY; 若(A)<#data,则(PC)+rel→PC,且1→CY; 若(A)=#data,则顺序执行,且0→CY。

② rel为负数时,范围为:-128~-1 (80H~FFH)。

③相对转移指令“SJMP rel”

★正向跳转时: rel=目的地址-源地址-2

=地址差-2。

例如:

0157H

0100H:SJMP rel

设转移的地址为0157H,则: rel=0157H-0100H-2=55H。故该指令可写成:

0100H:SJMP 55H 其机器码为: 80H 55H

⑵位置1指令

SETB C SETB bit

; 1→ CY。 1字节指令 ;1→bit 。 2字节指令

2. 位修正指令

⑶位取反指令

CPL C

;(C)→C, 1字节指令

CPL bit ;(bit) → bit。 2字节指令

3. 位逻辑运算指令 ⑴位逻辑“与”指令 ANL C, bit ;(C) ∧ (bit)→C。 2字节指令 ANL C, /bit ;(C) ∧ (bit) →C。 2字节指令

; 否则顺序执行。

JNZ rel ;(PC)+2→PC。若A≠0,则转移到(PC)=(PC)+rel ;

;否则顺序执行。

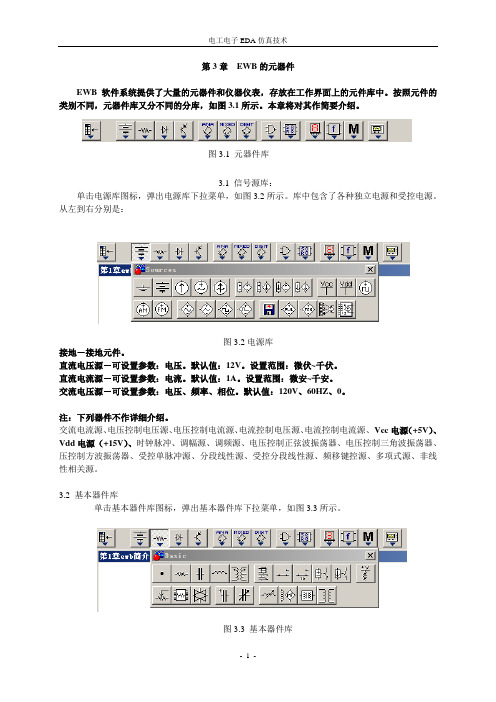

第3章EWB的元器件

第3章 EWB 的元器件EWB 软件系统提供了大量的元器件和仪器仪表,存放在工作界面上的元件库中。

按照元件的类别不同,元器件库又分不同的分库,如图3.1所示。

本章将对其作简要介绍。

3.1 信号源库:单击电源库图标,弹出电源库下拉菜单,如图3.2所示。

库中包含了各种独立电源和受控电源。

从左到右分别是:接地-接地元件。

直流电压源-可设置参数:电压。

默认值:12V 。

设置范围:微伏~千伏。

直流电流源-可设置参数:电流。

默认值:1A 。

设置范围:微安~千安。

交流电压源-可设置参数:电压、频率、相位。

默认值:120V 、60HZ 、0。

注:下列器件不作详细介绍。

交流电流源、电压控制电压源、电压控制电流源、电流控制电压源、电流控制电流源、 Vcc 电源(+5V )、Vdd 电源(+15V )、时钟脉冲、调幅源、调频源、电压控制正弦波振荡器、电压控制三角波振荡器、压控制方波振荡器、受控单脉冲源、分段线性源、受控分段线性源、频移键控源、多项式源、非线性相关源。

3.2 基本器件库单击基本器件库图标,弹出基本器件库下拉菜单,如图3.3所示。

从左到右为:连接器-用于线与线之间的连接,一个连接器可以连接四条线,连接器的产生与消失由计算机自动完成。

电阻-可设置参数:R 。

默认值为1K 。

设置范围是欧到兆欧。

电容、电感、线性变压器、继电器。

(略)开关-可设置参数:键。

默认值为空格键。

设置范围:A~Z ,0~9。

延迟开关-可设置参数:导通时间,断开时间。

默认值为0.5S ,0S 。

压控开关、电流控制开关、上拉电阻电位器-可设置参数:键。

电阻,比例设定,增量。

默认值为R ,1K ,50%,5%。

设置范围:A~Z ,0~9。

Ω~M Ω,0%~100%,0%~100%。

排电阻、电压控制模拟开关、电解电容、可变电容、可变电感、无铁心线圈、铁心、非线性变压器。

(略)3.4 二极管库:单击二极管库图标,弹出二极管库下拉菜单,如图3.4所示。

第3章VHDL及编程技巧

第3章VHDL及编程技巧§3.1 VHDL简介3.1.1 关于VHDL随着电子技术的发展,当前数字系缆的设计正朝着速度快,容量大、体积小,重量轻的方向发展。

推动该潮流迅猛发展的引擎就是日趋进步和完善的ASIC设计技术。

目前数字系统的设计可以直接面向用户需求,根据系统的行为和功能要求,自上而下地完成相应的描述、综合、优化、仿真与验证,直到系统生成。

上述设计过程除了系统行为和功能描述以外,其余所有的设计过程几乎都可以用计算机来自动地完成,也就是通常意义上的电子设计自动化(EDA)。

这样做可大大地缩短系统的设计周期,以适应当今品种多、批量小的电子市场的需求,提高产品的竞争能力。

电子设计自动化(EDA)的关键技术之一是要求用形式化方法来描述数字系统的硬件电路,即所谓的硬件描述语言(HDL—Hardware Description Language)。

可以说硬件描述语言及相关的仿真、综合等技术是当今电子设计自动化领域中工程师必备的工具。

硬件描述语言的发展至今已有几十年的历史,并已成功地应用到系统的仿真、验征和设计综合等方面。

上世纪80年代后期,已出现了上百种的硬件描述语言,它们对设计自动化起到了促进和推动作用。

但是它们大多各自针对特定设计领域,无统一的标准。

广大用户所期盼的是一种面向设计的多层次、多领域且得到一致认同的标准的硬件描述语言。

80年代后期由美国国防部开发的VHDL语言恰好满足了上述要求,并在1987年12月由IEEE 标准化(定为IEEEstd 1076--1987标准,1993年进一步修订,被定为ANSI/IEEEstd 1076--1993标准)。

它的出现为电子设计自动化(EDA)的普及和推广奠定了坚实的基础。

据1991年有关统计资料表明,VHDL语言已被广大设计者所接受并用来设计数字系统,尤其是欧洲地区的应用相当广泛。

另外众多的CAD厂商也纷纷使用新开发的电子设计软件与VHDL语言兼容。

《rfid原理及应用》第3章编码和调制

《RFID技术基础》

添加副标题

汇报人姓名

数据和信号

3 编码和调制

数字数据取离散值,为人们所熟悉的例子是文本或字符串。在射频识别应答器中存放的数据是数字数据 。

02

数据可定义为表意的实体,分为模拟数据和数字数据。模拟数据在某些时间间隔上取连续的值,例如,语音、温度、压力等。

01

*

数据和信号

3 编码和调制

*

3 编码和调制

脉冲调幅波

*

3 编码和调制

数字调制ASK方式的实现

国际标准ISO 14443的负载调制测试用的PICC电路

01

02

*

3 编码和调制

数字调制ASK方式的实现

国际标准ISO 14443的负载调制测试用的PICC电路

应答器谐振回路由线圈L和电容器CV1组成,其谐振电压经桥式整流器VD1~VD4整流,并用齐纳二极管VD5稳压在3 V左右。副载波信号(874 kHz)可通过跳线选择Cmod1或Rmod1进行负载调制。由曼彻斯特码或NRZ码进行ASK或BPSK副载波调制。

3 编码和调制

3 编码和调制

3 编码和调制

3 编码和调制

RFID中常用的编码方式及编解码器 密勒(Miller)码

密勒码编码规则

bit(i-1)

bit i

密勒码编码规则

×

1

bit i的起始位置不变化,中间位置跳变

0

0

bit i的起始位置跳变,中间位置不跳变

1

0

bit i的起始位置不跳变,中间位置不跳变

曼彻斯特(Manchester)码

02

*

3 编码和调制

电气控制与PLC应用技术课后习题答案(第三章)

习题与思考题1.PLC的定义是什么?答:可编程逻辑控制器(Programmable Logic Controller),简称PLC。

是一种专门在工业环境下应用而设计的数组运算操作的电子装置。

它采用可以编程的存储器,用来在其内部存储执行逻辑运算、顺序运算、计时、计数和算数运算等操作的指令,并能通过数字式或模拟式的输入输出,控制各种类型的机械或生产过程。

2.简述PLC的发展概况和发展趋势。

答:发展概况:20世纪60年代末,PLC生产于美国马萨诸塞州。

PLC崛起于20世纪70年代,首先在汽车流水线上大量应用。

20世纪90年代是PLC发展最快的时期,PLC在系统结构上,从单机向多CPU和分布式及远程控制系统发展;PLC在编程语言上,图形化和文本化语言的多样性,创造了更具表达控制要求、通信能力和文字处理的编程环境,PLC 在应用范围和水平上得到了全方位的提高。

20世纪90年代至今,PLC走进了一个开放性和标准化的时代。

发展趋势:PLC通信的网络化和无线化,开放性和编程软件标准化、平台化,体积小型化、模块化、集成化,运算速度高速化、性能更可靠,向超大型、超小型两个方向发展,软PLC的发展。

3.PLC有哪些主要功能?答:低档PLC具有逻辑运算、定时、计数、移位以及自诊断、监控等基本功能还有少量的模拟量输入输出、算数运算、数据传送和比较、通信等功能,主要用于逻辑控制、顺序控制或少量模拟量控制的单机系统。

中档PLC除了低档PLC的基本功能外,还具有较强的模拟量输入/输出、算数运算、数据传送和比较、数制转换、远程I/O、子程序、通信联网等功能,还可以增设中断控制、PID控制等功能,适用于复杂控制系统。

高档PLC除了具有中档PLC的功能外,还增加了带符号算数运算、矩阵运算、位逻辑运算、二次方根运算及其他特殊功能函数的运算、制表及表格传送功能。

高档PLC具有更强的通信联网功能,可用于大规模过程控制或构成分布式网络控制系统,实现工厂自动化。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

发

1 1 Qn 变反

器

4.3 主从触发器

4.3.1 主从J-K触发器

第 4.工作波形图 四 章

触 发 器 5。CAI演示

4.3 主从触发器

4.3.2 其他主从触发器

第

四 章

• • •

主从RS触发器 主从D触发器 主从T触发器

触 发 器

4.3 主从触发器

4.3.1 主从J-K触发器

第 6.小结

四 章

•

第 1。逻辑图 Q

四

章

&1

Q

&2

触

&3

&4

发

器

R

S

K

CP

J

T

4.2 钟控触发器(同步,电平,电位)

4.2.4 钟控T触发器

第 2、功能表 四 ① 当cp=0时,静态保持; 章 ② 当cp=1时,有:

T Qn+1 功 能

触

发

0 Qn

保持

器

1 Qn

变反

4.2 钟控触发器(同步,电平,电位)

4.2.4 钟控T触发器

4.1.3 基本R-S触发器

第 2、功能表

四 • 完整真值表 R S Qn Qn+1

章

00 0 ×

不确定

00 1 ×

01 0 0

置0

触

01 1 0

发 器

10 0 1

10 1

1

置1

11 0 0

保持

11 1 1

4.1 基本触发器

4.1.3 基本R-S触发器

第 2、功能表 四 • 简化真值表 章

R S Qn+1 功 能

四

Q

Q

章

Q

Q

&1

&2

触

发 器

&3

R

K

&4

S

CP

J

K

J

4.2 钟控触发器(同步,电平,电位)

4.2.3 J-K触发器

第 2、功能表 四 ① 当cp=0时,静态保持; 章 ② 当cp=1时,有:

J K Qn+1 功 能

触 发 器

0 0 Qn 动态保持 0 1 0 置0 1 0 1 置1 1 1 Qn 变反

触

Qn+1 RS 00

Qn

00

01 11 10

1× 0

发

11 1× 0

器

4.2 钟控触发器(同步,电平,电位)

4.2.1 钟控R-S触发器

第 四 章

3、次态卡诺图与次态方程 • 次态方程 ① 当cp=0时,

Qn+1 = Qn

② 当cp=1时,有:

触

发

Qn+1 = S + R ⋅Qn

器

S ⋅R = 0

现象;

触 • 其次仍存在不定状态,即使用时,需要约

发 器

束条件,为了解决不定状态,采用让两路 数据成为互补的数据。

4.2 钟控触发器(同步,电平,电位)

4.2.2 钟控D触发器

第 1、逻辑电路图和符号

四

Q

Q

章

&1

&2

触

发

&3

&4

器

R

CP

S

1

D

4.2 钟控触发器(同步,电平,电位)

4.2.2 钟控D触发器

章

• 解:将T端恒接高电平

触 发 器

4.3 主从触发器

4.3.1 主从J-K触发器

第 1.逻辑结构

四 章

• 由两个钟控RS触发器组成:其中与输入 相连的RS触发器叫主触发器,与输出相

连的钟控RS触发器叫从触发器。

触 发

• Q反馈到J输入端,Q反馈到K输入端。

器 • 加到两个触发器的时钟CP是反相的。

附加

R +S =1

条件

4.1 基本触发器

4.1.3 基本R-S触发器

第 4、时序图 四 • 不含不确定状态的时序图 章 • 含有不确定状态的时序图

5、总结

触 • 优点:结构简单 发 • 缺点:存在不确定状态,抗干扰能力不强 器

4.2 钟控触发器(同步,电平,电位)

4.2.1 钟控R-S触发器

第

四 • 在基本R-S触发器基础上增加一个时钟

发

11 1

器

3.CAI演示

4.4 边沿触发器

4.4.1 维持阻塞边沿D触发器

第 四

4。波形图 已知边沿D触发器(正边沿翻转)的时钟信号和输 入信号如图所示,试画出Q=0。

CP

1

2

3

4

0

触

D

t

发

0

器

t

0 t

4.4 边沿触发器

4.4.2 边沿J-K触发器

第 四

• 主从JK触发器存在“一次变化现象”, 抗干扰能力较差。

四

章 • 将主从JK触发器中存储一位数据的过程由

两步到位变成一步到位:即在时钟信号下

降时才对输入信号作出响应并引起状态翻

触

转,而与此刻以前、以后的输入信号无 关,从而大大提高了抗干扰能力。

第 四 章

第四章 触 发 器

触 发 器

目录

4.1 基本触发器 4.2 钟控触发器 4.3 主从触发器 4.4 边沿触发器

4.1 基本触发器

第

四

Q

章

&

1

触

发

器

R

Q

&

2

S

4.1 基本触发器

第 • 双稳触发器通常简称触发器,它是由门

四

电路构成的逻辑电路,它的输出具有两个

章

稳定的物理状态(高电平和低电平),它 能记忆一位二进制代码。

第 2、功能表 四 ① 当cp=0时,静态保持; 章 ② 当cp=1时,有:

D Qn+1 功 能

触

发

00

置0

器

11

置1

4.2 钟控触发器(同步,电平,电位)

4.2.2 钟控D触发器

第 3、次态卡诺图与次态方程 四 • 次态卡诺图 章

触

Qn+1 D 01

Qn

00 1

发

10 1

器

4.2 钟控触发器(同步,电平,电位)

第 2、功能表 四 ① 当cp=0时,静态保持; 章 ② 当cp=1时,有:

R S Qn+1 功 能

触 发 器

0 0 Qn 动态保持 0 1 1 置1 1 0 0 置0 1 1 × 不确定

4.2 钟控触发器(同步,电平,电位)

4.2.1 钟控R-S触发器

第 3、次态卡诺图与次态方程 四 • 次态卡诺图 章

从触发器状态不变;

触 发

• 在CP时钟下降时,将主触发器的状态传送 给从触发器;而在CP=0期间,主触发器 不接收数据(CP=0,输入门封死),从触

器

发器保持状态不变。

4.3 主从触发器

4.3.1 主从J-K触发器

第 3.功能分析

四

章

J K Qn+1 功 能

0 0 Qn 保持

0 1 0 置0

触

1 0 1 置1

4.2 钟控触发器(同步,电平,电位)

4.2.1 钟控R-S触发器

第 四

4、激励表

• 由已知的Qn+1和Qn的值确定输入端取值的关 系表,叫触发器的激励表。

章 • 是真值表的变形,由特征方程和约束条件决定。

触 发

Qn Qn+1 00 01

RS

×0 01

器

1 0 10

1 1 0×

4.2 钟控触发器(同步,电平,电位)

4.2.4 钟控T触发器

4、激励表

第

四

章

Qn Qn+1 T

00

0

01

1

触

10

1

发

11

0

器

4.2 钟控触发器(同步,电平,电位)

4.2.4 钟控T触发器

第 5、状态图和状态表

四

章

现态

次态Qn+1

Q

T=0

T=1

触

0

0

1

发

1

1

0

器

4.2 钟控触发器(同步,电平,电位)

4.2.4 钟控T触发器

第 四

6、应用 • 用钟控T触发器构成一位计数器。

4.3 主从触发器

4.3.1 主从J-K触发器

第 1.逻辑结构(P96)

四

章

J

& G7

& Q'

G5

& G3

& G1

Q

触

K

& G8

& Q' G6

& G4

& G2

Q

发

1

器

CP

G9

.

7

4.3 主从触发器

4.3.1 主从J-K触发器

第 2.工作原理

四 章

主从JK触发器的工作分两步完成:

• 在CP=1期间,主触发器接收输入信号,

章

控制端,即CP端。

• 优势:

触 ① 提高触发器的抗干扰能力

发 ② 多个触发器能够在同一个控制信号的作用下同

器

步工作

2

4.2 钟控触发器(同步,电平,电位)

4.2.1 钟控R-S触发器

第 1、逻辑电路图和符号

四

Q

Q

章

&1

&2

触

发 器

&3

R

&4