多功能数字钟的设计与实现

多功能数字钟的设计及制作

目录摘要 (1)1数字钟的结构设计及方案选择 (1)1.1振荡器的选择 (1)1.2计数单元的构成及选择 (2)1.3译码显示单元的构成选择 (2)1.4校时单元电路设计及选择 (2)2 数字钟单元电路的设计 (2)2.1振荡器电路设计 (2)2.2时间计数单元设计 (3)错误!未定义书签。

2.2.2 用74LS390构成秒和分计数器电路 (3)错误!未定义书签。

2.2.4 时间计数单元总电路 (3)2.3译码显示单元电路设计 (4)2.4 校时单元电路设计 (4)2.5整点报时单元电路设计 (1)3 数字钟的实现电路及其工作原理 (4)4电路的搭建与调试 (4)5结束语 (5)参考文献.................................................................... 错误!未定义书签。

附录1:.. (5)摘要数字钟被广泛用于个人家庭及公共场所,成为人们日常生活中的必需品。

诸如定时自动报警、按时自动打铃、定时广播、自动起闭路灯、定时开关烘箱、甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。

因此,研究数字钟及扩大其应用,有着非常现实的意。

数字电子钟,从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

数字电子钟有以下几部分组成:振荡器,分频器,60进制的秒、分计时器和12进制计时计数器,秒、分、时的译码显示部分及校正电路等。

关键词:数字钟 555多谐振荡器计数器 74LS390 74LS48数字电子时钟的设计及制作1数字钟的结构设计及方案选择数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。

主要由振荡器、分频器、计数器、译码器显示器和校时电路组成。

振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,通常使用石英晶体震荡器,然后经过分频器输出标准秒脉冲,或者由555构成的多谐振荡器来直接产生1HZ的脉冲信号。

多功能数字钟-电子设计

多功能数字钟-电子设计

第一步实现多功能数字钟的基本功能,包括显示当前时间和设置定时

功能。

为了实现这一功能,我们需要使用一个定时器,以实现每秒钟更新

一次时间并显示在LCD屏上,同时实现定时功能。

第二步用一个按钮来切换显示当前时间和定时时间。

为了实现这一功能,我们需要在LCD屏上显示当前时间和定时时间,当按钮按下时,可以

改变当前时间和定时时间的显示。

第三步加入计时功能,使用者可以设置一个计时时间,当计时结束时,会有一个提醒和发出报警声。

为了实现这一功能,我们需要使用一个计数器,计算出时间差,当到达设定的计时时间时,发出报警声或者显示一个

提醒。

第四步增加闹钟功能,使用者可以设置一个闹钟时间,当达到闹钟时

间时,会有一个提醒和发出报警声。

为了实现这一功能,我们需要在指定

的时间段内,获取当前时间,通过一个实时检查程序,来实现闹钟功能,

当到达时间时,发出报警声或者显示一个提醒。

第五步加入天气预报功能,使用者可以查询当前城市的天气情况,以

及未来三天的天气预报。

为了实现这一功能,我们需要使用一个API来获

取天气情况,并将获取的信息在LCD屏上显示出来,方便使用者查询。

多功能数字钟的设计与实现项目设计方案

多功能数字钟的设计与实现项目设计方案1 数字钟设计功能及方案论证基本功能:1)设计一个数字钟。

要求用六位数码管显示时间,格式为00:00:00。

2)具有60进制和24进制(或12进制)计数功能,秒、分为60进制计数,时为24进制(或12进制)计数。

3)有译码、七段数码显示功能,能显示时、分、秒计时的结果。

扩展功能:1)设计提供连续触发脉冲的脉冲信号发生器,2)具有校时单元、闹钟单元和整点报时单元。

方案论证:方案一:用逻辑门电路直接搭接数字钟电路,此方案所需元件众多,频率稳定性差,电路复杂,所以不采用此方案。

方案二:用计数器74LS90以及译码器74LS48等芯片组成电路,用555振荡器及分频器产生1Hz信号供计数器技术,较之第一种方案容易实现。

方案三:用单片机实现计数及显示等,这种方案简单明了,电路简单只需要写好程序就可以,容易达到任务要求。

但单片机对个人能力要求较高,鉴于还没有学习单片机方面知识,所以不使用第三种方案。

综上,决定采用第二种方案。

2 设计原理及框图1)计数器电路:计数器电路由秒计数器、分计数器及时计数器构成。

根据设计要求,其中,时计数器为24进制,分计数器及秒计数器为60进制计数器。

2)译码显示电路:由74LS48芯片组成的译码电路将计数器输出的8421BCD码转化为数码管所需的逻辑状态,并为保证数码管正常工作提供足够工作电流。

3)整点报时电路:在数字钟电路出现整点时,数字钟会自动报时,其工作方式是发出连续的音频声波,复杂一些的可以是实时语音或音乐提示。

4)定时闹钟电路:要求可以设定一个指定的时间,是数字钟在指定时刻发出信号,使蜂鸣器“闹时”。

5)555振荡器电路:石英晶体振荡器电路给数字钟提供一个频率稳定的32768Hz的方波信号,可保证数字钟的走时准确及稳定。

6)分频器电路:分频器电路将32768HZ的高频方波信号经分频后得到1Hz的方波信号供秒计数器进行计数。

数字钟原理框图如下:图1.1 数字钟原理框图3 电路模块分析3.1计数器电路计数器电路我选择的是74LS90芯片。

数电课程设计多功能数字钟的设计与实现

课程设计任务书题目: 多功能数字钟的设计与实现初始条件:本设计既可以使用集成译码器、计数器、定时器、脉冲发生器和必要的门电路等,也可以使用单片机系统构建多功能数字钟。

用数码管显示时间计数值。

要求完成的主要任务: (包括课程设计工作量及技术要求,以及说明书撰写等具体要求)1、课程设计工作量:1周。

2、技术要求:1)设计一个数字钟。

要求用六位数码管显示时间,格式为00:00:00。

2)具有60进制和24进制(或12进制)计数功能,秒、分为60进制计数,时为24进制(或12进制)计数。

3)有译码、七段数码显示功能,能显示时、分、秒计时的结果。

4)设计提供连续触发脉冲的脉冲信号发生器,5)具有校时单元、闹钟单元和整点报时单元。

6)确定设计方案,按功能模块的划分选择元、器件和中小规模集成电路,设计分电路,画出总体电路原理图,阐述基本原理。

3、查阅至少5篇参考文献。

按《******大学课程设计工作规》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规。

时间安排:1、 2013年 3 月 18 日,布置课设具体实施计划与课程设计报告格式的要求说明。

2、 2013 年 3 月 22日至 2013 年 5 月 10 日,方案选择和电路设计。

3、 2013 年 5 月 25 日至 2013 年 7 月 2 日,电路调试和设计说明书撰写。

4、 2013 年 7 月 5 日,上交课程设计成果及报告,同时进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录1 引言 (1)1.1 数字钟简介 (1)1.2 EWB简介 (1)2 方案选择 (3)3 系统框图 (4)4 分电路设计 (5)4.1 脉冲产生电路 (5)4.1.1设计要求 (5)4.1.2所需元件 (5)4.1.3元件介绍 (5)4.1.4参数计算 (6)4.1.5电路设计 (7)4.2计数电路 (8)4.2.1秒电路 (8)4.2.2分电路 (9)4.2.3时电路 (11)4.3显示电路 (12)4.3.1所需元件 (12)4.3.2元件介绍 (12)4.3.3原理说明 (12)4.3.4电路设计 (12)4.4整点报时电路 (13)4.4.1设计要求 (13)4.4.2所需元件 (13)4.4.3元件介绍 (13)4.4.4参数计算 (13)4.4.5原理说明 (14)4.4.6电路设计 (14)4.5校时电路 (15)4.5.1设计要求 (15)4.5.2所需元件 (15)4.5.3元件介绍 (15)4.5.4原理说明 (15)4.5.5电路设计 (15)4.6闹钟电路 (16)4.6.1设计要求 (16)4.6.2所需元件 (16)4.6.3元件介绍 (16)4.6.4原理说明 (18)4.6.5电路设计 (18)5总电路图 (19)6心得体会 (20)7元件清单 (21)8参考文献 (23)摘要数字钟是一种用数字电路技术实现时、分、秒计时的钟表。

多功能数字钟的设计

实验题目:多功能数字钟的设计实验目的:1.了解数字钟的工作原理。

2.进一步熟悉用VHDL语言编写驱动七段码管显示的代码3.掌握VHDL编写中的一些小技巧实验原理:多功能数字钟应该具有的功能有:显示时-分-秒、整点报时、小时和分钟可调等基本功能。

首先要知道钟表的工作机理,整个钟表的工作应该是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加1秒,当秒从59秒跳转到00秒时,分钟增加1分,同时当分钟从59分跳转到00分时,小时增加1小时,但是需要注意的是,小时的范围是从0~23时。

在实验中为了显示的方便,由于分钟和秒钟显示的范围都是从0~59,所以可以用一个3位的二进制码显示十位,用一个四位的二进制码(BCD码)显示个位,对于小时因为它的范围是从0~23,所以可以用一个2位的二进制码显示十位,用4位二进制码(BCD码)显示个位。

本结构用到4个分频模块分别分出1Khz ,2 Hz ,1Hz ,0.5Hz 的信号。

其中1hz的信号用于计数器计数,2hz的时钟用于LED的点亮,0.5hz与1Khz的时钟用于生存蜂鸣器所需要的工作信号。

时钟的每一个部分分别用两个十进制计数器模块计数器的输出作为显示模块display的输入按键消抖模块key输入高频的工作时钟和有抖动的按键信号,输出一个没有抖动的按键信号KEYOUT蜂鸣器控制部分通过计数器的低14位输出对接入蜂鸣器的信号进行控制LED灯控制部分通过计数器低14的输出对4个灯进行控制分频部分freq_div.vhdlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity freq_div isport(CLK : in std_logic;CLKOUT : out std_logic;NUM : in integer );end;architecture one of freq_div issignal out_pos : std_logic := '0';signal out_neg : std_logic := '0';signal out_even : std_logic := '0';beginprocess(CLK)variable num_pos : integer := 0;beginif CLK'event and CLK = '1' thennum_pos := num_pos + 1;if num_pos = NUM thennum_pos := 0;end if;if num_pos <= NUM/2 thenout_pos <= '0';elseout_pos <= '1';end if;end if;end process;process(CLK )variable num_neg : integer := 0;beginif CLK'event and CLK = '0' thennum_neg := num_neg + 1;if num_neg = NUM thennum_neg := 0;end if;if num_neg <= NUM / 2 thenout_neg <= '0';elseout_neg <= '1';end if;end if;end process;process(CLK)variable cnt : integer := 0;beginif CLK'event and CLK = '1' thencnt := cnt + 1;if cnt = NUM /2 thenout_even <= not out_even;cnt := 0;end if;end if;end process;process(out_even,out_pos,out_neg,NUM)beginif NUM rem 2 = 0 thenCLKOUT <= out_even;elseCLKOUT <= out_pos or out_neg;end if;end process;end;Freq_div.vhd仿真结果如下按键消抖部分key.vhdlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity key isport(CLK : in std_logic;KEYIN : in std_logic;KEYOUT : out std_logic);end;architecture test of key istype states is(s0 , s1 , s2 , s3);signal cs , n_state : states := s0;beginprocess(CLK ,cs , KEYIN)variable cnt : integer range 0 to 1000;beginif CLK'event and CLK = '1' thenif cs = s1 or cs = s3 thencnt := cnt + 1;end if;case cs iswhen s0 =>if KEYIN = '0' thencs <= s1;end if;when s1 =>if cnt = 1000 thencs <= s2;cnt := 0;end if;when s2 =>if KEYIN = '1' thencs <= s3;end if;when s3 =>if cnt = 1000 thencs <= s0;cnt := 0;end if;end case;end if;end process;process(cs)beginif cs = s0 thenKEYOUT <= '1';elseKEYOUT <= '0';end if;end process;end;Key.Vhd仿真如下:数码管显示部分display.vhdlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity display isport(CLK : in std_logic;ledag : out std_logic_vector(6 downto 0);del : out std_logic_vector(2 downto 0);NUM : in std_logic_vector(19 downto 0) :="10001110110011011001");end;architecture exp of display isbeginprocess(CLK)variable cnt : std_logic_vector(2 downto 0);--variable NUM : std_logic_vector(19 downto 0) := "10001110110011011001";type LED_MATRIX is array( 0 to 9) of std_logic_vector(6 downto 0);variable table : LED_MATRIX := ( "0111111", --0 0x3f"0000110", --1 0x06"1011011", --2 0x5b"1001111", --3 0x4f"1100110", --4 0x66"1101101", --5 0x6d"1111101", --6 0x7d"0000111", --7 0x07"1111111", --8 0x7f"1101111" --9 0x6f);beginif CLK'event and CLK = '1' thencnt := cnt + 1;del <= cnt;case cnt iswhen "000" => ledag <= table( conv_integer( NUM(19 downto 18) ) );when "001" => ledag <= table( conv_integer( NUM(17 downto 14) ) );when "010" => ledag <= "1000000";when "011" => ledag <= table( conv_integer( NUM(13 downto 11) ) );when "100" => ledag <= table( conv_integer( NUM(10 downto 7) ) );when "101" => ledag <= "1000000";when "110" => ledag <= table( conv_integer( NUM(6 downto 4) ) );when "111" => ledag <= table( conv_integer( NUM(3 downto 0) ) );end case;end if;end process;end;dispaly.vhd仿真结果如下10进制计数器cnt10.vhdllibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity cnt10 isport(CLK : in std_logic;RST : in std_logic;EN : in std_logic;OV : out std_logic;NUM : out std_logic_vector(3 downto 0));end;architecture exp of cnt10 isbeginprocess(CLK,RST)variable cnt : std_logic_vector(3 downto 0);beginif RST = '1' thencnt := "0000";elsif CLK'event and CLK = '1' thenif EN = '1' thenif cnt < 9 thencnt := cnt + 1;OV <= '0';elsecnt := "0000";OV <= '1';end if;end if;end if;NUM <= cnt;end process;end;Cnt10.vhd仿真结果如下二极管控制部分led.vhdlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity led isport(CLK : in std_logic;LED_OUT : out std_logic_vector(3 downto 0);NUM : in std_logic_vector(13 downto 0));end;architecture test of led issignal LED_EN : std_logic;beginprocess(NUM)beginif NUM(13 downto 4) = "1011001101" and NUM(3 downto 0) > 4 then LED_EN <= '1';elseLED_EN <= '0';end if;end process;process(LED_EN,CLK)beginif LED_EN = '1' thenLED_OUT <= CLK & CLK & CLK & CLK;elseLED_OUT <= (others => '0');end if;end process;end;led.vhd仿真结果如下蜂鸣器部分beep.vhdlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity beep isport(CLK : in std_logic;BEEP_OUT : out std_logic;NUM : in std_logic_vector(13 downto 0));end;architecture test of beep issignal EN : std_logic;beginprocess(NUM)beginif NUM(13 downto 4) = "1011001101" and NUM(3 downto 0) >= 0 then EN <= '1';elseEN <= '0';end if;end process;process(EN ,CLK)beginif EN = '1' thenBEEP_OUT <= CLK;elseBEEP_OUT <= '0';end if;end process;end;顶层设计clock.vhdlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity clock isport(CLK : in std_logic;RESET : in std_logic;S1 : in std_logic;S2 : in std_logic;SPK : out std_logic;LEDOUT : out std_logic_vector(3 downto 0);ledag : out std_logic_vector(6 downto 0);del : out std_logic_vector(2 downto 0) );end;architecture exp of clock iscomponent freq_div isport(CLK : in std_logic;CLKOUT : out std_logic;NUM : in integer);end component;component cnt10 isport(CLK : in std_logic;RST : in std_logic;EN : in std_logic;OV : out std_logic;NUM : out std_logic_vector(3 downto 0) );end component;component display isport(CLK : in std_logic;ledag : out std_logic_vector(6 downto 0);del : out std_logic_vector(2 downto 0);NUM : in std_logic_vector(19 downto 0) );end component;component key isport(CLK : in std_logic;KEYIN : in std_logic;KEYOUT : out std_logic);end component;component led isport(CLK : in std_logic;LED_OUT : out std_logic_vector(3 downto 0);NUM : in std_logic_vector(13 downto 0) );end component;component beep isport(CLK : in std_logic;BEEP_OUT : out std_logic;NUM : in std_logic_vector(13 downto 0) );end component;signal CLK1K : std_logic;signal CLK1 : std_logic;signal CLK2 : std_logic;signal CLK0_5 : std_logic;signal RST : std_logic;signal EN : std_logic;signal OV_h : std_logic_vector(1 downto 0);signal OV_m : std_logic_vector(1 downto 0);signal OV_s : std_logic_vector(1 downto 0);signal COUNT : std_logic_vector(23 downto 0) := "00110010" & "10000101" & "00000101"; signal NUM : std_logic_vector(19 downto 0);signal CLK_s : std_logic;signal CLK_m : std_logic;signal CLK_h : std_logic;signal KEY_h : std_logic;signal KEY_m : std_logic;beginu_freq_1K : freq_div port map( CLK , CLK1K , 10);u_freq_1 : freq_div port map( CLK1K , CLK2 , 500 );u_freq_2 : freq_div port map( CLK2 , CLK1 , 2 );u_freq_3 : freq_div port map( CLK1 , CLK0_5 , 2);u_cnt_h2 : cnt10 port map( CLK_m or (not KEY_h), CLK_h or RST , EN ,OV_h(0) , COUNT(23 downto 20) );u_cnt_h1 : cnt10 port map( OV_h(0), CLK_h or RST , EN , OV_h(1) ,COUNT(19 downto 16) );u_cnt_m2 : cnt10 port map( CLK_s or (not KEY_m), RST , EN , OV_m(0) ,COUNT(15 downto 12));u_cnt_m1 : cnt10 port map( OV_m(0) , CLK_m or RST, EN , OV_m(1) ,COUNT(11 downto 8));u_cnt_s2 : cnt10 port map( CLK1 , RST , EN , OV_s(0) , COUNT(7 downto 4)); -- u_cnt_s1 : cnt10 port map( OV_s(0) , RST , EN , OV_s(1) , COUNT(3 downto 0) );u_cnt_s1 : cnt10 port map( OV_s(0) , CLK_s or RST , EN , OV_s(1) ,COUNT(3 downto 0) );u_dsplay : display port map( CLK , ledag , del , NUM );u_key_h : key port map( CLK , S1 , KEY_h );u_key_m : key port map( CLK , S2 , KEY_m );u_led : led port map( CLK2 , LEDOUT , NUM(13 downto 0));u_beep : beep port map( CLK0_5 and CLK1K , SPK , NUM(13 downto 0));CLK_s <= NUM(6) and NUM(5) and (not NUM(4));CLK_m <= NUM(13) and NUM(12) and (not NUM(11));CLK_h <= not ((not NUM(19)) or NUM(18) or NUM(17) or (not NUM(16)) or NUM(15) or NUM(14) );NUM(19 downto 18) <= COUNT(17 downto 16);NUM(17 downto 14) <= COUNT(23 downto 20);NUM(13 downto 11) <= COUNT(10 downto 8 );NUM(10 downto 7) <= COUNT(15 downto 12);NUM(6 downto 4) <= COUNT(2 downto 0);NUM(3 downto 0) <= COUNT(7 downto 4);EN <= '1';RST <= not RESET;end;。

多功能数字钟的设计与制作

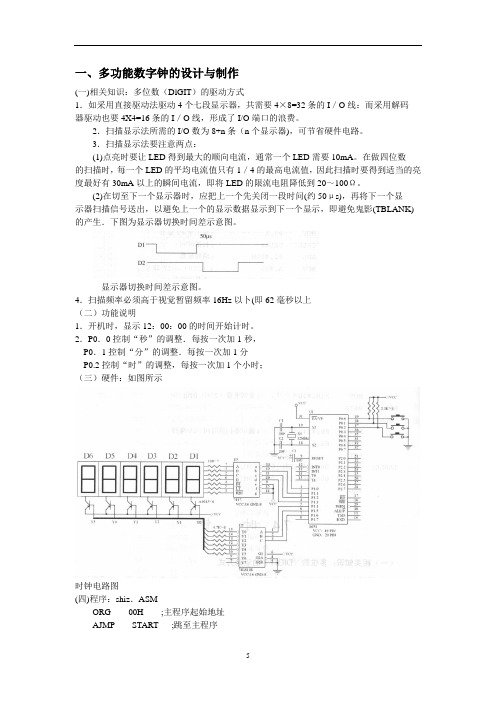

一、多功能数字钟的设计与制作(一)相关知识:多位数(DlGIT)的驱动方式1.如采用直接驱动法驱动4个七段显示器,共需要4×8=32条的I/O线:而采用解码器驱动也要4X4=16条的I/O线,形成了I/O端口的浪费。

2.扫描显示法所需的I/O数为8+n条(n个显示器),可节省硬件电路。

3.扫描显示法要注意两点:(1)点亮时要让LED得到最大的顺向电流,通常一个LED需要10mA。

在做四位数的扫描时,每一个LED的平均电流值只有1/4的最高电流值,因此扫描时要得到适当的亮度最好有30mA以上的瞬间电流,即将LED的限流电阻降低到20~100Ω。

(2)在切至下一个显示器时,应把上一个先关闭一段时问(约50μs),再将下一个显示器扫描信号送出,以避免上一个的显示数据显示到下一个显示,即避免鬼影(TBLANK) 的产生.下图为显示器切换时间差示意图。

显示器切换时间差示意图。

4.扫描频率必须高于视觉暂留频率16Hz以卜(即62毫秒以上(二)功能说明1.开机时,显示12:00:00的时间开始计时。

2.P0.0控制“秒”的调整.每按一次加1秒,P0.1控制“分”的调整.每按一次加1分P0.2控制“时”的调整,每按一次加1个小时;(三)硬件:如图所示时钟电路图(四)程序:shiz.ASMORG 00H ;主程序起始地址AJMP START ;跳至主程序ORG 0BH ;TIMER0中断起始地址AJMP TIM0 ;跳至TIMER0中断子程序TIM0START:MOV SP,#70H ;设置堆栈在70HMOV 28H,#00 ;显示寄存器初值为0 0MOV 2AH,#12H ;“时”寄存器l忉值为12HMOV 2BH,#00 ;“分”寄存器初值为0 0HMOV 2CH,#00 :“秒”寄存器初值为00HMOV TMOD,#00000001B :设TIMER0为MODElMOV TH0,#HIGH(65536—4000) ;计时中断为4000微秒MOV TL0,#LOW(6553 6—4000)MOV IE,#10000010B ;TIMER0中断使能MOV R4,#250 ;中断250次SETB TR0 j启动TIMER0LOOP:JB P0.0,N2 ;PO.O (秒)按了?不是则跳至N2检查PO.1 ACALL DELAY ;消除抖动MOV A,2CH ;将秒寄存器的值载入AADD A,#01 ;A的内容加1DA A ;做十进位调整MOV 2CH,A ;将A的值存入秒寄存器CJNE A,#60H,N1 ;是否等于60秒?不是则跳至N1MOV 2CH,#00 ;是则清除秒寄存器的值为00N1:JNB P0.0,$ ;P0.0(秒)放开了?ACALL DELAY ;消除抖动N2:JB P0.1,N4 ;p0.1 (分)按下了吗?不是则跳至N4检查P0.2 ACALL DELAY ;消除抖动MOV A,2BH ;将分寄存器的值载入AADD A,#01 ;A的内容加1DA A ;做十进位调整MOV 2BH.A ;将A的值存入分寄存器CJNE A,#60H,N3 ;是否等于60分?不是则跳至N1MOV 2BH.#00 ;是则清除分寄存器的值为00N3:JNB P0.1,$ ;p0.1 (秒)放开了?CALL DELAY ;消除抖动N4:JB P0.2,LOOP ;P0.2 1秒)按下了吗?不足则跳至LOOP CALL DELAY ;消除抖动MOV A,2AH ;将时寄存器的值载入AADD A.#01 :A的内容加1DA A ;做十进位调整MOv 2AH,A ;将A的值存入时寄存器CJNE A,#24H,N5 ;是否等于24时?不是则跳至N5MOV 2AH,#00 ;是则清除时寄存器的值为00N5:JNB P0.2,$ ;P0.2(秒)放开了?CALL DELAY :消除抖动JMP LOOPTIM0:MOV TH0,#HIGH(6 553 6—4000) ;重设计时4 000微秒NOV TL0,#LOW(6553 6—4 000)PUSH ACC :将A的值暂存于堆栈PUSH PSW ;将PSW的值暂存于堆栈DJNZ R4 X2 :计时1秒MOV R4,#250CALL CLOCK ;调用计时子程序CLOCKCALL DISP :调用显示子程序X2:CALL SCAN ;调用扫描子程序POP PSW ;至堆栈取叫PSW的值POP ACC :至堆栈取回ACC的值SCAN:MOV R0,#28H ;(28H)为扫描指针INC @R0 ;扫描指针加lCJHE @R0.#6,X3 ;扫描完6个显示器?不是跳至X3MOV @R0,#0 ;是则扫描指针为0x3: MOV A,@R0 ;扫描指针载入AADD A,#20H ;A加常数20H(显示寄存器地址)=各时间;显示区地址;存入R1=各时间显示地址MOV R1,A ;扫描指针存入AMOV A,@R0 ;将A高低4位交换(P1高4位为扫描值,SW AP A ;低4位为显示数据值)ORL A,@R1 ;扫描值+显示值MOV P1,A ;输出至P1RETCLOCK:MOV A,2CH ;(2CH)为秒寄存器ADD A,#l ;加1秒DA A ;做十进制调整MOV 2CH,A ;存入秒寄存器CJNE A,#60H,X4 ;是否超过60秒?不是则跳至X4MOV 2CH,#00 ;是则清除为00MOV A,2BH ;(2BH)为分寄存器ADD A,#l ;加1分DA A ;做十进制调整MOV 2BH,A ;存入分寄存器CJNE A,#60H.X4 ;是否超过60分?不是则跳至X4MOV 2BH,#00 ;是则清除为0 0MOV A,2AH 7(2AH)为时寄存器ADD A,#l ;加l时DA A ;做十进制调整MOV 2AH,A ;存入时寄存器CJNE A,#24H,X4 ;是否超过24时?不是则跳至x4MOV 2AH.#00 ;是则清除为00X4:RETDISP:MOV R1,#20H ;(20H)为显示寄存器.R1=20HMOV A,2CH ;将秒寄存器的内容存入AMOV B,#10H ;设B累加器的值为10HDIV AB ;A÷B,商(十位数)存入A.余数(个位数) ;存入BNOV @R1,B :将B的内容仔入(20H)INC R1 ;RI=21HMOV @R1,A ;将A的内容存入(21H)INC R1 ;R1=22HNOV A,2BH ;将分寄存器的内容仃入ANOV B,#10H ;设B累加器的值为10DIV AB ;A÷B,商(十位数)存入A,余数(个位数);存入BMOV @R1,B ;将B的内容存入(22H)INC Rl ;R1= 23HNOV @R1,A ;将A的内容存入(23H)INC R1 ;R1=24HMOV A,2AH ;将时寄存器的内容存入AMOV B,#10H ;设B累加器的值为10HDIV AB ;A÷B,商(十位数)存入A.余数(个位数) ;存入BM0v @R1,B ;将B的内容存入(24H)INC R1 ;R1=25HMOV @R1,A ;将A的内容存入(25H)RETDELAY:MOV R6,#60 ;5毫秒D1:MOV R7,#248DJNZ R7,$DJNZ R6,D1RETEND。

电子综合设计多功能数字钟报告

电子综合设计多功能数字钟报告报告内容如下:一、设计目的和原理多功能数字钟是一种能够显示时间,并具有闹钟、计时、倒计时等功能的电子设备。

本设计的目的是通过FPGA实现一个多功能数字钟的功能,以实现时间的显示和闹钟的设置功能。

二、设计方案和实现1.硬件设计方案:本设计使用FPGA作为主控芯片,使用七段数码管作为显示器,通过与FPGA的IO口连接来实现时间的显示功能。

同时,使用按键作为输入进行功能的选择和设置。

2.硬件连接:将FPGA的IO口连接到七段数码管的控制端,通过IO口输出相应的数字信号来控制数码管的亮灭。

将按键连接到FPGA的IO口,通过IO口输入按键的信号。

此外,还需要连接一个晶振电路来提供时钟信号。

3.软件设计方案:本设计使用VHDL语言进行程序设计,通过状态机来实现多功能数字钟的功能。

具体实现包括时间的显示、闹钟的设置和启动、计时和倒计时功能的实现。

通过按键的输入来切换不同的状态,实现不同功能的切换和设置。

4.软件实现具体步骤:(1)定义状态机的状态,包括时间显示、闹钟设置、计时和倒计时等状态。

(2)在时间显示状态下,通过FPGA的IO口输出相应的数字信号来控制七段数码管的亮灭,实现时间的显示。

(3)在闹钟设置状态下,通过按键的输入来设置闹钟时间,并将设置好的时间保存在寄存器中。

(4)在计时和倒计时状态下,通过按键的输入来实现计时和倒计时功能,并通过七段数码管的显示来实时显示计时和倒计时的时间。

以下为本设计的完整程序代码:```vhdl--时钟频率--定义状态signal state : state_type;--定义时钟、按键和数码管信号signal clk : std_logic;signal key : std_logic_vector(1 downto 0);signal seg : std_logic_vector(6 downto 0);--闹钟时间寄存器signal alarm_hour_reg : std_logic_vector(5 downto 0);signal alarm_min_reg : std_logic_vector(5 downto 0);--计时和倒计时寄存器signal count_up_reg : std_logic_vector(23 downto 0); signal count_down_reg : std_logic_vector(23 downto 0); signal count_down_flag : std_logic := '0';beginclock : processbeginwhile true loopclk <= '0';wait for 10 ns;clk <= '1';wait for 10 ns;end loop;end process;key_scan : process(clk)beginif rising_edge(clk) thenkey <= key_scan_func; -- 按键扫描函数end if;end process;fsm : process(clk, key)beginif rising_edge(clk) thencase state isif key = "10" then -- 第一个按键按下state <= set_alarm;elsif key = "01" then -- 第二个按键按下state <= count_up;end if;when set_alarm =>seg <= set_alarm_func; -- 闹钟设置函数if key = "00" then -- 两个按键同时按下elsif key = "01" then -- 第一个按键按下state <= count_up;end if;when count_up =>seg <= count_up_func; -- 计时函数if key = "00" then -- 两个按键同时按下elsif key = "10" then -- 第二个按键按下state <= count_down;count_down_flag <= '1';end if;when count_down =>seg <= count_down_func; -- 倒计时函数if key = "00" then -- 两个按键同时按下count_down_flag <= '0';elsif key = "01" then -- 第一个按键按下state <= count_up;count_down_flag <= '0';end if;end case;end if;end process;--数码管信号和显示模块的连接display : entity work.seg_displayport mapclk => clk,seg => segend architecture;```四、总结与展望通过FPGA实现多功能数字钟的设计,在硬件和软件的配合下,实现了时间的显示和闹钟的设置功能。

多功能数字时钟的设计与制作

目录摘要 (1)引言 (2)一、方案选择 (4)(一)何谓单片机 (4)(二)单片机的选择 (4)(三)设计方案论证 (6)(四)具有整点报时和定时闹钟功能的设计 (7)二、硬件设计 (12)(一)最小系统设计 (12)(二)数字钟的外围电路设计 (13)(三)数字时钟设计方案 (18)图2-10 电路原理图 (18)(四)单元电路设计及分析 (18)三、软件设计 (22)(一)系统流程图: (22)(二)设备与仪器 (23)(三)系统调试与分析 (24)(四)分析结果 (25)总结 (27)致谢 (27)参考文献 (29)本系统的设计电路以凌阳单片机SPCE061A作为控制器。

主要由显示电路, 功能控制电路、传感器电路、电压转换电路、遥控电路五部分。

吸收了硬件软件化的思想,大部分功能通过软件来实现,使电路简单明了,系统稳定性大大提高。

本系统不仅成功的实现了要求的基本功能,发挥部分也得到完全的实现,而且有一定的创新功能。

通过多功能数字钟的设计思路,详细叙述了系统硬件、软件的具体实现过程。

论文重点阐述了数字钟硬件中MCU模块、语音模块、时钟模块和相关控制模块等的模块化设计与制作;软件同样采用模块化的设计,包括中断模块、闹钟模块、语音模块、时间调整模块设计,并采用简单流通性强的C语言编写实现。

本设计实现了时间与闹钟的修改功能、语音播报功能、年、月、日和星期的显示功能。

并且通过对比实际的时钟,查找出了误差的来源,确定了调整误差的方法,尽可能的减少误差,使得系统可以达到实际数字钟的允许误差范围内。

关键字:凌阳单片机光耦液晶数字钟单片机自1976年由Intel公司推出MCS-48开始,迄今已有二十多年了。

由于单片机集成度高、功能强、可靠性高、体积小、功耗地、使用方便、价格低廉等一系列优点,目前已经渗入到人们工作和生活的方方面面,几乎“无处不在,无所不为”。

单片机的应用领域已从面向工业控制、通讯、交通、智能仪表等迅速发展到家用消费产品、办公自动化、汽车电子、PC机外围以及网络通讯等广大领域。

多功能数字钟的实现

嵌入式系统简介:一种 专用计算机系统,用于 控制、监视或辅助设备、

机器或工厂等

嵌入式系统组成:处理 器、存储器、输入/输出

设备、软件等

嵌入式系统实现方式: 硬件实现和软件实现

硬件实现:使用专用 的嵌入式处理器、存 储器和输入/输出设

备等

软件实现:使用嵌入式 操作系统、应用程序和

驱动程序等

嵌入式系统应用领域: 工业控制、医疗设备、 汽车电子、航空航天

实现功能

软件实现方式

编程语言:C语言 或Python等

开发环境: Visual Studio 或PyCharm等

程序结构:主 程序、子程序、

函数等

数据处理:时间、 日期、闹钟等数 据的存储和处理

用户界面:图形 用户界面(GUI)

的设计和实现

功能实现:时间显 示、闹钟设置、定 时器等功能的实现

嵌入式系统实现方式

定时器功能

设定时间:用户可以根据 自己的需求设定定时时间

提醒方式:当定时时间到 达时,数字钟会发出声音

或灯光提醒

暂停功能:用户可以暂停 定时器,以便稍后重新启

动

重复功能:用户可以设置 定时器重复提醒,例如每

天、每周等

秒表功能

秒表功能简介:用于 记录和显示时间,精

确到秒

秒表启动:按下开始 按钮,秒表开始计时

0

0

1

2

报警提示:当 设备出现异常 时,数字钟发 出报警提示

0 3

数据记录:记 录设备的运行 数据,便于分 析和优化生产 过程

0 4

智能家居场景

智能闹钟:通过 多功能数字钟实 现定时提醒、叫

醒等功能

智能照明:通过 多功能数字钟控 制室内光线,实

多功能数字钟的设计与实现

数字逻辑课程设计报告—多功能数字钟的设计与实现一、设计目的1、学会应用数字系统设计方法进行电路设计;2、学习使用QuartusII 9.0, 进一步提高软件的开发应用能力,增强自己的动手实践能力。

3、培养学生书写综合实验报告的能力。

二、设计任务及要求实现多功能数字钟的设计,主要有以下功能:1、记时、记分、记秒2、校时、校分、秒清03、整点报时4、时间正常显示5、闹时功能(选做)三、设计思路3.1 计时模块3.1.1 设计原理计时模块如图3.1.1所示,其中计时用60进制计数器,计分和计秒用24进制计数器。

图3.1.1 计时间模块计时间过程:计秒:1HZ计数脉冲,0~59循环计数,计数至59时产生进位信号;计分:以秒计数器进位信号作为分计数脉冲,0~59循环计数,59时产生进位;计时:以分计数器进位信号作为时计数脉冲,0~23循环计数,23时清0。

计数器的设计:3.1.2 设计程序编程分别设计24、60进制计数器,计数状态以BCD码形式输出。

24进制计数器源程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity FEN24 isport(en,clk:in std_logic; ----高电平有效的使能信号/输入时钟 co:out std_logic;h1,h0:out std_logic_vector(3 downto 0)); ----时高位/低位end FEN24;architecture behave of FEN24 isbeginprocess(clk)variable cnt1,cnt0:std_logic_vector(3 downto 0); ----记数beginif(en='0')then ---“使能”为0cnt0:="0010";cnt1:="0001";elsif clk'event and clk='1'then ---上升沿触发if cnt1="0010"and cnt0="0011"thencnt0:="0000"; ----高位/低位同时为0时 cnt1:="0000";co<='1';elseco<='0';if cnt0="1001"thencnt0:="0000";cnt1:=cnt1+1;elsecnt0:=cnt0+1; -----高位记数累加end if;end if;end if;h1<=cnt1;h0<=cnt0;end process;end behave;60进制计数器源程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity FEN60 isport(en,clk:in std_logic; ---高电平有效的使能信号/输入时钟co:out std_logic; ---输出/进位信号s1,s0:out std_logic_vector(3 downto 0));end FEN60;architecture behave of FEN60 isbeginprocess(clk,en)variable cnt1,cnt0:std_logic_vector(3 downto 0); ---计数beginif en='0'then ---“使能”为0 cnt1:="0000";cnt0:="0000";elsif clk'event and clk='1'thenif cnt0="1001"thencnt0:="0000";if cnt1="0101"then ---当计数为58(实际是经过59个计时脉冲)cnt1:="0000";co<='1'; ---进位elsecnt1:=cnt1+1;co<='0';end if;elsecnt0:=cnt0+1;end if;end if;s1<=cnt1;s0<=cnt0;end process;end behave;3.1.3 设计仿真及生成器件24进制计数器仿真波形截图如图3.1.2所示,其中计到23时,即高位h1为2,低位h0为3时产生进位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

多功能数字钟的设计与实现一、实验目的

1.掌握数字钟的设计原理。

2.用微机实验平台实现数字钟。

3.分析比较微机实现的数字钟和其他方法实现的数字钟。

二、实验内容与要求

使用微机实验平台实现数字钟。

1.基本要求如下:

1) 24 小时制时间显示。

2) 3) 4)可以随时进行时间校对。

整点报时。

闹钟功能,要求设置起闹时间时,不影响时钟的正常走时。

2.提高要求

1) 2)校时时相应位闪烁。

能够设置多个起闹点。

三、实验报告要求

1.设计目的和内容

2.总体设计

3.硬件设计:原理图(接线图)及简要说明

4.软件设计框图及程序清单

5.设计结果和体会(包括遇到的问题及解决的方法)

四、系统总体设计

根据设计要求,初步思路如下:

1)计时单元由定时/计数器8253的通道0 来实现。

定时采用硬件计数和软件技术相结合的方式,即通过8253产生一定的定时时间,然后再利用软件进行计数,从而实现24小时制定时。

8253定时时间到了之后产生中断信号,8253在中断服务程序中实现时、分、秒的累加。

2)时间显示采用实验平台上的6个LED数码管分别显示时、分、秒,采用动态扫描方式实现。

3)校时和闹铃定时通过键盘电路和单脉冲产生单元来输入。

按键包括校时键、闹钟定时键、加1键和减1键等。

4) 报警声响用蜂鸣器产生,将蜂鸣器接到 8255 的一个端口,通过输出电平的高低来

控制蜂鸣器的发声。

系统硬件设计主要利用微机实验平台上的电路模块。

硬件电路主要由键盘电路、 单脉冲产生单元、8253 定时计数器、8255 并行接口单元、8259 中断控制器、LED 显 示电路和蜂鸣器电路等等。

系统的硬件电路设计框图如图 1 所示。

图 1 硬件电路框图

五、硬件设计

根据设计思路,硬件电路可通过实验平台上的一些功能模块电路组成,由于实验平台 上的各个功能模块已经设计好,用户在使用时只要设计模块间电路的连接,因此,硬件电 路的设计及实现相对简单。

完整系统的硬件连接如图 2 所示。

硬件电路由定时模块、按键 模块、数码管显示模块和蜂鸣器模块组成。

Q6

路

图 2 系统硬件电路图

微机系统

8253

8255

8259

数码管显示 电路 键盘电路

蜂鸣器电路

单脉冲发生 单元

单脉冲发 生单元 键盘电路

8255

PA0 PB0 PC

8253

OUT0 GATE0 Clk0

地址 CS1 译码 CS2 电路 CS3

CS4 数码管显示模块

8259

IRQ2 IRQ3 IRQ5

PC BUS

蜂鸣器 单脉冲发 生单元

各个模块的详细说明:

1.定时模块

定时模块主要是实现硬件定时1s,由8253 的计数器0来实现。

Clk0接实验平台分频电路输出Q6,f=46875hz。

GATE0 接8255 的PA0,由8255的PA0输出来控制计数器的起停。

OUT0接8259的IRQ2,定时完成请求中断,进入中断服务程序。

软件在中断服务程序中实现时分秒的累加。

2.LED数码管模块

实验平台上提供一组六个LED数码管。

插孔CS1用于数码管段选的输出选通,插孔

CS2用于数码管位选信号的输出选通。

本设计用6个数码管来动态显示时分秒,动态显示

的定时时间由软件延时。

3.按键模块

按键模块包括有2个单脉冲发生单元的按键,3个键盘模块的按键。

2个单脉冲发生单元的按键K1,K2分别为校时键和闹钟定时键,采用中断方式。

3个键盘按键A键,B 键和C 键分别为加1键,减1键和切换键。

具体的功能定义如下表。

键盘电路和8255的连接见图3所示。

按键键名功能说明

K1校时键进入校时状态

K2闹钟定时键进入闹钟定时状态

A 键加1 键校分或校时的时候使其加1递增

B 键减1 键校分或校时的时候使其减1递减

C 键切换键校分后切换到校时

校时后切换到时钟状态

闹钟设定分值后切换到设定时值

闹钟设定时值后切换到时钟状态

图3 键盘电路和8255的连接图

4.蜂鸣器模块

蜂鸣器模块由蜂鸣器驱动电路和8255组成。

选择一只压电式蜂鸣器,压电式蜂鸣器工作时约需要100mA 驱动电流。

蜂鸣器电路如图4所示。

当8255的PB0 口输出为高电平时,蜂鸣器产生蜂鸣音,8255输出为低电平时,蜂鸣器不发声。

图4 蜂鸣器电路

六、软件设计

1. 软件设计思路

根据系统的功能,可以将程序分为5个功能模块,包括LED数码管扫描模块、时间计

时模块、校时模块、闹钟定时模块和键盘扫描模块。

1) LED 数码管扫描模块

在采用动态扫描方式时,要使得LED显示得比较均匀,又有足够的亮度,需要设置适当的扫描频率。

当扫描频率在70Hz左右时,能够产生足够的图形和比较好的效果。

在每一位LED显示后调用一个延时程序。

采用实验平台时,插孔CS1用于数码管段选的输出选通,插孔CS2用于数码管位选信

号的输出选通。

在编程时,只需要先输出数据选通相应的位,再输出显示数据。

显示数据

输出前要将数据转换为显示代码。

2)时间计时模块

计时是采用硬件计时和软件计时相结合的方法。

硬件定时100ms,产生中断。

8253定

时的时间是100ms,clk0的输入时钟f=46875hz,所以计数初值为124FH。

分别用Hour、Min、Sec来存储时分秒值。

在中断服务程序中,计数到1秒的时间时,Sec加1。

当Sec

加到60的时候进一,Min值加1。

当Min等于60时,Hour值加1,Hour值等于24时清零

开始下一次循环。

3)校时模块

当校时键按下时,进入校时中断程序。

停止计数器,开始键盘扫描。

当键盘是A键时,校正的相应值为加1,若为B键时,校正的相应值为减1。

C键负责在相应的位之间切换。

具体流程见校时中断程序的流程图。

4)闹铃定时模块

当闹铃定时键按下时,进入闹铃定时中断程序。

开始键盘扫描。

当键盘是A键时,定时的相应值为加1,若为B键时,定时的相应值为减1。

C键负责在相应的位之间切换。

具体流程同校时中断程序流程图。

5)键盘扫描模块

采用的是行反转法来扫描键盘的,调用键盘扫描的程序TESTKEY 后,程序中的变量KEY 的值就是按下的键的值,如果KEY 为0FFH 则表示无键盘输入,为0~15则按照上往下从左往右的顺序分别代表每一个按键按下的信息。

判断键值进行相应的操作。

2. 程序流程图

1)主程序流程图如图5

2) 3) 4)

图5 主程图流程图

计时中断程序流程图如图6

校时中断程序流程图如图7

闹铃定时中断程序流程图和校时中断程序流程图差不多,只是不需要关闭启动计数器。

定时中断

Cnt=10?

Y

N

Sec=60?

Y 0->Sec

Min=60?

Y 0->Min

Hour=60?

Y

N

N

N

图6 计时中断服务程序流程图

时分是定时时间?

Y

N

中断返回

中断保护 Cnt+1->Cnt 0->Cnt Sec+1->Sec

PB0输出0

Min+1->Min PB0输出1 Hour+1->Hour 0->Hour

PB0输出1

恢复中断

校时中断

PA0输出停

是A 键?

是B 键?

N

是C 键?

Y

是A 键?

是B 键?

N

是C 键?

Y

PA0输出启

中断返回

图7 校时中断服务程序流程图

中断保护

读键值

Min+1->Min 止计数器

Min-1->Min

N

Y Y N

读键值

Hour+1->Hour Hour-1->Hour N

Y Y N

动计数器。