三人表决器、五人表决器的实验报告

三人表决器、五人表决器的实验报告

三人表决器、五人表决器的实验报告

一 实验目的

1.熟悉Quartus II 软件的基本操作

2.学习使用Verilog HDL 进行设计输入

3.逐步掌握软件输入、编译、仿真的过程 二 实验说明

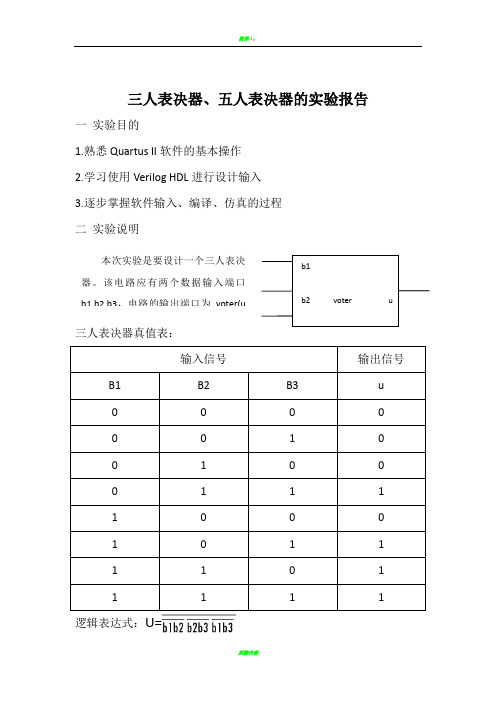

三人表决器真值表:

输入信号

输出信号

B1 B2 B3 u 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1

1

1

1

逻辑表达式:U=

b1

b2 voter u

本次实验是要设计一个三人表决器。

该电路应有两个数据输入端口b1,b2,b3,电路的输出端口为voter(u

三实验要求

1、完成三人表决器的Verilog HDL程序代码输入并进行仿真

2、采用结构描述方式和数据流描述方式

3、完成对设计电路的仿真验证

四、实验过程

(1)三人表决器:

程序代码

仿真结果

五人表决器:

程序代码

仿真结果

五、实验体会

通过三人表决器和五人表决器的设计,使我们更加熟悉Quartus 软件进行数字系统设计的步骤,以及运用Verilog HDL进行设计输入,并掌握三人表决器和五人表决器的逻辑功能和设计原理,逐步理解功能仿真和时序仿真波形。

三人表决器和五人表决器大体相似,并没有太大的区别。

三人表决器报告

三人表决器报告1. 摘要本文档是对三人表决器的详细报告,包括设计原理、功能特点以及使用场景等方面的介绍。

三人表决器是一种基于多人决策的工具,通过对多个人的表决结果进行统计和分析,以实现决策的公平和有效。

2. 引言在现实生活中,决策常常需要多个人共同参与。

然而,在多人参与的决策过程中,可能会出现意见不统一、讨论难以达成共识的情况。

三人表决器的出现能够帮助解决这类问题。

三人表决器是一种简单而又有效的工具,可以帮助多个人快速完成决策过程,并保证最终结果的公平和合理性。

3. 设计原理三人表决器的设计基于以下原理:3.1. 多数决原则三人表决器采用的是多数决原则。

也就是说,在决策过程中,只有获得多数人的支持才能最终采取行动。

这样做的好处是能够避免因为个别人的意见而导致决策失去公正性和有效性。

3.2. 匿名投票为了保证每个人能够真实地表达自己的意见,三人表决器采用匿名投票的方式,即投票参与者的身份不会被泄露。

这种设计可以有效地防止潜在的压力或影响对投票结果的干扰。

4. 功能特点三人表决器具有以下功能特点:4.1. 快速决策三人表决器的设计目标之一是能够快速进行决策。

参与者只需在规定的时间内投票,即可得出最终结果,避免无限的讨论和拖延。

4.2. 可视化结果三人表决器可以通过可视化方式展示投票结果。

这样可以让参与者直观地了解整体的投票情况,有助于各方更好地理解和接受最终结果。

4.3. 定制化选项三人表决器支持定制化选项,即参与者可以根据需要设定不同的选项。

这样能够更好地适应不同场景下的决策需求。

5. 使用场景三人表决器适用于以下场景:5.1. 团队决策在团队中,常常需要进行一些重要的决策,如项目方向、资源分配等。

使用三人表决器可以帮助团队成员快速达成共识,减少决策时间。

5.2. 会议投票在会议期间,可能会出现一些需要快速决策的问题,如提案通过与否、预算审批等。

通过使用三人表决器,可以高效地完成这些决策过程。

5.3. 民主决策在一些组织或社区中,民主决策是一种重要的决策方式。

三人表决器仿真实验分析

三人表决器摘要本次设计的三人表决器,是投票系统中的客户端,是一种代表投票或举手表决的表决装置。

表决时,与会的有关人员只要按动各自表决器上“赞成”“反对”“弃权”的某一按钮,荧光屏上即显示出表决结果。

在三人表决器中三个人分别用手指拨动开关S W1、S W2、S W3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用L E D(高电平亮)显示,如果决议通过那么实验板上L2亮;如果不通过那么实验板上L1亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮。

一.任务设计三人表决器电路,并在仿真软件上验证电路的正确性。

二.目标掌握三人表决器电路的结构。

学会仿真软件数字部分的操作。

三.要求1复习三人表决器电路的设计步骤。

2熟悉用集成电路的引脚位置及各引脚用途。

3使用TTL门电路时,一定要正确连接电源端和接地端4按集成电路引脚图正确接线,芯片电源引脚不要接错,以免损坏芯片,影响实验正常进行。

四.实训工具及设备电脑一台;Mult isi m软件五.仿真电路图六.设计的主要内容:按照设计题目,根据所学的组合逻辑所学的知识及数字电路和嵌入式的知识完成三人表决器的设计,使之能够满足表决时少数服从多数的表决规则,根据逻辑真值表和逻辑表达式完成表决功能。

七.三人表决器概述:1.三人表决器的功能描述三个人分别用手指拨动开关S W1、S W2、S W3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用LE D (高电平亮)显示,如果决议通过那么实验板上L2亮;如果不通过那么实验板上L1亮;如果对某个决议有任意二到三人同意,那么此决议通过,L2亮;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1亮2.三人表决器”的逻辑功能表决结果与多数人意见相同。

三人表决器五人表决器的实验报告

三人表决器、五人表决器的实验报告

一 实验目的

1、熟悉Quartus II 软件的基本操作

2、学习使用Verilog HDL 进行设计输入

3、逐步掌握软件输入、编译、仿真的过程 二 实验说明

三人表决器真值表:

输入信号

输出信号

B1 B2 B3 u 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1

1

1

1

逻辑表达式:U=

b1

b2 voter u

b3

本次实验就是要设计一个三人表决器。

该电路应有两个数据输入端口b1,b2,b3,电路的输出端口为voter(u 输出信号)。

三实验要求

1、完成三人表决器的Verilog HDL程序代码输入并进行仿真

2、采用结构描述方式与数据流描述方式

3、完成对设计电路的仿真验证

四、实验过程

(1)三人表决器:

程序代码

仿真结果

五人表决器:

程序代码

仿真结果

五、实验体会

通过三人表决器与五人表决器的设计,使我们更加熟悉Quartus 软件进行数字系统设计的步骤,以及运用Verilog HDL进行设计输入,并掌握三人表决器与五人表决器的逻辑功能与设计原理,逐步理解功能仿真与时序仿真波形。

三人表决器与五人表决器大体相似,并没有太大的区别。

课程设计试验报告三人表决器

武汉纺织大学《数字逻辑》课程设计报告题目:三裁判表决器院系:数学与计算机学院专业班级:计科094学号:0904681223学生姓名:李勤指导教师:朱勇2011年 5 月20 日2一、 引言通过对传统数字电路的设计,掌握对数字逻辑设计概念的熟悉。

二、系统介绍:主要仪器是TOS-2数字电路实验系统。

选用的芯片是74LS151 8-1数据选择器。

通过设计好的逻辑表达式,在TOS--2数字电路上选择好个个需要连入的拐脚,进行连线。

实现三人表决器的功能。

三、设计任务及设计原理:引脚图功能表设计有三个变量输入A ,B C ,二个输出 W ,F,其中F=W ,逻辑表达式: F=ABC C AB C B A BC A +++。

A,B,C 通过三个开关相接,把D0---D7设置好之后, 16 15 14 13 12 11 10 974LS1511 2 3 4 5 6 7 8V CC D 4 D 5 D 6 D 7 A 0 A 1 A 2D 3 D 2 D 1 D 0 Y Y S GND 输 入输 出D A 2 A 1 A 0 S Y Y × × × × 1D 0 0 0 0 0D 1 0 0 1 0D 2 0 1 0 0D 3 0 1 1 0D 4 1 0 0 0D 5 1 0 1 0D 6 1 1 0 0D 7 1 1 1 00 1D 0 0D D 1 1D D 2 2D D 3 3D D 4 4D D 5 5D D 6 6D D 7 7D数学与计算机学院硬件课程设计报告就可以通过调节开关来输入。

输出接到一个LED灯,如果通过,那么灯就亮,否则的话,灭。

74LS1510 GA AB BC CD0D1 Y Y0 D3D3 WD41 D5D6D7方法之一四、代码清单:(机房答辩,提交代码)只需要连线,无代码。

五、程序调试心得体会:第一次线连接好之后,首先试验的是逻辑功能的正确性。

课程设计试验报告 5人表决器

武汉纺织大学《数字逻辑》课程设计报告题目:5人表决器院系:数学与计算机学院专业班级:计科094学号:0904681223学生姓名:李勤指导教师:朱勇2011年 6 月2 日一、引言设计一个五人表决器,掌握异步清零以及锁存器的工作机制,掌握QuartusII软件的使用方法以及GW48型SOPC开发平台中的输入输出模式配置方法。

二、系统介绍:主要仪器是PC机、DICE-EH2000 EDA实验开发系统,用到的器件是ACEX1K系列EP1K30TC144-3的芯片。

三、设计任务及设计原理:v_in:表决信号输入端,高电平为赞成,低电平为反对;lock:判决锁存信号,上升沿表决结束,锁存表决输入信号,并计算输出表决信息;clr:清零信号,高电平有效,进入新的一次表决过程;v_over:表决结束信号,高电平有效,清零信号有效后,此信号为低电平。

num_agr:BCD码输出显示表决结果中赞成的人数;num_opp:BCD码输出显示表决结果中反对的人数;v_out:对应显示每个表决信号的状态;led_agr:判决结果为赞成时有效;led_opp:判决结果为反对时有效首先在QuartusII上进行功能和时序仿真,之后通过器件及其端口配置下载程序到SOPC开发平台中。

在硬件实现中:1.用实验平台的拨动开关实现5人表决的输入信号(v_in):注:要求使用最右面5个开关。

2. 用实验平台的按键实现清零(clr)和锁存(lock)信号:注:采用模式4的输入方式,要求使用键7实现清零(clr)、键6实现锁存(lock)。

(模式4的I/O设置见附录)3. 用实验平台的数码管实现赞成和反对人数的显示:注:要求使用数码管6显示赞成票数、数码管5显示反对票数。

4. 用实验平台的LED发光阵列实现表决结果和每人的表决信号:注:要求LED1显示判决赞成(led_agr)信号,LED8显示判决反对(led_opp)信号。

LED4、LED5、LED6同时显示判决结束信号。

三人表决器电路设计实验报告小红书

三人表决器电路设计实验报告小红书本文主要介绍三人表决器电路设计实验报告,该实验旨在设计一种能够实现多人表决并且可以显示表决结果的电路。

实验采用了数字电路设计的相关知识和技术,最终成功实现了预期的功能。

以下是实验的详细过程和结果展示。

一、实验背景三人表决器是一种可以用来处理多人表决的电路,通过设计能够实现多人表决并根据表决结果显示不同的反馈。

该电路可用于各种投票场合,如会议室、学生议会或大型活动等。

二、实验原理三人表决器电路由多个基本组件构成,包括开关、计数器、显示器等。

主要原理是通过开关输入的二进制编码来计数,然后根据计数结果来显示不同的反馈。

由于本实验是基于数字电路设计,涉及了二进制算术、逻辑运算以及组合电路等相关知识。

三、实验材料和步骤实验所需材料:(1)开发板:FPGA开发板(2)元器件:LED灯、计数器模块、开关、电路板实验步骤:(1)原理和电路设计确定并使用EDA软件进行电路图设计。

(2)电路原型制作,验收并进行调试(3)连接电路,在开发板上植入(或flash)bit文件。

(4)将开关、LED灯和计数器模块等电路元件安装在电路板上。

(5)通过开关输入不同的二进制编码,以观察显示器的反馈结果。

四、实验结果分析在实验进行过程中,我们成功地完成了电路的设计、制作和测试,并达到了预期的实验目的。

在实验中,我们通过FPGA开发板编写了硬件描述语言(HDL)来描述电路,并成功将其烧录进开发板中。

在测试的过程中,我们使用了开关来输入二进制编码,并且观察到了不同的计数结果。

同时,我们还观察到了预期的反馈结果,包括LED灯逐个亮起、提示声音和不同的计数显示。

总结:本次实验成功地实现了三人表决器电路设计的目的,我们通过HDL 语言进行了电路设计,利用开发板和相关元器件完成了电路的制作,并通过实验测试获得了较好的实验结果。

该实验不仅增强了我们对数字电路设计的理解和实践能力,同时也扩展了我们的应用技能,有助于提高实际工作中数字电路设计的水平。

三人表决项目报告

三人表决器项目报告系别:专业:姓名:指导老师:学号:摘要本次设计的三人表决器,是投票系统中的客户端,是一种代表投票或举手表决的表决装置。

表决时,与会的有关人员只要按动各自表决器上“赞成”“反对”。

在三人表决器中三个人分别用开关SW1、SW2、SW3的状态来表示自己的意愿。

1、项目功能三个人分别用手指拨动开关SW1、SW2、SW3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平,不同意就把自己的指拨开关拨到低电平。

表决结果用LED(高电平亮)显示,如果两个及其两个以上通过那么实验板上LED灯亮,如果没有人通过或者只有一人通过没通过则不亮。

2、项目目标1. 熟悉逻辑函数的表示方法与化简方法;2. 正确理解数字电路的要求,能知道与门、或门、非门的含义。

3. 了解要用到的每个芯片的引脚是什么门电路并且运用。

3、实验器材:输入输出模块,面包板,芯片74LS20、74LS00、74LS138、74LS153,导线四、实验步骤1、得出真值表和卡诺图设:A、B、C分别代表三个输入,同意为1,不同意为0;Y为输出,通过为1,不通过为0。

有真值表可得出卡诺图如下:由卡诺图可知化简后表达式如下:Y=BC+AC+AB2、设计电路,接入输入输出模块进行试验方案一:芯片74LS00与74LS2074 LS00是四-二输入与非门,它内部有四个与非门,每个与非门有两个输入端、一个输入端。

74 LS20是二-四输入与非门,它内部有两个与非门,每个与非门有四个输入端、一个输出端。

74 LS00、74 LS20引脚及内部电路图(1-1)图1-1: 74LS00 74 LS20 电路图接法如下:74LS00的VCC与74LS20的VCC接5V的直流电,两块芯片的7脚都接地;74LS00的1、13脚接输入端A;2、5脚接输入端B;4、12脚接输入端C。

74LS的11、3、6脚接在74LS20的1、2、4脚上;74LS20的6脚为输出Y。

三人表决器_数电小实验之三人表决器

三⼈表决器_数电⼩实验之三⼈表决器数电⼩实验20级会员们的模电实验已经结束了,他们的培训计划已经从模电实验进⾏到了数电实验。

他们将学习到⼀个新的知识——逻辑电路。

接下来让我们⼀起深⼊了解本次任务吧!实验:三⼈表决器的设计和搭建要求:1.写出真值表、逻辑表达式、画出实验电路;2.只能⽤74HC00和74HC20;实验任务设计⼀个3变量的多数表决电路(当三个输⼊端中有2个及以上输⼊“1”时,输出端才为“1”),然后在实验板上实现⾃⼰设计的逻辑电路,并验证是否正确。

实验原理采⽤74HC00+74HC20设计⽽成,三⼈各控制A、B、C三个按键中的⼀个,以少数服从多数的原则表决事件,按下表⽰同意,否则为不同意。

若两⼈及两⼈以上同意,发光⼆极管点亮,否则不亮。

1.真值表如下:2.逻辑表达式:根据真值表,我们可以写出输出函数的与或表达式,即:3.实验电路:74HC00四与⾮门:芯⽚介绍:74HC00 是TTL2 输⼊端四与⾮门,⾼电平4V,低电平1V,与⾮门电路经常⽤来实现组合逻辑的运算。

74HC20四输⼊双与⾮门:74HC20是常⽤的双四输⼊与⾮门集成电路,常⽤在各种数字电路和单⽚机系统中。

认真学习的20级会员们:看着⼩20们努⼒的⾝影,像是看到了去年的我们,这些实验不仅提⾼了他们的动⼿实践能⼒,也为将来的单⽚机学习打下了良好的基础。

届届传承的精神:热⼼善良的学长们,时刻⿎舞着20级们的学习,不仅为他们拓展了数电实验的新知识,同时也激发了他们的学习兴趣,使他们在学习中更有⾃信。

成功不是将来才有的,⽽是从决定去做的那⼀刻起,持续累积⽽成,现在的点滴付出,在不久的将来,将会有意想不到的结果。

因为疫情使协会会员们来得晚放假得早,但协会会员们都克服了种种困难,在较短的时间内完成了各⾃的学习任务且表现良好。

希望未来20级会员们能够尽快成长,在协会撑起⼀⽚天。

扫码关注我们郑州铁院⽆线电做事先做⼈编辑:物联⽹19A1苏笑颜⽂字:物联⽹19A1苏笑颜校审:铁道车辆19A2孟珊如审核:王云飞、张凯。

实验五 三人表决器实验报告

实验五:三人表决电路的设计和电路实现

一.实验目的

通过操作掌握电烙铁的使用,正确理解数字电路的要求;能知道与门,非门,或门的含义,了解芯片的每个引脚是什么门电路;做到真正了解门电路的含义。

二.项目要求

1.判断引脚的正确位置,理解数字电路的原理,掌握操作步骤,能正确安装所选电路

6*6*5

3

IC座

14p

1

4-2输入与非门

CD4011

1

IC座

14P

1

2-4输入与非门

CD4012

1

独石电容

104

1

发光二极管

3mm红发红

1

接线座

2P

1

P

六.实验总结

2.利用原理图纸,分析故障原因,工作电压为5v

三.工作原理

本电路采用4-2输入与非门CD4011和2-4输入与非门CD4012组成,控制a,b,c三个按键中的一个,以少数服从多数的原则表决事件,按下表示同意,否则不同意。若表决通过,发光二极管点亮,否则不亮。

四.实验散件清单

名称

规格

数量

电阻

470

5

轻触开关

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

B1

B2

B3

u

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

1

1

0

0

0

1

01Βιβλιοθήκη 1110

1

1

1

1

1

三人表决器真值表:

-^3

逻辑表达式:U=n利忑苛总

三实验要求

1、完成三人表决器的Verilog HDL程序代码输入并进行仿真

2、采用结构描述方式和数据流描述方式

3、完成对设计电路的仿真验证

四、实验过程

(1)三人表决器:

三人表决器、五人表决器的实验报告

一实验目的

1.熟悉QuartusII软件的基本操作

2.学习使用Verilog HDL进行设计输入

3.逐步掌握软件输入、编译、仿真的过程

二实验说明

本次实验是要设计一个三人表决 器。该电路应有两个数据输入端口b1,b2,b3,电路的输出端口为voter(u输出信号)。

输入信号

仿真结果

1西IIOe

*

與X

11 £

niu

i

血

•

J

0

F:

]

F

C

1

I

T

五、实验体会

通过三人表决器和五人表决器的设计,使我们更加熟悉Quartus软件进行数字系统设计的步骤,以及运用Verilog HDL®行设计输入, 并掌握三人表决器和五人表决器的逻辑功能和设计原理,逐步理解功 能仿真和时序仿真波形。三人表决器和五人表决器大体相似, 并没有 太大的区别。

程序代码

五人表决器:

程序代码

=modulethree_voter_exlfA^B.rCfD^E^Y);inputA^E^C^D^E;

out口u匸Y;

wire[1:0]add^resul匸;

assignadd_res口1匸=A+B+C+D+E;

S55ignY= (add_re5ult>=3) ?11b1:11bO;endmodule