任意进制计数器的设计

任意进制计数器的设计

任意进制计数器的设计【摘要】计数器集成芯片一般有4位二进制、8位二进制或十进制计数器,而在实际应用中,往往需要设计一个任意n进制计数器,本文给出它的设计方法和案例。

【关键词】计数器;清零一、利用反馈清零法获得计数器1 集成计数器清零方式异步清零方式:与计数脉冲cp无关,只要异步清零端出现清零信号,计数器立即被清零。

此类计数器有同步十进制加法计数器ct74ls160、同步4位二进制加法计数器ct74ls161、同步十进制加/减计数器ct74ls192、同步4位二进制加/减计数器ct74ls193等。

同步清零方式:与计数脉冲cp有关,同步清零端获得清零信号后,计数器并不立刻被清零,只是为清零创造条件,还需要再输入一个计数脉冲cp,计数器才被清零。

属于此类计数器有同步十进制加法计数器ct74ls162、同步4位二进制加法计数器ct74ls163、同步十进制加/减计数器ct74ls190、同步4位二进制加/减计数器ct74ls191等。

2 反馈清零法对于异步清零方式:应在输入第n个计数脉冲cp后,利用计数器状态sn进行译码产生清零信号加到异步清零端上,立刻使计数器清零,即实现了n计数器。

在计数器的有效循环中不包括状态sn,所以状态sn只在极短的瞬间出现称为过渡状态。

对于同步清零方式:应在输入第n-1个计数脉冲cp后,利用计数器状态sn-1进行译码产生清零信号,在输入第n个计数脉冲cp 时,计数器才被清零,回到初始零状态,从而实现n计数器。

可见同步清零没有过渡状态。

利用计数器的清零功能构成n计数器时,并行数据输入端可接任意数据,其方法如下:①写出n计数器状态的二进制代码。

异步清零方式利用状态sn,同步清零方式利用状态sn-1。

②写出反馈清零函数。

③画逻辑图。

例1 试用ct74ls160的异步清零功能构成六进制计数器。

解:①写出sn的二进制代码。

sn=s6=0110②写出反馈清零函数。

③画逻辑图。

如图1所示。

计数器的设计实验报告

计数器的设计实验报告篇一:计数器实验报告实验4 计数器及其应用一、实验目的1、学习用集成触发器构成计数器的方法2、掌握中规模集成计数器的使用及功能测试方法二、实验原理计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。

计数器种类很多。

按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。

根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。

根据计数的增减趋势,又分为加法、减法和可逆计数器。

还有可预置数和可编程序功能计数器等等。

目前,无论是TTL还是CMOS集成电路,都有品种较齐全的中规模集成计数器。

使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。

1、中规模十进制计数器CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如图5-9-1所示。

图5-9-1 CC40192引脚排列及逻辑符号图中LD—置数端CPU—加计数端CPD —减计数端CO—非同步进位输出端BO—非同步借位输出端D0、D1、D2、D3 —计数器输入端Q0、Q1、Q2、Q3 —数据输出端CR—清除端CC40192的功能如表5-9-1,说明如下:表5-9-1当清除端CR为高电平“1”时,计数器直接清零;CR置低电平则执行其它功能。

当CR为低电平,置数端LD也为低电平时,数据直接从置数端D0、D1、D2、D3 置入计数器。

当CR为低电平,LD为高电平时,执行计数功能。

执行加计数时,减计数端CPD 接高电平,计数脉冲由CPU 输入;在计数脉冲上升沿进行8421 码十进制加法计数。

执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD 输入,表5-9-2为8421码十进制加、减计数器的状态转换表。

加法计数表5-9-减计数2、计数器的级联使用一个十进制计数器只能表示0~9十个数,为了扩大计数器范围,常用多个十进制计数器级联使用。

用74LS290构成任意进制计数器的方法王静

第 28 卷 第 1 期(上) 2012 年 1 月

计数器是一个用以实现计数功能的时序电路,它是数 字系统中使用最广泛的时序部件,几乎不存在没有计数器 的系统.它除了可以累计输入脉冲个数(计数)外,还可以用 作分频、定时等等.

计数器的常用构成方法有两种:一是可以用时钟触发 器和门电路组成计数器;二是采用集成计数器构成所需要 的计数器.中规模集成计数器由于体积小,功耗低、可靠性高 等优点而得到了广泛地应用.然而,定型产品的种类是很有 限的,就计数进制而言,常用的标准计数器多为十进制、四 位二进制(十六进制)、八位二进制(二百五十六进制)几种.因 此,在需要其它任意进制计数器时,只能在现有中规模集成 计数器基础上,经过外电路的不同连接来实现.本文介绍一 种由 74LS290 构成任意进制的计数器的方法. 1 74LS290 的电路组成

第一步:采用级联的方法,将多个集成计数器串联起 来,扩大计数器的容量.74LS290 没有专门的进位信号输出 端,可以用本级的高位输出信号驱动下一级计数器.

第二步:采用脉冲反馈法获得所需的计数器. 以下是用两片 74LS290 构成一个 84 进制计数器的具 体方法: 首先将每块 74LS290 按 8421BCD 十进制方式连线,分 别代表个位和十位.

赤 峰 学 院 学 报( 自 然 科 学 版 ) Journal of Chifeng University(Natural Science Edition)

用74160集成计数器构成任意进制计数器的电路设计

用74160集成计数器构成任意进制计数器的电路设计单嵛琼;单长吉【摘要】74160 is die for 10 synchronous counter addition,take advantage of its reset and the number of pre-set function can make mould for any number of counters.So as to solve the problem that we can't buy any kind of counter.%74160是模为10的同步加法计数器,利用它的清零和预置数功能可以构成模为任意数的计数器,从而解决了我们需要计数器但市场上又买不到这种计数器的困难。

【期刊名称】《大学物理实验》【年(卷),期】2016(029)003【总页数】3页(P15-17)【关键词】计数器;清零;置数;有效状态【作者】单嵛琼;单长吉【作者单位】昭通学院,云南昭通 657000;昭通学院,云南昭通 657000【正文语种】中文【中图分类】O453市场上能买到的集成计数器芯片一般为4位二进制计数器和十进制计数器,如果需要其它进制计数器,可用现有的4位二进制计数器和十进制计数器芯片进行设计。

74160是8421BCD码同步加法十进制计数器,可以用它来构成任意进制计数器。

74160是8421BCD码同步加法计数器[1-2],图1是它的逻辑符号:是清零端,端是预置数端,EP、ET是两个使能端,CP端是时钟脉冲端,RCO是进位输出端,D3、D2、D1、D0是四个预置数据输入端,Q3、Q2、Q1、Q0是四个数据输出端。

其中进位输出端的逻辑表达式为[3]:RCO=ET·Q3·Q1。

由表1可知,74160具有异步清零、同步置数、计数和保持的功能。

用74160构成模小于10的计数器的计数器时通常有两种方法:异步清零法和同步置数法[4].文章中选取用74160构成五进制计数器来说明这两种方法的应用。

任意进制计数器的构成方法

之前例子中,如果74LS160芯片是 同步清零功能,异步预置功能呢,该如 何实现?状态也采8421码编码。

同步清零:6进制,第6个有效边沿清零0

同步 ,RD/ 应在状态5时有效

M=6,在SM-1=S5=0101时反馈使 RD 0,待第6个

上升沿到来时复位至0000态, RD 1。

异步预置:6进制,逢6预置0

异步 ,LD/ 在状态6时有效

M=6,当为SM=S6=0110时反馈使 LD0, 立刻预置成0000态,LD1 。

跳至 跳至

0态(跳转目标 只有一个:0,

不可设置)

0态或其它状态—由数 据输入端D的值决定,

即可设置。

异步:一有效立刻执行; 同步:有效后待有效边沿到时执行。

用74LS160 实现6进制计数器

方法一:置零法 利用74LS160的异步置零功能来实现

逢6清零 R D ( Q 3 Q 2 Q 1 Q 0 ) ,L D 1 ,E E P 1 P

有四种功能:异步置零、同步预置、 保持和计数,四种功能优先级别是异步置 零>同步预置>保持>计数。

三、M<N的实现方法

实 现 方 法

置零功能

置数功能

置零法(复位法):利用置零功能 分异步和同步

置数法(置位法):利用预置数功能 分异步和同步

可从N个循 环状态的中 任一状态

可从N个循 环状态的中 任一状态

提示:同时使用置零和置数功能

任意进制 计数器的构成方法

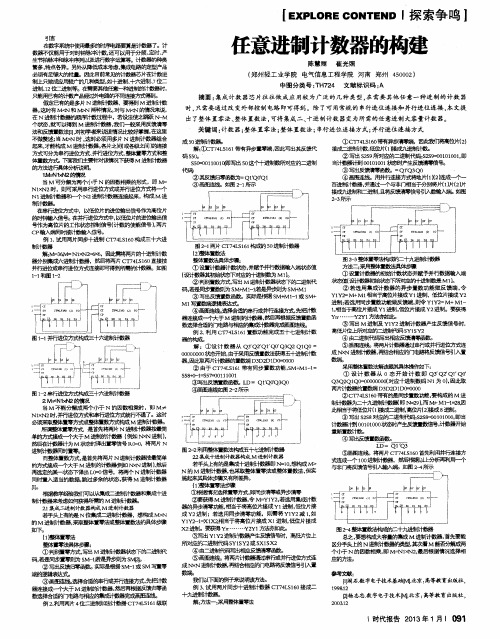

任意进制计数器的构建

② 其反魄 日 零函数为 =Q1 ' QO ' Q1 ③ 画图i 圭 璺 ‰ 如图}1 所示

①c T 7 4 L S 1 6 o 带有异步清写端,因此 位片( 2 ) 接成= 进% } 数, 低位片( 1 艟成九 进 汁女 ② 写出 ¥ 2 S 9 所对应的二进朱 【 码: S 2 S 9  ̄ 0 0 1 0 1 0 0 1 , 即 当 蚩 髂i 十 至 0 0 0 1 0 1 0 0 1 j 好 冬 时产 生 馈渭写信号。 ③ 写出反豌静 函数。= Q1 Q3 Q0 ④ 画图连线 用并行连接方式将地 片 ( 1 ) ( 2 b 鸯 成—个一 百进 十 数器。 并通过—个与非门相当于分别将片( 1 ) 片( 2 片 接成九揣 匕进制, 目 将反馈漓写 唁 号g I ^ 数输 ^ 端。 如图

时, 只需要通过改 变外部控制电路 即可得到。除 了可用常规 的 串行进位连接 和并行进位连接 , 本文提

出了整体置零 法、 整体置数法 , 可将集成二 、 十进制计数器变为所需的任意进 制大容量计数 器。 关键词 : 计数 器; 整体置零法 ; 整体置数法 ; 串行进位 连接方式; 并行进位 连接 方式

例 利用 c T 7 4 L S 1 6 1 置数功能完成五十七进制计数 器的 构眈

图2 _ 3 整体置写法构成的二 十九进静 数器 方法二: 采用整体置数法具体 步骤 ① 状态 姻导 莉 嗷 f 透吓所列应的十进带 I l ! 故 是 M1 ) 。 ② 若选用集成计数器的异步置数功能做反 馈端. 令 Y I Y 2 -M+ = M1 相当于高度片 接成Y1 进制. T 氐 位片接成Y2 进制; 若选用同步置数功能做反馈端。 则令 Y I Y 2 = M+M1 — 1 . 相当 于高位片接成 Y 1 进制。 低位片接成Y 2 进制。要获得 Yn " ……・ ' Y2 Y1 方 亦如此。 ③ 写出M 进带 圾 Y l I Y 2

总结任意进制计数器的设计方法

总结任意进制计数器的设计方法一、引言计数器是数字电路中常见的组合逻辑电路,其作用是在一定范围内对输入的信号进行计数。

而进制计数器则是在特定进制下进行计数的计数器,如二进制计数器、十进制计数器等。

本文将总结任意进制计数器的设计方法。

二、基本概念1. 进位:当某一位达到最大值时,需要向高位进位。

2. 借位:当某一位减法结果为负时,需要向高位借位。

3. 余数:在除法中,被除数除以除数所得到的余数即为该数字的个位数字。

4. 商:在除法中,被除数除以除数所得到的商即为该数字的十位以及更高位数字。

三、二进制计数器设计方法1. 同步二进制计数器同步二进制计数器又称为并行加法器或者锁存式加法器。

其实现原理是将多个全加器连接起来,并且每一个全加器都接收同样的时钟信号。

当时钟信号发生变化时,所有全加器同时进行运算。

2. 异步二进制计数器异步二进制计算机又称为Ripple Counters或者Clock-Triggered Flip-Flops。

其实现原理是通过多个D触发器连接起来,每个D触发器都接收上一个触发器的输出信号。

当时钟信号发生变化时,第一个D触发器会先被触发,然后它的输出信号会传递到下一个D触发器中。

四、十进制计数器设计方法1. 二进制编码计数器二进制编码计数器是一种使用二进制代码表示数字的计数器。

其实现原理是通过将BCD码转换成二进制来实现计数。

2. BCD码计数器BCD码计数器是一种使用BCD码表示数字的计数器。

其实现原理是通过多个BCD加法器连接起来,每个加法器都接收同样的时钟信号。

当时钟信号发生变化时,所有加法器同时进行运算。

五、任意进制计数器设计方法1. 基于同步电路设计方法任意进制计算机可以通过同步电路来实现。

其实现原理是将多个全加器连接起来,并且每一个全加器都接收同样的时钟信号。

当时钟信号发生变化时,所有全加器同时进行运算。

2. 基于异步电路设计方法任意进制计算机也可以通过异步电路来实现。

其实现原理是通过多个D触发器连接起来,每个D触发器都接收上一个触发器的输出信号。

六步搞定——任意进制任意起始值计数器

六步——任意进制,任意起始值计数器的设计

计数器的介绍课本介绍了三种方法:

反馈清零法:起始值二进制数每一位都为0;

反馈置数法:任意起始值;

TC反馈置数法:输出置数态限制每一位都为1,也就是说起始值也是固定的;

以下选择反馈置数法较为灵活,但是做法相对比较固定。

例如,设计一个32进制,初态为180计数器

第一步:固定图

不管什么进制什么起始值下面的接法是固定的。

第二步:置数端电平

左边为低位片,右边为高位片

32进制,初态为180

初态=输入置数端=180=1011 0100=高位片的DCBA 低位片的DCBA 接入置数端的电平:

第三步:接入与非门

输出置数态=180+32-1=211=1101 0011=

高位片QD QC QB QA 低位片QD QC QB QA

也就是说计数器从180开始计数到211又转回180;

把所有1找出来,得高位片QD QC QA和低位片QB QA共有五个一;接入六个端口输入的与非门nand6(因为没有奇数个输入端的与非门)多余端接VCC

第四步:把五个输出为一的Q接入与非门

整体图样

第五步:加入波形

CLK为时钟

A为控制立刻进入初态180

32进制,初态为180仿真波形。

计数器的设计实验报告

计数器的设计实验报告一、实验目的本次实验的目的是设计并实现一个简单的计数器,通过对计数器的设计和调试,深入理解数字电路的基本原理和逻辑设计方法,掌握计数器的工作原理、功能和应用,提高自己的电路设计和调试能力。

二、实验原理计数器是一种能够对输入脉冲进行计数,并在达到设定计数值时产生输出信号的数字电路。

计数器按照计数方式可以分为加法计数器、减法计数器和可逆计数器;按照计数进制可以分为二进制计数器、十进制计数器和任意进制计数器。

本次实验设计的是一个简单的十进制加法计数器,采用同步时序逻辑电路设计方法。

计数器由触发器、门电路等组成,通过对触发器的时钟信号和输入信号的控制,实现计数功能。

三、实验设备与器材1、数字电路实验箱2、集成电路芯片:74LS160(十进制同步加法计数器)、74LS00(二输入与非门)、74LS04(六反相器)3、示波器4、直流电源5、导线若干四、实验内容与步骤1、设计电路根据实验要求,选择合适的计数器芯片 74LS160,并确定其引脚功能。

设计计数器的清零、置数和计数控制电路,使用与非门和反相器实现。

画出完整的电路原理图。

2、连接电路在数字电路实验箱上,按照电路原理图连接芯片和导线。

仔细检查电路连接是否正确,确保无短路和断路现象。

3、调试电路接通直流电源,观察计数器的初始状态。

输入计数脉冲,用示波器观察计数器的输出波形,检查计数是否正确。

若计数不正确,逐步排查故障,如检查芯片引脚连接、电源电压等,直至计数器正常工作。

4、功能测试测试计数器的清零功能,观察计数器是否能在清零信号作用下回到初始状态。

测试计数器的置数功能,设置不同的预置数,观察计数器是否能按照预置数开始计数。

五、实验结果与分析1、实验结果成功实现了十进制加法计数器的设计,计数器能够在输入脉冲的作用下进行正确计数。

清零和置数功能正常,能够满足实验要求。

2、结果分析通过对计数器输出波形的观察和分析,验证了计数器的工作原理和逻辑功能。

数字电路逻辑设计 第六章2

(一)反馈清零法

74160是模10计数器,要实现模853计数,须用三片74160级联。 ⑴先设计模1000计数器: M = M1×M2 ×M3=10 × 10 × 10=1000 ☆ 利用各片间进位信号快速传递方法,组成计数模值为1000计数器。 ⑵ 用异步清0法,使计数器计数脉冲输入到第853个脉冲时产整体置0 信号 使计数器返回到初始状态0000。 计数范围:

画出逻辑图如图

D2 D1 D0 CTT D3 CTP CTRDIV16 CO CT161 CR

LD

1

Q 3 Q2 Q 1 Q 0

0

0

&

O

0

(二)同步预置法

例:用四位同步二进制计数器74161设计余3BCD码计数器。

解:余3BCD码计数器的状态转移图如图所示

0011 1100

LD Q3Q2

画出逻辑图

&

1 CTP CR CTT 1

74161(1)

D0D1D2D3

Q0Q1Q2Q3 CO

CTP CTT

CR

74161(2)

D0D1D2D3

Q0Q1Q2Q3 CO

LD

LD

CP

(二)同步预置法

方法三、整体同步反馈置数: (利用进位输出作为置数译码信号) 计数范围196-255,当计数器计到255时,CO=1,使 两片74161置数控制端 /LD=0,下一个CP到来时置数。 预置输入=256-60=196 (196)10=(11000100)2 低位片预置数:0100 高位片预置数:1100

工作波形图: 5 6 7 8

9

10

6.5采用中规模集成器件设计任意进制计数器

1. M<N,N为单片计数器的最大计数值

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

任意进制计数器的设计

【摘要】计数器集成芯片一般有4位二进制、8位二进制或十进制计数器,而在实际应用中,往往需要设计一个任意n进制计数器,本文给出它的设计方法和案例。

【关键词】计数器;清零

一、利用反馈清零法获得计数器

1 集成计数器清零方式

异步清零方式:与计数脉冲cp无关,只要异步清零端出现清零信号,计数器立即被清零。

此类计数器有同步十进制加法计数器

ct74ls160、同步4位二进制加法计数器ct74ls161、同步十进制加/减计数器ct74ls192、同步4位二进制加/减计数器ct74ls193等。

同步清零方式:与计数脉冲cp有关,同步清零端获得清零信号后,计数器并不立刻被清零,只是为清零创造条件,还需要再输入一个计数脉冲cp,计数器才被清零。

属于此类计数器有同步十进制加法计数器ct74ls162、同步4位二进制加法计数器ct74ls163、同步十进制加/减计数器ct74ls190、同步4位二进制加/减计数器ct74ls191等。

2 反馈清零法

对于异步清零方式:应在输入第n个计数脉冲cp后,利用计数器状态sn进行译码产生清零信号加到异步清零端上,立刻使计数器清零,即实现了n计数器。

在计数器的有效循环中不包括状态sn,所以状态sn只在极短的瞬间出现称为过渡状态。

对于同步清零方式:应在输入第n-1个计数脉冲cp后,利用计数器状态sn-1进行译码产生清零信号,在输入第n个计数脉冲cp 时,计数器才被清零,回到初始零状态,从而实现n计数器。

可见同步清零没有过渡状态。

利用计数器的清零功能构成n计数器时,并行数据输入端可接任意数据,其方法如下:

①写出n计数器状态的二进制代码。

异步清零方式利用状态sn,同步清零方式利用状态sn-1。

②写出反馈清零函数。

③画逻辑图。

例1 试用ct74ls160的异步清零功能构成六进制计数器。

解:①写出sn的二进制代码。

sn=s6=0110

②写出反馈清零函数。

③画逻辑图。

如图1所示。

图1 用ct74ls160的异步清零功能构成六进制计数器

图2 用ct74ls162的同步清零功能构成六进制计数器

例2 试用ct74ls162的同步清零功能构成六进制计数器。

解:

①写出sn-1的二进制代码。

sn-1=s5=0101

②写出反馈清零函数。

③画逻辑图。

如图2所示

二、利用反馈置数法获得n计数器

1 集成计数器置数方式

异步置数方式:与计数脉冲cp无关,只要异步置数端出现置数信号,计数器立即被置数。

属于此类计数器有同步十进制加/减计数器ct74ls190/192、同步4位二进制加法/减计数器

ct74ls191/193。

同步置数方式:与计数脉冲cp有关,同步置数端获得置数信号后,计数器并不立刻被置数,还需要再输入一个计数脉冲才能将预置数置于计数器。

属于此类计数器有同步十进制加法计数器

ct74ls160/162、同步4位二进制加法计数器ct74ls161/163。

2反馈置数法

利用计数器的置数功能构成n计数器时,要确定计数器从某个预置数状态开始计数,并行数据输入端d3~d0接入计数器的计数起始数据,计满n个状态后产生置数信号,使计数器返回到预置数状态。

利用计数器的清零功能构成n计数器的方法如下:

①确定计数器计数状态和预置数状态。

②写出计数器状态的二进制代码。

当预置数为全0时,取前n 个计数状态,则异步置数方式利用状态sn,同步清零方式利用状态sn-1。

③写出反馈置数函数。

④画逻辑图。

例3 试用ct74ls161的同步置数功能构成十进制计数器。

解:ct74ls161是十六进制计数器,置数状态在0000~1111这16个状态中任选,因此实现的方案很多。

方法一:置全0法(前个状态计数)

①确定计数器计数状态和预置数状态。

取置数状态为s0=0000,预置数d3d2d1d0=0000,计数范围为0000~1001。

②写出计数器状态的二进制代码。

③写出反馈置数函数。

③画逻辑图。

如图3(a)所示。

(a)

(b)

图3 用ct74ls161的同步置数功能构成十进制计数器

(a)置全0法(前10个状态计数)

(b)co置数法(后10个状态计数)

方法二:co置数法(后n个状态计数)

用进位输出信号co作为预置数的控制信号。

m-n=16-10=(6)10=(0110)2,设预置数d3d2d1d0=0110,计数范围为0110~1111。

计到1111时,进位输出信号co=q3q2q1q0=1,通过非门产生一个置数信号加到同步置数端,即,在下一个计数脉冲cp到来时,把预置数d3d2d1d0=0110并行置入q3q2q1q0中,计数器返回到预置数状态q3q2q1q0=0110,从而实现了十进制计数。

电路如图3(b)。

三、大容量n进制计数器

当要求实现的计数器的计数模值超过单片计数器的计数范围

时,可将多片计数器级联起来,就可获得大容量进制计数器。

常用的方法有两种:

1 大模分解法

如果将模n可以分解为多个因数相乘(每个因数小于单片计数器的最大值),即,则可先用片计数器分别组成模值为n1、n2、…、nn的计数器,然后再将它们级联起来组成n进制计数器。

例4 试用两片ct74ls190构成五十进制计数器。

解:,个位片ct74ls190(1)组成十进制计数器(低位片);十位片ct74ls190(2)组成五进制计数器(高位片),然后级联组成五十进制计数器,电路如图4所示。

图中,级联采用串行进位方式,即将低位片ct74ls190(1)串行进位端的输出信号作为高位片计数器ct74ls190(2)的计数输入脉冲。

当十位计数器ct74ls190(2)计到5时,异步置数端端,计数器被置数到0,从而实现了五十进制计数。

图4 两片ct74ls190构成五十进制计数器

三、整体反馈置零或整体反馈置数法

例5 试用两片ct74ls161构成四十二进制计数器。

解:(1)将两片ct74ls161采用并行进位方式组成进制计数器。

(2)将256进制计数器采用整体反馈置零法构成42进制计数器。

42进制计数器对应的二进制代码,当计数器计到42时,计数器状态,反馈置零函数,这是经与非门输出低电平,使两片

ct74ls161同时置零,从而实现四十二进制计数,逻辑图如图5所

示。

图5 两片ct74ls161构成四十二进制计数器

参考文献:

[1] 杨志忠.数字电子技术基础【m】.北京:高等教育出版社.2010.

[2] 赵景波.数字电子技术应用基础【m】.北京:人民邮电出版社.2009.。