数字电路与逻辑设计习题及复习资料

数字电路和逻辑设计基础(含答案)

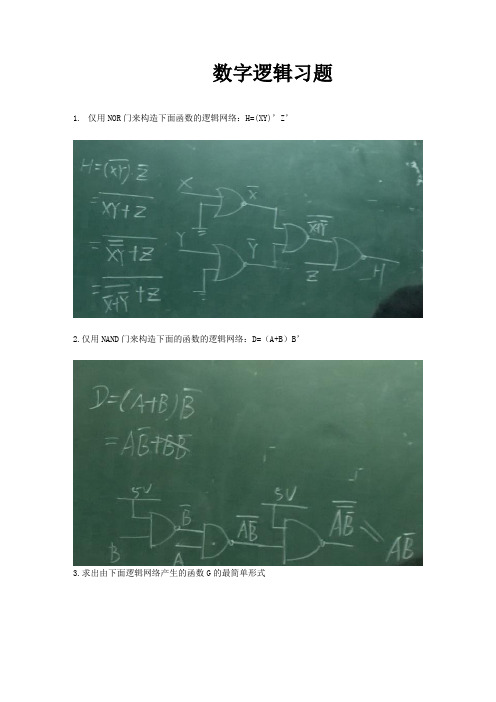

数字逻辑习题1.仅用NOR门来构造下面函数的逻辑网络:H=(XY)’Z’

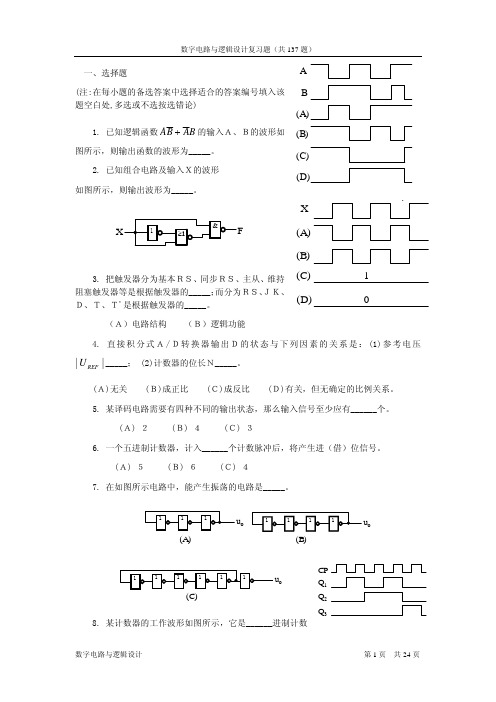

2.仅用NAND门来构造下面的函数的逻辑网络:D=(A+B)B’

3.求出由下面逻辑网络产生的函数G的最简单形式

4.卡诺图化简:G(A,B,C,D)=Σm(2,3,4,7,8,14,15)

5. 卡诺图化简:G(A,B,C,D)=Σm(0,1,3,4,6,7,12,13,14)

6.卡诺图化简:G(A,B,C,D)=Σm(0,4,5,6,7,8,13,14,15)

7.卡诺图化简:G(A,B,C,D)=Σm(1,2,3,4,6,7,9,12,13)

8.采用一个组合电路来控制一个十进制的七段显示,此电路有4个输入,并提供用压缩十进制数表示的4位代码(0(d)=0000,……8(d)=1000,9(d)=1001)。

7个输出用来定义哪段激活,以显示给定的十进制数

(1)写出这个电路的真值表

(2)用sop形式表示真值表

(3)用pos形式表示真值表

(4)写出各段化简的表达式

7.时序电路分析

补充:。

数字电路及逻辑设计复习题

B

&

&

FB

&

≥1

F

C

&

C

&

(C)

(D)

17. 维持阻塞D触发器电路中,当CP脉冲升沿过后,输入信号D改变,则其输出状态 ______。

(A) 不变; (B) 不定; (C) 随D而变

18. 要实现图中各 TTL 门电路输出端所示的逻辑关系,各电路的接法正确的有 ______________。

A B 悬空

)2。

16. 用与非门实现逻辑函数 Z=AB+AC 时,逻辑表达式应写成__________。

真值表

C 00001111 D1 0 0 1 1 0 0 1 1 D2 0 1 0 1 0 1 0 1 F1 F2 17. 填写如图 TTL 电路的真值表。

D1

&

&

F2

D2

EN F1

C

18. 用代数法可把逻辑函数 Z = AB + ABD + AC + BCD 化简为___________。

相异点

模拟多路转换器

数字多路转换器

11. 凡是使电流IL流入反相器的负载,叫做________,使IL从反相器流出的负载,叫做 ________。

数字电路与逻辑设计

第 6 页 共 24 页

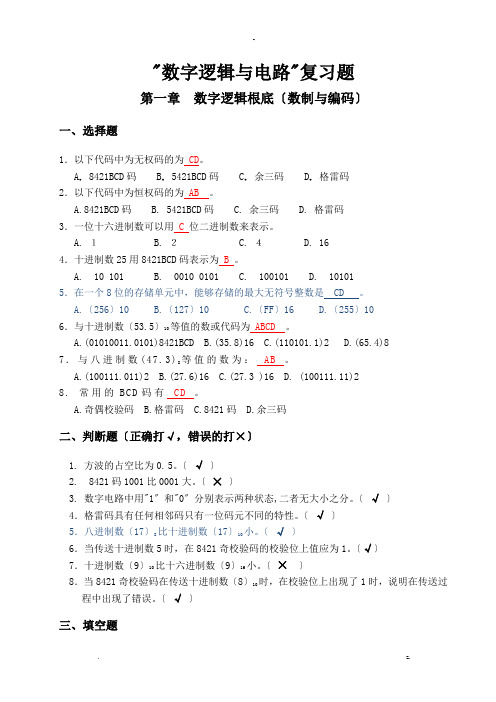

数字电路与逻辑设计复习题(共 137 题)

12. 基本RS、同步RS、主从JK和维持阻塞D四种不同结构的触发器中,可以作计 数器和移位寄存器的有____________________。

| U REF | _____; (2)计数器的位长N_____。

(A)无关 (B)成正比 (C)成反比 (D)有关,但无确定的比例关系。 5. 某译码电路需要有四种不同的输出状态,那么输入信号至少应有______个。

(完整版)数字电路与逻辑设计试题与答案,推荐文档

数字电路与逻辑设计(1)班级 学号 姓名 成绩一.单项选择题(每题1分,共10分)1.表示任意两位无符号十进制数需要( )二进制数。

A .6B .7C .8D .9 2.余3码10001000对应的2421码为( )。

A .01010101 B.10000101 C.10111011 D.111010113.补码1.1000的真值是( )。

A . +1.0111 B. -1.0111 C. -0.1001 D. -0. 10004.标准或-与式是由( )构成的逻辑表达式。

A .与项相或 B. 最小项相或 C. 最大项相与 D.或项相与5.根据反演规则,()()E DE C C A F ++⋅+=的反函数为( )。

A. E )]E D (C C [A F ⋅++=B. E)E D (C C A F ⋅++=C. E )E D C C A (F ⋅++= D. E)(D A F ⋅++=E C C 6.下列四种类型的逻辑门中,可以用( )实现三种基本运算。

A. 与门B. 或门C. 非门D. 与非门7. 将D 触发器改造成T 触发器,图1所示电路中的虚线框内应是( )。

图1A. 或非门B. 与非门C. 异或门D. 同或门8.实现两个四位二进制数相乘的组合电路,应有( )个输出函数。

A . 8 B. 9 C. 10 D. 11 9.要使JK 触发器在时钟作用下的次态与现态相反,JK 端取值应为( )。

A .JK=00 B. JK=01 C. JK=10 D. JK=11 10.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要( )个异或门。

A .2 B. 3 C. 4 D. 5二.判断题(判断各题正误,正确的在括号内记“∨”,错误的在括号内记“×”,并在划线处改正。

每题2分,共10分)1.原码和补码均可实现将减法运算转化为加法运算。

( )2.逻辑函数7),M(1,3,4,6,C)B,F(A,∏=则m(0,2,5)C)B,(A,F ∑=。

数字电路与逻辑设计习题_4第四章组合逻辑电路剖析

数字电路与逻辑设计习题_4第四章组合逻辑电路剖析第四章组合逻辑电路一、选择题1.下列表达式中不存在竞争冒险的有。

A.Y=B +A BB.Y=A B+B CC.Y =A B C +ABD.Y =(A+B )A D 2.若在编码器中有50个编码对象,则要求输出二进制代码位数为位。

A.5B.6C.10D.503.一个16选一的数据选择器,其地址输入(选择控制输入)端有个。

A.1B.2C.4D.16 4.下列各函数等式中无冒险现象的函数式有。

A.B A AC C B F ++= B.B A BC C A F ++=C.B A B A BC C A F +++=D.C A B A BC B A AC C B F +++++=E.B A B A AC C B F +++= 5.函数C B AB C A F ++=,当变量的取值为时,将出现冒险现象。

A.B=C=1B.B =C=0C.A =1,C=0D.A =0,B=0 6.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻辑表达式为Y = 。

A.3X A A X A A X A A X A A 01201101001+++B.001X A AC.101X A AD.3X A A 017.一个8选一数据选择器的数据输入端有个。

A.1 B.2 C.3 D.4 E.8 8.在下列逻辑电路中,不是组合逻辑电路的有。

A.译码器B.编码器C.全加器 D.寄存器9.八路数据分配器,其地址输入端有个。

A.1B.2C.3D.4E.8 10.组合逻辑电路消除竞争冒险的方法有。

A. 修改逻辑设计B.在输出端接入滤波电容C.后级加缓冲电路D.屏蔽输入信号的尖峰干扰 11.101键盘的编码器输出位二进制代码。

A.2B.6C.7D.812.用三线-八线译码器74LS 138实现原码输出的8路数据分配器,应。

A.A ST =1,B ST =D ,C ST =0 B. A ST =1,B ST =D ,C ST =D C.A ST =1,BST =0,CST =D D.A ST =D ,BST =0,CST =013.以下电路中,加以适当辅助门电路,适于实现单输出组合逻辑电路。

数字电路与逻辑设计习题及参考答案 精品

数字电路与逻辑设计习题及参考答案一、选择题1. 以下表达式中符合逻辑运算法则的是 D 。

A.C ·C=C 2B.1+1=10C.0<1D.A+1=12. 一位十六进制数可以用 C 位二进制数来表示。

A . 1B . 2C . 4D . 163. 当逻辑函数有n 个变量时,共有 D 个变量取值组合?A. nB. 2nC. n 2D. 2n4. 逻辑函数的表示方法中具有唯一性的是 A 。

A .真值表 B.表达式 C.逻辑图 D.状态图5. 在一个8位的存储单元中,能够存储的最大无符号整数是 D 。

A .(256)10B .(127)10C .(128)10D .(255)106.逻辑函数F=B A A ⊕⊕)( = A 。

A.BB.AC.B A ⊕D. B A ⊕7.求一个逻辑函数F 的对偶式,不可将F 中的 B 。

A .“·”换成“+”,“+”换成“·”B.原变量换成反变量,反变量换成原变量C.变量不变D.常数中“0”换成“1”,“1”换成“0”8.A+BC= C 。

A .A+B B.A+C C.(A+B )(A+C ) D.B+C9.在何种输入情况下,“与非”运算的结果是逻辑0。

DA .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是110.在何种输入情况下,“或非”运算的结果是逻辑1。

AA .全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为111.十进制数25用8421BCD 码表示为 B 。

A .10 101B .0010 0101C .100101D .1010112.不与十进制数(53.5)10等值的数或代码为 C 。

A .(0101 0011.0101)8421BCDB .(35.8)16C .(110101.11)2D .(65.4)813.以下参数不是矩形脉冲信号的参数 D 。

A.周期B.占空比C.脉宽D.扫描期14.与八进制数(47.3)8等值的数为: BA. (100111.0101)2B.(27.6)16C.(27.3 )16D. (100111.101)215. 常用的BCD码有 D 。

数字逻辑及电路复习题及答案

"数字逻辑与电路"复习题第一章数字逻辑根底〔数制与编码〕一、选择题1.以下代码中为无权码的为 CD。

A. 8421BCD码B. 5421BCD码C.余三码D.格雷码2.以下代码中为恒权码的为 AB 。

A.8421BCD码B. 5421BCD码C. 余三码D. 格雷码3.一位十六进制数可以用 C 位二进制数来表示。

A. 1B. 2C. 4D. 164.十进制数25用8421BCD码表示为 B 。

A. 10 101B. 0010 0101C. 100101D. 101015.在一个8位的存储单元中,能够存储的最大无符号整数是 CD 。

A.〔256〕10B.〔127〕10C.〔FF〕16D.〔255〕10 6.与十进制数〔53.5〕10等值的数或代码为 ABCD 。

A.(01010011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)87.与八进制数(47.3)8等值的数为:A B 。

A.(100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)28.常用的BC D码有C D 。

A.奇偶校验码B.格雷码C.8421码D.余三码二、判断题〔正确打√,错误的打×〕1. 方波的占空比为0.5。

〔√〕2. 8421码1001比0001大。

〔×〕3. 数字电路中用"1〞和"0〞分别表示两种状态,二者无大小之分。

〔√〕4.格雷码具有任何相邻码只有一位码元不同的特性。

〔√〕5.八进制数〔17〕8比十进制数〔17〕10小。

〔√〕6.当传送十进制数5时,在8421奇校验码的校验位上值应为1。

〔√〕7.十进制数〔9〕10比十六进制数〔9〕16小。

〔×〕8.当8421奇校验码在传送十进制数〔8〕10时,在校验位上出现了1时,说明在传送过程中出现了错误。

〔√〕三、填空题1.数字信号的特点是在时间上和幅值上都是断续变化的,其高电平和低电平常用 1和 0来表示。

数字电路与逻辑设计复习题

22. (8A)H=(

)10

23. 数制转换及表示:(BCD 码为 8421BCD 码)

(1) (1110001)2=( (2) (35.125)10=(

)10=(

)16

)2=(

)BCD

24. 用代数法可把逻辑函数 Z = AB + ABD + AC + BCD 化简为

_________________________。

A B 悬空

&

F = AB

A B

(A)

& F = AB

Aபைடு நூலகம்B

悬空

(B)

≥1 F = A+B

(C)

A B

≥1 F = A+B

A B

≥1 F = A+B

100Ω

5.1KΩ

(D)

(E)

数字电路与逻辑设计

第 2 页 共 15 页

数字电路与逻辑设计复习题

19. 已知某组合电路的卡诺图如图所示,则此组合电路为_____。

25. 要把逻辑函数 Z = A BC DE 用与或非门来实现,应写成__________________。

26. 由n个D触发器构成的环形计数器,其有效计数状态共有_____个。 三、作图题 (注:请按题目要求绘出波形图或电路图等)

1. 如图(a)所示,电路是由 T’触发器构成的计数电路,试画出与图(b)时钟脉冲

输出

P1

P2

10

11

00

00

输入 ABC 100 101 110 111

输出 P1 P2 11 01 00 01

3. 已知A、B、C、D的波形,如图所示。请画出逻辑函数F的波形。已知:

数字电路与逻辑设计复习

第二章 逻辑函数及其简化 公式法化简

① F=(A⊕B)(B⊕C) ●A+B+A+C

解: F=[(A⊕B)(B⊕C) +A+B] ●(A+C) =[(AB+AB)(BC+BC)+A+B) ●(A+C)

第二章 逻辑函数及其简化 1 若A、B、C、D、E为某逻辑函数输入变量,函数的最大项表达式 所包含的最大项的个数不可能是: A 32 B 15 C 31 D 632 2 以下表达式中符合逻辑运算规则的是: A. C●C=C2 B. 1+1=10 C. 0﹤1 D. A+1=1 3 符合逻辑运算规则的是: A. 1×1=1 B. 1+1=10 C. 1+1=1 D. 1+1=2 4 逻辑函数F=AB+CD+BC的反函数F是:_____;对偶函数F﹡是:____; 5 逻辑代数的三个重要规则是:_________,__________,_________ 当逻辑函数有n个变量时,共有____种变量取值组合。 6 异或与同或在逻辑上正好相反,互为反函数,对吗? 7 逻辑变量的取值,1比0大,对吗? 8 F=A⊕B⊕C=A⊙B⊙C,对吗? 答案:1. D 2. D 3. C 4. ___ 5. ____ ____ 6. √ 7. × 8. √

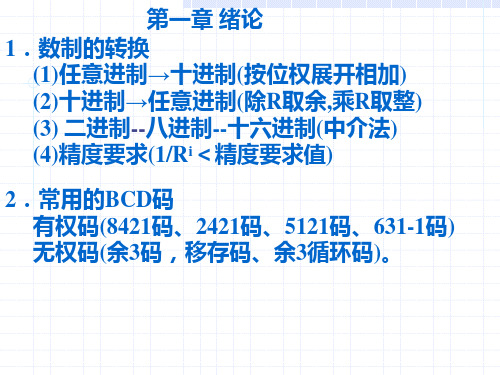

第一章 绪论 1.数制的转换 (1)任意进制→十进制(按位权展开相加) (2)十进制→任意进制(除R取余,乘R取整) (3) 二进制--八进制--十六进制(中介法) (4)精度要求(1/Ri<精度要求值) 2.常用的BCD码 有权码(8421码、2421码、5121码、631-1码) 无权码(余3码,移存码、余3循环码)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电路与逻辑设计模拟题一、 选择题1、(36.7)10 的8421BCD 码为。

() A 、(0110110.101)8421BCD B 、(0011110.1110)8421BCD C 、(00110110.0111)8421BCD D 、(110110.111)8421BCD2、与(6B.2)16相对应的二进制数为() A 、(1101011.001)2 B 、(01101010.01)2 C (11101011.01)2 D 、(01100111.01)23、在BCD 码中,属于有权码的编码是()A 、余3码B 、循环码C 、格雷码D 、8421码 4、如图1-1所示门电路,按正逻辑体制,电路实现的逻辑式F=()5、如果1-2所示的波形图,其表示的逻辑关系是()6、下列器件中,属于组合电路的有()A 、计数器和全加器B 、寄存器和比较器C 、全加器和比较器D 、计数器和寄存器7、异或门F=A ⊕B 两输入端A 、B 中,A=0,则输出端F 为() A 、A ⊕B B 、B C 、B D 、08、已知4个组合电路的输出F1~F4的函数式非别为:F 1=AB+A C ,F 2=AB+A CD+BC ,F 3=A B +B C ,F 4=(A+B )·(A +C ),则不会产生竞争冒险的电路是( ) A 、电路1 B 、电路2 C 、电路3 D 、电路4 9、边沿触发JK 触发器的特征方程是() A 、θ1+n =J nθ+k nθ B 、θ1+n =J nθ+k nθ C 、θ1+n =J nθ+k n θ D 、θ1+n =J nθ+K nθ10、用n 个出发器件构成计数器,可得到的最大计数长度为( ) A 、n B 、2n C 、n 2D 、2n11、(011001010010.00010110)8421BCD 所对应的十进制数为() A 、(652.16)10 B 、(1618.13)10C 、(652.13)10D 、(1618.06)1012、八进制数(321)8对应的二进制数为() A 、(011010001)2 B 、(110011)2 C 、(10110111)2 D 、(1101011)213、与(19)10相对应的余3BCD 码是() A 、(00101100)余3BCD B 、(01001100)余3BCDC 、(00110101)余3BCD D 、(01011010)余3BCD 14、如图1-3所示门电路,按正逻辑体制,电路实现的逻辑关系F=() A 、C B A ⋅⋅ B 、C B A ⋅⋅ C 、A+B+C D 、C B A ++图1-315、如图1-4所示的波形图表示的逻辑关系是() A 、F=B A ⋅ B 、F=A+B C 、F=B A ⋅ D 、F=B A +16、已知逻辑函数的卡诺图如图1-5所示能实现这一函数功能的电路是()17、组合逻辑电路的特点是()A 、含有存储元件B 、输出、输入间有反馈通路C 、电路输出与以前状态有关D 、全部由门电路构成18、函数F=C B AB C A ⋅++,当变量取值为(),不会出现冒险现象。

A 、B=C=1 B 、B=C=0 C 、A=1,C=0 D 、A=B=0 19、由与非门组成的基本RS 触发器的特性方程是()A 、⎪⎩⎪⎨⎧=++=+100001S R R S n n θθB 、⎩⎨⎧=++=+100001S R R S n n θθC 、⎩⎨⎧=++=+100001S R R S n n θθD 、⎪⎩⎪⎨⎧=++=+100001S R R S n n θθ20、4个触发器构成8421BCD码计数器,共有()个无效状态。

A、6B、8C、10D、不定二、填空题1、(67)10所对应的二进制数为和十六进制数为。

2、逻辑函数F=AB+A B的对偶函数Fˊ=3、在数字逻辑电路中,三极管主要工作在两种稳定状态。

4、如图2-1所示电路能实现的逻辑关系是F= 。

5、CMOS传输门组成的电路如图2-2所示,当C=0时,U0= ,当C=1时,U0= 。

6、四选一数据选择器,AB为地址信号,I0=I3=1,I1=C,I2=C,当AB=00时,输出F= ;当AB=10时,输出F= 。

7、3线―8线译码器如图2-3所示,他所实现函数F= 。

8、时序逻辑电路一般由和两分组成。

9、半导体存储器,根据用户对存储器进行操作分为和两大类。

10、十进制数(56)10转换为二进制数为和十六进制数为11、逻辑函数F=A·(B+C)·1的反函数F=12、由于二极管具有特性,因此可作为开关元件使用。

13、由oc门构成的电路如图2-4所示,F的表达式为14、如图2-5所示电路中,F 的表达式为15、八选一数据选择器电路如图2-6所示,他所实现函数F=16、3线-8线译码器电路如图2-7所示,它所实现函数 F 1= ;F 2= 。

17、JK 触发器,要使n n θθ=+1,则输入J=K= ;或J= ,K=18、 型时序电路的输出不仅与电路内部的状态有关,且与外输入有关。

型时序电路的输出仅与电路内部的状态有关。

19、RAM 由若干基本存储电路组成,每个基本存储电路可存放 。

三、分析化简题 1、化简函数(1)Y 1=(B A B A +·C+C B A )·(AD+BC )(代数法化简)(2)Y2=AB+B D +BCD+A B C (卡诺图化简) (3)Y 3(A 、B 、C 、D )=)14,12,4,2,1(∑m +∑)10,9,8,7,6,5(φ(∑m 为函数Y 的最小项和,∑φ为任意项和)(卡诺图化简) 2、电路如图3-1所示,分析电路逻辑功能。

3、分析图3-2所示电路的逻辑功能,写出电路的驱动方程,状态方程和输出方程,画出电路的状态转换图和时序图。

4、图3-3所示电路由555定时器构成,它是什么电路?已知定时电阻R=11 K Ω,要求输出脉冲宽度t w =1秒,试计算定时电容C 的数值?5、图3-4电路中74LS290已接成异步十进制计数器,θ0为最低位,θ3为最高位,设计数器输出高电平为 3.5v ,低电平为0v 。

当θ3θ2θ1θ0=0101时,求输出电压U 0的值?6、化简函数(1)Y 1=BD B A D C A B A +++⋅ (代数法化简) (2)Y 2=CD D A C A ++ (卡诺图化简) (3)Y 3(A 、B 、C 、D )=∑∑+)、、、、、()、、、、(15141312111097531φm (∑m 为函数Y3的最小项和,∑φ为任意项和)(卡诺图化简) 7、电路如图3-5所示,分析电路逻辑功能。

(本题8分)8、分析图3-6所示电路的逻辑功能,写出电路的驱动方程,状态方程和输出方程,画出电路的状态转换图,并说明该电路能否自启动。

9、由555定时器构成的多谐振动器如图3-7所示,已知R 1=1K Ω,R2=8.2K Ω,C=0.1μF 。

试求脉冲宽度T 1,振荡频率f 和占空比q 。

10、图3-8所示电路是倒T 形电阻网络D/A 转换器,已知R=10K Ω,U REF =10V 。

试求:(1)U 0输出范围;(2)当D 3D 2D 1D 0=0110时,U 0=?四、设计题1、用如下器件实现函数Y=A ⊕B ⊕C ,画出逻辑图(或阵列结构图)。

(1)与非门;(2)3线―8线译码器(74LS138)和与非门; (3)八选一数据选择器(74LS151); (4)ROM 的阵列结构图。

2、试用置零法将4位同步二进制计数器74LS161接成十三进制计数器,并画出状态转换图,可以附加必要的门电路。

3、用如下器件实现函数Y=(A ⊕B )∙C+C B A ⋅⊕画出逻辑图(或阵列结构图)。

(1)与非门; (2)3线-8线译码器(74LS138)和与非门; (3)八选一数据选择器(74LS151); (4)ROM 的阵列结构图。

4.试用置零法将4位同步二进制计数器74LS161接成八进制计数器,并画出状态转换图,可以附加必要的门电路。

数字电路与逻辑设计模拟参考答案一、1、C2、A3、D4、B5、C6、C7、B8、B9、C 10、D 11、A 12、A 13、B 14、C 15、D 16、D 17、D 18、B 19、C 20、A 二、1、(1000011)2 ,(43)162、(A+B )·(B A +)3、饱和及截止4、A C B C ⋅+⋅5、U i1,U i26、1,C7、m 1+m 3+m 4+m 5+m 68、1 9、组合逻辑电路,存储电路 10、只读存储器,随机读写存储器 11、(111000)2,(38)16 12、C B A ⋅+ 13、单向导电14、F=A ⊕B 15、F=B A +=B A 16、C B C A B A ++ 或 B A C A C B ++18、1,nθ nθ 19、米利,17、m 1+m 2+m 3+m 7,m 3+m 5+m 6+m 7摩尔20、一位二值代码三、1、(1)Y 1=ACD+ABC (2)Y 2 =AB+B D +A CD(3)Y3=B D +C D +A C D2、(1)写出逻辑函数式F=ABC C ABC B ABC A ⋅+⋅+⋅=)(C B A ABC ++=ABC+C B A ++=ABC+A B C (2(3)由真值表可知当ABC=000或111时 F=1,否则F=0 所以该电路为“一致电路” 3、(1)驱动方程⎪⎩⎪⎨⎧==1010K J nθ ⎩⎨⎧==1101K J n θ (2)状态方程⎪⎩⎪⎨⎧==++nn n n on n 1011110θθθθθθ (3)输出方程 Z=n1θ(4)状态转换图 Zθ1θ01(5)时序图此电路是一个同步三进制加法计数器电路可自启动。

4、构成单稳态触发器 ∵t w =1.1RC ∴C=R 1.11=310101.11⨯⨯=0.083⨯10-3F=83F μ 5、I Z =(15.33θ+25.32θ+45.31θ+85.30θ) U 0=―R F I Z =―2(15.33θ+25.32θ+45.31θ+85.30θ) 当θ3θ2θ1θ0=0101时 U 0=―(25.3+85.3)⨯2=―(3.5+0.875)=―4.375V 6、(1)Y 1=BD B A D C A B A ⋅++⋅=D C A B A +=A+D C A B +=A+B (2)Y 2=D C A +(3)Y 3=D7、(1)写出输出函数表达式))(()(B A B A B A AB AB B AB A AB B AB A F ++=+=+⋅=⋅⋅=1 =B A B A +=BA ⊕B A AB F ⋅==2(2)列真值表(3)由真值表可知,F 1和AB 是异或关系,相当于两个一位二进制数相加所得的本位和数;F 2是A 和B 的逻辑与,相当于两数相加的进位数,所以该电路是由两个一位二进制数相加的加法电路,又称为半加器。