高速、多路LVDS交叉开关

LVDS原理及设计指南

LVDS原理及设计指南LVDS全称为低压差分信号(Low Voltage Differential Signaling),是一种高速串行接口技术,广泛应用于电子设备中进行高速数据传输。

LVDS主要通过两对差分信号进行数据传输,其中一对信号传输高电平信号,另一对信号传输低电平信号,通过差分运算来提高抗干扰能力和抗噪声能力,以实现高质量的数据传输。

LVDS的工作原理如下:1.发送端:将输入信号通过电流驱动压缩成低压差分信号,并通过双绞线传输给接收端。

2.传输线路:使用双绞线进行数据传输,利用差分运算来抵消传输线上的共模噪声和反射噪声。

3.接收端:对接收到的低压差分信号进行解码,还原成原始的输入信号。

设计LVDS接口时需要注意以下几点:1.信号线路的设计:为了保证信号的完整性和稳定性,需要控制信号线的阻抗匹配,减小信号线的长度和延迟,并避免信号线与高频噪声信号线的交叉和平行布线。

2.布线和PCB设计:保持信号线的长度均匀,并尽量使用同一层或相邻层进行差分信号线布线,以减小信号线之间的不平衡和串扰。

3.电源和接地:为了提供噪声的抑制和信号的稳定性,需要使用低噪声电源和低阻抗接地。

4.EMI抑制:由于LVDS接口传输速率高,会引起较大的电磁辐射干扰,因此需要在设计中加入适当的EMI抑制措施,如电磁屏蔽、地线设计和滤波器等。

5.信号匹配:为了保证所发送信号的完整性和稳定性,需要将发送端与接收端之间的差分阻抗匹配,以最大限度地减小信号反射和串扰。

总之,LVDS是一种高速串行接口技术,通过差分运算进行数据传输,具有抗噪声和抗干扰能力强的特点。

在设计LVDS接口时需注意信号线路的设计、布线和PCB设计、电源和接地、EMI抑制以及信号匹配等方面,以保证高质量的数据传输。

LVDS原理及设计指南

LVDS原理及设计指南LVDS(Low Voltage Differential Signaling)是一种低电压差分传输技术,常用于高速数据通信和时钟分配系统。

它通过使用两条平衡的信号线(一个正极和一个负极)来传输数据,以减少噪音干扰,提供更高的数据传输速率和更低的功耗。

LVDS的原理是将要传输的数据进行编码,然后在发送端将编码后的信号通过一个差分发射器发送出去。

在接收端,差分接收器将接收到的信号进行解码,并还原为原始数据。

差分发射器和差分接收器之间通过两条平衡的信号线相连,使得信号可以在传输过程中保持高的抗干扰能力。

为了实现高速数据传输和低功耗,设计LVDS系统时需要注意以下几点:1.选择合适的传输线:LVDS系统常用的传输线有两对铜排、双绞线和屏蔽电缆。

传输线的选择应根据系统需求和环境条件来确定,以保证信号传输的稳定性和可靠性。

2.保持信号的差分平衡:在设计LVDS系统时,传输线的长度和阻抗应保持一致,以保证差分信号的平衡性。

同时,在PCB设计中,需要采取合适的布线方式,如使用相邻层的信号层和地层进行屏蔽,以减少信号的串扰。

3.电源和地线的设计:为了保证LVDS系统的稳定性和可靠性,需要为差分发射器和差分接收器提供稳定的电源和地线。

一般应采用低噪声的电源和地线设计,并保持电源和地线与传输线相互独立,以防止互相干扰。

4.噪声抑制和滤波措施:在LVDS系统中,噪声干扰是一个常见的问题。

为了减少噪声的影响,可以采用电源滤波器、地线滤波器、抗干扰电容和电感等措施,以有效抑制噪声的干扰。

5.时钟分配的设计:对于需要传输时钟信号的LVDS系统,时钟分配的设计尤为重要。

时钟线应尽量短,以保证时钟信号的稳定性和准确性。

同时,需要采用低噪声的时钟源,并根据时钟分配的延时要求进行恰当的布线和抗干扰措施。

6.PCB设计布局:在LVDS系统的PCB设计中,需要合理规划和布局不同电路模块的位置,以减少信号的干扰和串扰。

完整版LVDS接口详解

1 . LVDS输出接口归纳液晶显示器驱动板输出的数字信号中,除了包括RGB 数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可高出28MHz 。

采用 TTL 接口,数据传输速率不高,传输距离较短,且抗电磁搅乱(EMI )能力也比较差,会对RGB 数据造成必然的影响;别的,TTL 多路数据信号采用排线的方式来传达,整个排线数量达几十路,不仅连接不便,而且不适合超薄化的趋势。

采用 LVDS 输出接口传输数据,能够使这些问题瓜熟蒂落,实现数据的高速率、低噪声、远距离、高正确度的传输。

那么,什么是 LVDS 输出接口呢? LVDS ,即 Low Voltage Differential Signaling ,是一种低压差分信号技术接口。

它是美国 NS 公司(美国国家半导体公司)为战胜以 TTL 电平方式传输宽带高码率数据时功耗大、 EMI 电磁搅乱大等缺点而研制的一种数字视频信号传输方式。

LVDS 输出接口利用特别低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,能够使得信号在差分PCB线或平衡电缆上以几百Mbit / s 的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中获取了广泛的应用。

2. LVDS 接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的 17L电平并行RGB数据信号和控制信号变换成低电压串行LVDS信号,尔后经过驱动板与液晶面板之间的柔性电缆(排线)将信号传达到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号LVDS接口电路的变换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

SCAN90CP02型LVDS交叉点开关功能及应用

路[6J。由于许多高速的LVDS 互连线路都采用交流

电祸合 ( 即电容藕合 ) 的设计,以便消除驱动器与 远程接收器之间的信号偏移,因此确保新技术能够

支持 1149.6 标准便显得非常重要。 SCAN90CP02 芯片可以支持的测试范围包括

让业界可以测试先前无法测试的交流电藕合互连线

2 超高速交叉点开关 SCAN90CP02 介绍

SCAN90CP02型电路是美国国家半导体公司推 出的 1.5Gb/s 的 2x2 低压差分信号传输模拟交叉点

开关。其高速数据通路和直通引脚可使电路内部的 抖动达到最小。当信号在有损的背板和电缆上传输 时, 其可配置的预增强功能( 0/25%/50%/ 100%可选 )

能预见到如此 的结果。

总第 90 期

潘莉莉等: SCAN90CP02 型LVDS 交叉点开关功能及应用

IEEE 1149.6 标准确定了把系统的边界扫描能 力应用于测试带有不同信号的一系列高速互联总线

连。 由于SCAN90CP02 设有预增强功能, 因此不但

可以执行正常的开关功能, 而且可作为缓冲器使用, 以便将现有的 FPGA, ASIC 及串行/解串器( SerDes ) 等的 LVDS 信号放大。另外,该电路的 LVDS 输出

声和低功耗。LVDS 已广泛应用于接口器件和现场

在同样的边界工具环境下实施一系列其他测试和系 统内编程功能。这提高了效率,降低了开发和生产

成本[2)。 用旧的方法, 为同一个设计要做 3 次测试: 首先是原型测试; 然后是制造测试; 最后是现场修

正。现在,工程师们可以用边界扫描做为贯串于整 个产品生命周期的统一的测试方法。 边界扫描在线路板测试的所有方面都能带来有 益的效果。首先,测试准备时间缩短了,这是因为 基于扫描的测试是高度 自 动化的,在线路板布局之 前,测试就可以被很快地准备好,并预先评估其测 试效果 ; 第二,因为边界扫描不需要很多的物理测 试点, 它可以减少或省去用于夹具的费用,并简化

NS推出全新低电压差分信号传输(LVDS )2x2交叉开关

NS推出全新低电压差分信号传输(LVDS )2x2交叉开关美国国家半导体公司(National Semiconductor Corporation)宣布推出一系列全新的达到汽车应用等级的低电压差分信号传输(LVDS )2x2交叉开关交叉开关,具备高达3.125Gbps的数据率。

该系列PowerWise 交叉开关的每通道功耗仅为105mW,符合美国国家半导体PowerWise标准,搭配美国国家半导体的LVDS驱动器和接收器,可以极大地节省功耗及降低散热量。

特别适用于车载娱乐信息系统、仪表板显示器、GPS定位导航系统、以及后部/车道辅助泊车摄影预警系统。

美国国家半导体LVDS系列芯片经认证符合汽车电子设备委员会(AEC)制定的AEC-Q100标准。

作为稳定可靠的差分信号传输技术,LVDS非常适合用于车载电子系统,不仅具有功耗低,带宽高,电磁辐射少等特点,而且宽广的共模电压范围和差分信号使它具有不易受噪声干扰的特点,同时具有电磁辐射少(EMI)及抗噪音能力,因为许多汽车的重要装置,如引燃系统、传动管理、娱乐信息系统及安全装置都已改用电子系统控制。

新推出的LVDS系列芯片共有8款,包括3款2x2交叉开关、一组单/双通道差分驱动器差分驱动器和接收器,以及一对双通道的驱动器及接收器。

所有芯片都符合AEC-Q100第3级标准的规定,并保证可在高达摄氏85度的温度下正常工作:PowerWise DS25CP102Q 2x2 LVDS交叉开关抖动性能(6ps 典型值,3.125Gbps传输率传输率)。

此外,这款交叉点开关电路还提供发送端预加重及接收端均衡两种功能可供选择,以延长信号通过电缆或FR-4 底板的传送距离。

该芯片采用16引脚的 LLP 封装。

PowerWise DS25CP152Q 2x2 LVDS 交叉开关无信号调整功能调整功能,但仍具有业界领先的抖动性能,且数据传输率高达3.125Gbps.该芯片采用16引脚的LLP封装。

GM8122 T45_数据手册

ps

20

40

ps

输入为VID=200mV、VIC=1.2V、50%占空系数、 f=1000Mbps,RL=75Ω,CL=5pF

650

1000

ps

输入为VIC=1.2V、VID=200mV、50%占空系数、 f=1MHz、tr/tf≤500ps,RL=75Ω

650

1000

ps

输入为VIC=1.2V、VID=200mV、50%占空系数、 f=1MHz、tr/tf≤500ps,RL=75Ω

文件编号 GM8122 T45

代号

T45

总页数 共 页

GM8122 型高速 LVDS 2X2 交叉开关 数据手册

版 本 号: 拟 制: 审 核: 批 准:

成都国Байду номын сангаас电子技术股份有限公司 08 年 06 月 30 日

成都国腾电子技术股份有限公司

GM8122

GM8122

版本记录:1.0

新旧版本改动比较:

输入为VIC=1.2V、VID=200mV、50%占空系数、

-

- tr/tf≤100p(s 10%到 90%);f=1000MHz(IN0),

f=500MHz(IN1);RL=75Ω

6 机械尺寸

4

成都国腾电子技术股份有限公司

GM8122

本器件采用 16 引线的陶瓷双面引线扁平封装(F16X2),外形尺寸参照 GB/T 7092-1993 中 7.1 的规定。外壳外形按图 3 规定。

9 10 11 12

方向 引脚名

NC

OUT1- Out OUT1+ Out GND Out

说明

悬空 LVDS 输出 1 负端 LVDS 输出 1 正端

lvds概述

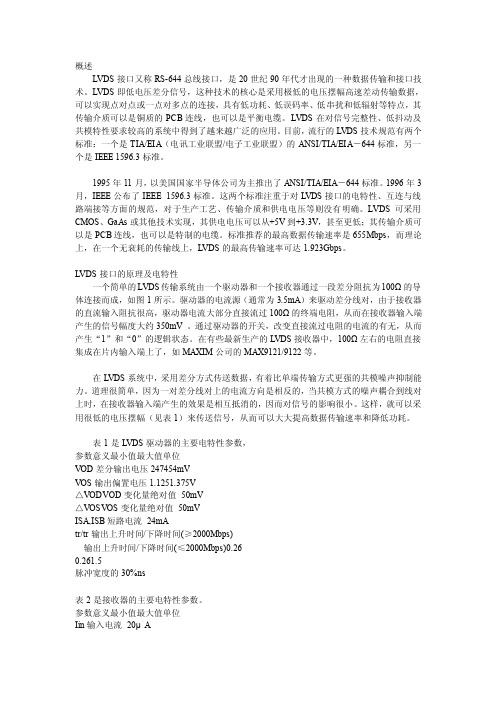

概述LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。

LVDS即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。

目前,流行的LVDS技术规范有两个标准:一个是TIA/EIA(电讯工业联盟/电子工业联盟)的ANSI/TIA/EIA-644标准,另一个是IEEE 1596.3标准。

1995年11月,以美国国家半导体公司为主推出了ANSI/TIA/EIA-644标准。

1996年3月,IEEE公布了IEEE 1596.3标准。

这两个标准注重于对LVDS接口的电特性、互连与线路端接等方面的规范,对于生产工艺、传输介质和供电电压等则没有明确。

LVDS可采用CMOS、GaAs或其他技术实现,其供电电压可以从+5V到+3.3V,甚至更低;其传输介质可以是PCB连线,也可以是特制的电缆。

标准推荐的最高数据传输速率是655Mbps,而理论上,在一个无衰耗的传输线上,LVDS的最高传输速率可达1.923Gbps。

LVDS接口的原理及电特性一个简单的LVDS传输系统由一个驱动器和一个接收器通过一段差分阻抗为100Ω的导体连接而成,如图1所示。

驱动器的电流源(通常为3.5mA)来驱动差分线对,由于接收器的直流输入阻抗很高,驱动器电流大部分直接流过100Ω的终端电阻,从而在接收器输入端产生的信号幅度大约350mV 。

通过驱动器的开关,改变直接流过电阻的电流的有无,从而产生“1”和“0”的逻辑状态。

在有些最新生产的LVDS接收器中,100Ω左右的电阻直接集成在片内输入端上了,如MAXIM公司的MAX9121/9122等。

在LVDS系统中,采用差分方式传送数据,有着比单端传输方式更强的共模噪声抑制能力。

LVDS信号的工作原理和特点

LVDS信号的工作原理和特点LVDS(Low Voltage Differential Signaling)是一种低电压差分信号传输技术,广泛应用于高速数据传输领域。

它通过将信号分为正负两个相位的差分信号来传输数据,具有较高的抗干扰能力和较低的功耗。

本文将详细介绍LVDS信号的工作原理和特点。

一、LVDS信号的工作原理LVDS信号的工作原理基于差分传输原理,即通过正负两个相位的差分信号来传输数据。

LVDS信号通常由一个差分发送器和一个差分接收器组成。

1. 差分发送器:差分发送器将输入的信号分为正负两个相位的差分信号。

正相位信号和负相位信号的电平差值代表了传输的数据信息。

正相位信号和负相位信号的波形形状相同,但电平相反。

2. 差分接收器:差分接收器接收到正负两个相位的差分信号后,通过比较两个信号的电平差值来恢复出原始的数据信息。

差分接收器具有较高的抗干扰能力,可以有效地反抗传输过程中的噪声和干扰。

二、LVDS信号的特点1. 高速传输:LVDS信号具有较高的传输速率,通常可以达到几百兆比特每秒(Mbps)甚至更高的速率。

这使得LVDS信号在高速数据传输领域得到广泛应用,例如在显示器、摄像头、通信设备等领域。

2. 低功耗:LVDS信号的传输电压较低,通常为2.5伏特(V)或者3.3伏特(V),相比于其他传输技术,LVDS信号具有较低的功耗。

这使得LVDS信号在电池供电设备中得到广泛应用,例如在便携式电子设备、无线通信设备等领域。

3. 抗干扰能力强:LVDS信号采用差分传输原理,具有较高的抗干扰能力。

差分传输可以有效地反抗传输过程中的噪声、干扰和信号失真,提高了数据传输的可靠性和稳定性。

4. 传输距离远:由于LVDS信号采用差分传输原理,信号的传输距离可以达到几十米甚至更远。

这使得LVDS信号在需要远距离传输数据的场合得到广泛应用,例如在工业自动化、医疗设备等领域。

5. 灵便性强:LVDS信号的传输速率、电压等参数可以根据具体需求进行调整和配置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

行接 口设置 ,能够 很容易地集 成到汽车

总线架 构 内。输 出还 可 以置为 高阻 态 ,

电话 :0 0 6 l - 2 8 1 — 5 7 2 8

h t //s n. xp.o tp: c n c m

以 支 持 多 个 开 关 并 联 使 用 。 AX9 / 高达 0 6 。此外 ,即使接收信号 的眼 M 2 1 3 .UI

MAX9 3 / 14 MAX9 3 提供 可升级的方 图已关闭达 7 %,解 串器也 可将之锁 定 15 0

案 ,能 够 方便 地 级联 使 用 以支 持 更 多 及解 串 。作 为 业 界标 准 sD I接 口的

I O端 口的需求 。 /

Ma i x m

低中频调 谐器 系统

电话 :0 1 4 7 5 3 2 —5 0 — 5 3

htp t , . c o hi c m mi r c p.o

低失真 ;改善 l d O B的 E 辐射级别 ; MI 采用小散热 片的热保护机 制 ,确保即使 在芯 片 温 度较 高 时 ,也 不 产生 音 乐 中

路输入可连 接至任一路输 出 ,或连接 至

一 新布 品 发

高速 .多路 L D V S交叉开关

M AX9 2 M AX91 4 3 / 1 3 /M AX9 5 3 l

外 ,器件具备业界 领先的低 放射量 ,因 高集成立体声 D类放 大器 而无须外部 屏蔽 ,特 别适用于对噪 声敏

TDA8 5 是 一 个 2× l 0 l0 90 5 ~ 7 W

Mi r c i Te h o o y co hp c n lg

独特 的热保 护机制 可以 防止音 乐 中断 。

其他特性: 最宽达8 V的电源工作范 围; 5

护以及 ±1 k 0 V接触放 电模式E D保 护。 S

M AX9 / AX9 / 2M 1 3 4 MAX9 5 每 1 3 的 1 3

且符合 L N总线 2 0 2 1 AE J6 2 带宽 较 小 ,但 只 需搭 配 一 颗低 成 本 的 的大信号 处理的功能 ,这款低 中频调谐 I ./ . 和S 2 0 标准以及 上一代的 L N1 X标 准 。 I . MC 2 2 发器备有内置稳压器 , P 0 X收 减少 了所 需的外部组 件数量 ,从而 增强

LN S E J 6 2 I/ A 2 0 收发器

M 和 M C P 202 1 C P 2022

穿越驱动 器。

块 ,从 而在主机 中节省 了很大空 间并 减

TE 6 0  ̄ TE 6 0 整 LMH4 4 3 5芯 片采用 独特 的结构 , 低 了系统成本 。 F 6 1 H F 6 6

每个端 口支持高达 8 0 / 的数据 速 感的系统 ,如汽车 收音机 、车载娱 乐系 的D类放大 器 , 为单 层 电路板而设计 。 4 Mb s 专 率。 MAX9 3 具 有 3 12 路输入端 I和 2 Z I 路 统、GP S导航 、视 镜 、方向盘控制 和车 T DA8 5 9 0能以极低 的失真 取得持高保 输 出端 口, MAX9 3 具 有3 14 路输入端 口 库 大门开关 。MC 2 2 P 0 X收 发器在运 行 真音响性 能 , 可以在 ± 1 . ~±4 V的 25 0 和4 路输 出端 口, MAX9 3 具有 4 15 路输 模式 和 待机 模 式 时功 耗 很 低 ( 别 为 宽泛 电压供应 范 围之 问工作 ,静态 电流 分 入端 口和 3路输 出端 口。所有端 口均具 1 5 mA和 1 mA) 1 6 ,非常适 合非 点火 开 也很低 。 DA8 5 提高 了E 性能 , T 90 MI 其 有 ± 2 k I O气 隙放 电模式 ES 5V S D保 关 应用 ,并且 有助于延长 电池寿命 。 护 、± 1k EC气 隙放 电模式 E D保 5V I S

T F 6 x系列调谐 器采 用了突破性 E 60

S TE 2 M 专为传 送无 压缩 1 8 p MP 4 4 0 0

信号而制 定全部 Gb s

电话 :0 0 2 1 5 9 l-6 l — 1 9

h t // tp W . a i -i c r .n m x m c.o c n

只需要 3 2 VDS接 噪声放大 器和 自动增益控 制 , J6 2 2 0 认可和 OE 认可 ,并通过 AEC— F GA的接 口。此款收 发器的 L M P

QI0 O 标准认证 。收发器 内置稳压器 , 并 口可以抑制 电磁干扰 ,虽然并行总线 的 个低成本 的外围器件 。此外 ,通过特殊

输 出在所有显示 器上播放视频 图像 。开 关的切换可通过 引脚或 L N/ : I I C兼容 串

串行数 字接 口( D ) S I 双通道串行 /

解 串收发器

L MH4 4 3 5串行 /解 串收 发器的输 出对准抖动仅 3 p , 0 s 最低输 入抖动容 限

断;开关机 P p声抑制 ;高 电源噪声抑 o 制性 能 ;电流 削波保护 。

( C 22 M P 0 X)是 L N/ AE J 6 2收 发 使5 I S 20 位低 电压差分信 号传输( VDS并 行 合了全部关键 射频组件 ,包括了压控振 L )

器。这两款新 器件 已取得第 三方 L N/ 总 线 可 以 充 分 发 挥 其 性 能 , 以 简 化 荡器 、陶瓷滤波 器、中频变压线 圈、低 I

线 ,每秒 可 传送 高达 6 0个帧 。此 外 , 关键射频 组件 ,并 省去 了对手动调节 的 L MH4 4 还 内置 4 S I 35 个 D 电缆驱动器 、 需求 。因此 ,整机厂 可以容 易的 将调谐

2 D 输 出驱动器及 2 个S I 个时钟恢 复环路 器 应 用在 主 板上 ,不再 需 要 调谐 器 模