基于FPGA的多功能数据选择器设计与实现

基于fpga的四选一数据选择器和一位全加器的设计

ENTITY mux21 ISPORT(A,B,S : IN BIT;Y : OUT BIT);END ENTITY mux21;ARCHITECTURE one OF mux21 ISBEGINY <= A WHEN S= '0' ELSE B;END ARCHITECTURE one;ENTITY xor2 ISport(a,b : in bit;c : out BIT);end entity xor2;ARCHITECTURE one OF xor2 ISbeginc <= '0' when a=b else '1' ;end ARCHITECTURE one;ENTITY mux41 ISPORT(A,B,C,D,S1,S2 : IN BIT;Y : OUT BIT);END ENTITY mux41;ARCHITECTURE ons OF mux41 IS COMPONENT mux21PORT(A,B,S : IN BIT;Y : OUT BIT);END COMPONENT;COMPONENT xor2port(a,b : in bit;c : out bit);END COMPONENT;SIGNAL d1,e,f : bit ;BEGINu1 : mux21 PORT MAP(A=>A,B=>B,S=>S1,Y=>e); u2 : mux21 PORT MAP(A=>C,B=>D,S=>S2,Y=>f); u3 : xor2 PORT MAP(a=>S1,b=>S2,c=>d1);u4 : mux21 PORT MAP(A=>e,B=>f,S=>d1,Y=>Y); END ARCHITECTURE ons;(四选一)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY h_adder ISPORT(A,B : IN STD_LOGIC;CO,SO : OUT STD_LOGIC);END ENTITY h_adder;ARCHITECTURE fh1 OF h_adder ISBEGINSO <= NOT(A XOR (NOT B));CO <= A AND B;END ARCHITECTURE fh1;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY or2a ISPORT(a,b : IN STD_LOGIC;c : OUT STD_LOGIC);END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc <= a OR b;END ARCHITECTURE one;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_adder ISPORT(ain,bin,cin : IN STD_LOGIC;cout,sum : OUT STD_LOGIC);END ENTITY f_adder;ARCHITECTURE fd1 OF f_adder ISCOMPONENT h_adderPORT(A,B : IN STD_LOGIC;CO,SO : OUT STD_LOGIC);END COMPONENT;COMPONENT or2aPORT(a,b : IN STD_LOGIC;c : OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f : STD_LOGIC;BEGINu1 : h_adder PORT MAP(A=>ain, B=>bin, CO=>d, SO=>e); u2 : h_adder PORT MAP(A=>e, B=>cin, CO=>f, SO=>sum); u3 : or2a PORT MAP(a=>d, b=>f, c=>cout);END ARCHITECTURE fd1;LIBRARY IEEE;(一位全加器)。

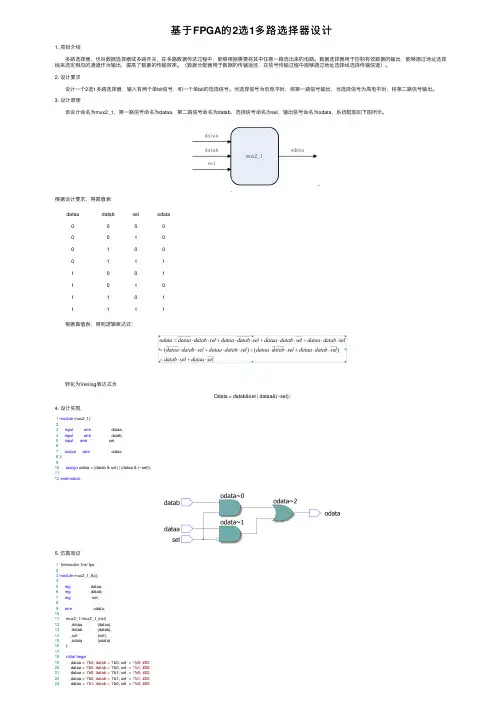

基于FPGA的2选1多路选择器设计

基于FPGA的2选1多路选择器设计1. 项⽬介绍 多路选择器,也叫数据选择器或多路开关,在多路数据传送过程中,能够根据需要将其中任意⼀路选出来的电路。

数据选择器⽤于控制有效数据的输出,能够通过地址选择线来选定相应的通道作为输出,提⾼了数据的传输效率。

(数据分配器⽤于数据的传输途径,在信号传输过程中能够通过地址选择线选择传输信道)。

2. 设计要求 设计⼀个2选1多路选择器,输⼊有两个单bit信号,和⼀个单bit的选择信号。

当选择信号为低电平时,将第⼀路信号输出,当选择信号为⾼电平时,将第⼆路信号输出。

3. 设计原理 该设计命名为mux2_1,第⼀路信号命名为dataa,第⼆路信号命名为datab,选择信号命名为sel,输出信号命名为odata,系统框图如下图所⽰。

根据设计要求,得真值表:dataa datab sel odata00000010010001111001101011011111 根据真值表,得到逻辑表达式: 转化为Verilog表达式为Odata = datab&sel | dataa&(~sel);4. 设计实现1module mux2_1(23input wire dataa,4input wire datab,5input wire sel,67output wire odata8 );910assign odata = (datab & sel) | (dataa & (~sel));1112endmodule5. 仿真验证1 `timescale 1ns/1ps23module mux2_1_tb();45reg dataa;6reg datab;7reg sel;89wire odata;1011 mux2_1 mux2_1_inst(12 .dataa (dataa),13 .datab (datab),14 .sel (sel),15 .odata (odata)16 );1718initial begin19 dataa = 1'b0; datab = 1'b0; sel = 1'b0; #20;20 dataa = 1'b0; datab = 1'b0; sel = 1'b1; #20;21 dataa = 1'b0; datab = 1'b1; sel = 1'b0; #20;22 dataa = 1'b0; datab = 1'b1; sel = 1'b1; #20;23 dataa = 1'b1; datab = 1'b0; sel = 1'b0; #20;24 dataa = 1'b1; datab = 1'b0; sel = 1'b1; #20;25 dataa = 1'b1; datab = 1'b1; sel = 1'b0; #20;26 dataa = 1'b1; datab = 1'b1; sel = 1'b1; #20; 27end2829endmodule参考资料: (1);。

基于FPGA的多功能信号源设计与实现

基于FPGA的多功能信号源设计与实现摘要直接数字频率合成(DDS)是七十年代初提出的一种新的频率合成技术,其数字结构满足了现代电子系统的许多要求,因而得到了迅速的发展,现场可编程门阵列器件(FPGA)的出现,改变了现代电子数字系统的设计方法,提出了一种全新的设计模式。

本设计结合这两项技术,并利用FPGA灵活的控制技术,设计了一种新的波形发生器。

本文首先介绍了DDS的基本原理,接着对EDA技术及可编程逻辑器件的特点和发展历程进行了详细地介绍,其中对要使用到的Quartus II、 MATLAB/DSP Builder、ModelSim 等软件作了介绍。

根据DDS基本原理用VHDL语言完成了对正弦信号发生器、数字移相信号发生器的设计,并用Quartus II进行时序仿真,嵌入式逻辑分析仪(SignalTap II)进行在线实时测试,最后下载到EDA实验开发平台上进行试验,通过示波器观察实验结果。

用现代DSP技术设计工具DSP Builder建模设计了调幅(AM)信号发生器、频移键控(FSK)信号发生器、正交幅度调制(QAM),并对其进行算法仿真,再用ModelSim进行功能仿真,Quartus II进行时序仿真,(功能仿真模拟波形与MATLAB算法仿真波形一致,功能仿真的数据流图与Quartus II时序仿真一致)仿真结果表明,本次设计达到了设计要求。

关键词直接数字频率合成;波形发生器;现场可编程门阵列;VHDL;DSP BuilderABSTRACTDirect Digital frequency Synthesis (DDS) was advanced rapidly in early 1970s and has been developing owing to its entirely digital structure. The appearance of Field Programmable Gates Array has changed the design method of digital electronic system and provided a new design model. With the two technology and the flexible control ability of FPGA, Functional Waveform Generator, has been developed .This new signal source can generate high frequency waveform data and also can change parameters of the Functional Waveform Generator. This paper will describe its process and characteristics.This paper introduces the basic principles of DDS, and then on the EDA technology and the characteristics of programmable logic devices and development of a detailed description of history, in which you want to use to Quartus II, MATLAB / DSP Builder, ModelSim software, also introduced.According to the basic principles of using VHDL language DDS completed a sinusoidal signal generator, digital Phase Shift Generator and timing simulation with the Quartus II embedded logic analyzer (SignalTap II) on-line real-time testing, and finally downloaded to EDA experiments Development platform to test results by an oscilloscope.DSP design tools with modern technology designed DSP Builder model amplitude modulation (AM) signal generator, frequency shift keying (FSK) signal generator, quadrature amplitude modulation (QAM), and its algorithm simulation, ModelSim for reuse Functional simulation, Quartus II timing simulation, (functional simulation waveforms consistent with the MATLAB simulation waveform algorithms, functional simulation of the data flow diagram consistent with Quartus II timing simulation) simulation results show that this design met the design requirements.Key words Direct Digital Frequency Synthesis ;Waveform Generator;Field Programmable Gate Array;VHDL;DSP Builder目录摘要 (I)ABSTRACT (II)1 绪论 (1)1.1 频率合成技术的种类 (1)1.1.1 直接模拟式频率合成器 (1)1.1.2 锁相式频率合成技术 (1)1.1.3 直接数字频率合成技术 (3)1.1.4 混合式频率合成技术 (4)1.2 本文的主要工作 (4)2 DDS技术及原理 (5)2.1 DDS工作原理 (5)2.2 基本DDS结构的常用参量计算 (7)2.3 DDS的优缺点 (7)2.3.1 DDS的优点 (7)2.3.2 DDS的缺点 (8)2.4 本章小结 (9)3 EDA技术与可编程逻辑器件 (10)3.1 EDA技术的发展与VHDL语言 (10)3.1.1 EDA技术 (10)3.1.2 VHDL硬件描述语言 (11)3.1.3基于VHDL的自顶向下设计方法 (11)3.2可编程逻辑器件及其设计方法 (12)3.2.1可编程逻辑器件 (12)3.2.2 设计准备 (13)3.2.3 设计输入 (13)3.2.4功能仿真 (14)3.2.5设计处理 (14)3.2.6时序仿真 (15)3.2.7器件编程侧试 (15)3.3 CPLD/FPGA (15)3.3.1 Cyclone系列FPGA (15)3.4 Altera可编程逻辑器件开发软件 (17)3.4.1 可编程器件的开发流程 (17)3.4.2 Quartus II的特点 (17)3.5 本章小结 (18)4 Matlab/DSP Builder 设计向导 (19)4.1 Matlab/DSP Builder及其设计流程 (19)4.2使用ModelSim 进行RTL级仿真 (21)4.3 使用Quartus II实现时序仿真 (22)5 各种信号的实现 (23)5.1DDS设计 (23)5.1.1DDS程序设计及仿真 (24)5.1.2硬件调试 (27)5.2数字移相信号发生器的设计 (29)5.2.1 数字移相程序与仿真 (30)5.2.2 硬件调试 (33)5.3正交幅度调制 (35)5.4 AM信号发生器的设计 (37)5.5 FSK信号发生器设计 (39)5.6 本章小结 (42)结论 (43)参考文献 (44)附录 (45)致谢 (49)1 绪论频率合成器是电子系统的心脏,是决定电子系统性能的关键设备,随着通信、数字电视、卫星定位、航空航天、雷达和电子对抗等技术的发展,对频率合成器提出了越来越高的要求。

多路数据选择器

基于FPGA的多路数据采集器的设计李庭武李本印(陇东学院电气工程学院,甘肃庆阳745000)摘要:数据采集是从一个或多个信号获取对象的过程,它是计算机与外部物理世界连接的桥梁,尤其在恶劣的数据采集环境中得到广泛应用。

本课题主要研究利用FPGA把采集到的八路模拟信号电压分别转换成数字信号,在数码管上实时显示电压值,并且与计算机运行的软件示波器连接,实现电压数据的发送和接收功能。

关键词:FPGA;模数转换;数码显示管;键盘;设计Design of multi-channel data terminal Based on FPGALi Tingwu Li Benyin(Electrical Engineering College, Longdong University, Qingyang 745000, Gansu, China)Abstract: Data acquisition is a process that access to the object from the one or more signal, it is the bridge between the computer and the external physical world, and especially widely applied in data acquisition in harsh environment . This essay mainly studies on the usage of FPGA to collect the eight analog signals that are converted to digital voltage signal, digital tube display real-time voltage value. Connecting with the computer running software oscilloscope so that to realize the voltage data sending and receiving function.Keywords: FPGA; analog-to-digital converting chip; digital display tube; keyboard; design0 引言20世纪以来,数字信号处理技术已逐渐渗透到通信、家电、军事等各个应用领域。

实验一 FPGA VHDL四选一数据选择器的设计

实验二四选一数据选择器的设计1实验目的(1)进一步熟悉和掌握Qartus II的使用方法;(2)掌握FPGA实验箱使用方法;(3)学习和掌握电路原理图的设计流程1.实验内容使用Qartus II的元件库,通过元件图的方式设计具有4选1功能的数据选择器,并使用FPGA实验箱对程序进行硬件下载,验证。

2.实验条件开发软件:Qartus II 8.0实验设备:FPGA实验箱拟用芯片:Altera EP3C55F484C83.实验设计1)系统原理根据4选1数据选择器的工作原理,有公式:S0S1A S1S0S1S0S1S0Y=+B+C+DS1S0可见,要实现功能,需要6个输入,一个输出。

其中是数据选S1S0择端,A,B,C,D是数据输入端。

由输出高低电平(开关信号)决定数据的输出和传送。

2)电路原理图建立原理图。

元件项使用四个三接口与门和一个四接口的与门,以及两个非门构成。

实验原理比较简单,就是用来实现四选一功能的实现。

如图2-1所示图2-1 4选1数据选择器的原理图3)电路波形图工程编译完成后,必须对其功能和时序性质进行仿真测试。

下图就是实现仿真后的波形,满足原设计要求。

如图2-2所示。

图2-2 四选一数据选择器仿真后的波形4)引脚锁定和硬件测试为了能够对乘法器进行硬件验证,应将其输入信号锁定在芯片确定的引脚上,编译下载。

其锁定输入信号、输出信号如下图2-3。

‘图2-3 四选一数据选择器引脚锁定5)编译文件下载编译文件下载结果如图2-4所示。

图2-4 四选一数据选择器编译文件下载4.实验结果使用实验箱旁边的频率信号低的4个信号做输入信号,通过FPGA 实验箱上的蜂鸣器发出的声音频率快慢来测试实验是否成功。

A输入接入1HZ信号 B输入接入4HZ信号C输入接入8HZ信号 D输入接入16HZSO输入接入L8开关 S1输入接入L7开关Y输出接入蜂鸣器可得实验结果如下表表2-1所示L7=关,L8=关L7=关,L8=开L7=1,L8=开L7=开,L8=开发声频率很慢慢较快快表2-1 开关不同位置时蜂鸣器发声状态实验箱结果如图2-5所示图2-5 实验箱进行试验5.心得体会通过这次实验,让我学习到了如何在Qartus II中使用原理图的方式做出所需要的功能器件。

基于FPGA实现四选一选择器的设计

基于FPGA实现四选一选择器的设计摘要本文是基于FPGA的四选一选择器的设计:基于FPGA在数据选择方面的优势,把FPGA作为选择器的控制核心;主要研究如下:软件部分——四选一选择器程序。

针对数据选择器的设计,对FPGA进行了型号选择,使用VHDL语言在型号FLEX10K/20RC208-4上编写了四选一选择器的程序,通过使能端的控制,从而达到四选一的功能。

硬件部分——使用protel画出原理图并作出PCB板。

本设计采用了单八路模拟开关CD4051,通过输入端的控制,选择一路信号,通过ADC0804模数转化,输出8路信号给FLEX10K/20RC208-4,经FLEX10K/20RC208-4处理后,接TCL7528后,将数字信号转换为模拟信号并输出。

本文通过软件和硬件的两个方面的设计,实现了四选一选择器的功能。

关键词:FPGA ;VHDL ;PROTEL ;选择器内蒙古科技大学毕业设计说明书(毕业论文)FPGA implementation based on four selected design of a selectorAbstrateThis article is based on a choice selection of four FPGA Design: FPGA-based data selection in the advantages of the FPGA as a selector control center; main research are as follows:Software parts - 4 election a choice program. Design for data selection, model selection on the FPGA, using the VHDL language in the model FLEX10K/20RC208-4 four selected to write a program selector, by enabling the client to control, so as to achieve a function of four elections.Hardware - protel schematic drawing and make a PCB board. This design uses a single eight-way analog switches CD4051, through the control input, select the way the signal, ADC0804 module through the transformation of the output signal 8 to FLEX10K/20RC208-4, by FLEX10K/20RC208-4 treatment, then TCL7528, will digital signal is converted to analog signals and output.In this paper, two aspects of hardware and software design, implementation, choose one of four selector functions.Keywords: FPGA ; VHDL ; ROTEL ; selectorI目录摘要 .............................................................................................................................................. Abstrate (I)第一章绪论 01.1 FPGA简介 01.1.1 FPGA发展现状 01.1.2 FPGA的发展趋势 (1)1.1.3 FPGA基本结构 (1)1.1.4 FPGA的特点 (3)1.1.5 FPGA选型 (4)1.1.6 FPGA设计原则 (5)1.2本论文研究的主要内容 (6)第二章FPGA芯片设计 (7)2.1 BTYG-EDA实验开发系统简介 (7)2.1.1 BTYG-EDA实验开发系统特点 (7)2.1.2 BTYG-EDA实验开发系统资源介绍 (7)2.1.3 主芯片引脚和外部硬件连接关系 (7)2.2 FLEX10K/20RC208-4 (11)2.3 本章小结 (13)第三章MAX+plus II软件和VHDL语言――软件部分 (14)3.1 MAX+plus II开发软件 (14)3.1.1 MAX+plus II功能特点 (14)3.1.2 MAX+plus II系统要求 (15)3.1.3 MAX+plus II设计流程 (15)3.2 VHDL语言简介 (18)3.2.1 VHDL基本介绍 (18)3.2.2 VHDL语言的特点 (19)3.2.3 VHDL系统优势 (20)II内蒙古科技大学毕业设计说明书(毕业论文)3.2.4 VHDL程序基本结构 (20)3.3 MAX十plus II中硬件描述语言输入的设计过程 (21)3.3.1 输入VHDL文件 (21)3.3.2 将文件指定为设计项目 (21)3.3.3 项目编译 (22)3.3.4 项目仿真 (22)3.4 程序仿真介绍及仿真图 (22)3.5本章小结 (24)第四章protel99——硬件部分 (25)4.1 protel简介 (25)4.1.1 Protel99SE的功能特点 (25)4.1.2 用Protel99SE进行电路设计的步骤 (26)4.2 四选一选择器的原理图及各元件介绍 (26)4.3 本章小结 (33)第五章总结与展望 (34)5.1 取得的成果 (34)5.2 工作展望 (34)参考文献 (35)附录A (36)附录B (37)致谢 (39)III第一章绪论1.1 FPGA简介1.1.1 FPGA发展现状当今社会是数字化的社会,是数字集成电路广泛应用的社会,数字集成电路本身在不断地进行更新换代。

fpga8选1数据选择器

BEGIN Q<=D(0) WHEN A="000" ELSE

D(1) WHEN A="001" ELSE

D(2) WHEN A="010" ELSE

D(3) WHEN A="011" ELSE

D(4) WHEN A="100" ELSE

D(5) WHEN A="101" ELSE

教师评分

操作成绩

报告成绩

教师签名

日 期

D(6) WHEN A="110" ELSE

D(7) WHEN A="111" ELSE

'Z';

END one;

仿真波形图

实验总结及个人心得体会

通过本次实验,复习了之前学习的条件信号赋值语句。条件信号赋值语句在执行时,首先要进行条件判断,然后再进行信号赋值操作。同时,进一步加强了对8选1数据选择器的逻辑功能的理解。

FPGA实验报告

姓名朱聪聪学号39姓名武帅实验目的

1、理解数据选择器功能。

2、掌握VHDL并行语句中条件信号赋值的格式和用法。

设计要求

设计一个8选1数据选择器使其满足如下真值表:

8选1数据选择器真值表

地址码(选择信号)

输出Q

A0

A1

A2

0

0

0

D0

0

0

1

D1

0

1

0

D2

表达式2WHEN 赋值条件2ELSE

……

表达式n;

设计原理图及源程序

LIBRARY IEEE;

基于FPGA的多功能信号发生器的设计

电子电路设计与方案0 前言现场可编程门阵列具有运行速度快,修改灵活方便,并自带大量的输入输出端口等优点,通过FPGA实现该信号发生器的核心部件DDS模块,可以灵活地对信号发生器的参数进行调整,另外通过单片机的配合实现对其他外设电路的控制,实现信号发生器显示、参数调节等辅助的功能,通过数模转换电路和波形处理电路实现所需信号波形的输出。

本设计的主要指标为:(1)频率范围:0~1MHz,可通过键盘任意设置频率,步进1Hz。

(2)频率精度:±1%。

(3)幅值范围:±5V,可通过键盘任意设置幅度,步进100mV。

(4)幅值精度:±5%。

(5)用液晶显示所选波形名称,频率,幅值。

1 系统硬件结构该信号发生器主要是由FPGA构成其最小系统,通过编程实现信号发生器的主要功能部件数字频率合成功能模块,并对其信号进行控制和处理,使得输出波形更加平滑、符合要求。

当然为了使电路能够实现人机对话、参数设置等功能,并设计了由单片机和外围电路构成的控制电路部分,实现对显示电路、输入电路的控制。

本系统通过单片机来识别按键所输入的指令,并根据其该指令,产生输出波形的参数要求,并将该数据送入FPGA 的ROM中,再由FPGA完成DDS数据处理功能(频率控制、移相等),将波形数据送入D/A转换器,并将波形参数(如频率、幅值等)送入到显示电路中显示,最后通过低通滤波电路滤波使输出的波形平滑。

系统硬件结构如图1所示。

本设计未采用专用DDS芯片,而是通Verilog HDL语言编程在目标芯片上来实现信号源的主要功能,可以根据实际设计的要求来增删DDS的功能,具有灵活、方便等特点,同时该DDS模块中的参数及子模块根据所用目标器件稍加调整,完全可用于其他需要DDS技术的应用场合,有很好的通用性。

图1 系统硬件结构图2 单元电路的设计整个硬件系统以FPGA为核心,配合外围电路控制参数实现波形的模拟输出。

外围电路主要包括控制电路及信号处理电路两部分。

FPGA综合设计实例

FPGA综合设计实例FPGA(现场可编程门阵列)是一种集成电路设备,具有可编程功能,可以根据用户的需求进行不同的设计。

综合设计是指将高级硬件描述语言(HDL)转化为对应的逻辑网表,并进行布线和时序优化的过程。

下面将介绍一个FPGA综合设计的实例。

在这个实例中,我们将使用Verilog HDL来设计一个简单的4位加法器。

这个加法器可以接受两个4位的二进制数作为输入,并将它们相加得到一个4位的二进制数作为输出。

首先,我们需要定义输入和输出信号。

使用Verilog HDL,我们可以使用wire或reg关键字来声明这些信号。

在这个例子中,我们将使用reg关键字。

```verilogmodule adderinput [3:0] A, B,output [3:0] Sreg [3:0] S;// Adder logic implementation goes hereendmodule```接下来,我们需要在模块中实现加法器的逻辑。

我们可以使用Verilog HDL中的"+"操作符来实现加法操作。

```verilogmodule adderinput [3:0] A, B,output [3:0] Sreg [3:0] S;S=A+B;endendmodule```最后,我们需要在FPGA中综合和实现这个设计。

首先,我们需要使用综合工具将Verilog HDL代码转化为逻辑网表。

这个过程也称为综合。

接下来,我们需要使用布局工具将逻辑网表映射到FPGA中的可用资源上,并进行适当的布线。

这个过程也称为布局和布线。

最后,我们需要使用时序优化工具来优化设计的时序性能,并进行时序约束以确保电路的正确功能。

总结起来,这个实例展示了一个简单的FPGA综合设计过程。

通过使用Verilog HDL和相应的工具,我们可以将高级硬件描述语言转化为可在FPGA中实现的逻辑电路,并通过综合、布局和布线、时序优化等步骤完成设计。

基于FPGA的多通道采样系统设计课程设计论文

FPGA课程设计题目:基于FPGA的多通道采样系统设计院(系):电气工程及其自动化学院专业:电子信息工程12-01摘要本论文介绍了基于FPGA的多通道采样系统的设计。

用FPGA设计一个多通道采样控制器,利用VHDL语言设计有限状态机来实现对AD7892的控制。

由于FPGA器件的特性是可以实现高速工作,为此模拟信号选用音频信号。

由于音频信号的频率是20Hz-20KHz,这样就对AD转换的速率有很高的要求.因为FPGA的功能很强大,所以我们把系统的许多功能都集成到FPGA器件中,例如AD通道选择部分,串并输出控制模块,这样使得整个系统的外围电路简单、系统的稳定性强。

FPGA的配置模式选用被动串行模式,这样就增强了系统的可扩展性。

输出模式可选择性使得系统的应用相当广泛,串行输出可以用于通信信号的采集,方便调制后发射到远程接受端,远程接收端对采集的数据进行解调;而并行输出模式则可以通过高速存储器将采集的信号放到微机或者其他的处理器上,根据采集的数据进行相应的控制。

此系统的缺点是由于FPGA器件配置是基于SRAM查找表单元,编程的信息是保持在SRAM中,但SRAM在掉电后编程信息立即丢失,所以每次系统上电都需要重新配置芯片,这对在野外作业的工作人员很不方便,解决的方法是专用的配置器件来配置FPGA,在每次系统上电的时候会自动把编程信息配置到FPGA芯片中。

但设计中没有采用到这种配置方案主要是考虑到专用配置器件的价格问题。

本文开始介绍了多通道系统的组成部分,然后分别介绍了各个组成部分的原理和设计方法,其中重点介绍了FPGA软件设计部分。

还对当前十分流行的基于FPGA的设计技术作了简单的阐述,最后对系统的调试和应用作了简短的说明。

关键词:音频放大;滤波器;FPGA;VHDL;AD7892;有限状态机;目录摘要 (2)引言 (3)1题目来源 (3)2研究意义 (3)3多通道采样系统的组成 (3)4方案设计 (4)5 单元电路的设计 (4)5.1音频放大、滤波部分 (4)(1)音频放大部分 (4)(2)有源滤波器的设计 (4)5.2 AD采样电路 (5)5.3 FPGA控制部分 (5)(1)通道选择模块 (6)(2)延时模块的设计 (6)(3)串并输出选择控制 (7)5.4 FPGA的硬件设计 (8)6 软件介绍 (8)7 整机调试 (8)7.1 硬件电路的调试步骤 (8)(1)音频放大部分调试 (8)(2)滤波部分调试 (8)(3)FPGA硬件电路调试 (9)(4)AD采样模块调试 (9)(5) 联机调试 (9)8 结论 (9)参考文献 (10)附录 (11)引言FPGA(Field-Programmable Gate Array 现场可编程门阵列)是近年来广泛应用的超大规模、超高速的可编程逻辑器件,由于其具有高集成度(单片集成的系统门数达上千万门)、高速(200MHz 以上)、在线系统可编程等优点,为数字系统的设计带来了突破性变革,大大推动了数字系统设计的单片化、自动化,提高了单片数字系统的设计周期、设计灵活性和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的多功能数据选择器设计与实现章军海201022020671[摘要]传统的数字系统设计采用搭积木式的方法来进行设计,缺乏设计的灵活性。

随着可编程逻辑器件(PLD)的出现,传统设计的缺点得以弥补,基于PLD的数字系统设计具有很好的灵活性,便于电路系统的修改与调试。

本文采用自顶向下的层次化设计思想,基于FPGA设计了一种多功能数据选择器,实现了逻辑单元可编程、I/O单元可编程和连线可编程功能,并给出了本设计各个层次的原理图和仿真时序图;本文还基于一定的假设,对本设计的速度和资源占用的性能进行了优化。

[关键词]层次化设计;EDA;自顶向下;最大时延0引言:在现代数字系统的设计中,EDA(电子设计自动化)技术已经成为一种普遍的工具。

基于EDA技术的设计中,通常有两种设计思想,一种是自顶向下的设计思想,一种是自底向上的设计思想[1]。

其中,自顶向下的设计采用层次化设计思想,更加符合人们的思维习惯,也容易使设计者对复杂系统进行合理的划分与不断的优化,因此是目前设计思想的主流。

基于层次化设计思想,实现逻辑单元、I/O单元和连线可编程可以提高资源的利用效率,并且可以简化数字系统的调试过程,便于复杂数字系统的设计[2][3]。

1系统原理图构架设计1.1系统整体设计原理本设计用于实现数据选择器和数据分配器及其复用的I/O端口和连线的可编程却换,提高系统的资源利用效率。

系统顶层原理框图如图1所示,系统拥有两个地址选择端口a0、a1,一个功能选择端口ctr,还有五路I/O复用端口。

其中,地址选择端口用于决定数据选择器的数据输入端和数据分配器的数据输出端;功能选择端口用于切换数据选择器和数据分配器,以及相应的I/O端口和连线;I/O复用端口数据的输入和输出,其功能表如表一所示。

图1顶层模块原理图表一顶层系统功能表根据层次化设计思想,要实现上述功能表中的功能,系统得由数据选择器、数据分配器和端口控制器三部分组成。

其中,数据选择器和数据分配器为功能单元,分别完成相应的数据处理功能,端口控制器完成相应数据端口模式和功能的切换功能。

根据对各个模块的功能要求,可以得到如图2所示的系统框架原理图。

图2 系统框架原理图1.2数据选择器设计原理数据选择器用于控制有效数据的输出,能够通过地址选择线来选定相应的通道作为输出,提高了数据的传输效率。

本设计中的数据选择器采用了层次化设计思想,通过将本设计中优化过的一种自定义逻辑运算模块和与非门组合构成。

由于自定义逻辑运算模块是一种速度快、片上面积小的与非结构模块,该数据选择器形成了与非-与非结构,有运行速度快、驱动能力强且占用片上面积小等优点。

该模块有两个数据端口a1、a0,用于选择相应的通道;还有四个数据端口x0、x1、x2、x3,分别是四个数据输入通道;还有一个输出通道y_select,用于输出选择的数据。

其原理框图如图3所示,将自定义逻辑单元的输出,经过一个四输入的与非门,得到最终的输出信号y_select。

要实现如表二所示的逻辑功能,得用a0、a1的地址选择信息,来选择四个输入中的一个作为输出,以实现数据选择的功能。

其原理图和功能表分别如下图所示:图3 数据选择器原理图1.3数据分配器设计原理数据分配器用于选择数据的传输途径,在信号传输过程中能够通过地址选择线选择传输信道。

本设计的数据分配器的设计与数据选择器的设计思想类似,采用了层次化设计思想,基于自定义的优化后的逻辑运算模块,对逻辑运算模块的信号进行取非运算得到相应的输出。

整个模块采用了与非-非门结构,其传输速度快,驱动能力强,占用资源较其它形式少。

该模块有两个地址选择端口a1、a0,用于选通逻辑运算模块相应的输出;有一个输入端口,用于输入要传输的数据;四个输出端口x_0、x_1、x_2、x_3,作为四路输出通道。

其结构原理图如图4所示,完成如表三所示功能,通过数据线选择正确的通道,完成有效分配功能。

图4 数据分配器原理图1.4端口控制器设计原理端口控制器用于对本系统的功能、I/O 端口和连线进行切换,是本系统实现可编程I/O 单元设计、可编程逻辑单元设计和可编程连线的核心。

本设计的端口控制器采用三态门作为选通开关,利用三态门的特性有效的对I/O 端口进行配置,使不用的端口形成高阻态,以实现I/O 端口的多路复用和输入输出的有效切换。

其具体结构原理图如图5所示。

图5 端口控制器原理图该模块由三态门和非门构成,拥有一个选择端口ctr用于对功能、I/O端口和连线进行选择,是本系统控制的核心;拥有四个单向输入端口x_0、x_1、x_2、x_3,用于将数据分配器的处理结果送到系统输出端口;拥有四个单向输出端口x0、x1、x2、x3,将输入的四路数据分别送到数据选择器的五个输入端口;拥有四个输入输出端口,通过切换来实现数据表四端口控制器功能表1.5逻辑运算模块设计原理逻辑运算模块用于完成本系统的主要逻辑运算,因此是本系统的处理速度和占用片上面积等参数的主要体现,本模块通过被相应的功能模块调用来完成各功能的逻辑运算。

其具体结构原理图如图6所示,该模块有两个数据选择端口a0、a1,用于选通相应的数据通道;拥有四个数据输入端口x0、x1、x2、x3,分别用于传输四路独立的信号;拥有四路输出端口y0、y1、y2、y3,用于输出四路独立的信号。

该模块利用图6所示原理图,完成表五所示的逻辑功能。

表五逻辑运算单元功能表该模块作为本系统主要的逻辑运算单元,其性能的好坏对系统的整体性能有很大影响,本系统中数据选择器和数据分配器都调用了该模块,因此该模块的设计应该将一些性能参数纳入考虑范围。

本系统考虑到逻辑模块的时延和片上面积,前者影响系统的处理速度,后者代表系统资源的利用效率。

电路的单元时间延迟取决于时间常量RC,当输出电阻恒定时,其输出延时取决于电容值C,现在以最小单晶管的电容为单位,假设源漏电容为栅电容的两倍。

则有如图7所示参数模型,其中Tmax代表最大时延,A代表片上占用面积,A=2A=6A=12A=20Tmax=6Tmax=19Tmax=40Tmax=69图7 常用逻辑器件的参数模型根据上述模型,可以计算得到本系统的A=2*2+12*4=52、Tmax=6+40+3*3=55,其参数较其它门电路所构成的该功能模块更好[4]。

2系统仿真与分析2.1整体仿真设计框图对于本系统的时序仿真,可以通过产生相应的激励信号来对系统的功能进行验证,通过系统最终的输出和输入信号的比较来确定系统功能是否得以实现。

本系统的仿真框图如图8 所示,该框图由激励产生模块和系统集成模块组成,激励产生模块为系统产生测试所需的时序(如图9所示),系统接收激励信号,产生相应的输出结果,以测试系统相应的功能。

图8 整体仿真设计框图图9 激励产生模块输出由图9可以看出,当功能控制信号ctr输出为0时,数据输出端xbir_0、xbir_1、xbir_2、xbir_3输出相应的脉冲信号,y_bir被设置为高阻态,系统进入数据选择器功能测试阶段;当功能控制信号ctr输出为1时,数据输出端y_bir输出相应的脉冲信号,xbir_0、xbir_1、xbir_2、xbir_3被设置为高阻态,系统进入数据分配器功能测试阶段。

2.2各模块仿真时序图及其分析2.2.1系统整体仿真时序分析通过在Quartus设置相应的输入信号,对输出信号进行跟踪观察,可以得到如图10所示的仿真时序图。

图10 系统整体时序图由该时序图可以看出,当功能控制信号ctr为1时,系统通过控制a1、a0从xbir_0、xbir_1、xbir_2、xbir_3输入的信号中选择一路从y_bir进行输出,实现了系统的数据选择器的功能;当功能控制信号ctr为0时,系统通过控制a1、a0,选择从xbir_0、xbir_1、xbir_2、xbir_3中的其中一个输出端口输出y_bir端口输入的信号,实现了系统的数据分配器的功能。

该时序完全符合表一所示的系统顶层功能表,证明本系统设计的正确性。

2.2.2数据选择器仿真时序分析在Quartus时序仿真中对数据选择器相应的端口进行设置,跟踪输出信号可以得到如图11所示的仿真时序图。

图11 数据选择器时序图由该时序图可以看出,该模块通过设置a0、a1来选择相应的输入信号从y_select端口进行输出,其时序与表二所示的功能表相符合,进一步验证了该模块的正确性。

在输出中存在一些很小的毛刺现象,是由于a0、a1不是同时发生状态转换,导致模块输出端的输出状态发生迅速的跳变所引起的。

由于毛刺持续的时间很短暂,该现象不会影响该模块的整体性能。

2.2.3数据分配器仿真时序分析在Quartus时序仿真中对数据分配器进行相应的设置,将相应的信号设置在输入端口,跟踪输出信号可以得到如图12所示的仿真时序图。

图12 数据分配器时序图由该模块的时序图可以看出,通过设置a0、a1可以选择x_0、x_1、x_2、x_3四个输出端口之一作为输入端y_in的输出。

该图的时序与表三所示的功能表相对应,图中还可以看出系统延时也比较短,只有5个ns,进一步证明该模块的高传输速度。

2.2.4端口控制器仿真时序分析在Quartus中对图5所示原理图进行时序仿真,设置相应的端口信号,跟踪其输出可以得到如图13所示的仿真时序图。

图13 端口控制器时序图由该模块的仿真时序图可以看出,当功能控制端口为0时,x_0、x_1、x_2、x_3、y_select 端口作为信号输入端,分别由xbir_0、xbir_1、xbir_2、xbir_3、y_bir双向端口输出,x0、x1、x2、x3、y_in被设置为高阻态,实现了数据分配器的I/O端口和连线的设置;当功能控制端口为1时,双向端口xbir_0、xbir_1、xbir_2、xbir_3、y_bir作为信号输入端,分别由x0、x1、x2、x3、y_in端口输出,x_0、x_1、x_2、x_3、y_select被设置为高阻态,实现了数据选择器的I/O端口和连线的设置,该仿真时序与表四所示的功能图完全一致。

2.2.5逻辑运算模块仿真时序分析在Quartus中对图6所示原理图进行时序仿真,设置相应的端口信号,跟踪其输出可以得到如图14所示的仿真时序图。

图14 逻辑运算模块时序图由该模块的时序仿真图可以看出,a1、a0实现了通道的正常选通,该时序与表五所示的功能表相符合。

为观察本系统的时延特性,本系统采用仿真的都为时序仿真,仔细观察时序图可以看出,该模块的该模块只有5ns以内的延时,证明该模块的速度性能很好,因此,系统中的数据选择器和数据分配器都有比较好的速度性能。

3总结本系统实现了多功能数据选择器的功能,完成了对于可编程IO单元、可编程逻辑单元和可编程连线的层次化设计,达到了设计要求。