555-556时基电路的特点和封装

555时基电路工作原理

555时基电路工作原理一、引言555时基电路是一种常用的集成电路,广泛应用于定时、脉冲发生、频率分频、模拟电路等领域。

本文将详细介绍555时基电路的工作原理及其相关特性。

二、555时基电路的基本结构555时基电路由比较器、RS触发器、RS锁存器和电压比较器组成。

其中,比较器用于比较电压,RS触发器用于存储电平状态,RS锁存器用于锁存电平状态,电压比较器用于产生输出信号。

三、555时基电路的工作原理1. 稳态工作原理:当电源接通时,电容C1开始充电。

当电容电压达到2/3的电源电压时,比较器会输出高电平,导致RS触发器的Q端输出低电平,RS锁存器的S端输出高电平,电压比较器输出低电平。

此时,555时基电路处于稳态工作状态。

2. 充电过程:在稳态工作状态下,电容C1开始充电,电压逐渐上升。

当电容电压达到1/3的电源电压时,比较器会输出低电平,导致RS触发器的Q端输出高电平,RS锁存器的S端输出低电平,电压比较器输出高电平。

此时,555时基电路进入充电过程。

3. 放电过程:在充电过程中,电容C1的电压继续上升,直到达到2/3的电源电压。

此时,比较器输出高电平,RS触发器的Q端输出低电平,RS锁存器的S端输出高电平,电压比较器输出低电平。

555时基电路进入放电过程。

4. 循环工作:充电过程和放电过程交替进行,形成一个连续的循环工作状态。

通过调整电容C1和电阻R1、R2的数值,可以控制充放电时间的长短,从而实现不同的定时功能。

四、555时基电路的应用1. 定时器:通过调整电容和电阻的数值,可以实现不同的定时功能,如延时触发、定时报警等。

2. 脉冲发生器:通过调整电容和电阻的数值,可以产生不同频率和占空比的脉冲信号。

3. 频率分频器:通过将555时基电路与其他逻辑电路结合,可以实现频率的分频操作。

4. 模拟电路:555时基电路可以用作模拟信号的发生器,产生各种波形信号。

五、555时基电路的特性1. 稳定性:555时基电路具有较高的稳定性,可以在不同温度和电源变化的环境下正常工作。

555时基电路工作原理

555时基电路工作原理1. 介绍555时基电路是一种经典的集成电路,常用于产生稳定的时钟信号或者触发脉冲。

本文将详细介绍555时基电路的工作原理,包括内部结构、引脚功能、工作模式和工作原理等方面。

2. 内部结构555时基电路由电压比较器、RS触发器、RS锁存器、放大器和输出级组成。

其中,电压比较器用于比较输入电压与参考电压的大小,RS触发器用于产生稳定的时钟信号,RS锁存器用于存储触发脉冲的状态,放大器用于放大电压信号,输出级用于驱动外部负载。

3. 引脚功能555时基电路共有8个引脚,分别是VCC、GND、TRIG、OUT、RESET、CTRL、THRES和DISCH。

VCC和GND分别为电源引脚,TRIG为触发引脚,OUT为输出引脚,RESET为复位引脚,CTRL为控制引脚,THRES为阈值引脚,DISCH为放电引脚。

4. 工作模式555时基电路有三种主要的工作模式,分别是单稳态、自由运行和双稳态。

单稳态模式下,输出信号在触发脉冲后保持稳定一段时间;自由运行模式下,输出信号以一定频率连续产生脉冲;双稳态模式下,输出信号在两个稳定状态之间切换。

5. 工作原理555时基电路的工作原理如下:- 当TRIG引脚电压低于THRES引脚电压时,RS触发器的输出为高电平,放电管导通,电容器C开始放电。

- 当电容器C电压降低到CTRL引脚电压的2/3时,电压比较器输出低电平,RS触发器的输出变为低电平,放电管截止,电容器C停止放电。

- 当电容器C电压升高到CTRL引脚电压的1/3时,电压比较器输出高电平,RS触发器的输出变为高电平,充电管导通,电容器C开始充电。

- 当电容器C电压升高到THRES引脚电压时,充电管截止,电容器C停止充电。

- 这个过程不断循环,使得输出信号产生稳定的时钟信号或者触发脉冲。

6. 应用领域555时基电路广泛应用于各种电子设备中,如定时器、频率计、脉冲宽度调制器、电压控制振荡器等。

它具有工作稳定、使用方便、成本低廉等优点。

第一讲555时基集成电路讲解学习

5)放电开关

555时基电路的放电开关由晶体三级管VT(75551C为CMOS管)组 成。由于555电路组成定时电路时,定时的时间由RC电路的充电时 间常数决定的。但是为使定时电路能反复使用,在完成一次定时控 制后应将电容器C上的电荷放掉,为下次定时控制作好准备,放电 管VT就为此而设。当C充电时VT截止,当C放电时VT饱和导通, 提供放电通路。

5kΩ的电阻组成的,所以这种IC被称为555时 基集成电路。尽管有的分压器并不是3个5kΩ

的电阻(如图3的7555,是3个100k电阻),都习 惯称555时基电路。

• 2)比较器

•

比较器由运放组成,共有两个比较器。其中

一个称为上比较器,输入端为反相输入端(6脚),

比较基准是Uf1=2/3Ucc;另一个则称为下比较器,

输入端为同相输入端(2脚),比较基准是

Uf2=1/3Ucc。若在5脚(称为控制端)外接基准电

压Uc,则Uf1=Uc,Uf2=1/2Uc,Un称为阀值电

平,Uf2称为触发电平。

• R-S触发器:R-S触发器是由二个与非门交叉组 成(7555IC则为两个或非门交叉组成)。R-S触发 器有同步R-S触发器和基本R-S触发器两类,555 时基电路是基本R-S触发器,这种触发器的输入 端要求低电平触发。其逻辑功能见其真值表(表1 所示)。

t=RCln3=1.1RC (其中,ln3=ln(1器

图4 555/7555构成的单稳态触发器

图5是一个数字式电容测量电路。这里555为单稳态电路,它的输 出作为计数门控信号,精度可达0.5%,K1-1与K1-2是同步动作的 量程选择开关,这里设有三档量程(10μF、1μF、0.1μF),可测量 10μF以下的电容,RPl~RP3分别调整各量程的满度,使显示数字 与CX容量一致,需要注意的是启动脉冲的周期要足够长,不能与 555单稳态时间相等或更短,启动周期长一些有利于观察显示的数 字,每次测量只要启动一次。其工作过程:启动脉冲经门1与门2 整形,再经3DG6反相放大变成负启动脉冲去触发555构成的单稳 态电路,555将输出正比于被测电容Cx的定时门控脉冲,在该门 控脉冲(高电平)期间,1MHz时钟脉冲通过门3送到计数译码显示 单元,结果显示的数字大小正比于Cx容量的大小。

555时基电路应用和工作原理

555时基电路应用和工作原理时间:2009-12-28 15:07:12 来源:作者:1 555时基电路的特点555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。

但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。

此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。

由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体,如图1所示。

图1 555集成电路内部结构图555集成电路是8脚封装,双列直插型,如图2(A)所示,按输入输出的排列可看成如图2(B)所示。

其中6脚称阈值端(TH),是上比较器的输入;2脚称触发端(TR),是下比较器的输入;3脚是输出端(Vo),它有O和1两种状态,由输入端所加的电平决定;7脚是放电端(DIS),它是内部放电管的输出,有悬空和接地两种状态,也是由输入端的状态决定;4脚是复位端(MR),加上低电平时可使输出为低电平;5脚是控制电压端(Vc),可用它改变上下触发电平值;8脚是电源端,1脚是地端。

图2 555集成电路封装图我们也可以把555电路等效成一个带放电开关的R-S触发器,如图3(A)所示,这个特殊的触发器有两个输入端:阈值端(TH)可看成是置零端R,要求高电平,触发端(TR)可看成是置位端S,要求低电平,有一个输出端Vo,Vo可等效成触发器的Q端,放电端(DIS)可看成是由内部放电开关控制的一个接点,由触发器的Q端控制:Q=1时DIS端接地,Q=0时DIS端悬空。

另外还有复位端MR,控制电压端Vc,电源端VDD和地端GND。

这个特殊的触发器有两个特点:(1)两个输入端的触发电平要求一高一低,置零端R即阈值端(TH)要求高电平,而置位端s即触发端(TR)则要求低电乎;(2)两个输入端的触发电平使输出发生翻转的阈值电压值也不同,当V c端不接控制电压时,对TH(R)端来讲,>2/3VDD 是高电平1,<2/3VDD是低电平0:而对TR(S)端来讲,>1/3VDD 是高电平1,<1/3VDD是低电平0。

555时基电路的基本特性和用法

555时基电路的基本特性和用法我们在使用555时基电路之前应该先了解它的基本特性。

按照集成电路的分类方法,数字集成电路以外的集成电路都归入模拟集成电路中,因此关于555时基电路的特性可以从非线性模拟集成电路手册中查找。

一、555电路的型号、封装和引脚1.型号我国目前广泛使用的555时基电路的统一型号是:双极型为CB555,CMOS型为CB7555。

这两种电路每个集成片内只有一个时基电路,称为单时基电路。

此外还有一种双时基电路,在一个集成片内包含有两个完全相同、又各自独立的时基电路。

它们的型号分别是CB556和CB7556。

表1列出它们的型号和与之对应的国内、国外常用的型号。

2.封装和引脚555单时基电路的封装有8脚圆形和8脚双列直插型两种。

圆形集成电路引脚的编号方法是把引脚朝下,带标志的引脚置于上倒,从带标志的引脚左边开始按逆时针方向顺序编号,见图1(a)。

双列直插型单时基电路的引脚编号方法是把集成片平放,从带标志的引脚开始按逆时针方向顺序编号,见图1(b)。

556双时基电路的封装只有14脚双列直插型一种。

引脚按双列直插型集成电路的统一方法编号,见图1(C)。

CB555(CB7555)单时基电路各引脚的作用见图1(a)、(b)和图2。

6脚是阈值输入端TH,2脚是触发输人端,5脚是控制端VC,4脚是主复位端,8脚是电源正极Vcc或VDD。

3脚是输出端VO,7脚是放电端DIS,1 脚是公共地端 GND或VSS。

对双时基电路CB556(CB7556)来讲,两个时基电路共用一个电源端(14)一个地端(7),其余12个脚按左右分开,各为一个独立的时基电路,见图1(c)。

为了便于应用,在图2上,用圆圈内的数码表示出单时基电路的引脚号。

在小方框内用斜线隔开的2个数码表示出双时基电路左右两个时基电路的引脚号。

例如 5/9表示左边时基电路输出端V01的引脚号是5,右边时基电路输出端V02的引脚号是9。

双极型和CMOS型555电路的内部电路和参数虽然不同,但它们的引脚编号和功能是完全相同的。

555时基电路

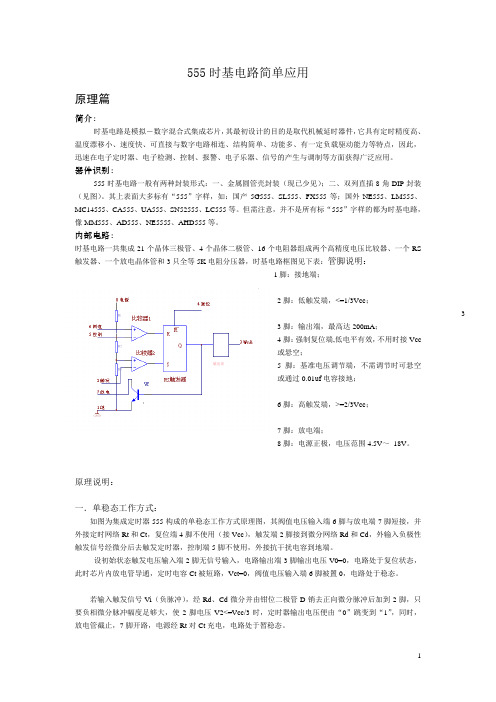

555时基电路简单应用原理篇简介:时基电路是模拟-数字混合式集成芯片,其最初设计的目的是取代机械延时器件,它具有定时精度高、温度漂移小、速度快、可直接与数字电路相连、结构简单、功能多、有一定负载驱动能力等特点,因此,迅速在电子定时器、电子检测、控制、报警、电子乐器、信号的产生与调制等方面获得广泛应用。

器件识别:555时基电路一般有两种封装形式:一、金属圆管壳封装(现已少见);二、双列直插8角DIP封装(见图)。

其上表面大多标有“555”字样,如:国产5G555、SL555、FX555等;国外NE555、LM555、MC14555、CA555、UA555、SN52555、LC555等。

但需注意,并不是所有标“555”字样的都为时基电路,像MM555、AD555、NE5555、AHD555等。

内部电路:时基电路一共集成21个晶体三极管、4个晶体二极管、16个电阻器组成两个高精度电压比较器、一个RS触发器、一个放电晶体管和3只全等5K电阻分压器,时基电路框图见下表:管脚说明:1脚:接地端;2脚:低触发端,<=1/3Vcc;33脚:输出端,最高达200mA;4脚:强制复位端,低电平有效,不用时接Vcc或悬空;5脚:基准电压调节端,不需调节时可悬空或通过0.01uf电容接地;6脚:高触发端,>=2/3Vcc;7脚:放电端;8脚:电源正极,电压范围4.5V~18V。

原理说明:一.单稳态工作方式:如图为集成定时器555构成的单稳态工作方式原理图,其阀值电压输入端6脚与放电端7脚短接,并外接定时网络Rt和Ct,复位端4脚不使用(接Vcc),触发端2脚接到微分网络Rd和Cd,外输入负极性触发信号经微分后去触发定时器,控制端5脚不使用,外接抗干扰电容到地端。

设初始状态触发电压输入端2脚无信号输入,电路输出端3脚输出电压V0=0,电路处于复位状态,此时芯片内放电管导通,定时电容Ct被短路,Vct=0,阀值电压输入端6脚被置0,电路处于稳态。

简述555时基电路的功能

555时基电路的功能1. 介绍555时基电路的概念555时基电路是一种由现代集成电路制成的多种用途的集成电路。

它是由Hans Camenzind在1971年发明的,并且由尺寸小巧但功能强大的MOSFET晶体管组成。

555时基电路因其广泛应用于各种定时、计数以及波形发生器等电子电路中而备受欢迎。

2. 555时基电路的组成555时基电路由7个主要元件组成,它们是:两个比较器、一个电压反相器、一个RS触发器、一个电压控制电流源、一个输出级以及一个控制电压电阻网络。

3. 555时基电路的基本功能555时基电路的主要功能可归纳如下:3.1 稳定的时间基准555时基电路能够提供稳定的时间基准,这是由其内部的电阻和电容网络决定的。

通过调整这些元件的值,可以产生精确的时间延迟和周期。

3.2 时钟信号生成555时基电路可以用作一个时钟信号发生器,根据设定的电容充电和放电时间,可以产生各种频率的高精度时钟信号。

3.3 定时器和延时器555时基电路可以被配置为一个定时器或延时器。

当555时基电路作为定时器使用时,当达到指定时间时,输出电平会发生变化。

而当555时基电路作为延时器使用时,当触发脉冲作用在电路上时,输出电平会在一段时间后发生变化。

3.4 矩形波发生器555时基电路能够产生一种称为矩形波的波形信号。

通过调整电阻和电容的值,可以控制矩形波信号的频率和占空比。

矩形波信号广泛应用于各种测量和计数电路中。

3.5 单稳态触发器555时基电路还可以被用作一个单稳态触发器。

在单稳态触发器模式下,当有一个触发脉冲时,输出电平会在一段时间内保持为高电平,然后恢复到低电平。

这种功能可以被用于产生各种脉冲信号。

4. 555时基电路的应用领域由于其多功能和易用性,555时基电路在各种电子电路领域得到了广泛应用。

以下是几个常见的应用领域:4.1 定时器和计数器电路555时基电路常被用作定时器和计数器电路的核心部件。

它可以用来产生精确的时间延迟、控制定时开关以及完成各种计数任务。

555时基电路工作原理

555时基电路工作原理一、引言555时基电路是一种常用的集成电路,广泛应用于计时、脉冲生成、频率分频等领域。

本文将详细介绍555时基电路的工作原理。

二、555时基电路概述555时基电路是一种集成电路,由美国公司Signetics(现为NXP公司)于1971年推出。

它是一种多功能定时器和脉冲发生器,由比较器、RS触发器和放大器组成,可工作于单稳态、多稳态和振荡器模式。

三、555时基电路的内部结构555时基电路的内部结构包括比较器、RS触发器、放大器和输出级等部分。

比较器用于比较输入电压与参考电压,RS触发器用于存储输出状态,放大器用于放大信号,输出级用于驱动外部负载。

四、555时基电路的工作原理1. 单稳态模式在单稳态模式下,555时基电路输出一个固定时长的脉冲。

当触发引脚(TRIG)收到一个低电平脉冲时,555时基电路的输出引脚(OUT)会产生一个高电平脉冲,时长由外部电容和电阻决定。

当电容充电至2/3 Vcc时,输出引脚的电平变为低电平,脉冲结束。

2. 多稳态模式在多稳态模式下,555时基电路的输出引脚可以处于两种不同的状态,高电平和低电平。

通过控制控制引脚(CONT)的电压,可以实现状态的切换。

当控制引脚为高电平时,输出引脚为高电平;当控制引脚为低电平时,输出引脚为低电平。

3. 振荡器模式在振荡器模式下,555时基电路输出一个连续的方波信号。

通过控制外部电容和电阻的数值,可以调整输出方波的频率和占空比。

五、555时基电路的应用555时基电路具有广泛的应用领域,包括但不限于以下几个方面:1. 计时器:555时基电路可用作计时器,通过调整外部电容和电阻的数值,实现不同的计时功能。

2. 脉冲发生器:555时基电路可用作脉冲发生器,通过调整触发引脚的输入脉冲,产生不同的脉冲信号。

3. 频率分频器:555时基电路可用作频率分频器,通过控制外部电容和电阻的数值,将输入信号的频率分频为较低的频率。

六、555时基电路的优缺点555时基电路具有以下优点:1. 简单易用:555时基电路的引脚定义清晰,使用方便。

简述555时基电路的功能

简述555时基电路的功能555时基电路是一种集成电路,由双稳态多谐振荡器、比较器和放大器组成。

它的主要功能是产生各种不同的脉冲信号和定时信号,广泛应用于计时、闪光灯、音乐合成、遥控器等领域。

一、555时基电路的原理1. 双稳态多谐振荡器555芯片中的双稳态多谐振荡器是其核心部分。

当输入电压超过阈值电平时,输出为高电平;当输入电压低于触发电平时,输出为低电平。

这使得芯片能够在两个状态之间进行切换,并产生周期性的脉冲信号。

2. 比较器和放大器555芯片中的比较器和放大器用于检测输入信号与阈值之间的差异,并将其转换为输出信号。

比较器将输入信号与参考电压进行比较,并产生高或低的数字输出信号。

放大器用于增强比较后得到的信号以便更好地控制输出。

二、555时基电路的应用1. 计时555时基电路可以用作计时器或定时开关。

通过调整元件参数,可以产生不同的时间延迟,从几微秒到数小时不等。

它可以用于定时器、闹钟、计数器等应用。

2. 闪光灯555时基电路可以用来控制摄影中的闪光灯。

通过调整元件参数和输入信号,可以产生不同的脉冲宽度和频率,从而控制闪光灯的亮度和持续时间。

3. 音乐合成555时基电路可以用于音乐合成。

通过将输入信号与输出信号相结合,可以产生各种不同的音调和节奏。

这种技术被广泛应用于电子琴、合成器和其他音乐设备中。

4. 遥控器555时基电路可以用来制作遥控器。

通过设置特定的频率和编码方式,可以将信号发送到接收器以控制设备的操作。

这种技术被广泛应用于家庭娱乐系统、汽车安全系统和其他遥控设备中。

三、555时基电路的优点1. 稳定性高555芯片具有很高的稳定性,能够在广泛的工作温度范围内保持一致性。

2. 简单易用555芯片非常容易使用,并且在设计过程中需要的元件数量较少,因此可以减少成本和复杂性。

3. 可靠性高555芯片具有很高的可靠性,能够在长时间内保持稳定的工作状态。

四、555时基电路的缺点1. 精度有限555芯片在一定程度上受到元件参数和工作温度的影响,因此其精度有限。

555时基电路工作原理

555时基电路工作原理一、引言555时基电路是一种常用的集成电路,广泛应用于定时、脉冲和振荡等电子设备中。

本文将详细介绍555时基电路的工作原理。

二、555时基电路的基本结构555时基电路由比较器、RS触发器、RS锁存器和输出级组成。

其中,比较器用于比较输入电压与参考电压,RS触发器用于产生输出脉冲,RS锁存器用于锁存输出状态,输出级用于放大输出信号。

三、555时基电路的工作原理1. RS触发器工作原理555时基电路中的RS触发器是由两个交叉耦合的双稳态触发器构成。

其中一个触发器作为SET端,另一个触发器作为RESET端。

输入电压通过SET和RESET端的控制,触发器的输出状态发生变化。

2. RS锁存器工作原理555时基电路中的RS锁存器由两个交叉耦合的NAND门构成。

其中一个NAND门的输出连接到另一个NAND门的输入,形成正反馈回路。

输入电压通过控制两个NAND门的输入,锁存器的输出状态保持不变。

3. 比较器工作原理555时基电路中的比较器用于比较输入电压与参考电压。

当输入电压大于参考电压时,比较器输出高电平;当输入电压小于参考电压时,比较器输出低电平。

4. 输出级工作原理555时基电路中的输出级由双稳态触发器和放大器构成。

当RS触发器的输出状态发生变化时,输出级的放大器放大输出信号,并输出给外部电路。

四、555时基电路的工作模式1. 单稳态模式在单稳态模式下,555时基电路在接收到触发信号后,输出一个固定宽度的脉冲。

通过调节电阻和电容的数值,可以控制脉冲的宽度。

2. 延时模式在延时模式下,555时基电路在接收到触发信号后,输出一个持续时间可调的脉冲。

通过调节电阻和电容的数值,可以控制脉冲的持续时间。

3. 振荡模式在振荡模式下,555时基电路自身产生周期性的脉冲信号。

通过调节电阻和电容的数值,可以控制脉冲的频率和占空比。

五、555时基电路的应用领域555时基电路广泛应用于各种定时、脉冲和振荡的电子设备中,如计时器、闪光灯、报警器、电子钟等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

555/556时基电路的特点和封装

常见的数字或模拟集成电路型号的阿拉伯数字,仅表示其编号,而555时基集成电路的3个“5”,却有具体的内涵,故各生产厂家无一例外地在型号中加以保留。

这是因为在该集成电路基片上的基准电压电路是由三个误差极小的5KΩ电阻组成,分压精度高。

555电路大量应用于电子控、电子检测、仪器仪表、家用电器、音响报警、电子玩具等诸多方面。

可用作振荡器、脉冲发生器、延时发生器、定时器、方波发生器、单稳态触发振荡器、双稳态多谐振荡器、自由多谐振荡器、锯齿波产生器、脉宽调制器、脉位调制器等等。

555时基电路之所以得到这样的广泛应用,在于它具有如下几个特点:

1、555在电路结构上是由模拟电路数字电路组合而成,它将模拟功能与逻辑功能兼容为一体,能够产生精确的时间延迟和振荡。

它拓宽了模拟集成电路的应用范围。

2、该电路采用单电源。

双极型555的电压范围为1.5V~15V;而CMOS型的电源适应范围更宽,为2V~18V。

这样,它就可以和模拟运算放大器和TTL或CMOS数字电路共用一个电源。

3、555可独立构成一个定时电路,且定时精度高。

4、555的最大输出电流达200mA,带负载能力强,可直接驱动小电机、喇叭、继电器等负载。

图1

555时基集成电路的封装外形一般有两种,一种是做成8脚圆形TO-99型,如图1中(a)所示;另一种是8脚双列直插式封装,如图1中(b)所示。

556双时基集成电路内含两个相同的时基电路,双列直插14脚封装,如图2所示。

图2

CMOS型555/556时基集成电路与双极型的555/556管脚排列完全相同,国产型号的555/556与国外产品的管脚排列也一致,易于互换。

同时应指出,CMOS型555/556在绝大多数场合都可以直接替代双极型555/556,但CMOS型的驱动电流较双极型的要小,且多数电参数都有所改善,如静态电流300μA,阈值端、触发端、复位端等的输入阻抗高达1010欧姆,电源电压的适应范围也加宽,为2~18V。