设置约束规则

allegro 约束规则设置

allegro 约束规则设置【原创版】目录1.Allegro 约束规则的概念2.Allegro 约束规则的设置方法3.Allegro 约束规则的实际应用4.Allegro 约束规则的优点与局限性正文一、Allegro 约束规则的概念Allegro 是一款专业的 EDA(电子设计自动化)软件,广泛应用于电路设计领域。

在 Allegro 中,约束规则是一种用于指导和约束电路设计过程的工具,可以帮助设计者更加高效、精确地完成电路设计。

二、Allegro 约束规则的设置方法1.打开 Allegro 软件,导入或创建需要设置约束规则的电路设计项目。

2.在设计界面中,找到需要添加约束规则的元件或线路,右键选择“Properties”(属性)。

3.在弹出的属性对话框中,找到“Constraints”(约束)选项卡。

4.在“Constraints”(约束)选项卡中,可以根据需要设置各种约束规则,如位置约束、尺寸约束、角度约束等。

5.设置完毕后,点击“OK”按钮关闭属性对话框,约束规则即可生效。

三、Allegro 约束规则的实际应用1.位置约束:通过设置位置约束,可以精确控制元件在电路板上的位置,确保电路布局的稳定性和可靠性。

2.尺寸约束:通过设置尺寸约束,可以控制元件的大小和间距,提高电路密度和性能。

3.角度约束:通过设置角度约束,可以确保元件和线路的摆放方向符合设计要求,提高电路的可读性和可维护性。

四、Allegro 约束规则的优点与局限性1.优点:Allegro 约束规则可以有效地提高电路设计的精度和效率,降低设计错误率,提高设计质量。

2.局限性:虽然 Allegro 约束规则功能强大,但设置过程较为繁琐,需要设计者具备一定的专业知识和操作技巧。

此外,约束规则的设置和调整可能需要多次迭代,对设计者的耐心和经验有一定要求。

Excel数据验证技巧如何设置有效性约束

Excel数据验证技巧如何设置有效性约束Excel是一款功能强大的电子表格软件,在商务和学术领域广泛应用。

为了确保数据的准确性和一致性,Excel提供了数据验证功能,可以通过设置有效性约束来限制输入数据的范围和格式。

本文将介绍Excel中的数据验证技巧,帮助读者更好地掌握有效性约束的设置方法。

1. 基本概念在Excel中,有效性约束是一种规则,用于限制单元格中输入的数据。

它可以确保数据符合特定条件,比如数值范围、文本长度、日期格式等。

通过设置有效性约束,可以避免输入错误和数据不一致性,提高数据处理的准确性。

2. 设置有效性约束2.1 打开数据验证对话框在Excel中,设置有效性约束的第一步是打开数据验证对话框。

选择需要设置约束的单元格,然后点击“数据”选项卡,再点击“数据验证”按钮。

或者使用快捷键Alt+D+L。

2.2 选择验证条件在数据验证对话框中,选择“设置”选项卡,可以看到多种验证条件可供选择。

根据实际需求,选择适合的验证条件,比如整数、小数、日期、时间、文本长度等。

2.3 配置验证规则在验证条件选择完毕后,需要配置具体的验证规则。

根据选定的条件,在相应的输入框中输入约束规则。

例如,如果选择整数条件,可以设置最小值、最大值等参数;如果选择文本长度条件,可以设置最小长度、最大长度等参数。

2.4 配置输入消息和错误警告在数据验证对话框的“输入消息”选项卡中,可以配置一个输入提示,以提醒用户输入数据的要求或输入的意义。

而在“错误警告”选项卡中,可以配置一个错误警告,以提醒用户输入错误或不合法数据时的提示。

这些消息和警告对于保证数据输入的准确性和规范性非常重要。

2.5 应用有效性约束完成对数据验证对话框中的设置后,点击“确定”按钮,就可以将有效性约束应用到选择的单元格中。

此时,输入的数据将会受到设置的约束条件的限制。

3. 实际应用场景有效性约束在实际应用中非常广泛。

下面列举几个常见的应用场景。

3.1 数值范围限制在进行数据统计和分析时,可能需要设置数值范围的有效性约束。

allegro 16.3 约束规则设置

Allegro 16.3约束规则设置约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB设计流程中用于管理所有工具的高速电子约束。

可以使用约束管理器和SigXplorer Expert 开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。

所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。

电子约束(ECSets)就是限制PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns。

以下图为一约束设置窗口。

一、说明先解释一下约束的类型以及约束中用到的简写名词,如下图所示:1、NCIs(NET CLASS)由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。

如下图所示。

2、NCC(Net Class-Class)一般用在约束组与组之间的间距的时候使用,如下图。

3、DPr(Differential Pairs)差分对一组差分对一般由两条Xnet或者net以差分走线的方式组成,如下图。

差分对的形成有两种方式:一是由模型指定的差分对,再者就是由用户自己定义的差分对。

•模型定义的差分对:可以在器件信号模型中指定差分对,可以使用PCB Design,PCB SI,SigXplores 来将模型指定给相应的元件。

•用户定义的差分对:可以在约束管理器中 Net 一级的对象中创建差分对,可以灵活的更改差分对命名和更改差分对成员,但是没有模型指定差分对的精确性。

以下是设置差分对规则时,需要赋予约束的项。

针对以上约束中用到的一些约束点进行解释说明:差分对的worksheets包含5个主要的约束目录:(1)Pin Delay此值指一对网络之间管脚封装上的延迟,单位是时间ns 或者长度mil。

(2) 不耦合长度(Uncoupled Length)不耦合长度约束是用来限制差分对的一对网络之间的不匹配长度。

cadence 16.2约束规则设置

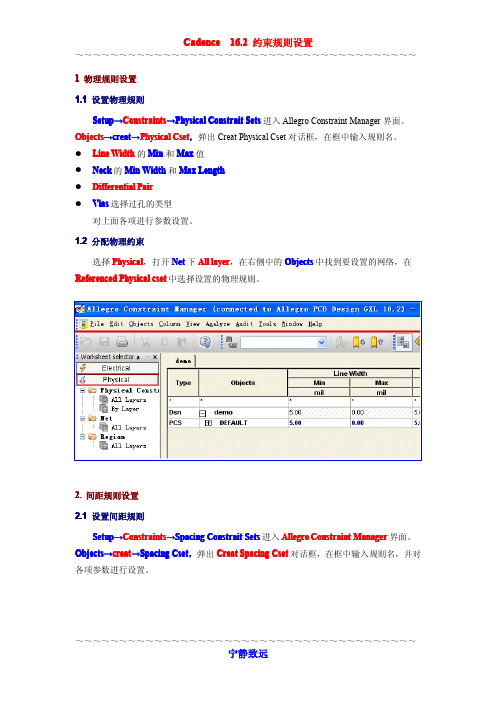

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 1 物理规则设置 1.1 设置物理规则 →Constraints →Physical Constrait Sets 进入 Allegro Constraint Manager 界面。 Setup Setup→ Constraints→ →creat →Physical Cset,弹出 Creat Physical Cset 对话框,在框中输入规则名。 Objects Objects→ creat→ � � � � Line Width 的 Min 和 Max 值 Neck 的 Min Width 和 Max Length Differential Pair Vias 选择过孔的类型 对上面各项进行参数设置。 1.2 分配物理约束 选择 Physical,打开 Net 下 All layer,在右侧中的 Objects 中找到要设置的网络,在 Referenced Physical cset 中选择设置的物理规则。

3. 设置网络属性 →Constraints →Constrait manager 后,打开 Properties ,分别对 Net Properties 下 Setup Setup→ Constraints→ 的 Electrical Properties,General Properties 和 Ratsnest Properties 进行设置。 4. 元件属性设置 4.1 设置元件属性 →Constraints →Constrait manager 后 , 打 开 Properties , 分 别 对 Component Setup Setup→ Constraints→ Properties 下的 General,Thermal,Swapping 和 Reuse 属性进行设置。 4.2 设置管脚属性 Setup →Constraints →Constrait manager 后,打开 Properties ,分别对 Pin Properties Setup→ Constraints→ 下的 General,Shapes 和 Manufacturing 属性进行设置。

allegro 约束规则设置

allegro 约束规则设置摘要:1.Allegro 约束规则的概念与作用2.Allegro 约束规则的设置方法3.Allegro 约束规则的实际应用4.Allegro 约束规则的优点与局限性正文:【1.Allegro 约束规则的概念与作用】Allegro 是一款专业的PCB 设计软件,其中的约束规则设置是PCB 设计过程中至关重要的一环。

约束规则是指在设计过程中,对元件、走线等进行布局和布线的限制条件,以确保设计满足电路功能和性能要求。

通过设置约束规则,可以有效地提高设计效率和准确性,降低设计风险。

【2.Allegro 约束规则的设置方法】在Allegro 中设置约束规则,可以分为以下几个步骤:(1)打开Allegro 软件,导入或创建PCB 设计文件。

(2)在设计界面中,选择需要设置约束规则的元件或走线,可以在原理图或布局视图中进行操作。

(3)点击鼠标右键,选择“约束规则”选项,打开约束规则对话框。

(4)在约束规则对话框中,根据需要设置的约束条件,分别设置“宽度”、“间距”、“角度”等参数。

同时,可以设置约束规则的优先级,以满足不同设计需求。

(5)点击“确定”按钮,完成约束规则设置。

【3.Allegro 约束规则的实际应用】Allegro 的约束规则在实际应用中具有广泛的作用,主要包括:(1)设置元件布局位置:通过设置约束规则,可以控制元件在布局中的位置,确保布局的合理性和美观性。

(2)设置走线宽度和间距:通过设置约束规则,可以保证走线的宽度和间距满足设计要求,降低电路故障的风险。

(3)设置元件和走线的角度:通过设置约束规则,可以控制元件和走线的摆放角度,以满足散热、信号传输等性能要求。

【4.Allegro 约束规则的优点与局限性】Allegro 的约束规则具有以下优点:(1)提高设计效率:通过设置约束规则,可以减少手动调整的时间和精力,提高设计效率。

(2)提高设计准确性:约束规则可以确保设计满足电路功能和性能要求,降低设计失误的风险。

ConstraintManager约束规则基本设置

C o n s t r a i n t M a n a g e r约束规则基本设置 Revised by Petrel at 2021约束规则的设置孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。

在AllegroPCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。

首先,需要认识一下,AllegroPCB的约束管理器:在PCB设计界面中,执行Setup/Constraints/ConstraintManager命令,弹出AllegroConstraintManager对话框,如下图。

在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。

约束规则可以按板层、网络或者区域进行设置。

约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。

工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。

在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。

约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。

一、电气规则设置在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/ElectricalCSet命令可新建电气规则。

allegro 约束规则设置

Allegro约束规则设置随着电子商务的不断发展,大量的交易评台涌现出来。

其中,Allegro 作为东欧最大的电商评台,拥有数百万的用户和商家。

为了保证评台的可持续发展和用户的利益,Allegro评台制定了一系列的约束规则,以规范和管理用户的行为。

本文将详细介绍Allegro评台的约束规则设置。

一、账户注册与使用规定1.1 注册要求在注册Allegro评台账户时,用户需要提供真实尊称、唯一识别信息号码等个人信息,以确保账户的真实性和有效性。

1.2 账户使用规定用户在使用账户进行交易时,需要遵守评台规定的交易流程和规则,不得有任何违反法律法规和评台规定的行为,如欺诈、虚假宣传、侵权等。

二、商品交易规定2.1 商品发布规定商家在发布商品时,需提供详细、真实的商品信息,不得发布违禁品或虚假商品,如有违反将面临相应的处罚。

2.2 交易行为规范买家和卖家在交易过程中应遵守规定的交易流程,如按时付款、按时发货,不得擅自修改订单或逾期交易。

三、评价与投诉规定3.1 评价规定买家在收到商品后,可对交易进行评价,评价内容需客观、真实,不得进行恶意、虚假的评价。

3.2 投诉处理规定对于买家或卖家的投诉,评台将进行核实和处理,如发现违规行为,将给予相应的处罚,并保障投诉方的权益。

四、违规处理规定4.1 违规行为处罚对于违反评台规定的行为,评台将根据情节严重程度给予相应的处罚,如下架商品、冻结账户等。

4.2 申诉机制对于被处罚的用户,可通过评台设立的申诉机制进行申诉,评台将重新审核相关情况,并依据申诉结果做出处理。

五、合作商家规定5.1 合作资格要求Allegro评台对合作商家有一定的资质和经营要求,包括经营年限、信誉度等。

5.2 合作权益合作商家可享受评台提供的一系列增值服务和营销支持,提升业务竞争力。

Allegro评台的约束规则设置是为了维护评台的正常运营秩序,保障用户和商家的合法权益,促进良好的交易环境。

用户在使用评台时,需严格遵守相关规定,如有违规行为,将面临相应的处罚。

allegro差分线分组约束规则设置

allegro差分线分组约束规则设置摘要:1.Allegro差分线分组约束规则简介2.设置差分线分组约束规则的步骤3.约束规则的应用场景及优势4.总结与建议正文:1.Allegro差分线分组约束规则简介Allegro软件是一款专业的印刷电路板(PCB)设计软件,其差分线分组约束规则是其中一项重要的功能。

通过这项功能,用户可以实现自动化布局,确保PCB上各个元件的正确位置和连接关系,从而提高整体设计的稳定性和可靠性。

2.设置差分线分组约束规则的步骤在Allegro软件中设置差分线分组约束规则,主要可以分为以下几个步骤:步骤一:创建差分线。

首先,在Allegro中创建差分线,它们用于定义分组约束规则。

步骤二:定义约束规则。

在创建差分线后,设置相应的约束规则,如最小间距、最大间距等。

步骤三:应用约束规则。

将设置好的约束规则应用于需要布局的元件,以确保它们在PCB上的位置和连接关系满足设计要求。

步骤四:检查与修复。

在布局过程中,不断检查PCB设计是否符合约束规则,如有问题,及时进行修复。

3.约束规则的应用场景及优势差分线分组约束规则在以下场景中具有显著优势:- 提高设计效率:通过自动化布局,设计者可以更快地完成PCB设计,减少重复性工作。

- 保证连接可靠性:约束规则确保了元件之间的正确连接,降低了故障风险。

- 优化电路性能:合理的布局可以降低信号干扰,提高电路性能。

- 易于维护:约束规则使得设计更加规范,便于后期维护和升级。

4.总结与建议差分线分组约束规则在Allegro软件中发挥着重要作用,能够帮助设计者实现自动化布局,提高PCB设计的质量。

在使用过程中,建议设计者熟练掌握约束规则的设置方法,并根据实际需求进行调整。

Allegro约束规则设置

Allegro约束规则设置约束规则的设置孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。

在Allegro PCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。

首先,需要认识一下,Allegro PCB的约束管理器:在PCB设计界面中,执行Setup/Constraints/Constraint Manager命令,弹出Allegro Constraint Manager对话框,如下图。

在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。

约束规则可以按板层、网络或者区域进行设置。

约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。

工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。

在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。

约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。

一、电气规则设置在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/Electrical CSet命令可新建电气规则。

1、选择信号完整性仿真规则Signal Integrity属性,其中包括电气属性、反射属性、单调失真属性、初始串扰、仿真串扰以及同步开关噪声这六个规则设置。

Allegro16.6约束规则设置详解

Allegro16.6约束规则设置详解前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围7、设置等长7.1、不过电阻的NET等长7.2、过电阻的XNET等长7.3、T型等长8、设置通用属性9、差分规则设置9.1、创建差分对9.2、设置差分约束10、Pin Delay二、高级约束规则设置11、单个网络长度约束12、a+b类长度约束13、a+b-c类长度约束14、a+b-c在最大和最小传播延迟中的应用1、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示(2)、定义特殊的间距约束点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。

取一个有意义点的名字,如下图所示,单击OK。

其值是从默认规则拷贝的,先修改其值。

按住Shift键选中所有,输入12,回车。

然后为所需要设置的网络分配规则单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示(3)、设置Class-Class规则若针对不同的信号群组有不同的间距规则,则需要设置Class-Class选到Net Class-Class后,在右边CLOCK(2)上右键选择Ctreat-Class-Class...,如下图所示选择2个不同的Net Classes,如下图所示,单击OK如下图所示。

在右边的Referenced Spacing CSet栏可以修改其值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

约束管理器

命令:setup->constraints->constraint manager

电气 规则

线宽 规则

规则对象 规则应用网络

规则设置区域

间距 规则

规则应用区域

命令:analyze->analysis modes

选择 需要 设置 项目

设 置 分 析 选 项

设置线宽规则

默认规则

设置间距规则

默认规则 线对其他对象的规则,如线对过孔 (via),线对引脚(pins),以及对 SHPAP , HOLE等 所有对象的规则

创建新的间距规则

命令:选中default->右键->create->spacing Cset

新间距规则命名

新间距规则命名 命名要见名知意 比如本列:电源线,间距:10MIL

Analyze>analysis modes: design modes

设 置 设 计 约 束

设置设计约束

Analyze>analysis modes: design modes(package)

设置元件属性

单击某一网络、元件或者引脚可 直接定位到PCB图中显示。

网络属性

元件属性

设置布线约束

新何拷贝而来 默认为右键点击时选择的项目

新线宽规则设置-PINS

其他对象新间距规则设置步骤相同,若需 要所有规则在同一窗口设置,选择ALL

将新规则指派给网络

将新间距规则指派到某区域

选择REGION,点击默认规则,右键->create->region

创建新区域规则

设置区域规则参数

在PCB EDITOR中创建相 应区域

1. 回到PCB EDITOR 2. 菜单:shape->rectangle 3. 在option控制面板中,选 择Constraint 类,在 Asssign to Region中选择 新建的region。 4. 设置完成后在图纸绘制区 域。

对某网络单独设置规则

不是所有规则都需要首先创建新的规则集合。 对某些网络可以直接修改约束规则 方法:选择该NET,直接编辑相关规则参数。

调入电器规则 创建BUS 设置线路 拓扑结构 分支长度

设置阻抗

设置最大、最小传输延时 设置布线总长度 设置差分对 设置相对传输延时

表层布线长度

平行线长度

Electrical constraint set:使用最多的是net选项下的routing->wiring

创建总线

编辑总线

直接调入规则

选中需要设置的网络:右键->constraint set references

Relative propagation delay

瓶颈线宽

新建线宽规则

命令:选中default->右键->create->Physical Cset

新建规则命名

新线宽规则命名 命名要见名知意 比如本列:电源线,宽度:20MIL

新由何拷贝而来 默认为右键点击时选择的项目

新线宽规则设置

将新规则应用指派到相应网 路

选择 NET->ALL LAYERS 选择需要应用新规则的网络如图所示应用 新的规则

直接设置方法

拓扑 分支 长度 最大 布线 长度 平行 线长 度

设置过孔数

最大数量 实际数量

设置阻抗

目标阻抗 限度范围

设置最大最小延迟

Min/max propagation delays

最小延迟

最大延迟

设置总布线长度

Total etch length 布线长度最小值 布线长度最大值

设置相对传输延迟