cadence 16.2约束规则设置

Cadence_Allegro16.2常用操作方法

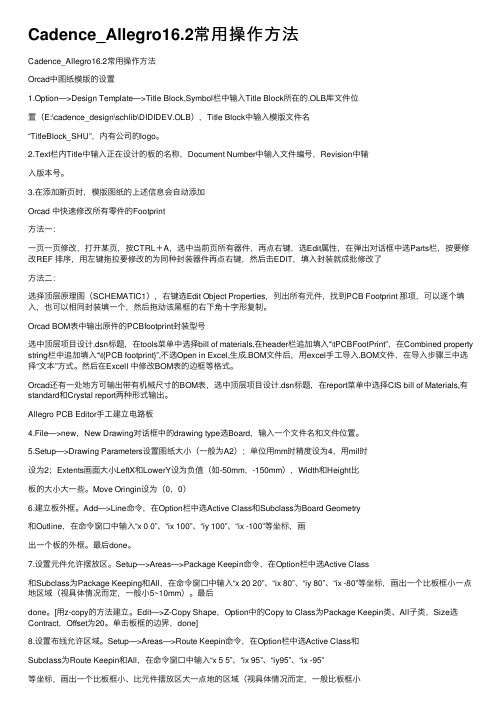

Cadence_Allegro16.2常⽤操作⽅法Cadence_Allegro16.2常⽤操作⽅法Orcad中图纸模版的设置1.Option—>Design Template—>Title Block,Symbol栏中输⼊Title Block所在的.OLB库⽂件位置(E:\cadence_design\schlib\DIDIDEV.OLB),Title Block中输⼊模版⽂件名“TitleBlock_SHU”,内有公司的logo。

2.Text栏内Title中输⼊正在设计的板的名称,Document Number中输⼊⽂件编号,Revision中输⼊版本号。

3.在添加新页时,模版图纸的上述信息会⾃动添加Orcad 中快速修改所有零件的Footprint⽅法⼀:⼀页⼀页修改,打开某页,按CTRL+A,选中当前页所有器件,再点右键,选Edit属性,在弹出对话框中选Parts栏,按要修改REF 排序,⽤左键拖拉要修改的为同种封装器件再点右键,然后击EDIT,填⼊封装就成批修改了⽅法⼆:选择顶层原理图(SCHEMATIC1),右键选Edit Object Properties,列出所有元件,找到PCB Footprint 那项,可以逐个填⼊,也可以相同封装填⼀个,然后拖动该⿊框的右下⾓⼗字形复制。

Orcad BOM表中输出原件的PCBfootprint封装型号选中顶层项⽬设计.dsn标题,在tools菜单中选择bill of materials,在header栏追加填⼊“\tPCBFootPrint”,在Combined property string栏中追加填⼊“\t{PCB footprint}”,不选Open in Excel,⽣成.BOM⽂件后,⽤excel⼿⼯导⼊.BOM⽂件,在导⼊步骤三中选择“⽂本”⽅式。

然后在Excell 中修改BOM表的边框等格式。

Orcad还有⼀处地⽅可输出带有机械尺⼨的BOM表,选中顶层项⽬设计.dsn标题,在report菜单中选择CIS bill of Materials,有standard和Crystal report两种形式输出。

Cadence Allegro 16.2规则设置

Spacing规则(约束)Rexdlutarm@2009-07-02 Allegro 16.0以后版本的约束规则设置较之前有很大改变,对于用惯了15.x的人来说,很多不习惯新的约束管理器。

和在对待女人的态度上,恰相反。

80后说90后脑残,15.7说16.2脑残,Xp说Vista脑残。

Vista确实很脑残。

新事物取代旧事物是自然界发展的客观规律。

说明:1本文只介绍了Spacing约束的设置,因为Physical规则通常来说都设置的非常简单。

掌握了Spacing规则Physical规则对你来说一定是小Case。

另外,Physical 规则的设置也写的话,一定显得都是在重复Spacing的设置;2文中所有的规则(约束),如不特殊说明默认情况下均指Spacing规则(约束);3对于Electrical的约束,是另一种约束,本文不作讨论。

约束的设置方式:1直接的:Net中写数值,2 间接的:创建Constraint Set,然后Assign给Net;这两种都很常用,后者管理方便。

在Physical和Spacing设置中用后者比较好,但是在Electrical中,我看到很多很多的人会混合使用。

使用第二种约束设置方式的约束设置步骤:1约束的对象2约束的内容3给对象分配内容1这3个步骤默默的引导着所有间接约束的设置。

基本约束预备先理解:Net class2Net class-classRegionRegion-classRegion-class-classBus……现在不理解,想跳过去。

没关系,你早晚都要理解的。

最简单和稍微复杂一点的约束:最简单的就是default的约束,稍微复杂一点的就是修改了一点默认的约束。

再复杂一些的约束:你可能会想让不断变化的CLK(我们不考虑是不是差分)和其他的线离的远一些。

在Constraint Set中Create规则并设置规则的内容:Creat & Set之后3给Net分配规则:更高级的约束:What Can U Think?有了一根线的约束,贪婪的本性会使你你很快上升到两根线(通常是Diff)和更多线的约束。

(整理)Cadence_SPB16.2入门教程——PCB布线.

Cadence_SPB16.2入门教程——PCB布线(一)PCB布线4.1 PCB层叠结构层叠结构是一个非常重要的问题,不可忽视,一般选择层叠结构考虑以下原则:·元件面下面(第二层)为地平面,提供器件屏蔽层以及为顶层布线提供参考平面;·所有信号层尽可能与地平面相邻;·尽量避免两信号层直接相邻;·主电源尽可能与其对应地相邻;·兼顾层压结构对称。

对于母板的层排布,现有母板很难控制平行长距离布线,对于板级工作频率在 50MHZ以上的(50MHZ以下的情况可参照,适当放宽),建议排布原则:·元件面、焊接面为完整的地平面(屏蔽);·无相邻平行布线层;·所有信号层尽可能与地平面相邻;·关键信号与地层相邻,不跨分割区。

基于以上原则,对于一个四层板,优先考虑的层叠结构应该是:·S ←信号·G ←地平面·P ←电源层·S ←信号对于一个六层板,最优的层叠结构是:·S1 ←信号·G1 ←地平面·S2 ←信号·G2 ←地平面·P ←电源层·S4 ←信号对于一个八层板,有两种方案:方案 1:方案2:·S1 ←信号S1 ←信号·G1 ←地平面G1 ←地平面·S2 ←信号S2 ←信号·G2 ←地平面P1 ←电源层·P ←电源层G2 ←地平面·S3 ←信号S3 ←信号·G3 ←地平面P2 ←电源层·S4 ←信号S4 ←信号方案2主要是比方案1多了一个电源层,在电源比较多的情况下可以选择方案2。

对于更多层的结构也是按照上面的原则来定,可以参考其它的资料。

下面以SMDK6410核心板(设计为八层板)来设置层叠结构,包括规则设置,PCB布线等。

打开程序->Cadence SPB 16.2->PCB Editor,然后打开在第3 章布局好的PCB文件。

Allegro约束规则设置

约束规则的设置孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。

在Allegro PCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。

首先,需要认识一下,Allegro PCB的约束管理器:在PCB设计界面中,执行Setup/Constraints/Constraint Manager命令,弹出Allegro Constraint Manager对话框,如下图。

在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。

约束规则可以按板层、网络或者区域进行设置。

约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。

工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。

在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。

约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。

一、电气规则设置在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/Electrical CSet命令可新建电气规则。

1、选择信号完整性仿真规则Signal Integrity属性,其中包括电气属性、反射属性、单调失真属性、初始串扰、仿真串扰以及同步开关噪声这六个规则设置。

cadence Allegro16.3约束规则

约束规则设置约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB设计流程中用于管理所有工具的高速电子约束。

可以使用约束管理器和SigXplorer Expert 开发电路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。

所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。

电子约束(ECSets)就是限制PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延迟为2ns。

以下图为一约束设置窗口。

一、说明先解释一下约束的类型以及约束中用到的简写名词,如下图所示:由众多nets或者buses、differential pairs、Xnet所组成的类,可对其赋予相似的约束。

如下图所示。

2、NCC(Net Class-Class)一般用在约束组与组之间的间距的时候使用,如下图。

3、DPr(Differential Pairs)差分对一组差分对一般由两条Xnet或者net以差分走线的方式组成,如下图。

差分对的形成有两种方式:一是由模型指定的差分对,再者就是由用户自己定义的差分对。

•模型定义的差分对:可以在器件信号模型中指定差分对,可以使用PCB Design,PCB SI,SigXplores 来将模型指定给相应的元件。

•用户定义的差分对:可以在约束管理器中 Net 一级的对象中创建差分对,可以灵活的更改差分对命名和更改差分对成员,但是没有模型指定差分对的精确性。

以下是设置差分对规则时,需要赋予约束的项。

针对以上约束中用到的一些约束点进行解释说明:差分对的worksheets包含5个主要的约束目录:(1)Pin Delay此值指一对网络之间管脚封装上的延迟,单位是时间ns 或者长度mil。

(2) 不耦合长度(Uncoupled Length)不耦合长度约束是用来限制差分对的一对网络之间的不匹配长度。

若“gather control”设置为ignore,则实际不不耦合长度不包括两个驱动和接收之间的耦合带之外的长度。

Cadence_SPB16.2中文教程

2

图 1.3 表贴元件焊盘设置

如果是通孔焊盘,需要填写的参数有: BEGINLAYER 层的 Regular Pad,Thermal Relief,Anti Pad; DEFAULTINTERNAL 层的 Regular Pad,Thermal Relief,Anti Pad; ENDLAYER 层的 Regular Pad,Thermal Relief,Anti Pad; SOLDEMASK_TOP 层的 Regular Pad; PASTEMASK_TOP 层的 Regular Pad。 如图 1.4 所示。 在 BEGINLAYER、DEFAULTINTERNAL、ENDLAYER 三个层面中的 Thermal Relief 可以 选择系统提供的默认连接方式,即 Circle、Square、Oblong、Rectangle、Octagon 五种,在 PCB 中这几种连接方式为简单的‘+’形或者‘X’形。也可以选用自己画的热风焊盘连接 方式,即选择 Flash。这需要事先做好一个 Flash 文件(见第二节)。这些参数的设置见下面的 介绍。

第 2 章 建立封装 .......................................................................................................10

第 3 章 元器件布局 ...................................................................................................23

第 5 章 输出底片文件 ...............................................................................................70

ConstraintManager约束规则基本设置

C o n s t r a i n t M a n a g e r约束规则基本设置 Revised by Petrel at 2021约束规则的设置孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。

在AllegroPCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。

首先,需要认识一下,AllegroPCB的约束管理器:在PCB设计界面中,执行Setup/Constraints/ConstraintManager命令,弹出AllegroConstraintManager对话框,如下图。

在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。

约束规则可以按板层、网络或者区域进行设置。

约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。

工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。

在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。

约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。

一、电气规则设置在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/ElectricalCSet命令可新建电气规则。

cadence等长规则设置

cadence等长规则设置cadence等长规则设置提到绕等长的问题,就不得不说一下等长约束规则的设置了。

在allegro的规则管理器里,只有你想不到的规则,没有设置不了的。

正是因为其五花八门,所以经常有很多的BUG出现,对于很多人来说,建规则会成为比较难跨越的高山。

等长规则的设置有多种不同的方法,有傻白甜型,有端方君子型,有腹黑高冷型,总有一款适合你的。

1、做人从傻白甜开始望文生义,傻白甜就是操作简单,结果尽如人意的意思了。

这种方法几乎是一步到位的,选中目标网络,单击右键,直接创建Match Group,然后取个好听又好记的名字,如下图。

好了。

2、端方君子,心之所向对于简单的点对点的拓扑,傻白甜能起到相应的作用,但是对于一些比较复杂的拓扑结构,可能就收效甚微了,这时候就需要我们的君子登场了。

为什么说这种方法是端方君子型呢,主要是因为它一步一步,有理有据,按照步骤试一下的话,就会觉得,原来如此,建等长规则还是比较简单的。

下面就是动作分解了,首先选中目标网络,建立net group。

建立net group后,选中建立的net group,单击右键,选择SigXploer命令,打开SigXploe,也可以选择单个网络打开SigXploe,网络的拓扑显示如下。

是感觉真的很美好呢?3、腹黑高冷才是真绝色然而,也有君子搞不定的时候,因为毕竟不是所有的BUG都是光明正大的阳谋,让你可以知道怎么去改正,就像拓扑连接不正确时,可以通过给阻容器件赋模型来解决。

有的BUG就像避无可避的阴谋诡计,比如无法打开SigXploer,器件模型出问题等,无处着手时,这时候就需要剑走偏锋,腹黑的方法才能够一招致胜。

这次直接选择网络建立pin Pair,不管什么拓扑错误或是其他,直接避过,建立点对点的连接,这也正是高冷风范,不管什么BUG,都是“我不听,我不听”。

然后再选择目标pin Pair ,直接建立Match Group 。

cadence规则设置介绍

PROPAGATION_DELAYPROPAGATION_DELAY这个设定主要用来对Net绝对长度的设定,如要求设定一组Net的长度要在Min Mil到Max Mil之间的话,就可以用这种设定来完成.设定值的写法如果一个Net只有连接两个Pin就可以用下面这种语法:L : S : min : max , L:S 是固定格式就可以了,后面的min是Net长度的最小值,max 是最大值如果只要求Net长度在多少之内就可以省略min值,如: L : S : : max相反如果只有求在多少以上就可以省略max值,如:L : S : min :如果一个Net连接多个Pin,而只要求某个Pin到某个Pin的走线长度在多少范围内就可以,这种情况的设定就相对复杂些,具体要写出连接的Pin,语法见下面:Ux1.Piny1 : Ux2: Piny2: min: max, 就是前面要写出具体从那个零件的哪个pin到哪个零件的哪个pin.例子:PROPAGATION_DELAY = L:S:1200 MIL:1400 MIL 后面蓝色部分就是要在设置是输入的,其实MIL可以省略会自动产生,设定走线长度要求在1200Mil到1400Mil间PROPAGATION_DELAY = L:S:1200: 设定走线大于1200Mil就可以了PROPAGATION_DELAY = L:S: :1400 设定走线小于1400Mil就可以了PROPAGATION_DELAY = U1.2:R1.1:500:600 设定U1的Pin2到R1的Pin1的走线长度在500Mil与600Mil之间RELATIVE_PROPAGATION_DELAYRELATIVE_PROPAGATION_DELAY这个设定主要用来对一组Net做等长设定,如要求设定一组Net的长度误差要在Tolerance Mil之间的话,就可以用这种设定来完成. 这里会多一个基准线的概念,就是其它设定的走线需要和这基准线来比较,如果比它长多少,短多少都在Tolerance之内就是达到要求的,语法:Group : G : L : S : Delta : ToleranceGroup :等长组名,不要和以定义的BUS_NAME的值相同,建议可以在原来值前面加R_定义Delta :这个值可能有点难理解,就是设定的这个走线的长度要比基准线长还是短多少,一般都是要求和基准线一样长,那就是这里的为0, 如果要长就用+Delta,短就用-Delta,+可以省略Tolerance :与基准线之间的误差,可以是具体值(xx Mil) 也可以用百分比(xx%),注意:Tolerance的值为+/-多少,如果写50,就是误差为+/- 50Mil, 其实误差就是100Mil另外对一组设定好等长的走线还要指定基准线, 基准线的值和前面一般的一样,就是Delta和Tolerance项省略,那样系统就默认为这组等长线的基准线例:要设定一组Data线等长, 误差为+/-25Mil, 如果没有特别要求特定线为基准,可以自己选择基准线先设定所有走线:RELATIVE_PROPAGATION_DELAY=R_DATA:G:L:S:0:25再特定设基准线: RELATIVE_PROPAGATION_DELAY=R_DATA:G:L:S::如果有根线要比基准线长50Mil则设定为:RELATIVE_PROPAGATION_DELAY=R_DATA:G:L:S:50:25IMPEDANCE_RULEIMPEDANCE_RULE=A:B:C:DA:起点PINB:终点PINC:阻抗的数值大小D:阻抗的误差大小例如:(1).IMPEDANCE_RULE=ALL:ALL:50ohm:10ohm设定走线的阻抗是50ohm,误差值是正负10ohm(2).IMPEDANCE_RULE=U1.1:R1.1:50ohm:20%设定走线在U1.1 到R1.1 之间的阻抗是50ohm,误差是正负20%SWITCH/SETTLE_DELAY在约束管理器界面的“NET”栏部分打开timing,点击switch/settle delay, 在min 和max栏分别设置网络的信号上升沿和下降沿,输入方法为min:“0.25:0.26”,max:“3.25 3.25”即表示网络的信号上升沿和下降沿分别为0.25ns和0.26ns。

CADENCE16.0中添加区域规则的方法

关于在CADENCE16.0中添加区域规则的方法CADENCE16.0在class里面增加了一个新class : constraint region 实际上这个class是属于shap的所以在华这个区域时应该用画shap的工具栏开始吧在option栏中class选到constraint region ,subclass选到你所需要的层top /bottom/all…..选取绘制shap的工具栏中的其中一个都行在PCB上画出你所想约束的区域打开约束管理器选择到你所要约束的对象线宽或是线距这里选择线宽右键选择object一栏在弹出的菜单中选择—create—Region这时会跳出一个对话框会要你给这个区域命名他会有一个默认的名称为了更好表达含义最好用那个区域对象模块命名这里就接受默认的这一栏后面就是约束设置栏这里演示的是设置这个区域的线宽区域设置好后就要把这个规则加到PCB的区域上在shap工具栏选择然后点击之前你所画的约束区域这时这个区域处于选中状态(在find栏中要给shap项打钩才可选中VISIBILITY栏中相应的层要打开才可见)边框高亮时刻编辑的可以拖动边框改变他的大小在option栏中有这一项点击那个空白下拉框会看到你在约束管理器中新建的区域选中你所要的区域此时PCB上的那个约束区域还处于选中状态将鼠标移到选中的区域上点击右键弹出如下菜单选择Assign Region 这是物理上的区域就和规则上的区域就对连接了此时再用information按钮查看物理区域属性会有一条是区域组名再画线你将会看到区域内外有不同的线宽End这种是先画物理约束区域-- 再定区域规则—再连接也可以先定规则---在物理区域的同时指明约束规则16.0对约束规则定义更加细功能也更强设置过程也更加简单我先以为16.0把这个功能给丢弃了按道理也不会cadence这么大的工具不会这样做。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 1 物理规则设置 1.1 设置物理规则 →Constraints →Physical Constrait Sets 进入 Allegro Constraint Manager 界面。 Setup Setup→ Constraints→ →creat →Physical Cset,弹出 Creat Physical Cset 对话框,在框中输入规则名。 Objects Objects→ creat→ � � � � Line Width 的 Min 和 Max 值 Neck 的 Min Width 和 Max Length Differential Pair Vias 选择过孔的类型 对上面各项进行参数设置。 1.2 分配物理约束 选择 Physical,打开 Net 下 All layer,在右侧中的 Objects 中找到要设置的网络,在 Referenced Physical cset 中选择设置的物理规则。

3. 设置网络属性 →Constraints →Constrait manager 后,打开 Properties ,分别对 Net Properties 下 Setup Setup→ Constraints→ 的 Electrical Properties,General Properties 和 Ratsnest Properties 进行设置。 4. 元件属性设置 4.1 设置元件属性 →Constraints →Constrait manager 后 , 打 开 Properties , 分 别 对 Component Setup Setup→ Constraints→ Properties 下的 General,Thermal,Swapping 和 Reuse 属性进行设置。 4.2 设置管脚属性 Setup →Constraints →Constrait manager 后,打开 Properties ,分别对 Pin Properties Setup→ Constraints→ 下的 General,Shapes 和 Manufacturing 属性进行设置。

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

宁静致远

Cadence 16.2 约束规则设置

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 2.2 分配间距约束 选择 Spacing ,打开 Net 下 All layer,在右侧中的 Objects 中找到要设置的网络,在 Referenced Spacing cset 中选择设置的安全间距规则。

2. 间距规则设置 2.1 设置间距规则 →Constraints →Spacing Constrait Sets 进入 Allegro Constraint Manager 界面。 Setup Setup→ Constraints→ →creat →Spacing Cset,弹出 Creat Spacing Cset 对话框,在框中输入规则名,并对 Objects Objects→ creat→ ~~~~~~~~~~~~~

宁静致远