Allegro16.6约束规则设置详解(图文并茂)

Allegro16.6约束规则设置详解(图文并茂)

Allegro16.6约束规则设置详解(图文并茂)此文章由丹心静居整理--- 2014.10.13(为了不侵犯别人的成果,所以在这里做了特殊说明,以示敬意)首先感谢詹书庭编写这篇文章,为我们学习交流Cadence al l egr o软件提供了丰富的知识和方法。

请大家认真学习,不要辜负作者的良苦用心!这篇文章写得很好,操作步骤详细,截图一目了然,通俗易懂,唯一的缺点就是部分截图不是很清晰,我对个别图片做了调整和替换,不易替换的不清晰图片,仔细看下也能明白其中的意思。

俗话说的好,社会在发展,技术在进步,技术的进步在于不断的学习交流和实践。

所以为了方便大家学习交流,为大家提供一个良好的交流平台,在这里留下我们的Q Q群( 原文作者的Q Q群拒绝任何人加入)。

对原文作者表示歉意!学习交流Cadence al l egr o请加Q Q群: 一起来学A l l egRo【2】. 群号:331730476 .以下是正文前言:本文主要讲解Allegro16.6 约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗7、设置等长7.1 NET、不过电阻的等长7.2 XNET、过电阻的等长7.3、T型等长8、设置通用属性9、差分规则设置9.1、创建差分对9.2、设置差分约束10 Pin Delay、二、高级约束规则设置11、单个网络长度约束12、a+b 类长度约束13、a+b-c 类长度约束14、a+b-c 在最大和最小传播延迟中的应用第 2 页1、线间距设置(1)、设置默认间距规则点击CM 图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT 就是默认规则,我们可以修改其值。

按住Shift 键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示(2)、定义特殊的间距约束点选Default 按鼠标右键,执行Create-Spacing CSet加入新规则。

Allegro-16.6-功能集锦

Allegro 16.6 功能集锦➢在Allegro中增加零件及修改连线关系1.Setup - User Preferences Editor – Logic –logic _edit_enabled的Value勾选2.增加零件:Logic - Part Logic 在Part Modification Area 填入相关信息(也可以在Part Selection Area中找到类似的元器件)单击Add再OK3.修改连接关系:单击元器件焊盘,在右边的Options中选择网络。

或者增加新的网络(Create)编辑网络名(Rename)删除网络名(Remove)➢如何在Allegro中即时显示dynamic length(动态走线长度)对话框Setup - User Preferences Editor – Route – Connect – allegro_etch_length_on勾选➢在Allegro中如何将尖角走线改成圆弧走线1.可以直接画圆弧:右边的Options选项中的Line lock选择Arc并勾选最下面的Replace etch(替换原有走线)2.使用slide命令(移动走线):右边的Options选项中 Vertex Action中Move改成Arc Corner,去拉动走线➢在Allegro中如何把DRC标记显示为实心Setup - User Preferences Editor – Display – Visual – display_drcfill勾选➢在Allegro中怎么增加和删除泪滴(teardrop)1.增加泪滴(teardrop):Route – Gloss – parameters... – Fillet and tapered trace勾选,注意勾选前在Fillet and taperedtrace 点击跳出编辑框选择你所需要的对象2.Edit –Delete 右边的Options栏中选择Cline ,在Find栏中Find by name中选择Property ,点击More ,点选Fillet= ,/Apply/OK即可注意:无论加泪滴还是删掉泪滴,一定要先打开所有的走线层,否则,没打开的走线层就不会有执行➢如何在Allegro中设置自动存盘系统自动存盘需要用户自己设置,具体方法如下:Setup - User Preferences Editor – File_management – AutosaveAutosave_dbcheck:设置存盘时是否需要数据检查,如果此项设为存盘时需要数据检查则会使存盘时间加长Autosace_time:自动存盘时间设置。

ALLEGRO约束设置

A L L E G R O约束规则设置介绍目录:第一部分:差分对的约束设置............... 错误!未指定书签。

第二部分:非差分信号约束设置............. 错误!未指定书签。

第三部分:区域约束设置................... 错误!未指定书签。

第四部分:XNet等长设置................... 错误!未指定书签。

本文所有操作与设置均在AllegroPCBeditor15.5环境中进行。

第一部分:差分对的约束设置下面我们将通过对LVDS差分对信号的约束设置分步骤的讲解各个设置过程,或点击图标打开“ConstraintsSys”窗口,将出现下图所示窗口。

点击“Setstandardvalues”,弹出“Defaultvaluesform”界面,在此可设置默认值,且窗口中所有设置值各自分属于spacingrule和Physicalrule中名为“Default”的约束集。

此处我们取默认值。

图1下面步骤2-步骤4为Physical(Line/vias)rule物理特性(线宽和过孔)约束设置过程步骤2:线宽约束设置。

点击“Physical(Line/vias)ruleset→setvalues”,在出现的窗口上方空白处填入新约束名称,如“LVDS_SIG”,然后点击“ADD”,新的约束就产生了。

如果需要设置这是某一层的约束,还要在“subclass”中选择相应的层面。

接下来就在相应栏填入需要的值。

如下图所示:图2如果还有其它信号的线宽要求,请重复上述步骤。

Minlinewidth:最小线宽Maxlinewidth:最大线宽,填0=∞Minneckwidth:Neck模式最小线宽Maxnecklength:Neck模式最大走线长度DiffPairprimarygap:首选差分间距(单端线可不填)DiffPairneckgap:Neck模式差分间距(单端线可不填)过孔规格在“Vialistproperty”中设定,一般设定在默认约束规则下。

Allegro16.6约束规则设置详解_SCC

Allegro16.6约束规则设置详解前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围7、设置等长7.1、不过电阻的NET等长7.2、过电阻的XNET等长7.3、T型等长8、设置通用属性9、差分规则设置9.1、创建差分对9.2、设置差分约束10、Pin Delay二、高级约束规则设置11、单个网络长度约束12、a+b类长度约束13、a+b-c类长度约束14、a+b-c在最大和最小传播延迟中的应用1、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

按住Shift键,点击第一个和最后一个即可选中所示,然后输入一个值,这样就都修改了,如下图所示(2)、定义特殊的间距约束点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。

取一个有意义点的名字,如下图所示,单击OK。

其值是从默认规则拷贝的,先修改其值。

按住Shift键选中所有,输入12,回车。

然后为所需要设置的网络分配规则单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示(3)、设置Class-Class规则若针对不同的信号群组有不同的间距规则,则需要设置Class-Class选到Net Class-Class后,在右边CLOCK(2)上右键选择Ctreat-Class-Class...,如下图所示选择2个不同的Net Classes,如下图所示,单击OK如下图所示。

在右边的Referenced Spacing CSet栏可以修改其值。

Allegro16.6设置等长规则

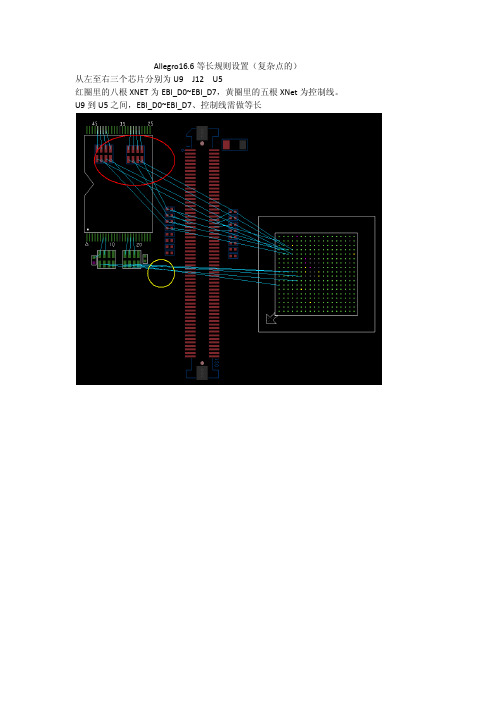

Allegro16.6等长规则设置(复杂点的)从左至右三个芯片分别为U9 J12 U5红圈里的八根XNET为EBI_D0~EBI_D7,黄圈里的五根XNet为控制线。

U9到U5之间,EBI_D0~EBI_D7、控制线需做等长多出来的八根XNET为EBI_D8~EBI_D15J12到U5之间EBI_D0‐ EBI_D15做等长接下来开始步骤:(设模型、X‐NET就不说啦,坛子里有很多说的挺清楚的)将EBI_D0~EBI_D15设为一个Class,EBI_D将EBI_D0~EBI_D15设PINPAIREBI_D0~EBI_D7设置两组PINPAIREBI_D8~EBI_D15设置一组PINPAIR设EBI_D0 拓扑Set‐Constraint红框中填好点ADD再新增另一个规则点ADD点OK后回到以下界面,FILE‐Update Constraint Manager点是出现两组MGrp,每组下面只出现一对,因为仅对EBI_D0设了规则。

EBI_D0和EBI_D1~D7的拓扑一样的,将刚才生成的ElecCset赋予它们赋予它们的同时,两组MGrp里的PPr也在增多但EBI_D8~D15的拓扑和它们不一样,所以得重新建拓扑设规则省略几步,和之前设的时候一样的点是,可以看到EBI_D8被赋予规则EBI_D8,EBI_D9~D15拓扑与EBI_D8一样的,所以把EBI_D8这一规则分别赋予它们。

目前为止,EBI_D0~D15从U5到J12就做了等长,走线时就有控制进度条显示但是从U5到U9这一段还有几根控制线未加进来找到这几根控制线,add to MatchGroupEBINAND这一MatchGroup里就有这些XNET了。

红色框中选择ALL DRIVERS..红色框中改为0mil:100milU9到U5之间,EBI_D0~EBI_D7、控制线就做好等长啦、这种设等长的方式思路挺清晰的,所以就推荐给大家,或者是给还不会设等长的一点参考。

cadence allegro 16.6入门学习参考步骤

1

2 2

3

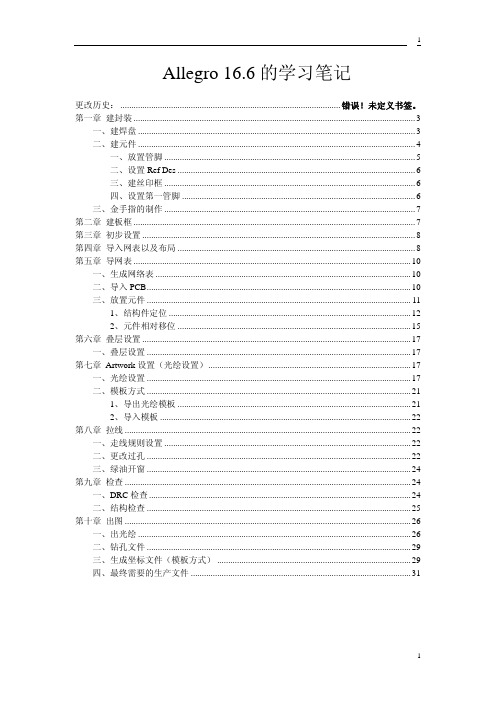

第一章 封装

一、建 焊盘

打开建立焊盘的软件 Pad Designer 路径:

, 进入下图所示,设定相关参数:

包括采用的制式,现在选公制单位毫米,精度 3,右侧问是否需要多重钻孔,这个 功能一般是用于做非圆孔。一般圆孔不用勾选。 下面设定钻孔样式,一般是圆孔,钻孔内部是否镀铜 plated(no plated 即为不镀铜,一 般用于塑胶件定位孔),再是钻孔直径,设置精度,是否偏移等。 如果是表贴元件,钻孔直径设为 0。

1

Allegro 16.6 的学习笔记

更改历史: .................................................................................................... 错误!未定义书签。 第一章 建封装 ................................................................................................................................ 3

高速PCB设计软件allegro16.6版本约束管理界面讲解

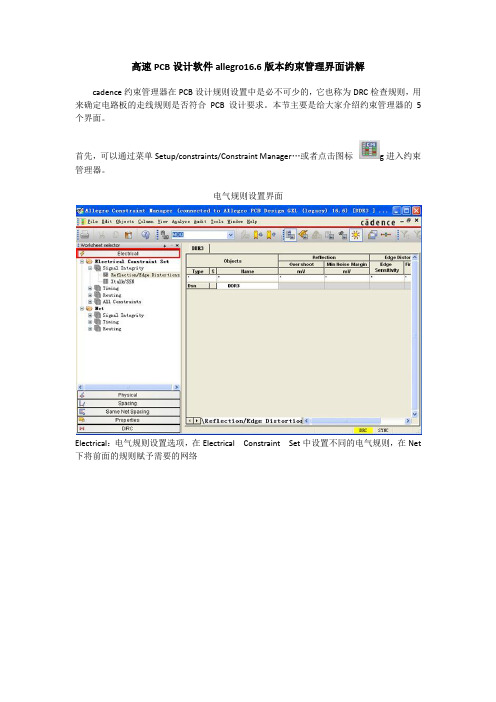

高速PCB设计软件allegro16.6版本约束管理界面讲解cadence约束管理器在PCB设计规则设置中是必不可少的,它也称为DRC检查规则,用来确定电路板的走线规则是否符合PCB设计要求。

本节主要是给大家介绍约束管理器的5个界面。

首先,可以通过菜单Setup/constraints/Constraint Manager…或者点击图标g进入约束管理器。

电气规则设置界面Electrical:电气规则设置选项,在Electrical Constraint Set中设置不同的电气规则,在Net 下将前面的规则赋予需要的网络物理规则设置界面Physical:物理规则设置选项,在Physical Constraint Set中设置不同的物理规则,在net 下将前面的规则赋予需要的网络;其中Region 是区域规则,主要针对BGA、引脚间距小、出线密度高的器件,需绘制一个区域框并赋予区域规则,区域内线宽和间距都可能小于区域外,物理规则下能够赋予物理规则。

间距规则设置界面Spacing:间距规则设置选项,在Spacing Constraint Set中设置不同的物理规则,在net 下将前面的规则赋予需要的网络,Net Class-Class是设置网络类之间的间距,补充网络间距之间的不足。

Region中可以赋予区域间距规则。

同名网络间距规则设置界面Same Net Spacing:同名网络间距设置选项,即一个网络本身之间的间距,主要是在需要绕线时运用。

属性设置界面DRC界面DRC:DRC错位查看选项,能够查看不同规则下错误的数量和位置,以及和错误相关的规则约束条件。

对高速PCB设计软件cadence16.6版本约束管理器界面进行介绍完毕后,下期继续为大家介绍与网络有关的约束与规则的讲解。

Allegro约束规则设置

Allegro约束规则设置约束规则的设置孙海峰在PCB设计中规则设置是必不可少的,它也可以被称为DRC检查规则,用来确定电路板的走线规则是否符合设计要求。

在Allegro PCB的电路板设计过程中,设计约束规则主要包括时序规则、走线规则、间距规则、信号完整性规则等以及物理规则等设置。

首先,需要认识一下,Allegro PCB的约束管理器:在PCB设计界面中,执行Setup/Constraints/Constraint Manager命令,弹出Allegro Constraint Manager对话框,如下图。

在约束管理器中,设计者可以对电路板的电气规则、物理规则、间距规则等设计规则进行设置定义。

约束规则可以按板层、网络或者区域进行设置。

约束管理器是Cadence系统提供的专用规则设置系统,主要有菜单栏、工具栏、工作表选择区、工作状态报告栏四部分,在工作表中选择一个对象,然后右击,在弹出的命令菜单中,可以进行任意操作。

工作表选择区内可以选择电气规则、物理规则、间距规则等规则设置。

在对应Net文件夹内,可以创建指定网络的对象分组,如:系统、设计、总线、差分对、扩展网络(XNet)、网络、相对或匹配群组,也可以创建基于相关属性的电气规则(ECSet)、物理规则(PCSet)、间距规则(SCSet)等。

约束管理器的约束对象分为引脚对、总线和匹配群组,她们相互之间存在优先级差异,即底层对象会集成顶层对象指定约束,为底层对象指定的约束优先高于上层继承的约束,对象层次的优先级为系统、设计、总线、差分对、扩展网络、相对或匹配群组、引脚对。

一、电气规则设置在约束管理器中,选择Electrical选项卡,其中可以为设计或网络来设置时序规则、信号完整性规则、布线的电气规则(延时、差分对)等,执行Objects/Create/Electrical CSet命令可新建电气规则。

1、选择信号完整性仿真规则Signal Integrity属性,其中包括电气属性、反射属性、单调失真属性、初始串扰、仿真串扰以及同步开关噪声这六个规则设置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

前言:本文主要讲解Allegro16.6约束管理器的使用,从基本约束规则到高级约束规则的设置。

目录:一、基本约束规则设置 1、线间距设置2、线宽设置3、设置过孔4、区域约束规则设置5、设置阻抗6、设置走线的长度范围置详解(图文并茂)则设约束规.616o r g Alle (为了不侵犯别人的成果,所以在这里做了特殊说明,以示敬意)首先感谢詹书庭编写这篇文章,为我们学习交流Cadence allegro 苦用心!俗话说的好,社会在发展,技术在进步,技术的进步在于不断的学习交流和实践。

所以为了方便大家学习交流,为大家提供一个良好 QQ )!学习交流 Cadence allegro 请加QQ 群:一起来学AllegRo 【2】.群号:331730476 .以下是正文这篇文章写得很好,操作步骤详细,截图一目了然,通俗易懂,唯一的缺点就是部分截图不是很清晰,我对个别图片做了调整和替换,不易替换的不清晰图片,仔细看下也能明白其中的意思。

此文章由丹心静居整理---2014.10.13 加入。

对原文作者表示歉意的交流平台,在这里留下我们的群原文作者的群拒绝任何人(QQ 软件提供了丰富的知识和方法。

请大家认真学习,不要辜负作者的良2014-10-13 第 1 页,共 83 页二、高级约束规则设置11、单个网络长度约束12、a+b 类长度约束 13、a+b-c 类长度约束14、a+b-c 在最大和最小传播延迟中的应用y a l e D n i P 、10约束分差设置、.29分对差创建、.19设置则分规差、 9属性用置通设、 8等长型T 、.37等长NET X 阻的过电、.27等长NET 阻的电不过、.17置等长设、 71、线间距设置(1)、设置默认间距规则点击CM图标,如下图所示,打开约束管理器。

单击Spacing,再点击All Layers,如下图所示。

右边有一个DEFAULT就是默认规则,我们可以修改其值。

入一个值,这样就都修改了,如下图所示点选Default按鼠标右键,执行Create-Spacing CSet加入新规则。

取一个有意义点的名字,如下图所示,单击OK。

其值是从默认规则拷贝的,先修改其值。

按住Shift键选中所有,输入12,回车。

然后为所需要设置的网络分配规则单击左边的Net-All Layers,在右边工作簿中,为GND网络设置12MIL_SPACE规则,在Referenced Spacing CSet下选中12MIL_SPACE,如下图所示(3)、设置Class-Class规则若针对不同的信号群组有不同的间距规则,则需要设置Class-Class选到Net Class-Class后,在右边CLOCK(2)上右键选择Ctreat-Class-Class...,如下图所示选择2个不同的Net Classes,如下图所示,单击OK如下图所示。

在右边的Referenced Spacing CSet栏可以修改其值。

执行Analyze-Analysis Modes...,如下图所示可以看到Spacing Mode的检查模式2、线宽设置(1)、设置默认约束点选Physical Constraint Set即可出现Default的Physical相关设定值,如Line Width、Neck width..等(2)、设置特殊物理规则点选Default按鼠标右键,执行Create Physical CSet加入新规则修改其值,如下图所示然后在分配网络,左边点击Net-All Layers,右边为所需设置的网络分配规则,如下图所示3、设置过孔物理规则设置里面有一栏是Vias,点击即可设置,如下图所示点击默认规则的Vias,如下图所示Remove可以移除过孔。

在左边的过孔列表中双击即可添加过孔。

同理,可设置其他物理规则的过孔,如下图所示。

4、区域约束规则设置在物理规则下,左边点击Region,在右边cds_2右键并选择Create-Region...,如下图所示输入其约束值。

然后执行Shape> Polygon/Rectangular/Circular设定范围,一般BGA比较常用。

类选择为Constraint Region,子类为All。

Assign to Region分配的区域设置为刚才创建的RGN1.5、设置阻抗(1)、通过Edit Property方式设置语法说明:IMPEDANCE_RULE=A:B:C:DA:起点PINB:终点PINC:阻抗的数值大小D:阻抗的误差大小例如:(1).IMPEDANCE_RULE=ALL:ALL:50ohm:10ohm设定走线的阻抗是50ohm,误差值是正负10ohm (2).IMPEDANCE_RULE=U1.1:R1.1:50ohm:20%设定走线在U1.1到R1.1之间的阻抗是50ohm,误差是正负20%执行Edit/Properties,点击一个网络,假设点击D0网络在过滤器里面输入im*,点击Apply输入数值all:all:60:5,单击Apply,如下图所示单击OK,结束命令。

然后打开检查模式,在Setup-Constraints-Modes... 如下图所示在弹出的窗口中,将电气模式下的阻抗检查打开,如下图所示违反规则,就会出现一个DRC,如下图所示(2)、在约束管理器中设置在约束管理器中,点选Impedance,如下图所示在cds_2上,右键Create-Electrical CSet,如下图所示输入名称60ohm单击OK,回到工作簿,设置其值,如下图所示然后为所需要设置的网络分配规则,如下图所示然后再打开检查模式,如下图所示6、设置走线的长度范围语法说明:PROPAGATION_DELAY=A:B:C:DA:起点PINB:终点PIN如果是整条NET只有2个PIN时,在A处写入L,在B处写入SC:最小线长D:最大线长例如:PROPAGATION_DELAY=U1.4:U2.8:1000mil:1500mil设定U1.4到U2.8的走线长度为1000MIL到1500MIL之间PROPAGATION_DELAY=L:S:1000mil:1500mil设定整条NET的走线长度为1000MIL到1500MIL之间(1)、通过Edit Property设置执行Edit /Porperties命令,单击一个网络,选择PROGATION_DELAY并输入其数值,如下图所示。

然后再开启检查模式,Setup-Constraints-Modes...(2)、在约束管理器中设置在Electrical Constraint Set 点选Min/Max Propagation Delays在cds_2上右键选择Create-Electrical CSet设定其值为网络分配约束,如下图所示再打开检查模式,Analyze-Analysis Modes...将电气规则下的,Propagation delay检查模式打开。

走线模式时,即可辅助线束走线状态。

(3)、在原理图中设置进入Capture中的Property Edit,选Cadence-Allegro及Flat Net执行Edit/Invoke UI对PROPAGATION_DELAY设定其值输出Netlist到Allegro。

进入Allegro后即可看到Properties再开启检查模式。

走线模式时,即可辅助显示走线状态7、设置等长语法说明:RELATIVE_PROPAGATION_DELAY=A:B:C:D:E:FA:组名。

不用和BUS_NAME 名相同,在设定MATCH_GROUP 时注意这一点。

B:是GLOBAL,在B位写入G 即可C:起点PIND:终点PIN如果NET只有2个PIN时,C处写L,D处写S。

E:写入要比参照线(Target)长或短的数值F:长度的误差(也可以用百分比表示)7.1、不过电阻的NET等长打开约束管理器,选择一组NET,右键创建MATCH_GROUP,如下图所示。

然后设定其值然后设置一个网络为目标网络,在网络Delta :Tolerance 栏处右键选择Set as target,如下图所示再打开检查模式。

如下图所示7.2、过电阻的XNET等长这里关键是设置XNET。

假设有一排过电阻的线需要等长。

首先创建电阻模型。

单击Signal Model图标,如下图所示点击电阻,如下图所示,单击RN0603 10所有这种模型的电阻都高亮了,如下图所示单击Create Model。

按钮。

默认,单击OK默认单击OK。

如下图所示。

再单击OK结束命令。

假设我们要将DR_MD49到DR_MD53网络等长。

打开约束管理器,选择相对延迟,这里可以看到我们刚才设置的XNET。

我们在DR_MD49网络上右键创建PIN PAIR选择2个端点,如上图所示,单击OK。

同理,其他需要设置等长的网络,也创建PIN PAIR。

然后按住Ctrl键选择这些PIN PAIR,右键创建MATCH GROUP 如下图所示设定约束值,及目标网络,方法同不过电阻网络等长设置。

7.3、T型等长这里为节约时间,直接引用现成的文档,基于15.7版本。

16.6设置方法类似。

T型等长设置,比如两个DDR之间的等长就属于T型等长,设置方法如下(以text_drr举例)。

首先添加T型连接点。

点击Logic-Net Schedule,单击你要设置网络的一个pin。

如下图。

在中间右键Insert T,加入T型连接点,如下图所示然后去点击第二个pin,再回到T型连接点,然后去点击第三个pin,右键done即可。

创建的T型连接点如下图所示这只是创建了一个网络的T型连接点,如果需要创建多个,可点击进入约束管理器设置。

在Net-Routing——Wiring下面,刚才设置的网络拓扑便会显示成UserDefined。

如下图所示选中那个网络,右键创建Creat-Electrical CSet,如下图然后将你需要设置T型结构的网络选择刚才设置的ECSet作为参考,Verify Schedule选择yes即打开验证,如下图所示。

然后打开检查模式,在约束管理器Analyze-Analysis Modes弹出的对话框中,将Stub length/Net的检查模式选择为on 如下如所示。

然后选中你设置的网络右键Analyze,看看是否通过,为绿色pass即可,如下图所示。

再回到p cb,打开飞线,看看是否都有了T型连接点,如下图所示。

然后在回到约束管理器,将刚才设置的T型结构的网络选中,右键Creat-Bus,如下图所示。

选中所创建的Bus,右键SigXplorer,如下图所示这里可以看到刚才设置的拓扑结构,单击Set菜单下Constraints子菜单,如下图所示,选择Rel Prop Delay面板创建两个约束,注意这里设置的是从T1到U2和T1到U3,即U2和U3之间T型等长,约束名称是一样的,范围Scope 选择Local,如下图所示设置好之后,单击Update Cm图标更新回约束管理器,如下图所示。