ADC_DAC

了解声卡的常见技术DAC和ADC

了解声卡的常见技术DAC和ADC 声卡是计算机中用于输入和输出音频信号的重要硬件设备,它能够将模拟音频信号转换为数字信号以便计算机处理,同时也能将数字信号转换为模拟信号以供外部设备播放。

在声卡中,常见的两项关键技术是数字模拟转换(DAC)和模数转换(ADC)。

一、数字模拟转换(DAC)数字模拟转换(Digital-to-Analog Converter,DAC)是声卡中的重要技术之一,主要用于将计算机内部生成的数字音频信号转换为模拟信号,以便输出到扬声器或其他音频设备上。

DAC技术的核心是将数字信号转换为模拟信号。

它通过将数字音频信号转换为一系列离散的模拟信号样本,再通过模拟滤波和放大等过程,还原出与原始音频信号相似的模拟音频信号。

在声卡中,DAC技术起到了至关重要的作用。

优质的DAC能够带来更高的音频还原度和更低的噪声水平,从而实现更好的音频质量。

DAC的技术参数包括采样率、位深度和信噪比等。

采样率是指每秒钟采集的样本数量,常见的采样率有44.1kHz和48kHz等。

位深度表示每个样本的精度,位深度越高,音频还原度越高。

信噪比则反映了DAC的输出信号与噪声的比值,信噪比越高,输出音频的清晰度越好。

二、模数转换(ADC)模数转换(Analog-to-Digital Converter,ADC)是声卡中另一个重要的技术,用于将模拟音频信号转换为数字信号,以便计算机进行处理和存储。

ADC技术的核心是将连续的模拟音频信号转换为一系列离散的数字音频样本,再通过量化和编码等过程,将连续的信号转化为离散的数字信号。

在声卡中,ADC技术的好坏直接影响着音频输入的质量。

高质量的ADC能够提供更高的采样率和更高的位深度,从而更准确地捕捉音频细节,保留音频的原始质量。

与DAC类似,ADC的技术参数也包括采样率和位深度。

采样率表示ADC每秒进行模拟信号采样的次数,常见的采样率有44.1kHz和48kHz等。

位深度则表示每个样本的精度,位深度越高,表示每个样本可以存储的信息越多,音频质量也会相应提高。

常用的ADC和DAC

常用ADC/DAC器件介绍ADC系列:1. ADS5483ADS5483 ADC 拥有高信噪比(SNR) 与无杂散动态范围(SFDR),可通过第二尼奎斯特区(Nyquist zone) 接收来自DC 的输入频率。

采样速率为135 MSPS 的ADC 在输入频率(IF) 为70 MHz 时可实现78.6 dBFS 的SNR 以及95 dBc 的SFDR,与同类ADC 相比,SNR 高出3.5 dB,SFDR 高出8 dB。

更高性能ADS 5483 能够显著增强设计灵活性,进而使众多应用受益匪浅。

例如,其不仅可针对测量测试系统提供更高的准确度,而且还能凭借更高带宽在包括空中接口等在内的无线通信领域提供更高的灵敏度,如WCDMA、TD-SCDMA、WiMAX、LTE以及多载波3 GSM 等。

2. ADS795x该系列器件不仅可针对高密度应用实现优异的线性与AC 性能,而且优化后还能最大限度地提升诸如手持式医疗仪器、可编程逻辑控制器以及数字电源等电池供电及低电压应用的性能。

ADS795x 产品系列高度集成了众多组件,如GPIO、可编程告警阈值、板上定序器以及SPI 兼容接口等,能最大限度地降低板级空间要求,并简化与主机设备的连接及相关软件。

3. AS1538AS1538带有8个12Bit的分辨率的输入通道。

其在50ksps的转换速度下低于850μA(包括内部基准)消耗电流。

在关断模式下,AS1538的供电电流可降至1.5μA以下。

无论是2.5V的内部基准还是1V至5.25V范围内的外部基准,都能对满刻度模拟输入范围进行设定。

AS1538的I2C兼容接口支持速度高达3.4MHz的接口,包括100kHz 和400kHz的行业标准速度。

用户可编程I2C地址可以在一条I2C总线上挂多达4种设备。

4. LTC2262LTC2262 用1.8V 的低压模拟电源工作,极大地节省了功率,而且不牺牲AC 性能。

这个ADC 在基带提供了72.8dB 的信噪比(SNR) 性能和88dB 的无寄生动态范围(SFDR)。

ADC与DAC电路设计精要

ADC与DAC电路设计精要模拟-数字转换器(ADC)和数字-模拟转换器(DAC)是数字电子系统中常见的关键组件,它们负责将模拟信号转换为数字信号或者将数字信号转换为模拟信号。

在设计ADC和DAC电路时,需要考虑到很多因素,包括精度、速度、功耗、成本等等。

本文将重点介绍ADC与DAC电路设计的关键要点。

首先,ADC电路设计的关键要点之一是分辨率。

分辨率是ADC能够区分的电压值范围的大小,通常以比特为单位表示,比如8位、10位、12位等。

分辨率越高,ADC能够提供的精度就越高。

在选择ADC器件时,需要根据具体的应用需求来确定所需的分辨率,同时还要考虑到采样率和动态范围等因素。

另外,ADC电路设计中还需要考虑信噪比(SNR)和失真。

信噪比是指ADC输出信号与输入信号的比值,表示了ADC在信号转换过程中添加的噪声水平。

失真是指ADC输出信号与输入信号之间的差异,包括非线性失真和量化噪声等。

为了提高ADC的性能,需要尽可能降低噪声水平和失真水平,同时选择合适的滤波器来滤除干扰信号。

对于DAC电路设计而言,精度和线性度是关键要点之一。

DAC的精度指的是输出信号与输入信号之间的误差程度,而线性度表示DAC输出信号与输入信号之间的线性关系。

高精度和高线性度能够保证DAC输出信号与输入信号的一致性,提高系统的性能。

在选择DAC器件时,需要考虑到分辨率、更新速率、功耗等因素,并根据具体的应用需求来确定合适的DAC类型。

此外,DAC电路设计还需要关注输出阻抗和加载效应。

输出阻抗是指DAC输出端的内部电阻,影响着DAC输出信号的稳定性和准确性。

加载效应是指DAC输出端连接的负载电路对DAC输出信号造成的影响。

在设计DAC电路时,需要选择合适的输出缓冲器和负载电路,以确保DAC输出信号能够被准确地传输到下游电路中。

总而言之,ADC与DAC电路设计涉及到很多关键要点,包括分辨率、信噪比、失真、精度、线性度、输出阻抗等等。

在设计ADC与DAC电路时,需要根据具体的应用需求来选择合适的器件和设计方案,以确保电路性能达到预期的要求。

ADC_DAC基础知识4

ADC和DAC基础—第四部分这是本系列5篇文章中的第四篇,介绍抖动、延迟和其它ADC中的误差。

作者:Walt Kester和James Bryant, Analog Devices公司无杂波动态范围(SFDR)在通信应用中或许最重要的指标就是它的无杂波动态范围。

SFDR指标对于ADC来说,就像对混频器和LNA的三阶交调截取点指标。

ADC的SFDR被定义为RMS信号幅度对峰值杂波频谱成分的RMS数值之比(在直流到fs/2的整个第一奈奎斯特区测得)。

SFDR一般被描绘为信号幅度的函数,并可能像图2-28所示那样,被描绘为相对于信号幅度(dBc)或ADC的满量程(dBFS)。

图2-28:无杂波动态范围(SFDR)。

对于接近满量程的信号,峰值频谱杂波一般由基波的头几个谐波之一决定。

然而,当信号落在小于满量程若干dB时,其它出现的杂波一般不是输入信号的直接谐波。

这是因为存在前面讨论过的ADC传输函数的差分非线性的缘故。

因此,SFDR要考虑所有源的失真,而不论它们来自何处。

AD9042是一种面向通信应用的12比特、41 MSPS宽带ADC,在此,高SFDR时至关重要的。

对于19.5 MHz的输入和41 MSPS采样频率,SFDR如图2-29所示。

注意:在整个第一奈奎斯特区获得了80 dBc的最小SFDR(直流到20MHz)。

绘图还显示SFDR被表示为dBFS。

SFDR一般比ADC的理论N比特SNR(6.02 N + 1.76 dB)要大的多。

例如,AD9042是具有80 dBc SFDR和65 dBc典型SNR(理论SNR为74 dB)的12比特ADC。

这是因为噪声。

向ADC 增加额外的分辨率可能要增加起SNR ,但是,可能会或可能不会增加它的SFDR 。

和失真测量之间存在根本的区别。

FFT 的处理增益(对于4096点 FFT 为33 dB)让频率杂波远远小于被观察的噪声基底图2-29: 12比特41 MSPS ADC —AD9042—的SFDR 与输入功率电平的关系。

ADC_DAC基础知识

– 数据转换中常用的码的类型

图1.8 二进制, 温度计码及1/n 码

• D/A 转换器的性能指标

• • • • • 微分非线性(NDL) 积分非线性(INL) 失调(offset) 增益误差(gain error) 信号与噪声加失真的比(SNDR) (signal-to-(noise+distortion)ratio)

π

V cos sin −1 = A

A2 − V 2 A

可得到:

)2 ) 2 Vb − (2Va cos(πp (Va , Vb )))Vb − A2 1 − cos 2 (πp (Va , Vb )) + Va = 0

(

)

设第i个转换码对应的发生频次为H(i) ,且:

Nt =

2 n −1 j =0

0.1

0.2 fin/fs

0.3

0.4

0.5

Vp-p = 0.9Vfs

SNDR=64.1dB ENOB = 10.36 bit

测试系统设计

function generator LPF single-todifferential DC bias

clock

reference voltages

ADC Prototype

图1.5 静态ADC指标

动态指标: • 信噪比(SNR)

是输出端信号功率与总的噪声功率的比 (通常采用正弦输入来测量)

• 信号与噪声加失真的比(SNDR)

是当输入为正弦时, 输出端信号功率与总噪声及谐波 功率的比.

• 有效位数(ENOB)

定义为:

ENOB =

SNDRp − 1.76 6.02

(8)

Logic Analyzer

从模拟到数字:ADC与DAC的工作原理

从模拟到数字:ADC与DAC的工作原理步骤详细并分点列出:一、引言- 介绍ADC(模拟到数字转换器)和DAC(数字到模拟转换器)的基本概念。

- 引出本文的目的是讨论它们的工作原理。

二、ADC的工作原理1. 模拟信号的采样- 解释模拟信号是连续变化的电信号。

- 介绍采样的概念,并列举示波器为例来说明采样的过程。

2. 量化- 解释量化的概念,即将采样信号离散化。

- 介绍量化位数对信号精度的影响。

- 引入比特率的概念,即ADC每秒可以处理的位数。

3. 编码- 解释编码的概念,将量化的数字转换为二进制码。

- 介绍常见的编码方式,如二进制编码和格雷码。

4. 抽样速率- 解释抽样速率的概念,即采样的频率。

- 介绍奈奎斯特抽样定理,即抽样频率必须大于等于信号最高频率的两倍。

5. 整体工作原理- 将以上各个环节连接起来,解释ADC是如何将模拟信号转换为数字信号的。

三、DAC的工作原理1. 数字信号的解码- 解释数字信号的离散性和二进制编码的含义。

- 介绍解码的概念,将二进制码转换为量化的数字。

2. 量化解码- 解释量化解码的概念,将数字信号转换为模拟信号。

- 介绍量化位数和解码精度的关系。

3. 数字信号的重构- 解释数字信号的离散性和抽样频率的含义。

- 介绍重构的概念,将抽样后的数字信号转换为连续变化的模拟信号。

4. 滤波- 解释滤波的概念,去除数字信号中的高频噪声。

- 介绍数字滤波器的作用和常见类型。

5. 整体工作原理- 将以上各个环节连接起来,解释DAC是如何将数字信号转换为模拟信号的。

四、总结- 归纳ADC和DAC的工作原理,强调它们在数字信号处理中的重要性。

- 提醒读者对这些原理有更深入的了解,以应用到实际的电子产品中。

以上只是一份写作范文的建议,您可以根据自己的需求和要求来调整和修改。

ADC_DAC基础知识3

ADC和DAC基础—第三部分这是5部分系列文章中的第三部分,介绍实际ADC中的失真和噪声。

作者:Walt Kester和James Bryant, Analog Devices在实际ADC中的失真和噪声不论采用什么架构,实际的采样ADC(具有集成的采样和保持)都具有许多噪声和失真源,如图2-20所示。

宽带模拟前端缓冲器具有宽的噪声、非线性及有限的带宽。

SHA进一步引入了非线性、带限和孔径抖动(aperture jitter)。

ADC实际量化器部分引入量化噪声以及积分和差分非线性。

在本文的讨论中,假设ADC的连续输出被载入长度为M的缓冲存储器,并且FFT处理器提供谱输出。

此外,假设FFT算法运算本身没有引入相对于ADC的重大误差。

然而,当考察输出噪声基底时,必须考虑FFT处理增益(取决于M)。

图2-20:显示噪声和失真源的ADC模型。

等效输入涉及的噪声(热噪声)因热和kT/C效应,宽带ADC内部电路引入一定量的宽带RMS噪声。

这种噪声甚至呈现在直流输入信号上,如图2-21所示,以直流输入的标称数值为中心,实际上大多数宽带(或高分辨率)ADC的输出是一种代码的分布。

为了测量其数值,ADC的输入被接地,并且大量的输出采样被收集并以柱状图被打印出来(有时指的是接地输入的柱状图)。

因为噪声接近高斯噪声,柱状图的标准偏差可以方便地计算出来,对应于有效的输入RMS噪声。

以LSB表示这种RMS噪声是常见的实践,虽然它可以表示为RMS电压。

可以采取不同的方式提取ADC交流性能的特征。

在ADC技术的早期(30多年以前),就交流指标而言,很少有标准化,并且人们也没有很好地掌握测量设备和技术,或者没有测量设备和技术可用。

经过30多年的发展,制造商和客户已经学会了测量转换器的动态性能,如图2-22所示的指标表示了目前所采用的最流行的指标。

实际上,所有的指标都是在频域表示转换器的性能。

FFT实际上是所有的测量的核心并将在本书的第五部分详细讨论。

什么是ADC和DAC

O(t)=0。

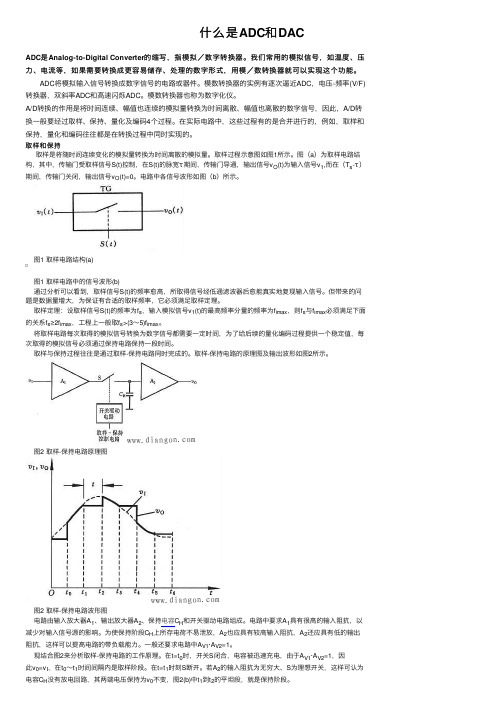

电路中各信号波形如图(图1 取样电路结构(a)取样与保持过程往往是通过取样-保持电路同时完成的。

取样图2 取样-保持电路原理图图2 取样-保持电路波形图电路由输⼊放⼤器A1、输出放⼤器A2、保持电容C H和开关驱动电路组成。

电路中要求取样-保持电路以由多种型号的单⽚集成电路产品。

如双极型⼯艺的有AD585、AD684;混合型⼯艺的有AD1154、SHC76等。

量化与编码数字信号不仅在时间上是离散的,⽽且在幅值上也是不连续的。

任何⼀个数字量的⼤⼩只能是某个规定的最⼩数量单位的整数倍。

为将模拟信号转换为数字量,在A/D转换过程中,还必须将取样-保持电路的输出电压,按某种近似⽅式归化到相应的离散电平上,这⼀转化过程称为数值量化,简称量化。

量化后的数值最后还需通过编码过程⽤⼀个代码表⽰出来。

经编码后得到的代码就是A/D转换器输出的数字量。

量化过程中所取最⼩数量单位称为量化单位,⽤△表⽰。

它是数字信号最低位为1时所对应的模拟量,即1LSB。

在量化过程中,由于取样电压不⼀定能被△整除,所以量化前后不可避免地存在误差,此误差称之为量化误差,⽤ε表⽰。

量化误差属原理误差,它是⽆法消除的。

A/D 转换器的位数越多,各离散电平之间的差值越⼩,量化误差越⼩。

量化过程常采⽤两种近似量化⽅式:只舍不⼊量化⽅式和四舍五⼊的量化⽅式。

1.只舍不⼊量化⽅式以3位A/D转换器为例,设输⼊信号v1的变化范围为0~8V,采⽤只舍不⼊量化⽅式时,取△=1V,量化中不⾜量化单位部分舍弃,如数值在0~1V之间的模拟电压都当作0△,⽤⼆进制数000表⽰,⽽数值在1~2V之间的模拟电压都当作1△,⽤⼆进制数001表⽰……这种量化⽅式的最⼤误差为△。

2.四舍五⼊量化⽅式 如采⽤四舍五⼊量化⽅式,则取量化单位△=8V/15,量化过程将不⾜半个量化单位部分舍弃,对于等于或⼤于半个量化单位部分按⼀个量化单位处理。

它将数值在0~8V/15之间的模拟电压都当作0△对待,⽤⼆进制000表⽰,⽽数值在8V/15~24V/15之间的模拟电压均当作1△,⽤⼆进制数001表⽰等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DAC(Digital to Analog Converter)

• ADC的逆过程

• 如:数字量1010 0111在5v单片机中代表的是多少 呢?

• 5 -> • 2.5+1.25+0.625+0.3725+0.18625+0.093125+0.04656 25+0.02328125 • 对应的1010 0111 • 2.5+0.625+0.093125+0.0465625+0.02328125 • =3.2879

AD/DA Converter

by 77695

What is AD/DA?

• 日常生活中——模拟量(什么是模拟量)

• 单片机中——数字量(什么是数字量) • 两者如何转换???

ADC(Analog to Digital Converter)

• 模拟量->数字量

• 如:5v单片机中3.5v怎么表示?

• 对应的模拟量就是: • 3.2879v

DeviceБайду номын сангаас

• ADC0804

PINs

• D0-D7:数字量输出端,输出结果为八位二进制结 果; • CLK:为芯片工作提供工作脉冲,时钟电路如图所 示,时钟频率计算方式是: • fCK=1/(1.1×R×C) • CS:片选信号; • WR:写信号输入端; • RD:读信号输入端; • INTR:转换完毕中断提供端;

Nowadays

• ADC0832

• /view/545294c758f5f61fb7 3666bd.html

Homework

• 数显电压表: • 要求:通过数码管显示可调电阻分压得到的电压 值

• 呼吸灯: • 以3s为周期,逐渐变亮变暗的LED灯。