8.1计算机组成之.8259A详细说明

8259A中断控制器

CAS0 CAS1 CAS3

级 联 缓 冲 比较器

内 部 总 线

中 断 服 务 寄 存 器

ISR

优 先 权 处 理 器

中 断 请 求 寄 存 器

IRR

IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7

SP / EN

中断屏蔽寄存器 IMR

IRR,IMR

1.中断请求寄存器IRR

IRi(i=07)上有中断请求时,IRR相应位置1。

AEOI=1自动中断结束方式AEOI=0:非自动中断结束(EOI) µ PM=1:86系列CPU; µ PM=0:非86系列CPU 。

普通全嵌套方式

普通全嵌套方式也叫固定优先权方式。 优先权从IR0到IR7依次递降。 级别高的中断请求可以中断级别低的中断服 务子程序。 一中断被响应的过程中,自动屏蔽同级和更 低级别的中断。

8259A在PC机中的I/O端口地址

PC机中相当有两片8259A级联,一个主片,一个从片。

ICW1 ICW2 ICW3 ICW4 OCW1 OCW2 OCW3

主片 0x20 从片 0xa0

0x21 0xa1

0x21 0xa1

0x21 0xa1

0x21 0xa1

0x20 0xa0

0x20 0xa0

主片初始化程序

0

X

ESMM SMM 0

1

P

RR

RIS

A0=0 , D4=0 , D3=1 是OCW3的特征。 ESMM=1,SMM=0: 设置特殊屏蔽

ESMM=1,SMM=1: 清除特殊屏蔽

P=1:发查询命令 ; P=0:不发查询命令 RR=1,RIS=0: 读IRR寄存器 RR=1,RIS=1: 读ISR寄存器

计算机接口与微机原理-第12周-中断控制器8259A-c

计算机接⼝与微机原理-第12周-中断控制器8259A-c可编程中断控制器8259Ap IBM PC/XT的中断指令p DOS系统功能调⽤p BIOS中断类型p8259A的中断级联p IBM PC/AT的中断级联p8259A的应⽤举例p8259A的编程⽅法中⼭⼤学信息科学与技术学院陈任IBM PC/XT中的中断指令(1) 8086/8088系统中与中断有关的专⽤指令。

1.INT n 软件中断指令(Interrupt)-软件中断指令,也称为软中断指令,其中n为中断类型号,其值必须在0~255的范围内。

-可在编程时安排在程序中的任何位置上,因此也被称为陷阱中断。

-CPU执⾏INT n指令时,先把标志寄存器的内容推⼊堆栈,再把当前断点的段基地址CS和偏移地址IP⼊栈保护,并清除中断标志IF和单步标志TF。

-然后将中断类型号n乘以4,找到中断服务程序的⼊⼝地址表的表头地址,从中断⽮量表中获得中断服务程序的⼊⼝地址,将其置⼊CS和IP寄存器,CPU就⾃动转到相应的中断服务程序去执⾏。

-原则上讲,利⽤INT n指令能以软件的⽅法调⽤所有256个中断的服务程序,尽管其中有些中断实际上是由硬件触发的。

因此可以利⽤这条指令来调试各种中断服务程序。

-例如,可⽤INT 0指令让CPU执⾏除法出错中断服务程序,可⽤INT 2指令执⾏NMI中断服务程序,⽽不必在NMI引脚上加外部信号。

IBM PC/XT中的中断指令(2)1. INT n 软件中断指令(Interrupt)2. INTO 溢出中断指令(Interrupt On Overflow)-当带符号数进⾏算术运算时,如果溢出标志OF置1,则可由溢出中断指令INTO产⽣类型为4的中断,若OF清零,则INTO指令不产⽣中断,CPU继续执⾏后续程序。

-在带符号数进⾏加减法运算之后,必须安排⼀条INTO指令,⼀旦溢出就能及时向CPU提出中断请求,CPU响应后可作出相应的处理,如显⽰出错信息,使运算结果⽆效等。

8259A中断实验

实验8259单级中断控制器实验一、实验目的⒈掌握8259中断控制器的接口方法。

⒉掌握8259中断控制器的应用编程。

二、实验内容利用8259实现对外部中断的响应和处理,要求程序对每次中断进行计数,并将计数结果送数码显示。

三、实验接线图图6-6四、编程指南⑴8259芯片介绍中断控制器8259A是专为控制优先级中断而设计的芯片。

它将中断源优先级排队、辨别中断源以及提供中断矢量的电路集于一片中。

因此无需附加任何电路,只需对8259A进行编程,就可以管理8级中断,并选择优先模式和中断请求方式。

即中断结构可以由用户编程来设定。

同时,在不需要增加其它电路的情况下,通过多片8259A的级联,能构成多达64级的矢量中断系统。

⑵本实验中使用3号中断源IR3,“”插孔和IR3相连,中断方式为边沿触发方式,每拨二次AN开关产生一次中断,满5次中断,显示“8259——good”。

如果中断源电平信号不符合规定要求,则自动转到7号中断,显示“Err”。

五、实验程序框图IR3中断服务程序:IR7中断服务程序:六、实验步骤1、按图6-6连好实验线路图。

⑴8259的INT连8088的INTR;⑵8259的INTA连8088的INTA;⑶“”插孔和8259的3号中断IR3插孔相连,“”端初始为低电平;⑷8259的CS端接FF80H孔。

2、运行实验程序,在系统处于命令提示符“P.”状态下,按SCAL键,输入12D0,按EXEC键,系统显示8259-1。

3、拨动AN开关按钮,按满l0次显示good。

七、实验程序清单CODE SEGMENT ;H8259.ASMASSUME CS: CODEINTPORT1 EQU 0FF80HINTPORT2 EQU 0FF81HINTQ3 EQU INTREEUP3INTQ7 EQU INTREEUP7PA EQU 0FF20H ;字位口PB EQU 0FF21H ;字形口PC EQU 0FF22H ;键入口ORG 12D0HSTART: JMP START0BUF DB ?,?,?,?,?,?intcnt db ?data1:db0c0h,0f9h,0a4h,0b0h,99h,92h,82h,0f8h,80h,90h,88h,83h,0c6h,0a1hdb 86h,8eh,0ffh,0ch,89h,0deh,0c7h,8ch,0f3h,0bfh,8FH START0: CLD ;递加CALL BUF1 ;写显示缓冲初值CALL WRINTVER ;写中断向量MOV AL,13H ;写ICW1MOV DX,INTPORT1OUT DX,ALMOV AL,08H ;写ICW2MOV DX,INTPORT2OUT DX,ALMOV AL,09H ;写ICW4OUT DX,ALMOV AL,0F7H ;写OCW1OUT DX,ALMOV intcnt,01H ;中断计数初值STI ;开中断WATING: CALL DISP ;DISP 8259-1JMP WATING ;循环显示WRINTVER: MOV AX,0H ;写中断向量子程序MOV ES,AXMOV DI,002CH ;IR3中断向量地址LEA AX,INTQ3 ;IR3中断服务地址STOSW ;写中断服务地址偏移量MOV AX,0000h ;写中断服务段地址STOSWMOV DI,003CH ;IR7中断向量地址LEA AX,INTQ7 ;IR7中断服务地址STOSW ;写中断服务地址偏移量MOV AX,0000h ;写中断服务段地址STOSWRETINTREEUP3: CLI ;IR3中断服务push ax ;压栈保护现场push bxpush cxpush dxMOV AL,INTCNT ;CALL CONVERS ;拆送缓冲区MOV BX,OFFSET BUF ;077BHMOV AL,10HMOV CX,05HINTRE0: MOV [BX],AL ;高五位缓冲区送熄灭码INC BXLOOP INTRE0MOV AL,20H ;中断返回码MOV DX,INTPORT1OUT DX,ALADD INTCNT,01HCMP INTCNT,06HJNA INTRE2 ;中断次数小于5次继续CALL BUF2 ;中断次数结束DISP:good INTRE1: CALL DISPJMP INTRE1CONVERS: AND AL,0FH ;拆送缓冲区MOV BX,offset buf ;077AHMOV [BX+5],ALRETINTRE2: MOV AL,20HMOV DX,INTPORT1OUT DX,ALpop dxpop cxpop bxpop axSTIIRET ;中断返回INTREEUP7: CLI ;IR7中断服务MOV AL,20H ;中断返回码MOV DX,INTPORT1OUT DX,ALcall buf3 ;disp:errINTRE3: CALL DISP ;循环显示:ERR JMP INTRE3DISP: MOV AL,0FFH ;显示子程序 ,5ms MOV DX,PAOUT DX,ALMOV CL,0DFH ;20HMOV BX,OFFSET BUFDIS1: MOV AL,[BX]MOV AH,00HPUSH BXMOV BX,OFFSET DATA1ADD BX,AXMOV AL,[BX]POP BXMOV DX,PBOUT DX,ALMOV AL,CLMOV DX,PAOUT DX,ALPUSH CXDIS2: MOV CX,00A0HLOOP $POP CXCMP CL,0FEH ;01HJZ LX1INC BXROR CL,1 ;SHR CL,1JMP DIS1LX1: MOV AL,0FFHMOV DX,PBOUT DX,ALRETBUF1: MOV BUF,08H ;写”8259-1”MOV BUF+1,02HMOV BUF+2,05HMOV BUF+3,09HMOV BUF+4,17HMOV BUF+5,01HRETBUF2: MOV BUF,09H ;写”good ”MOV BUF+1,00HMOV BUF+2,00HMOV BUF+3,0dHMOV BUF+4,10HMOV BUF+5,10HRETBUF3: MOV BUF,0eH ;写”err ”MOV BUF+1,18HMOV BUF+2,18HMOV BUF+3,10HMOV BUF+4,10HMOV BUF+5,10HRETCODE ENDSEND START。

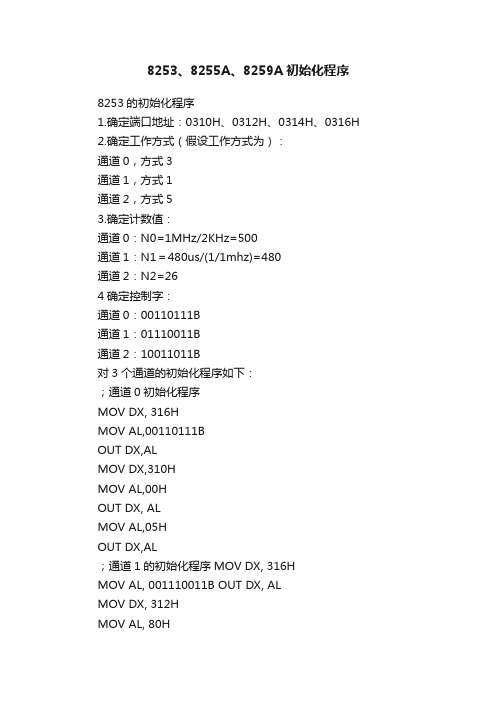

8253、8255A、8259A初始化程序

8253、8255A、8259A初始化程序8253的初始化程序1.确定端口地址:0310H、0312H、0314H、0316H2.确定工作方式(假设工作方式为):通道0,方式3通道1,方式1通道2,方式53.确定计数值:通道0:N0=1MHz/2KHz=500通道1:N1=480us/(1/1mhz)=480通道2:N2=264确定控制字:通道0:00110111B通道1:01110011B通道2:10011011B对3个通道的初始化程序如下:;通道0初始化程序MOV DX, 316HMOV AL,00110111BOUT DX,ALMOV DX,310HMOV AL,00HOUT DX, ALMOV AL,05HOUT DX,AL;通道1的初始化程序MOV DX, 316HMOV AL, 001110011B OUT DX, ALMOV DX, 312HMOV AL, 80HOUT DX, ALMOV AL, 04HOUT DX, AL;通道2初始化程序MOV DX, 316HMOV AL, 10011011B OUT DX, ALMOV DX, 314HMOV AL,26HOUT DX,AL; MOV AL,00H; OUT DX,AL8255A初始化程序对8255A进行初始化,要求端口A工作于方式1,输入;端口B 工作于方式0,输出;端口C的高4位配合端口A工作,低4位为输入。

1.确定控制字端口地址:006CH。

2.确定工作方式:端口A,工作方式1,输入端口B,工作方式0,输出端口C,C0为输入,C4为配合工作3.确定方式选择控制字:1 011 100 1H(B9H)对3个端口的初始化程序如下MOV AL,B9HMOV DX,006CHOUT DX,AL另一个8255A初始化程序已知某8255A在系统中占用88~8BH号端口地址,现欲安排其PA,PB,PC口全部为输出,PA,PB口均工作于方式0模式,并将PC6置位,使PC3复位,试编写出相应的初始化程序:1.确定端口地址控制字以及PC口置位复位端口,8BH2.确定工作方式3.确定方式选择控制字MOV AL,80HOUT 8BH,ALMOV AL,ODHOUT 8BH,ALMOV AL,06HOUT 8BH,AL在8259A内部有两组寄存器:一组为命令寄存器,用于存放CPU写入的初始化命令字ICW1~ICW4(initialization command words);另一组为操作命令寄存器,用于存放CPU写入的操作命令字OCW1~OCW3(operation command words)。

第14讲8259A编程

IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7

+5V

INT -SP/-EN

8259级联工作示意图 第八章 中断 级联工作示意图

中断级连

8259A可以级连,1个主片最多可以级连8个从片 级连时,主片的级连线CAS0~CAS2连至每个从片 的CAS0~CAS2,输出被选中的从片编号, 每个从片的中断请求信号 INT,连至主8259A的一 个中断请求输入端IRx;主片的 INT 线连至CPU的 IRx CPU 中断请求输入端INTR 在非缓冲方式下,引脚-SP/-EN,通过接地指定该 片充当从片(-SP=0);反之若接高电平则该片充 当主片(-SP=1)。

非缓冲方式

-SP/-EN引脚作为输入端 在8259A级连时,用它选择该芯片充当主片或从片

第八章 中断

23

3、8259A的编程

初始化编程

第八章 中断 5

注:纠正P360多处错误

CS A0 RD WR 0 0 0 0 0 1 0 1 0 1 × × 1 1 0 0 1 × 0 0 1 1 1 ×

功能 写入ICW1、OCW2和OCW3 写入ICW2~ICW4和OCW1 读出IRR、ISR和查询字 读出IMR 数据总线高阻状态 数据总线高阻状态

第八章 中断 16

4.特殊屏蔽方式

除了用操作命令字OCW1屏蔽掉的中断级和 正在服务的中断级外,允许其他任何级别的 中断请求中断正在服务的中断。用这种方法 可以在程序的不同阶段改变中断级的优先次 序。

第八章 中断

17

5. 查询法排序方式

该方式用查询的方法响应与8259a相连的8级 中断请求。采用该方式时,8259a的INT引脚 不用,或CPU处于关中断状态,以便使cpu 不能响应INT线上来的中断请求。这时若要选 择最高优先级,必须先用操作命令字发查询 命令,然后再用输入命令识别当前有无中断 请求及优先级最高的中断请求。

8259A介绍

(5)控制逻辑电路 控制逻辑电路根据CPU对8259A编程设定的工作方 式 管 理 8259A , 负 责 发 出 INTR 和 接 收 INTA# , 并 使 INTA#转化为内部所需的各种控制信号。 (6)读/写电路 读/写电路可接收CPU对8259A的初始化命令字ICW 和操作命令字OCW,并将其存入相应的端口寄存器, 来规定8259A的工作方式和控制模式;也可以向CPU提 供各端口寄存器的内容。 (7)数据总线缓冲器 连 接 系 统 总 线 和 8259A 的 内 部 总 线 , 用 于 传 输 8259A的控制字或状态字,以及中断类型号。 (8)级连缓冲/比较器 控制多片8259A的级连,扩展中断级。多片8259A 级连时,一片为主,其余为从。最多可9片级连,扩 展64级中断。

1.中断嵌套方式

(2)特殊全嵌套方式 和一般全嵌套方式基本相同,区别在于: 在特殊全嵌套方式下,处理某一中断时, 可实现对同级中断请求的响应。 系统中只有单片8259A时,通常用全嵌 套方式;而当8259A多片级连时,主片 必须采用特殊全嵌套方式,从片可采用 一般全嵌套方式。

一般全嵌套方式与特殊全嵌套方式的区别

8259A中断优先权的管理方式有固定优先权方式和自 动循环优先权方式两种。 (1)固定优先权方式 注: 特殊全嵌套仅用于多个8259A级连时的 在固定优先权方式中,IR7~IR0的中断优先权 主 8259A , 而 不 能 用 于 从 属 8259A 或 单 的级别是由系统确定的。 8259A系统。 它 们 由 高 到 低 的 优 先 级 顺 序 是 : IR0, IR1, IR2, …, IR7, 其中,IR0的优先级最高,IR7的优 先级最低。当有多个IRi请求时,优先权判决器(PR) 将它们与当前正在处理的中断源的优先权进行比较, 选出当前优先权最高的IRi,向CPU发出中断请求INT, 请求为其服务。

(8259A)

从ISR是 否全为0

N

Y EOI主

IRET

(3) 优先权循环方式

一个系统的优先权比较复杂,所以不能总规定IR0高 … IR7低。 8259A设计了两种改变优先权的方法。

•自动循环方式 ——适用于设备的优先权相等情况 当一个设备受到中断服务后,它的优先级自动降到最低,其相 邻的中断请求变成最高的。 例如: IR0 IR1 IR2 IR 3 IR4 IR5 IR6 IR7 初始 高 低 若IR4有中断请求,处理IR4后,IR5成为最高优先级, 优先级次序为:IR5 IR6 IR7 IR0 IR1 IR2 IR3 IR4 IR4左循环至最低优先级。

不管是普通、还是特殊的中断结束方式,级联系统中的中断结 束必须发送两次EOI: 一次给从片,一次给主片。 (向从片发EOI后,须检查从片中的所有申请中断的源是否全服务过。 只有都服务过了,才能向主8259送另一个EOI命令)。

17

中断结束字

什么是8259A的中断结束字(EOI)?

8259A的命令字.

表5.5 从片ID标志编码与主片IRi对应表 从片标志码(D2D1D0) 000 001 010 011 100 101 110 111

主片对应IRi

IR0

IR1

IR2

IR3

IR4

(2) ICW2

• ICW2的格式为下。设置中断类型号。

A0 1

D7 T7

D6 T6

D5 T5

D4 T4

D3 T3

D2 0

D1 0

D0 0

中断类型号的高5位

16位机无效

A0 1

D7

D6

D5

D4

D3

D2

D1

D0

T7

T6

T5

T4

T3

0

0

0

中断类型号的高 5 位

8259A 自动填入

• 8259A提供给CPU的中断类型号是一个8位代 码,是通过初始化命令ICW2提供的。但由于 ICW2的低3位被8位机占用,只有高5位能用, 因此在初始化编程时,通过命令字ICW2只写 入高5位,它的低3位是由中断请求线IRi的二 进制编码(如IR4的编码为100)决定,并且是在 第一个INTA# 到来时,将这个编码写入低3位 的。可见,同一片8259A上的8个中断源的中 断号的高5位都相同。 • 微机系统中断类型号的分配见表。

• 那么怎样来解决这个问题呢?8259A提供了一 种特殊的完全嵌套方式。在这个方式中,主片 仅仅是不理睬那些比在ISR中更低的优先级的 中断请求,而响应所有与ISR位相等或较高的 优先级的中断请求。 • 因此,如果在主片中采用特殊完全嵌套方式, 那么,当从片收到一个比该片服务中的那个优 先等级更高的中断请求,向主片发中断请求时, 它是会被主片识别的。 • 特殊完全嵌套方式是在主片的初始化时由命令 字ICW4的D4(SFNM)位指定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

级连缓冲 比较器

中断 服务 寄存器 ISR

优先权 判别 电路 PR

中断 请求 寄存器 IRR

IR0 IR1 IR2 IR3 IR4 IR5 IR6 IR7

中断屏蔽寄存器 IMR

内部总线

-4-

中断系统和中断控制器8259A 中断请求寄存器IRR:8位,用于锁存中断请求信号(信号有效方式由 编程决定)。当相应的中断请求输入引脚有中断请求时,寄存器的相 应位置1; 优先权判别电路PR:识别各中断请求(同时申请)的优先级别,允许 嵌套时须考虑正在服务中断的优先级别,然后送出最高优先级中断源 的请求,并在CPU响应周期内将中断服务寄存器ISR的相应位置位。 各中断请求的优先权级别由编程控制; 中断服务寄存器ISR:8位,用于记录已被CPU响应的中断请求。被服 务的中断将保持该信息位(自动EOI除外,此时不允许使用可屏蔽中 断嵌套),并由普通或特殊EOI命令复位。中断嵌套时,会有多个位 同时被置位,对应已被CPU响应而又未处理完毕的多个中断;

8259A详细说明

中断系统和中断控制器8259A

9.4 中断控制器8259A

现代计算机普遍采用功能很强的中断系统,可同 时处理多个中断源,配置可编程中断控制器对外部中 断(可屏蔽)进行控制和管理: 接收外部的中断请求; 确认当前级别最高的中断请求,并送至CPU的INTR引 脚; 当CPU响应中断时,提供中断类型码; 中断处理过程中屏蔽低优先权的中断请求,而允许高优 先权的中断请求送出,实现中断嵌套; Intel 8259A是典型的中断控制器芯片,广泛应用于微机 系统中。

4

5 6 7 8 9 10 11 12 13 14

25

24 23 22 21 20 19 18 17 16 15

D3

D2 D1

D0

CAS0 CAS1 GND

IR0

INT SP/EN

CAS2

-7-

中断系统和中断控制器8259A

中断响应线INTA:接收CPU在中断响应周期发来的中断响应 信号,8259A接到此信号后,送中断类型码(编程设定);

片选信号CS:由系统高位地址线译码产生,用于选中操作; 地址线A0:用以选择8259A内部不同寄存器; 读信号RD:低电平有效,实现对IRR、ISR和IMR读取; 写信号WR:低电平有效,用于对8259A写入控制字; 级联线CAS2~CAS0:主从式中断管理系统中,所有8259A 芯片的CAS2~CAS0引脚对应连接在一起,与SP/EN信号配 合,实现8259A的级联。对于8259A主片,用于输出,否则 用于输入。在CPU响应中断时,主片在CAS2~CAS0引脚上 输出级联设备编码,选中对应的从片,三个引脚信号的不同 组合000~111,对应于8个从片; 从片编程/缓冲使能SP/EN:双向,低电平有效。在非缓冲方 式下,用作输入线SP,SP=1表示该8259A为主片,否则为 从片;缓冲方式下,用作输出线EN,控制外接数据缓冲器的 接收和发送。

级联方式下,一般不用AEOI,而且一个中断结束可能要发两次 EOI命令,分别清除主、从片ISR中的相应位。

- 14 -

中断系统和中断控制器8259A

5. 中断查询方式

外设仍然通过中断请求要求服务; CPU不是通过中断响应获得中断类型码进入中断服务程序,而是通过 查询获得中断请求情况; 在IF=0,CPU关中断的情况下,外设中断请求信号INTR不被响应, CPU仍可通过查询进入中断服务。

- 11 -

中断系统和中断控制器8259A

3. 中断优先权设置方式

普通全嵌套方式:最基本、最常用的工作方式,也是默认工作方式。 此方式下,8259A的8个中断请求按照IR0优先权最高、IR7优先权最 低的固定优先权顺序,所以对于单片8259A最大中断嵌套深度为8级; 特殊全嵌套方式:与普通全嵌套方式基本相同,优先权按照IR0优先 权最高、IR7优先权最低的固定顺序。不同的是允许同级中断请求产 生INTR信号给CPU,即可以实现同级中断嵌套。该方式一般用在 8259A级联系统中,将主片设定为特殊全嵌套方式,当从片的某一中 断请求被处理时,保证从片较高优先权中断源能够得到响应;

- 15 -

中断系统和中断控制器8259A

7. 级联方式

一个主8259A可以带至多8个从8259A,将中断源扩展到64级; 从片的INT接至主片的IRi端,从片上的中断请求通过主片的INT送至 CPU; CPU的中断响应信号INTA分别送至主、从片上; 主片在级联线CAS2~CAS0上送出标识符编码,对应编码相同的从片 可以获得INTA信号; 在第二个INTA负脉冲时,主片不动作,由从片送上中断类型码; 通常主片的优先权控制采用特殊全嵌套方式,允许同级中断产生嵌套。

当CPU允许可屏蔽中断,即IF=1,发回INTA信号, 8259A使ISR相应位置位,同时将IRR相应位清0,然 后送出中断类型码;

若为AEOI方式,直接清除ISR相应位;否则需要在中 断服务结束时,控制器8259A

9.4.4 8259A的工作方式

-5-

中断系统和中断控制器8259A

中断屏蔽寄存器IMR:8位,用于存放对中断请求的屏蔽信息,可由编 程设定。当IMR中某位被置位,对应的中断请求就被屏蔽,即使IRR 对应位被置位,其中断申请也不能送往CPU;

数据总线缓冲器:8位双向三态缓冲器,是8259A与CPU间的数据传 输通道,用于CPU向8259A写入ICW,OCW,读出状态信息。中断响 应周期内,8259A通过数据总线缓冲器向CPU送中断类型码; 读写控制逻辑:负责接收CPU发来的控制信号,完成写入命令字和读 IRR、ISR和IMR的操作; 级联缓冲/比较器:用于实现8259A的级联,构成主从式扩展中断管理 系统; 控制逻辑:根据编程设定工作方式产生片内控制信号,根据IRR、 IMR的内容和PR的判断结果向CPU发出中断请求,并接受来自CPU的 中断响应信号。

6. 连接系统总线方式

缓冲方式:在多片8259A级联的大系统中,8259A通过总线缓冲器与 系统数据总线相连,SP/EN用作输出EN,控制总线缓冲器的数据传送; 非缓冲方式:当系统中只有一片或几片8259A芯片时, 8259A直接与 数据总线相连。单片系统,SP/EN接高电平;多片级联系统,主片 SP/EN接高电平,从片SP/EN接低电平。

-2-

中断系统和中断控制器8259A

9.4.1 8259A的性能概述

每片8259A能管理8级中断,可采用9片级联构成主从 式64级中断管理系统;

每级中断都可以被屏蔽或允许;

中断响应期间,可提供中断类型码;

允许多级中断嵌套; 可设置多种优先权管理方式及屏蔽功能;

8259A是可编程芯片,可通过编程选择不同的工作方式, 使用灵活、方便;

- 10 -

中断系统和中断控制器8259A

2.屏蔽中断源方式

程序中安排清除中断允许标志位指令(CLI),可以使CPU对所有 可屏蔽中断INT一起进行屏蔽,但无法实现选择性屏蔽。8259A可编程设 定允许或屏蔽指定的可屏蔽中断源:

普通屏蔽方式:通过将中断屏蔽寄存器IMR的某些位置1, 使对应的中断请求被屏蔽,目的是屏蔽高优先级的中断源; 特殊屏蔽方式:该方式主要用于中断嵌套时,开放低优先级 的中断请求,使其能得到及时响应。在预实现特殊屏蔽的中 断服务程序中通过置入控制字将IMR中相应位置1, ISR中 对应位会自动清0,从而屏蔽了本级中断,使低优先级的中 断可以得到响应。在该中断服务程序结束前要退出特殊屏蔽 方式,恢复ISR相应位,再用EOI结束中断服务程序,而且 特殊屏蔽期间被响应的低级中断服务程序必须用特殊中断结 束命令退出。

- 13 -

中断系统和中断控制器8259A

4. 中断结束(EOI)方式

一个中断请求被响应,8259A在ISR相应位置1;中断服务结 束时,必须将该位清0,这就是中断结束操作。

自动中断结束方式(AEOI):CPU一旦进入中断响应总线周期, 8259A就自动将ISR相应位清0。由于不能再为PR提供判优依据,会造 成重复嵌套。常用在不允许中断嵌套或保证不出现中断重复嵌套的场 合; 普通中断结束方式:须由CPU用OUT指令发来一个普通EOI命令, 8259A收到后,将当前ISR中已置1的具有最高优先权的位清0; 特殊中断结束命令:多用于优先权循环的情况下,由于无法确定当前 服务的中断级别,须由CPU发出特殊EOI命令,指明要清除ISR中的哪 一位;

-6-

中断系统和中断控制器8259A

2. 8259A的引脚功能

8259A为28引脚DIP。

CS WR RD D7 D6 D5 D4

1

2 3

28 27 26

VCC A0 INTA IR7 IR6 IR5 IR4 IR3 IR2 IR1

电源VCC和接地GND; 中断请求输入线IR7~IR0: 接受来自外设或8259A从片 的 中 断 请 求 信 号, 可 设 置 为上升沿或高电平触发; 双向三态数据线D7~D0: 可与系统数据总线直接相 连,或通过总线缓冲器与 系 统 数 据 总 线 相 连, 分 别 称为非缓冲和缓冲方式; 中断请求线INT:输出信号, 与CPU的可屏蔽中断输入 端INTR相连,向CPU送中 断请求信号;

8259A有多种工作方式,通过编程设置或改变。

1.中断请求触发方式

电平触发方式:将中断请求输入线上出现高电平视为有 效请求信号;对其有时间限定:过短,不能触发;过 长,重复触发。要求触发高电平持续至CPU中断响应 总线周期中第1个INTA脉冲的下降沿;

边沿触发:将中断请求输入线上出现的上升沿视为中断 请求信号,触发后可一直保持高电平,而不会产生重 复触发。常用负脉冲的后沿实现,同时要防止第1个 INTA信号有效前出现新的中断请求脉冲。

- 16 -

中断系统和中断控制器8259A

8259A缓冲方式级联