ARM LPC 3,4

NXP S32K144 32位ARM MCU汽车电子应用方案

NXP S32K144 32位ARM MCU汽车电子应用方案时间:2018-09-13 11:10:32 作者:NXP 来源:中电网NXP公司的S32K144是应用汽车工业的32位ARM ®Cortex®-M0+/M4F MCU高度可升级的KEA 系列产品,工作电压2.7V-5.5V,提供广泛的存储器,外设和封装选择,满足AEC-Q100规范,支持112MHz 频率(HSRUN模式),性能1.25 Dhrystone MIPS per MHz,集成了数字信号处理器(DSP),可配置嵌套中断向量控制器(NVIC)和单精度浮点单元(FPU).本文介绍了S32K144主要特性,系列架构图和评估板S32K144EVB主要特性和电路图.The S32K1xx Product Series further extends the highly sca lable portfolio of ARM ®Cortex ®-M0+/M4F MCUs in theautomotive industry. It builds on the legacy of the KEA series,whilst introducing higher memory options alongside a richerperipheral set extending capability into a variety of automotiveapplications. With a 2.7 –5.5 V supply and focus on automotive environment robustness, the S32K series devicesare well suited to a wide range of applications in electricalharsh environments, and are optimized for cost-sensitive applications offering lowpin-count options. The S32K seriesoffers a broad range of memory, peripherals, and packageoptions. They share common peripherals and pin countsallowing developers to migrate easily within an MCU familyor among the MCU families to take advantage of morememory or feature integration. This scalability allows developers to standardize on the S32K series for their endproduct platforms, maximizing hardware and software reuse,and reducing time-to-market.S32K is a scalable family of AEC-Q100 qua lifi ed 32-bit Arm® Cortex®-M4F and Cortex-M0+ based MCUs targeted for general purpose automotive and high-reliability industrial applications.Scalability – hardware and software compatible families with multiple performance, memory and feature options Integration–ISO CAN FD, CSEc hardware security, ASIL-B ISO26262 functional safety,ultra-low power performance Software Free automotive-grade Software Development Kit (SDK) and S32 Design Studio IDE AUTOSAR and MCAL Support, third-party ecosystem .S32K144主要特性:• Operating characteristics– Voltage range: 2.7 V to 5.5 V– Ambient temperature range: -40℃to 105℃forHSRUN mode, -40℃to 125℃for RUN mode • Arm™ Cortex-M4F/M0+ core, 32-bit CPU– Supports up to 112 MHz frequency (HSRUN mode)with 1.25 Dhrystone MIPS per MHz– Arm Core based on the Armv7 Architecture andThumb?-2 ISA– Integrated Digital Signal Processor (DSP)– Configurable Nested Vectored Interrupt Controller(NVIC)– Single Precision Floating Point Unit (FPU)• Clock interfaces– 4 - 40 MHz fast external oscillator (SOSC)– 48 MHz Fast Internal RC oscillator (FIRC)– 8 MHz Slow Internal RC oscillator (SIRC)– 128 kHz Low Power Oscillator (LPO)– Up to 112 MHz (HSRUN) System Phased LockLoop (SPLL)– Up to 50 MHz DC external square wave input clock– Real Time Counter (RTC)• Power management– Low-power Arm Cortex-M4F/M0+ core withexcellent energy efficiency– Power Management Controller (PMC) with multiplepower modes: HSRUN, RUN, STOP, VLPR, andVLPS. Note: CSEc (Security) or E EPRO M writes/erase will trigger error flags in HSRUN mode (112MHz) because this use case is not allowed toexecute simultaneously. The device will need toswitch to RUN mode (80 Mhz) to execute CSEc(Security) or EEPROM writes/erase.– Clock gating and low power operation supported onspecific peripherals.• Memory and memory interfaces– Up to 2 MB program flash memory with ECC– 64 KB FlexNVM for data flash memory with ECCand EEPROM emulation.Note: CSEc (Security) orEEPROM writes/erase will trigger error flags inHSRUN mode (112 MHz) because this use case isnot allowed to execute simultaneously. The devicewill need to switch to RUN mode (80 MHz) toexecute CSEc (Security) or EEPROM writes/erase. – Up to 256 KB SRAM with ECC– Up to 4 KB of FlexRAM for use as SRAM orEEPROM emulation– Up to 4 KB Code cache to minimize performanceimpact of memory access latencies–QuadSPI with HyperBus™ support• Mixed-signal analog– Up to two 12-bit Analog-to-Digital Converter(ADC) with up to 32 channel analog inputs permodule – One Analog Comparator (CMP) with internal 8-bitDigital to Analog Converter (DAC)• Debug functionality– Serial Wire JTAG Debug Port (SWJ-DP) combines– Debug Watchpoint and Trace (DWT)– Instrumentation Trace Macrocell (ITM)– Test Port Interface Unit (TPIU)– Flash Patch and Breakpoint (FPB) Unit• Human-machine interface (HMI)– Up to 156 GPIO pins with interrupt functionality– Non-Maskable Interrupt (NMI)• Communications interfaces– Up to three Low Power Universal Asynchronous Receiver/Transmitter (LPUART/LIN) modules with DMA supportand low power availability– Up to three Low Power Serial Peripheral Interface (LPSPI) modules with DMA support and low power availability– Up to two Low Power Inter-Integrated Circuit (LPI2C) modules with DMA supportand low power availability– Up to three FlexCAN modules (with optional CAN-FD support)– FlexIO module for emulation of communication protocols and peripherals (UART, I2C, SPI, I2S, LIN, PWM, etc).– Up to one 10/100Mbps Ethernet with IEEE1588 support and two Synchronous Audio Interface (SAI) modules.• Safety and Security– Cryptographic Services Engine (CSEc) implements a comprehensive set of cryptographic functions as described in theSHE (Secure Hardware Extension) Functional Specification. Note: CSEc (Security) or EEPROM writes/erase willtrigger error flags in HSRUN mode (112 MHz) because this use case is not allowed to execute simultaneously. Thedevice will need to switch to RUN mode (80 MHz) to execute CSEc (Security) or EEPROM writes/erase.– 128-bit Unique Identification (ID) number– Error-Correcting Code (ECC) on flash and SRAM memories– System Memory Protection Unit (System MPU)– Cyclic Redundancy Check (CRC) module– Internal watchdog (WDOG)– External Watchdog monitor (EWM) module• Timing and control– Up to eight independent 16-bit FlexTimers (FTM) modules, offering up to 64 standard channels (IC/OC/PWM)– One 16-bit Low Power Timer (LPTMR) with flexible wake up control– Two Programmable Delay Blocks (PDB) with flexible trigger system– One 32-bit Low Power Interrupt Timer (LPIT) with 4 channels– 32-bit Real Time Counter (RTC)• Package– 32-pin QFN, 48-pin LQFP, 64-pin LQFP, 100-pin LQFP, 100-pin MAPBGA, 144-pin LQFP,176-pin LQFP package options• 16 channel DMA with up to 63 request sources using DMAMUX图1.S32K14x系列架构图评估板S32K144EVBThe S32K144EVB is low-cost evaluation platform and development system for quick application prototyping and demonstration for the S32K144 MCU.评估板S32K144EVB主要特性:Small form factorArduin o™ UNO footprint-compatible with expansion “shield” supportOnboard connectivity for CAN, LIN, UART/SCIIntegrating an SBC (UJA1169) and LIN phy (TJA1027)Easy access to the MCU I/O header pins for prototypingPotentiometer, RGB LED, 2x push buttons and 2 touchpadsIntegrated open-standard serial and debug adapter (OpenSDA) with support for several industry-standard debug interfacesFlexible power supply options (micro USB or external 12 V supply)S32K144EVB Evaluation Board图2.评估板S32K144EVB外形图图3.评估板S32K144EVB电路图(1)图4.评估板S32K144EVB电路图(2) 图5.评估板S32K144EVB电路图(3)图6.评估板S32K144EVB电路图(4) 图7.评估板S32K144EVB电路图(5)AO‐Electronics 傲壹电子官网: 中文网:ALPS ADI IR JRC/NJR KEC OTAX Seoul Semiconductor TI Walsin Technology。

LPC系列arm芯片

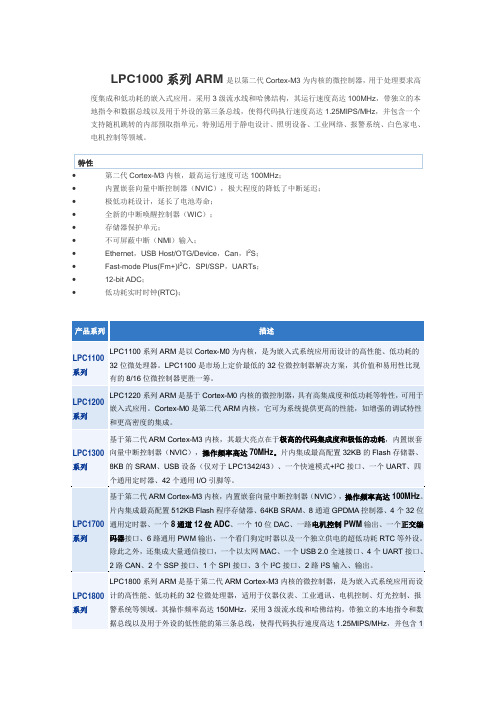

LPC1000系列ARM是以第二代Cortex-M3为内核的微控制器,用于处理要求高度集成和低功耗的嵌入式应用。

采用3级流水线和哈佛结构,其运行速度高达100MHz,带独立的本地指令和数据总线以及用于外设的第三条总线,使得代码执行速度高达1.25MIPS/MHz,并包含一个支持随机跳转的内部预取指单元,特别适用于静电设计、照明设备、工业网络、报警系统、白色家电、电机控制等领域。

特性•第二代Cortex-M3内核,最高运行速度可达100MHz;•内置嵌套向量中断控制器(NVIC),极大程度的降低了中断延迟;•极低功耗设计,延长了电池寿命;•全新的中断唤醒控制器(WIC);•存储器保护单元;•不可屏蔽中断(NMI)输入;•Ethernet,USB Host/OTG/Device,Can,I2S;•Fast-mode Plus(Fm+)I2C,SPI/SSP,UARTs;•12-bit ADC;•低功耗实时时钟(RTC);LPC1100L系列ARM采用Cortex-M0内核,是市场上定价最低的32位MCU解决方案,它的价值和易用性比现有的8位/16位微控制器更胜一筹。

LPC1100L系列ARM性能卓越、简单易用、功耗低,更重要的是,它能显著降低所有8位/16位应用的代码长度。

LPC1100L系列为那些寻求用可扩展ARM架构来执行整个产品开发过程的8位/16位用户提供无缝的整合需求。

这些MCU围绕着新的Cortex-M0架构建立,是开发以来最小巧、功耗最低且最有能效的ARM内核,为电池供电的消费类产品、智能电表、电机控制等应用提供理想的解决方案。

LPC1100L系列ARM每秒4500多万条指令的傲人性能让8位(每秒不到100万条指令)及16位(每秒300万到500万条指令)微控制器相形见绌;LPC1100L不仅能执行基本的控制任务,而且能进行复杂运算,即便最复杂的任务也能轻松应付。

执行效率的提高直接转化为能耗的降低,实现该性能水平的LPC1100L运行速度高达50MHz,其功耗也得到了很大程度的优化——仅需不到10mA的电流。

ARM的七种异常类型

ARM7支持六种操作模式:(1)用户模式(usr):正常的程序执行状态(2)FIQ模式(fiq):支持数据传送或通道处理(3)IRQ模式(irq):用于通用的中断处理(4)管理模式(svc):用于操作系统的保护模式(5)异常模式(abt):数据或者指令预取异常时进入(6)无定义模式(und):当无定义指令被执行时进入(7)软件控制,外部中断,异常处理都可以改变操作模式。

大部分的应用程序在用户模式下执行。

其他模式,比如管理模式,在中断、异常服务、或者访问被保护资源时进入。

ARM 的中央寄存器集是16 个用户寄存器R0 – R15。

这些寄存器均是32 位宽度,R0 – R12 没有其他特殊功能,寄存器R13 – R15在CPU中有特殊功能。

R13被用作栈指针(stack pointer,SP)。

R14被称为链接寄存器(link register, LR),当调用一个函数时返回地址被自动保存到链接寄存器,在函数返回时有效。

这使得快速进入和返回“叶”函数(不调用其他函数的函数)成为可能。

如果函数是分支的一部分(即该函数将调用另一个函数),链接寄存器必须入栈(R13)。

R15 是程序计数器(program counter, PC)。

有趣的是,许多指令也可以在R13 – R15中执行,就像它们是标准的用户寄存器。

ARM中断的问题ARM的七种异常类型---------1> 复位异常2> 数据访问中止异常3> 快速中断请求异常4> 一般中断请求5> 预取指令异常6> 软件中断异常7> 未定义异常-------------------------问题:1> 为什么除了进入复位异常模式外,在别的异常处理模式中都允许FIQ中断?2> 数据访问中止异常的优先级大于 FIQ异常,为什么在数据访问异常处理模式中,还允许 FIQ中断?这样不就成了:在高优先级异常处理中允许低优先级的中断发生?即使这样,因为FIQ中断的优先级 < 数据异常中断优先级,也不会进入 FIQ中断处理程序啊,这样不就更没有用处了??ARM体系的各种异常的分析(学习日记)- [ARM7TDMI]版权声明:转载时请以超链接形式标明文章原始出处和作者信息及本声明/logs/10669519.html1.复位异常(1)当内核的nRESET信号被拉低时,ARM处理器放弃正在执行的指令,当nRESET信号再次变高时,ARM处理器进行复位操作;(2)系统复位后,进入管理模式对系统进行初始化,复位后,只有PC(0x00000000)和CPSR (nzcvqIFt_SVC)的值是固定的,另外寄存器的值是随机的。

LPC546xx 32位ARM Cortex-M4微控制器产品数据手册说明书

LPC546xx32位ARM Cortex-M4微控制器;最高512 KB闪存和200 KBSRAM;高速USB设备/主机 + PHY;全速USB设备/主机;以太网AVB;LCD;EMC;SPIFI;CAN FD、SDIO;SHA;12位5M采样/s ADC;DMIC子系统第2.6版——2018年10月23日产品数据手册1. 简介LPC546xx是基于ARM Cortex-M4的微控制器系列,具有丰富的外设组合、功耗极低和增强的调试功能,适用于嵌入式应用。

ARM Cortex-M4是一款32位微控制器内核,具有低功耗、易调试、易集成等多种系统增强优势。

ARM Cortex-M4内核CPU采用3级流水线和哈佛架构,具有独立的本地指令和数据总线以及用于系统外设的第三总线,同时还包含一个支持不确定分支操作的内部预取单元。

ARM Cortex-M4支持单循环数字信号处理和SIMD指令。

内核集成硬件浮点处理器。

LPC546xx系列搭载高达512 KB的闪存、200 KB的片上SRAM、高达16 kB的EEPROM存储器、用于扩展程序存储器的四通道SPI闪存接口(SPIFI)、1个高速USB和1个全速USB主机和设备控制器、以太网AVB、LCD控制器、多个智能卡接口、SD/MMC、CANFD、1个外部存储器控制器(EMC)、1个带PDM麦克风接口和I2S的DMIC子系统、5个通用定时器、SCTimer/PWM、RTC/报警定时器、多速率定时器(MRT)、窗口看门狗定时器(WWDT)、10个灵活的串行通信外设(USART、SPI、I2S、I2C接口)、安全散列算法(SHA)、12位5.0 M采样/秒ADC和1个温度传感器。

2. 特性和优势◼ARM Cortex-M4内核(版本:r0p1):◆ARM Cortex-M4处理器,工作频率高达220 MHz。

◆LPC5460x/61x器件的CPU工作频率高达180 MHz。

ARM开发软件及实用工具介绍

ARM开发软件及实用工具介绍ARM 开发软件及实用工具介绍一、编译器介绍1、ADS1.2 ADS是ARM公司的集成开发环境软件,他的功能非常强大。

他的前身是SDT,SDT是ARM公司几年前的开发环境软件,目前SDT早已经不再升级。

ADS包括了四个模块分别是:SIMULATOR;C 编译器;实时调试器;应用函数库。

ADS 的编译器调试器较SDT都有了非常大的改观,ADS1.2提供完整的WINDOWS界面开发环境。

C 编译器效率极高,支持c 以及c++,使工程师可以很方便的使用C语言进行开发。

提供软件模拟仿真功能,使没有Emulators的学习者也能够熟悉ARM的指令系统。

配合FFT -ICE使用,ADS1.2提供强大的实时调试跟踪功能,片内运行情况尽在掌握。

ADS1.2需要硬件支持才能发挥强大功能。

目前支持的硬件调试器有 Multi-ICE以及兼容Multi-ICE的调试工具如FFT-ICE。

而简易下载电缆不能支持ADS1.2 2、ARM REALVIEW DEVELOPER SUITE RealView Developer Suite工具是ARM公司是推出的新一代ARM集成开发工具。

支持所有ARM 系列核,并与众多第三方实时操作系统及工具商合作简化开发流程。

开发工具包含以下组件:· 完全优化的ISO C/C++编译器· C++ 标准模板库· 强大的宏编译器· 支持代码和数据复杂存储器布局的连接器· 可选GUI调试器· 基于命令行的符号调试器(armsd) · 指令集仿真器· 生成无格式二进制工具、Intel 32位和Motorola 32位ROM映像代码的指令集模拟工具· 库创建工具· 内容丰富的在线文档官方网址:3、IAR EWARM Embedded Workbench for ARM 是IAR Systems 公司为ARM 微处理器开发的一个集成开发环境(下面简称IAR EWARM)。

ARM开发板使用手册

ARM开发板使用手册PHILIP LPC2132ARM7TDMI第一章介绍LPC2132开发板是专门为arm 初学者开发的实验板,用户可以做基础的arm实验,也可以做基于ucos-ii的操作系统实验。

本系统的实验源代码全部开放,用户可以在此基础上开发产品,减少重复劳动。

由于LPC2132体积很小,并且功能强大,因此特别适合需要复杂智能控制的场合,其运行速度高于早期的80486计算机,而体积只有指甲大。

我们已经将LPC2132产品成功应用在干扰比较强的工业场合,经过6个月的运行,各项指标符合要求。

因此我们特别推荐这一款开发板作为ARM初学者入门。

由于此款开发板体积很小,非常适合直接应用在工业以及民用智能控制器的场合。

LPC2132 CPU介绍LPC2131/2132/2138 是基于一个支持实时仿真和跟踪的16/32 位ARM7TDMI-STM CPU,并带有32kB、64kB 和512kB 嵌入的高速Flash 存储器。

128 位宽度的存储器接口和独特的加速结构使32 位代码能够在最大时钟速率下运行。

对代码规模有严格控制的应用可使用16 位Thumb 模式将代码规模降低超过30%,而性能的损失却很小。

较小的封装和很低的功耗使LPC2131/2132/2138 特别适用于访问控制和POS 机等小型应用中;由于内置了宽范围的串行通信接口和8/16/32kB 的片内SRAM,它们也非常适合于通信网关、协议转换器、软件modem、语音识别、低端成像,为这些应用提供大规模的缓冲区和强大的处理功能。

多个32 位定时器、1个或2 个10 位8 路的ADC、10 位DAC、PWM 通道、47 个GPIO 以及多达9 个边沿或电平触发的外部中断使它们特别适用于工业控制应用以及医疗系统。

主要特性●●16/32 位ARM7TDMI-S 核,超小LQFP64 封装。

●●8/16/32kB 的片内静态RAM 和32/64/512kB 的片内Flash 程序存储器。

ARM的37个寄存器详解

ARM的37个寄存器详解ARM寄存器ARM共有37个32位物理寄存器,7种⼯作模式下可访问的寄存器见下表,User和System使⽤完全相同的物理寄存器。

2.1 R0~R7所有⼯作模式下,R0-R7都分别指向同⼀个物理寄存器(共8个物理寄存器),它们未被系统⽤作特殊的⽤途。

在中断或异常处理进⾏⼯作模式转换时,由于不同⼯作模式均使⽤相同的物理寄存器,可能造成寄存器中数据的破坏。

2.2 R8~R12在User&System、IRQ、Svc、Abt和Und模式下访问的R8~R12都是同⼀个物理寄存器(共5个物理寄存器);在FIQ模式下,访问的R8_fiq~R12_fiq是另外独⽴的物理寄存器(共5个物理寄存器)。

2.3 R13和R14在User&System、IRQ、FIQ、Svc、Abt和Und访问的R13_~R14都是各⾃模式下独⽴的物理寄存器(共12个物理寄存器)。

R13在ARM指令中常⽤作堆栈指针(SP),但这只是⼀种习惯⽤法,⽤户也可使⽤其他的寄存器作为堆栈指针。

⽽在Thumb指令集中,某些指令强制性的要求使⽤R13作为堆栈指针。

由于处理器的每种⼯作模式均有⾃⼰独⽴的物理寄存器R13,在⽤户应⽤程序的初始化部分,⼀般都要初始化每种模式下的R13,使其指向该⼯作模式的栈空间。

这样,当程序进⼊异常模式时,可以将需要保护的寄存器放⼊R13所指向的堆栈,⽽当程序从异常模式返回时,则从对应的堆栈中恢复,采⽤这种⽅式可以保证异常发⽣后程序的正常执⾏。

R14称为链接寄存器(Link Register),当执⾏⼦程序调⽤指令(BL)时,R14可得到R15(程序计数器PC)的备份。

在每⼀种⼯作模式下,都可⽤R14保存⼦程序的返回地址,当⽤BL或BLX指令调⽤⼦程序时,将PC的当前值复制给R14,执⾏完⼦程序后,⼜将R14的值复制回PC,即可完成⼦程序的调⽤返回。

以上的描述可⽤指令完成。

执⾏以下任意⼀条指令:MOV PC, LRBX LR在⼦程序⼊⼝处使⽤以下指令将R14存⼊堆栈:STMFD SP!,{,LR}对应的,使⽤以下指令可以完成⼦程序返回:LDMFD SP!,{,PC}R14也可作为通⽤寄存器。

ARM初学入门

经过一段时间对ARM的学习,在这里跟大家说一些前期的学习经验,另外仅以一个例子说明一下ADS的开发过程,因为这也是初学,可能有的地方说的不太好,望大家谅解,另外可以找其它参考资料来学习。

第一部分:ARM前期学习经验个人认为,要想学好ARM应该首先对ARM的整体框架(包括ARM体系结构,ARM开发过程,及ARM程序框架及执行过程等)有一个了解。

这里这就不多说了,这些东西我也只是刚刚开始学习,还没有很好的掌握,就只说一些个人想法吧。

呵呵,因为时间比较紧张,本来说是一个星期搞定ARM,至少拿着书本可以一点点的做着,可是经过上一个星期,到最后,哇,真的快疯了。

刚开始拿到实验箱,以为和NIOS一样,多跑一些DEMO应该就差不多会玩了,没想到一开始就碰到一个大问题,ARM实验箱里边带了几本教材和实验指导书,拿着实验指导书做了几个DEMO就做不下去了,因为前两个DEMO还比较简单,就只是用汇编语言写了几条对ARM寄存器操作的语句,学过汇编语言的很快就可以理解了。

可是往后就不一样了,因为刚开始学,不太了解ARM程序的框架,实在是看不懂了,为什么每个全程里边都有用到44b.h ,44blib.h ,44blib.c还有一个44binit.s文件?前边三个还容易理解,玩过单片机的很容易就能看出来44b.h 里边定义了一些在S3C44B0X内部的寄存器,44blib.h和44blib.c定义了一些有关初始化的函数,而44binit.s呢?看不懂,到这里我的ARM程序就没法往下做了,只有在网上再找资料,看这个函数到底是干什么用的,原来这就是以前经常听说的“bootloader”或着说是“启动代码”,或着说是“ARM的引导程序”,就是处理器在启动的时候执行的一段代码,主要任务是初始化处理器模式,设置堆栈,初始化变量等等.由于以上的操作均与处理器体系结构和系统配置密切相关,所以一般由汇编来编写(关于这方面的内容大家可以查看相关资料)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

外部中断实例

(4)中断服务程序定义

• 声明 void

__irq IRQ_Eint3(void) • 中断服务程序结束前清除Eint3中断标志 EXTINT D3=1 清除Eint3中断标志 EXTINT=1<<3 • 中断服务程序结束前,更新优先级 VICVectAddr = 0;

外部ቤተ መጻሕፍቲ ባይዱ断实例

#include "config.h" #define BEEPCON 1<<7 void __irq IRQ_Eint3(void) { uint32 x; x = IO0SET; if( (x&0x00000080)==0 ) { //原来p0.7低电平, 现在使p0.7输出高电平 IO0SET = 0x00000080; } else { //原来p0.7高电平, 现在使p0.7输出低电平 IO0CLR =0x00000080; } EXTINT = 1<<3; //清除Eint3中断标志 VICVectAddr = 0;//ISR快结束时写入一个值,更新优先级 }

1 11059200

• 定时时间= * MR匹配值

* (PR预分频数+1)

• 定时2S 2=((PR+1)*MR)/11059200 (PR+1)*MR=11059200*2 T0PR=99 T0MR0= 2*11059200/100=2*110592=221184

定时器实例

(c) 匹配控制 T0MCR(0xE0004014) • 匹配产生中断 MCR D0=0 匹配时不产生中断 =1 匹配时产生中断 • 计数到时,使T0TC(0xE0004008)复位(当T0TC=T0MR) T0MCR D1=1 匹配时控制TC复位 T0MCR=0x00000003; (复位/中断 配置) (d)控制T0TC复位 T0TCR (0xE0004004) D0=1 控制定时器开始计数/计时 D1=1 控制定时器和预分频器在Fpclk下一个时 钟上升沿复位 复位并开始计时 T0TCR=0x00000003

外部中断实例

(2)初始化-----蜂鸣器 P0.7 GPIO输出 PINSEL0=0x00000000; IO0DIR=0x00000080; (3)初始化------KEY 外部中断 PINSEL1=3<<8 ; D9D8=11 P0.20为EInt3 (4)中断初始化--(a)开中断 IRQEnable() CPSR(D7) I=0 IRQ开中断 I=1 禁止中断

外部中断实例

f)设置触发模式与极性 EXTMODE 模式配置寄存器D3EINT3 0: 电平触发 1: 边沿触发 EXTMODE=1<<3 EXTPOLAR 极性配置寄存器D3EINT3 0 :下降沿触发 1 : 上升沿触发 EXTPOLAR=0x00; g)EInt3开中断 VICIntEnable D17置1 VICIntEnable=1<<17

定时器实例

Void Time0Init(void) //定时器0初始化配置

{ T0PR=99; T0MCR=0x03; //MR=TC 复位TC, 产生Timer0中断 T0MR0=221184; //定时2秒 T0TCR=0x03; VICIntSelect=0; // Timer0 D4=0 IRQ方式 VICVectCntl0=0x20|0x04; VICVECTAddr0=(uint32)IRQ_Timer0; VICIntEnable=1<<4; //Timer0开中断 }

外部中断实例

b)配置EINT3为IRQ中断

选择寄存器VICIntSelect

模块 系统控 制

1:FIQ 0:IRQ VICIntSelect D17=0 VICIntSelect= 0x00000000;

系统控 制

系统控 制 系统控 制 A/D 保留

产生中断标 志 外部中断0 (EINT0) (EINT1) EINT2 EINT3

VIC通 道 14

15

16 17

A/D转换器 保留

18 19-31

外部中断实例

c)配置EINT3中断向量,并且中断服务程序地址程序地址保存 在VICVectAddr0 D5=1 VICVectaddr0中保存D4..D0为中断通道号的中断 服务程序地址 D4..0=10001 (17 Slot) 中断通道号 VICVectCntl0=0B110001=0x20|17 d)中断服务程序向量地址寄存器 VICVectAddr0= D4..D0为中断通道号的中断服务程序地址 e)清除EINT3中断标志位 寄存器EXTINT D0EINT0; D1EINT1;D2EINT2;D3EINT3 EXTINT=1<<3; • 注意:有外部中断,将中断状态寄存器对应位置1,利用将 EXTINT对应位置1清除对应外部中断标志

向量中断控制器VIC 一、特点

1. 2. 3. 4. 5.

32路中断请求输入 16路IRQ向量中断 为中断请求动态配置优先级 可产生软件中断 由VIC管理中断过程

向量中断控制器VIC 二、功能

1.接收中断请求: 接收32个中断源的中断请求。 2.编程指定中断源中断类型

• • FIQ:快速中断类型,实现需要快速处理的任务,优 先级高. 非向量IRQ:由软件识别中断源,由程序控制调用 中断服务程序. 向量IRQ:由硬件识别中断源,并且硬件自动控制调 用中断服务程序。同时最多处理16路中断请求.

D0(EINT0)=0 =1 D1(EINT1)=0 =1 D2(EINT2)=0 =1 D3(EINT3)=0 =1 电平触发 边沿触发 电平触发 边沿触发 电平触发 边沿触发 电平触发 边沿触发

低电平、下降沿 高电平、上升沿 低电平、下降沿 高电平、上升沿 D2(EINT2)=0 =1 D3(EINT3)=0 =1 低电平、下降沿 高电平、上升沿 低电平、下降沿 高电平、上升沿

外部中断实例 (9)设定向量地址寄存器保存的中断服务程 序对应的中断源. • VICVectCntl0 … • VICVectCntl15 D5=1 对应的向量地址寄存器保存一中断源中 断服务程序入口. D4..D0=中断源对应的通道号

外部中断实例

(1)EINT3中断执行过程 状态寄存器CPSR I=0 IRQ开中断

外部中断实例 (5)清除中断标志,准备接收EINT3中断 寄存器EXTINT D0(EINT0)=1 清除中断标志 D1(EINT1)=1 清除中断标志 D2(EINT2)=1 清除中断标志 D3(EINT3)=1 清除中断标志

外部中断实例

(6)设置VIC中断识别(识别p0.20引脚信号为中断信号) • 外部模式寄存器EXTMODE

定时器实例

Int main(void) { IRQEnable(); PINSEL0=0x00000000; IO0DIR=0x00000080; Timer0Init(); while(1); return 0; }

外部中断实例 (8)开放EINT3中断 • 寄存器VICINTEnable:对应中断源通道号与 寄存器位对应. D17=0 屏蔽中断EINT3 =1 开放中断EINT3 (9)向量IRQ,将中断服务程序入口保存到向 量寄存器. • VICVectAddr0 :保存中断服务程序地址 … • VICVectAddr15 :保存中断服务程序地址

•

向量中断控制器VIC 二、功能

3.向ARM处理器发送中断信号:

• FIQ:接收到一个以上的FIQ请求,向ARM处理 器产生FIQ中断请求信号(所有FIQ或操作) • IRQ:接收到一个以上的IRQ(向量、非向量) 请求,向ARM处理器产生IRQ中断请求信号 (所有IRQ或操作)

向量中断控制器VIC 二、功能

定时器实例

#include “config.h” #define BEEPCON 1<<7 Void __irq IRQ_Timer0(void) { if((IO0SET&BEEPCON)==0) {IO0SET=BEEPCON;//不响} else {IO0CLR=BEEPCON;//响} T0IR=0x01; //清除Timer0中断标志 VICVectAddr=0x00; }

外部中断实例

int main(void) { IRQEnable(); //IRQ开中断 PINSEL0=0x00000000; // p0.7 配置为GPIO功能 PINSEL1 = 3<<8; // 设置管脚连接,P0.20配置为EINT3 IO0DIR = BEEPCON; // 设置Beep控制口为输出,p0.7配置为输出 IO0SET = BEEPCON; // 控制蜂鸣器不响 VICIntSelect = 0x00000000; // 设置EInt3为IRQ中断 VICVectCntl0 = 0x20|17; // VICVectAddr0保存通道号17的中断服务 //程序地址 VICVectAddr0 = (int)IRQ_Eint3; // 设置中断服务程序地址 EXTINT = 1<<3; // 清除EINT3中断标志 EXTMODE = 1<<3; //设置EINT3中断为边沿触发模式 EXTPOLAR = 0x00; // 设置EINT3中断为下降沿触发 VICIntEnable = 1<<17; // Eint3开中断 while(1); // 等待中断Ï return(0); }

定时器实例

一、题目 (1)内容

使用定时器0实现2秒定时,定时到时,控制蜂鸣器执 行前次定时到时的相反效果,即: 前次蜂鸣器响,本次不响; 前次蜂鸣器不响,本次响; (2)要求: 使用C语言编程 使用定时器中断

定时器实例

(1)、定时器初始化 ( a)、 定时器功能图