DSP2-F28335的结构原理

DSP第5章-F28335-概述

外设总线: 用于外设互联,复用多种总线。

5.3.3 外设

1. ePWM:6个,可单独控制各个引脚,功能更强大 2.eCAP:6个 3.eQEP:2个,测速更加方便 4.ADC:12位,16路,80ns转换时间 5.Watchdog Timer:1个 6.McBSP:2个,用于连接高速外设,如音频处理模块 7.SPI:1个,连接具有SPI借口的外设

得益于F28335浮点运算单元,从而简化软件开发,缩 短开发周期,降低开发成本。

5.1 F28335的性能

高性能静态CMOS技术:主频150MHZ,指令周期6.67ns; 低功

耗设计,1.9V/1.8V内核电压,3.3VI/O引脚电压;Flash编 程电压为3.3V

高性能32位CPU:IEEE-754单精度浮点运算单元(FPU) ;

3个32位CPU定时器:定时器0、1、2。T0、T1为一般定时器 ,T0连接至PIE,T1连接至中断INT13,T2用作DSP/BIOS的

5.1 F28335的性能

串行端口外设:2个eCAN2.0B; 3个SCI(UART);2个 McBSP;1个SPI; 1个I2C总线接口。

16通道12位模数转换模块:转换时间80ns,2X8通道复用输入 接口;2个采样保持电路;单/连续通道转换;内部或外部参考电 压

▪32位定点CPU架构,支持16位和32位指令操作。前者减 少存储,提高代码密度。后者加快指令执行时间。 ▪32位IEEE-754单精度FPU,具有高效C/C++引擎,可使 用高级语言编程。 ▪32X32位MAC64位处理能力。 ▪快速中断响应。 ▪“原子指令”读写简化机制。执行更快,代码更少。

F28335 EPWM各模块简介

F28335 EPWM各模块简介以DSP为基础的数字信号控制器(DSC)执行电动马达相位控制时,其核心组件为事件管理器(Event Manager)。

由于以DSP为基础的控制器应用范围正逐渐扩大到高效能电子产品的触发与控制等各种相关领域,因此这类事件管理器也需要一套全新架构。

以德州仪器(TI)基于DSP的24x和F28x数字信号控制器来看,事件管理器是由DSP 的可程式逻辑电路构成,以便产生脉冲宽度调变(PWM)信号。

这些事件管理器虽然是为了三相系统所设计,却拥有极大弹性,可以高效率应用在多相位或其它特殊需求应用(或许再加上一些软件)。

事件管理器的功能已通过数个世代的处理器考验与测试,只需要进行一些细部调整即可。

针对新的应用需求,TI开发出一套称为加强型事件管理器(eEVM)的架构,将应用于F28x衍生系列的新元件,包括TMS320F2801、TMS320F2806和TMS320F2808控制器(TMS320F2801已实作部份功能)。

加强型事件管理器的PWM产生方式与过去有很大差异。

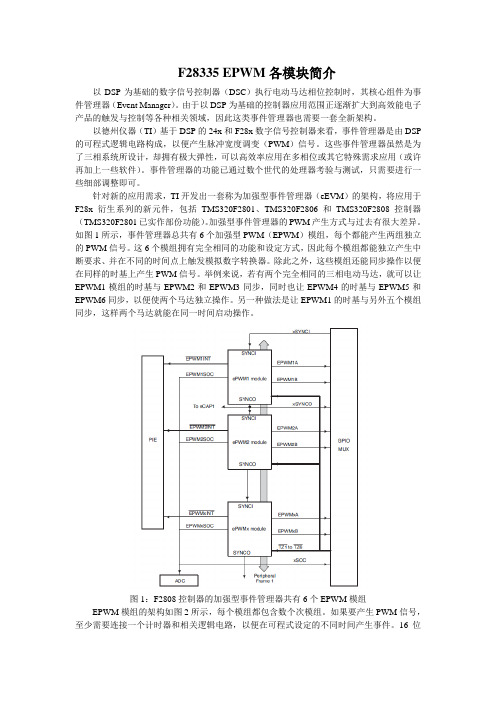

如图1所示,事件管理器总共有6个加强型PWM(EPWM)模组,每个都能产生两组独立的PWM信号。

这6个模组拥有完全相同的功能和设定方式,因此每个模组都能独立产生中断要求、并在不同的时间点上触发模拟数字转换器。

除此之外,这些模组还能同步操作以便在同样的时基上产生PWM信号。

举例来说,若有两个完全相同的三相电动马达,就可以让EPWM1模组的时基与EPWM2和EPWM3同步,同时也让EPWM4的时基与EPWM5和EPWM6同步,以便使两个马达独立操作。

另一种做法是让EPWM1的时基与另外五个模组同步,这样两个马达就能在同一时间启动操作。

图1:F2808控制器的加强型事件管理器共有6个EPWM模组EPWM模组的架构如图2所示,每个模组都包含数个次模组。

如果要产生PWM信号,至少需要连接一个计时器和相关逻辑电路,以便在可程式设定的不同时间产生事件。

DSP28335开发板原理图

F28335

GPIO76/XD3 GPIO77/XD2 GPIO78/XD1 GPIO79/XD0 GPIO38/XWE0 XCLOUT VDD VSS GPIO28/SCIRXDA/XZCS6 GPIO34/ECAP1/XREADY VDDIO VSS GPIO36/SCIRXDA/XZCS0 VDD VSS GPIO35/SCITXDA/XR/W XRD GPIO37/ECAP2/XZCS7 GPIO40/XA0/XWE1 GPIO41/XA1 GPIO42/XA2 VDD VSS GPIO43/XA3 GPIO44/XA4 GPIO45/XA5 VDDIO VSS GPIO46/XA6 GPIO47/XA7 GPIO80/XA8 GPIO81/XA9 GPIO82/XA10 VSS VDD GPIO83/XA11 GPIO84/XA12 VDDIO VSS GPIO85/XA13 GPIO86/XA14 GPIO87/XA15 GPIO39/XA16 GPIO31/CANTXA/XA17

直直驱直驱驱

Diode 1N4007 D5 R16 1K/5% Q1 S8550 EPWM2_A EPWM2_B EPWM3_A

LS1 D3 1N4148 Buzzer D3.3V R14 0R/5% D5V 16 15 14 13 12 11 10 9 D5V SOMI SPISOMIA CLK SPICLKA CN1 5 4 3 2 1 R94 10K/5% R95 10K/5% R96 10K/5% R97 10K/5% SD1 D3.3V 11 10 8 7 6 5 4 3 2 1 9 nCD WP DATA1 DATA0 GND CLK VDD GND CMD CD/DATA3 DATA2 PAD4 PAD3 PAD2 PAD1 15 14 13 12 R17 1K/5% R18 1K/5% R19 1K/5% R20 1K/5% R21 1K/5% R74 1K/5% R75 1K/5% D3.3V 3.3VAS

25_TI DSP入门芯片TMS320F28335

作为一个电子硬件工程师,怎么不能懂DSP,或者我们中有一些同学对DSP的理解还不是很多,今天就让我们给大家介绍一个DSP的入门芯片,来自TI的TMS320F28335。

相信看过了这一系列的内容,大家会对DSP有初步的了解。

TMS320F28335简介:TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。

其主要性能如下:高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;6通道的DMA控制器;片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。

GPI00~GPI063连接到该中断。

GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;88个可编程的复用GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序。

DSPF28335---中断系统

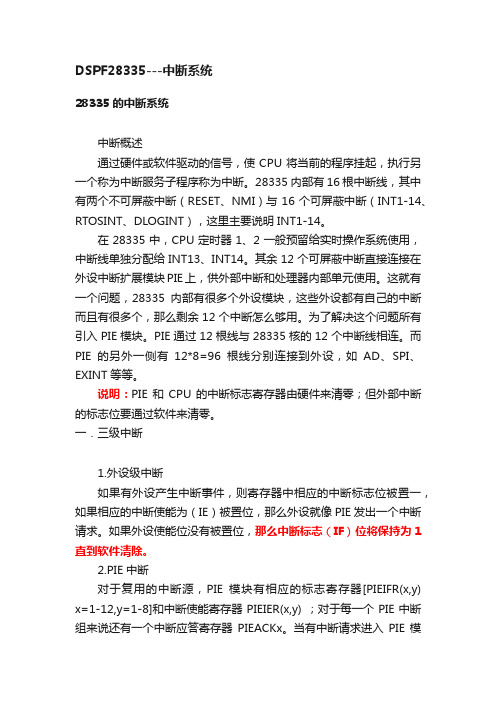

DSPF28335---中断系统28335的中断系统中断概述通过硬件或软件驱动的信号,使CPU将当前的程序挂起,执行另一个称为中断服务子程序称为中断。

28335内部有16根中断线,其中有两个不可屏蔽中断(RESET、NMI)与16个可屏蔽中断(INT1-14、RTOSINT、DLOGINT),这里主要说明INT1-14。

在28335中,CPU定时器1、2一般预留给实时操作系统使用,中断线单独分配给INT13、INT14。

其余12个可屏蔽中断直接连接在外设中断扩展模块PIE上,供外部中断和处理器内部单元使用。

这就有一个问题,28335内部有很多个外设模块,这些外设都有自己的中断而且有很多个,那么剩余12个中断怎么够用。

为了解决这个问题所有引入PIE模块。

PIE通过12根线与28335核的12个中断线相连。

而PIE的另外一侧有12*8=96根线分别连接到外设,如AD、SPI、EXINT等等。

说明:PIE和CPU的中断标志寄存器由硬件来清零;但外部中断的标志位要通过软件来清零。

一.三级中断1.外设级中断如果有外设产生中断事件,则寄存器中相应的中断标志位被置一,如果相应的中断使能为(IE)被置位,那么外设就像PIE发出一个中断请求。

如果外设使能位没有被置位,那么中断标志(IF)位将保持为1直到软件清除。

2.PIE中断对于复用的中断源,PIE模块有相应的标志寄存器[PIEIFR(x,y) x=1-12,y=1-8]和中断使能寄存器PIEIER(x,y) ;对于每一个PIE中断组来说还有一个中断应答寄存器PIEACKx。

当有中断请求进入PIE模块的时候,如果相应的PIE中断标志位PIEIFR(x.y)和中断使能寄存器PIEIER(x,y)置1;这是PIE控制器就会检查PIEACKx标志位看CPU 是否已经准备好接收这个PIE中断组的中断。

说明:如果PIEACKZx被清零,PIE会把这个中断请求送到CPU 级的INTx。

F28335EPWM各模块简介

F28335EPWM各模块简介F28335 EPWM各模块简介以DSP为基础的数字信号控制器(DSC)执行电动马达相位控制时,其核心组件为事件管理器(Event Manager)。

由于以DSP为基础的控制器应用范围正逐渐扩大到高效能电子产品的触发与控制等各种相关领域,因此这类事件管理器也需要一套全新架构。

以德州仪器(TI)基于DSP的24x和F28x数字信号控制器来看,事件管理器是由DSP 的可程式逻辑电路构成,以便产生脉冲宽度调变(PWM)信号。

这些事件管理器虽然是为了三相系统所设计,却拥有极大弹性,可以高效率应用在多相位或其它特殊需求应用(或许再加上一些软件)。

事件管理器的功能已通过数个世代的处理器考验与测试,只需要进行一些细部调整即可。

针对新的应用需求,TI开发出一套称为加强型事件管理器(eEVM)的架构,将应用于F28x衍生系列的新元件,包括TMS320F2801、TMS320F2806和TMS320F2808控制器(TMS320F2801已实作部份功能)。

加强型事件管理器的PWM产生方式与过去有很大差异。

如图1所示,事件管理器总共有6个加强型PWM(EPWM)模组,每个都能产生两组独立的PWM信号。

这6个模组拥有完全相同的功能和设定方式,因此每个模组都能独立产生中断要求、并在不同的时间点上触发模拟数字转换器。

除此之外,这些模组还能同步操作以便在同样的时基上产生PWM信号。

举例来说,若有两个完全相同的三相电动马达,就可以让EPWM1模组的时基与EPWM2和EPWM3同步,同时也让EPWM4的时基与EPWM5和EPWM6同步,以便使两个马达独立操作。

另一种做法是让EPWM1的时基与另外五个模组同步,这样两个马达就能在同一时间启动操作。

图1:F2808控制器的加强型事件管理器共有6个EPWM模组EPWM模组的架构如图2所示,每个模组都包含数个次模组。

如果要产生PWM信号,至少需要连接一个计时器和相关逻辑电路,以便在可程式设定的不同时间产生事件。

DSP28335的调试总结,这是一份总结很全面的资料,我在学

DSP28335的调试总结,这是一份总结很全面的资料,我在学习开发板的一些总结,希望能得到同行的帮助,愿与大家一起学习和分享1DSP的PWM信号1.1简介DSP28335共12路16位的ePWM,能进行频率和占空比控制。

ePWM的时钟TBCLK=SYSCLKOUT/(HSPCLKDIV×CLKDIV):PWM信号频率由时基周期寄存器TBPDR和时基计数器的计数模式决定。

初始化程序采用的计数模式为递增计数模式。

在递增计数模式下,时基计数器从零开始增加,直到达到周期寄存器值(TBPDR)。

然后时基计数器复位到零,再次开始增加。

PWM信号周期与频率的计算如下:1.2端口对应关系通道相应PWM的A/B对应JP0B端口号1ePWM1A92ePWM1B103ePWM2A114ePWM2B125ePWM3A136ePWM3B147ePWM4A158ePWM4B169ePWM5A1710ePWM5B1811ePWM6A1912ePWM6B20说明:JP0B的端口号按“Z”字形顺序数。

1.3初始化程序注释void InitPwm1AB(float32f){Uint16T= 2343750/f-1.0;//系统时钟SYSCLKOUT=150MHz,TBCLK=6.6666667ns,在连续增计数模式下,f=150000000/(TBPDR+1) EALLOW;//先初始化通用输入输出口//GpioCtrlRegs.GPAPUD.bit.GPIO0 = 0;GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1;GpioCtrlRegs.GPAPUD.bit.GPIO1 = 0;GpioCtrlRegs.GPAMUX1.bit.GPIO1 = 1;EPwm1Regs.TBPHS.half.TBPHS= 0; // 在相位寄存器中设置计数器的起始计数位置//下面两条语句组合对PWM的时钟进行分频EPwm1Regs.TBCTL.bit.CLKDIV = 6;EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0;EPwm1Regs.TBPRD = T; //在周期寄存器中设置计数器的计数周期//TBCTL为定时器控制寄存器EPwm1Regs.TBCTL.bit.CTRMODE= TB_COUNT_UP; //设置计数模式位为连续增计数模式,产生对称方波EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // 将定时器相位使能位关闭EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;//映射寄存器SHADOW使能并配置映射寄存器为自动读写EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // 定时器时钟源选择,一共有四种时钟源EPwm1Regs.CMPA.half.CMPA= 0.0001*T;// 设置EPWM1A比较值寄存器的比较值,即体现EPWM1A的占空比EPwm1Regs.CMPB= 0.0001*T;EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;//A模块比较模式EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;//B模块比较模式EPwm1Regs.CMPCTL.bit.LOADAMODE= CC_CTR_ZERO; // A模块比较使能,通过写0来清除SHDWAMODE位来使能load on CTR=ZeroEPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // B模块比较使能,通过写0来清除SHDWBMODE位来使能load on CTR=Zero//AQCTLA为输出A比较方式控制寄存器EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET; // TBCTR(计数器)计到零时使输出为反向EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;//TBCTR(计数器)与CMPA在up 计数时相等使输出为high,这关系的输出的占空比EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET;EPwm1Regs.AQCTLB.bit.CBU = AQ_CLEAR;EDIS;}2DSP的CAN通信2.1CAN2.0B协议简述TMS320F28335上有2个增强型CAN总线控制器,符合CAN2.0B协议,其总线波特率可达到1Mbps。

TMS320F28335中文资料资料讲解

TMS320F28335中⽂资料资料讲解T M S320F28335中⽂资料TMS320F28335中⽂资料TMS320F28335采⽤176引脚LQFP四边形封装,其功能结构参见参考⽂献。

其主要性能如下:⾼性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;⾼性能的32位CPU,单精度浮点运算单元(FPU),采⽤哈佛流⽔线结构,能够快速执⾏中断响应,并具有统⼀的内存管理模式,可⽤C/C++语⾔实现复杂的数学算法;6通道的DMA控制器;⽚上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有⽚上振荡器,看门狗模块,⽀持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU 的输⼊时钟频率;8个外部中断,相对TMS320F281X系列的DSP,⽆专门的中断引脚。

GPI00~GPI063连接到该中断。

GPI00⼀GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3⼀XINT7外部中断;⽀持58个外设中断的外设中断扩展控制器(PIE),管理⽚上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个⾼分辨率脉宽调制模块(HRPWM)、6个事件捕获输⼊,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1⽤作⼀般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2⽤于DSP /BIOS的⽚上实时系统,连接到中断INTl4,如果系统不使⽤DSP/BIOS,定时器2可⽤于⼀般定时器;串⾏外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串⾏接⼝)模块、1个SPI模块、1个I2C主从兼容的串⾏总线接⼝模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时⽀持多通道转换;88个可编程的复⽤GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的⽚内扫描仿真接⼝(JTAG);TMS320F28335的存储器映射需注意以下⼏点:⽚上外设寄存器块0~3只能⽤于数据存储区,⽤户不能在该存储区内写⼊程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ST1:

全局中断屏蔽位-------INTM;(0-使能,1-中断屏蔽) 调试使能屏蔽位-------DBGM;(1-时间敏感代码内屏蔽调试) 寻址模式设置位------PAGE0;(0-C28x,1-C27x) 中断向量映射位-------VMAP;(0-低端,1-高端,默认) 堆栈指针定位位--------SPA;(0-未操作,1-已偶定位操作) 循环指令状态位-------LOOP;(0-循环结束,1-循环进行) 仿真及保护寄存器允许位-EALLOW;(1-仿真及保护寄存器允许) 空闲状态位-------IDLESTAT;(0-常态,1-低功耗状态) 寻址模式位----------AMODE;(0-C28x,C27x,1-C2xLP) 目标兼容模式位----OBJMODE;(0-C27x,1-C28x,要修改) M0和M1映射模式位--M0M1MAP;(0-TI测试,1-用户) XF状态位---------------XF;(0-XF引脚的状态,汇编指令) 辅助寄存器指针--------ARP;(000-确定当前辅助寄存器)

存储器

程序地址总线 PAB (22) 程序读数据总线 PRDB(32) 数据读地址总线 DRAB (32) 数据读数据总线 DRDB (32)

程序空间

(4M* 16)

数据空间

(4G * 16)

寄存器组

ARAU SP DP XAR0 XAR7 @X XT MPY32x32 P FPU R0H R7H

数据读总线

例:ASR AX,T ;T中低4位是移位位数 ASRL ACC,T;T中低5位是移位位数

12

2、乘积寄存器--P

乘法的结果

存放16位或32位数据; P的输出要经移位器,移位值由PM(ST0中)决定:

PM值

000

移位模式

左移1位

PM值 移位模式

100 右移3位

001

010 011

不移

右移1位 右移2位

101

110 111

13

右移4位

右移5位 右移6位

3、累加器--ACC

传送,算数,逻辑,比较,乘法运算结果 分拆为:16位和8位

14

与累加器相关的状态位:

符号扩展模式位------------SXM; 溢出模式位----------------OVM; 测试/控制标志位------------TC; 进位位----------------------C; 零标志位--------------------Z; 负标志位--------------------N; 溢出标志位------------------V; 溢出计数器位(6个位)--OVC/OVCU。

2017/3/1 Wednesday

ALU (32)

32

ACC (32)

AH (16) AL (16)

AH.MSB AH.LSB AL.MSB AL.LSB

32

Shift R/L (0-16) 数据总线

9

自寄存器

32

三、F28335的ARAU

Data Bus

XAR0 XAR1 XAR2 XAR3 XAR4 XAR5 XAR6 XAR7 ARAU ARAU Data Memory DP DP(16) (16)

寄存器总线

(96个中断)

PIE

McBSP 88*GPIO

Data Bus(数据总线)

2017/3/1 Wednesday 4

Program Bus(程序总线)

ePWM

DMA

6 CH.

一、F28335的基本组成(续)

XINTF

Sectored Flash

(256KW)

SARAM

(34KW)

BootROM

Shift R/L (0-16)

32 32 32

2、ACC

•AH:AH.MSB,AH.LSB •AL:AL.MSB,AL.LSB

32 x 32 or Dual 16 x 16 P (32) or PH/PL

32

8/16/32

Shift R/L (0-16)

8/16

32

3、Shift(桶型)

•输入ALU前的移位 •对P输出的移位 •对ACC输出的移位 •对寄存器内容移位

2017/3/1 Wednesday

7

一、F28335的乘法器

程序总线

32

数据总线

16 32

XT (32) or T/TL

16/32

1、32位乘法

•经XT(32)×另一个32位数 •积, P(高32位或低32位)

8/16/32 32

MULTIPLIER

Shift R/L (0-16)

32 32 32

32 x 32 or Dual 16 x 16 P (32) or PH/PL

32

Shift R/L (0-16)

8/16

2、双16位乘法-DMAC

•经XT(32)×另一个32位数

•积,ACC(高位字积):P(低位字积)

ALU (32)

32

ACC (32)

AH (16) AL (16)

AH.MSB AH.LSB AL.MSB AL.LSB

22位,指向当前操作指令(到达D2阶段)地址

到达D2阶段的指令不会被中断(要执行完)

19

8、返回程序计数器--RPC

22位,存放长调用的返回地址。 用指令LCR完成长调用时,RPC中的原来的内 容被压入堆栈,返回地址会装载到RPC中; 用指令LRETR实现返回时,RPC中的内容会被 传送到PC中,先前压入堆栈的内容会被弹出到 RPC中。

LCR和LRETR比另一对指令LC和LRET速度快。

20

9、中断控制寄存器--IFR、IER、DBGIER

3个寄存器的相应位定义是对应的: IFR相应位=1时,有对应的中断请求; IER相应位=1时,对应的中断使能; DBGIER用于实时仿真模式(以支持时间紧急中断)。

21

指令操作使用或影响的控制位或标志位

Atomic ALU

(R-M-W)

乘法器

(32x32 bit)

辅助 寄存器组 (32 bit)

FPU

时钟管理 Watchdog 定时器*3

实时JTAG 仿真逻辑

CPU

寄存器总线

(96个中断)

PIE

McBSP 88*GPIO

Data Bus(数据总线)

4、片上外设

•ePWM/eCAP/eQEP •ADC(12位*16路) •eCAN(2) •I2C(1) •SCI(3) •SPI(1) •McBSP(2) •GPIO(88)

(8KW)

OTPROM

(1KW)

eCAP eQEP

存储器

A(19-0)

DMA总线

12- bit ADC

片上外设

1、存储器 •Flash,256KW(8*32KW) •SARAM,34KW •Boot ROM,8KW •OPT存储器,1KW

D(31-0)

系统控制

CAN2.0B I 2C SCI SPI

Program Bus

ARAU

1、DP-直接寻址

•DP中为页号 •6位页内偏移量

32

MUX

22

6 LSB from IR

MUX

XARn 32- bits ARn 16- bits

2、XARx-寄存器间址

2017/3/1 Wednesday

10

四、F28335的CPU寄存器

C28x寄存器组

16bit T PH AH AR0H AR1H AR2H AR3H AR4H AR5H AR6H AR7H 16bit TL PL AL AR0 AR1 AR2 AR3 AR4 AR5 AR6 AR7 16bit IER IFR DBGIER ST0 ST1 SP DP 22bit PC RPC

数据/程序写总线

•DPWDB •DWAB

•DRAB •DRDB

ALU

ACC

执行单元

数据/程序写数据总线 DWDB (32) 数据写地址总线 DWAB (32)

~

片上外设 外部接口

(二)、F28335的CPU

一、F28335的乘法器 二、F28335的ALU 三、F28335的ARAU 四、35的CPU寄存器

16

5、数据页指针--DP

每页64个字

17

6、辅助寄存器--XAR0~XAR7

8个:

操作数地址指针; 32位通用寄存器; 16位通用寄存器(AR0~AR7),可作循环控制。

(注意:高16位可能受影响)

注意:高16位不能单独访问。

18

7、程序计数器--PC

F1: Instruction Address F2: Instruction Content D1: Decode Instruction D2: Resolve Operand Addr R1: Operand Address R2: Get Operand E: CPU doing “real” work W: store content to memory

6bit

FPU寄存器组

32bit R0H R1H R2H R3H R4H R5H R6H R7H STF RB

XT P ACC XAR0 XAR1 XAR2 XAR3 XAR4 XAR5 XAR6 XAR7

11

1、被乘数寄存器--XT

XT,被乘数(32位) T , 被乘数(16位)或移位位数

TL , 存16位有符号整数,可符号自动扩展

2、CPU 3、系统控制 •ALU,R-M-W:atomic •时钟管理 •Watchdog •乘法器 •定时器*3个 •AR及ARAU •PIE(仅用45) •DMA及JTAG •FPU及控制器