用vhdl设计D触发器知识讲解

d触发器输出方程

D 触发器是数字电路中的一种时序逻辑电路,其输出取决于输入和时钟信号。

D 触发器的输出方程可以根据其工作原理和逻辑表达式来确定。

D 触发器的工作原理是在时钟信号的边沿上更新输出。

当时钟信号处于上升沿(rising edge)或下降沿(falling edge)时,根据输入D 的值来更新输出。

具体输出的更新方式取决于是D 触发器采用的是正极性触发(positive edge-triggered)还是负极性触发(negative edge-triggered)。

以正极性触发的D 触发器为例,其输出方程可以表示为:

Q(t+1) = D

其中Q(t+1) 表示输出在时钟的下一个时刻的值,D 表示输入。

这个输出方程假设D 触发器没有时钟延迟或噪声等因素的影响,并且是理想的情况。

在实际应用中,还需要考虑电路的延迟、时序设计等因素。

所以具体的D 触发器输出方程可能会因电路实现的细节而有所不同。

总结使用触发器、移位寄存器设计时序逻辑电路和方法。

总结使用触发器、移位寄存器设计时序逻辑电路和方法。

在数字电路设计中,时序逻辑电路是指需要考虑时间因素的电路,其输出取决于当前和之前的输入信号。

触发器和移位寄存器是时序逻辑电路中常用的组件,它们可以被用来存储信息和同步信号,从而帮助我们构建更加复杂的电路。

触发器是一种时序逻辑电路,它可以存储一个比特位,并且只能被时钟信号触发来改变存储状态。

触发器的最常见类型是D触发器,它有一个数据输入(D)和时钟输入(C),当C的上升沿到来时,D触发器会将D的数据存入内部寄存器中。

移位寄存器是一种特殊的触发器组合,其可以在多个触发器之间进行移位操作。

移位寄存器通常用于存储多个比特位,并且可以用于串行通信和数字信号处理等应用中。

当时钟信号触发时,移位寄存器会将每个触发器的输出传递给下一个触发器,从而实现数据的移位操作。

时序逻辑电路的设计需要考虑各种电路的延迟和时序关系,以确保电路的正确功能。

此外,还需要注意电路中的时钟频率,以确保电路能够快速响应输入信号并进行适当的处理。

在实际的电路设计中,我们可以使用Verilog或VHDL等硬件描述语

言来描述时序逻辑电路和组件,从而可以通过模拟和仿真来验证电路

的正确性。

同时,我们还可以使用EDA工具来帮助我们自动化设计流程,从而提高设计效率和准确性。

总之,触发器和移位寄存器是时序逻辑电路中非常重要的组件,它们可以帮助我们存储和处理数字信号,并构建更加复杂的数字电路。

在电路设计过程中,我们需要注意各种时序关系和延迟,并使用适当的硬件描述语言和EDA工具来实现设计目标。

VHDL语言实现数字电路设计

VHDL语言实现数字电路设计数字电路是由逻辑门、寄存器以及其他数字组件组成的电子系统,用于处理和传输数字信号。

VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统。

通过使用VHDL语言,我们可以实现数字电路的设计,从而满足各种需求。

VHDL语言提供了一种结构化的设计方法,允许设计者描述硬件电路的结构、功能以及时序行为。

以下是一些常见的数字电路设计任务,以及如何使用VHDL语言来实现它们。

1. 门电路设计门电路是最简单的数字电路之一,由逻辑门组成。

使用VHDL语言,我们可以通过描述逻辑门的输入和输出来实现门电路的设计。

例如,我们可以使用VHDL语言描述一个与门:```vhdlentity AND_gate isport (A, B : in bit;Y : out bit);end entity AND_gate;architecture dataflow of AND_gate isbeginY <= A and B;end architecture dataflow;```在这个例子中,我们定义了一个输入端口A和B,以及一个输出端口Y。

在architecture部分,我们使用VHDL语言描述了Y的逻辑值为A和B的逻辑与。

2. 时序逻辑电路设计时序逻辑电路是根据时钟信号进行操作和状态转换的电路。

使用VHDL语言,我们可以描述时序逻辑电路的行为和状态变化。

例如,我们可以使用VHDL语言描述一个触发器:```vhdlentity D_flip_flop isport (D, CLK : in bit;Q : out bit);end entity D_flip_flop;architecture behavior of D_flip_flop issignal Q_temp : bit;beginprocess(CLK)beginif CLK'event and CLK = '1' thenQ_temp <= D;end if;end process;Q <= Q_temp;end architecture behavior;```在这个例子中,我们定义了一个输入端口D和CLK,以及一个输出端口Q。

[全]数字电路--D触发器

![[全]数字电路--D触发器](https://img.taocdn.com/s3/m/229f4a7add3383c4ba4cd2d7.png)

数字电路--D触发器

2.维持阻塞D触发器

工作原理:

1)CP = 0时,G3、G4被封锁,触发器维持原态不变。

2)CP的上升沿到来时:

①D = 0,则Q5 = 1,Q6= 0,Q3 = 0,Q4 = 1,触发器置“0”,Q = 0,

Q 非= 1;G3输出端到G5输入端的连线叫做“置0维持线”。

②D =1,则Q5 = 0,Q3 = 1,Q6= 1,Q4= 0,触发器置“1”,Q = 1,Q 非= 0;G4输出端到G6输入端的连线叫做“置1维持线”。

维持阻塞触发器不会有空翻现象

维持阻塞D触发器就是D触发器。

由于是上升沿触发,又称为边沿D触发器。

五、T触发器(受控翻转型触发器)

4.测试电路

(1)对照测试线路图和装配图进行检查,仔细检查电路中各电路是否安装正确,导线、焊点是否符合要求,检查有极性器件是否安装并连接正确。

(2)用万用表R×1挡测电源与地之间的电阻。

发现短路,应先检查,排除短路点。

(3)检查无误后,按集成电路标记口的方向插上集成电路,方可通电测试。

第4章_VHDL设计初步1

4.2.2 D触发器VHDL描述的语言现象说明

4. 上升沿检测表式和信号属性函数EVENT

关键词EVENT是信号属性,VHDL通过以下表式来测定 某信号的跳变边沿: <信号名>'EVENT

4.2.2 D触发器VHDL描述的语言现象说明

5. 不完整条件语句与时序电路

【例4-11】 ENTITY COMP_BAD IS PORT( a1 : IN BIT; b1 : IN BIT; q1 : OUT BIT ); END ; ARCHITECTURE one OF COMP_BAD IS BEGIN PROCESS (a1,b1) BEGIN IF a1 > b1 THEN q1 <= '1' ; ELSIF a1 < b1 THEN q1 <= '0' ;-- 未提及当a1=b1时,q1作何操作 END IF; END PROCESS ; END ;

第4章

本章内容

4.1 多路选择器VHDL描述(简单组合电 路) 4.2 寄存器描述及其VHDL语言现象(简 单时序电路) 4.3 1为二进制全加器的VHDL设计(实例) 4.4 VHDL文本输入设计方法(工具使用, 通过上机操作掌握)

本章重点掌握内容

1、实体及端口的定义。 2、结构体和信号的定义。 3、基本逻辑操作符和信号赋值操作符。 4、IF-THEN-ELSE(顺序)、WHEN-ELSE (并行)语句。 5、进程语句。 6、信号的上升沿表示方法。 7、元件例化方法。

是什么是VHDL?

Very high speed integrated Hardware Description Language (VHDL)

是IEEE、工业标准硬件描述语言 用语言的方式而非图形等方式描述硬件电路

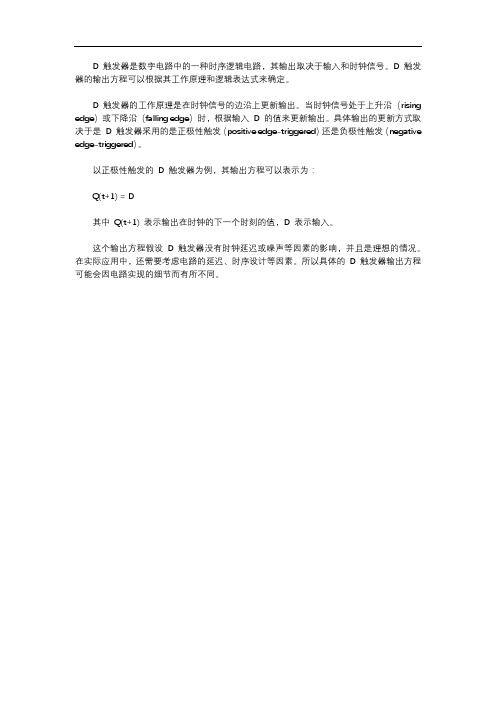

时序逻辑VHDL设计---触发器

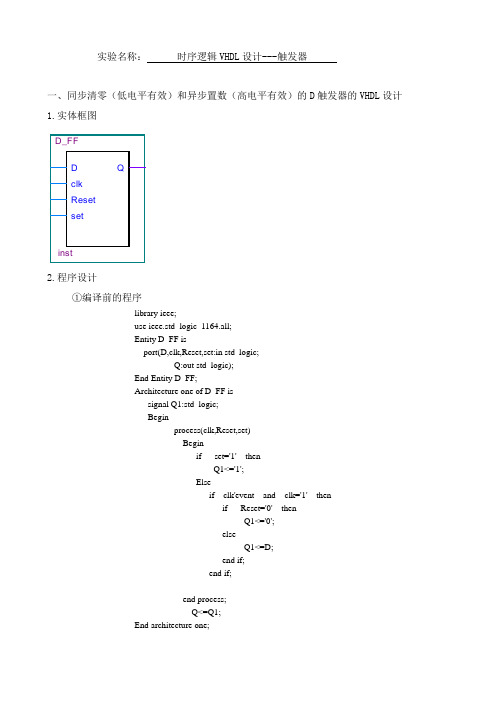

实验名称:时序逻辑VHDL设计---触发器一、同步清零(低电平有效)和异步置数(高电平有效)的D触发器的VHDL设计1.实体框图Dclk Reset set QD_FFinst2.程序设计①编译前的程序library ieee;use ieee.std_logic_1164.all;Entity D_FF isport(D,clk,Reset,set:in std_logic;Q:out std_logic);End Entity D_FF;Architecture one of D_FF issignal Q1:std_logic;Beginprocess(clk,Reset,set)Beginif set='1' thenQ1<='1';Elseif clk'event and clk='1' thenif Reset='0' thenQ1<='0';elseQ1<=D;end if;end if;end process;Q<=Q1;End architecture one;②程序编译错误情况错误1:Error (10500): VHDL syntax error at D_FF.vhd(22) near text "process"; expecting "if"错误2:Error (10500): VHDL syntax error at D_FF.vhd(24) near text "architecture"; expecting "if"分析:经检查,发现原程序少了END if,没有与if匹配,添加即可。

③正确的程序library ieee;use ieee.std_logic_1164.all;Entity D_FF isport(D,clk,Reset,set:in std_logic;Q:out std_logic);End Entity D_FF;Architecture one of D_FF issignal Q1:std_logic;Beginprocess(clk,Reset,set)Beginif set='1' thenQ1<='1';Elseif clk'event and clk='1' thenif Reset='0' thenQ1<='0';elseQ1<=D;end if;end if;end if;end process;Q<=Q1;End architecture one;3.仿真波形图4.仿真波形分析当置数端SET出现高电平时,此时不管CP脉冲和D的状态如何,输出立即置为‘1’,实现异步置数的功能;当清零端RESET出现低电平时,而且必须当CP脉冲为上升沿时,输出清零,实现同步清零;除此之外,当CP脉冲为上升沿状态时,D=0,Q=0;D=1,Q=1;二、异步清零(高电平有效)和同步置数(低电平有效)的JK触发器的VHDL设计1.实体框图clk reset setJK[0..1]QJK_FFinst2.程序设计①编译前的程序Library ieee;use ieee.std_logic_1164.all;Entity JK_FF isport( clk,reset,set,J,K:in std_logic;Q:out std_logic);End entity JK_FF;Architecture two of JK_FF issignal Q1:std_logic;beginprocess(clk,reset,set,J,K)beginif reset='1' thenQ1<='0';elseif clk'event and clk='1' thenif set='0' thenQ1<='1';elsecase JK iswhen "00" => Q1<=Q1;when "10" => Q1<='1';when "11" => Q1<=not Q1;when others =>NULL;end case;end if;end if;end if;end process;Q<=Q1;end architecture two;②程序编译错误情况错误1:Error (10482): VHDL error at JK-FF.vhd(19): object "JK" is used but not declared错误2:Error (10523): Ignored construct two at JK-FF.vhd(7) due to previous errors分析:JK为两位,需要定义如下:JK:in std_logic_vector(0 to 1);③正确的程序Library ieee;use ieee.std_logic_1164.all;Entity JK_FF isport( clk,reset,set:in std_logic;JK:in std_logic_vector(0 to 1);Q:out std_logic);End entity JK_FF;Architecture two of JK_FF issignal Q1:std_logic;beginprocess(clk,reset,set,JK)beginif reset='1' thenQ1<='0';elseif clk'event and clk='1' thenif set='0' thenQ1<='1';elsecase JK iswhen "00" => Q1<=Q1;when "01" => Q1<='0';when "10" => Q1<='1';when "11" => Q1<=not Q1;end case;end if;end if;end if;end process;Q<=Q1;end architecture two;3.仿真波形图4.仿真波形分析当清零端ResET出现高电平时,此时不管CP脉冲和JK的状态如何,输出立即清零,实现异步清零的功能;当置数端SET出现低电平时,而且必须当CP脉冲为上升沿时,输出立即置数‘1‘,实现同步置数的功能;除此之外,当CP脉冲为上升沿状态时,J=K=0,Q保持;J=0,K=1,Q置零;J=1,K=0,Q置1;J=K=1,Q翻转一、8位锁存器的VHDL设计1.实体框图D[0..7] clk Q[0..7]latch8a2.程序设计①编译前的程序Library ieee;use ieee.std_logic_1164.all;Entity latch8a isport(D:in std_logic_vector(7 to 0);clk:in std_logic;Q:out std_logic_vector(7 to 0));End latch8a;Architecture three of latch8a issignal q1:std_logic_vector(7 to 0);beginprocess (clk,D)beginif clk'event and clk='1' thenQ1<=D;end if;end process;Q<=Q1;End architecture three;②程序编译错误情况错误:无③正确的程序Library ieee;use ieee.std_logic_1164.all;Entity latch8a isport(D:in std_logic_vector(0 to 7);clk:in std_logic;Q:out std_logic_vector(0 to 7));End latch8a;Architecture three of latch8a issignal q1:std_logic_vector(0 to 7);beginprocess (clk,D)beginif clk'event and clk='1' thenend if;end process;Q<=Q1;End architecture three;3.仿真波形图4.仿真波形分析当CLK脉冲为高电平时,输出为与其相对应的输出。

VHDL时序电路的D触发器

D触发器的VHDL描 述

最简单,最常用,最具 代表性的时序原件是D触 发器,它是现代数字系 统设计中最基本的底层 时序单元,甚至是ASIC 设计的基本单元。JK和T 触发器都可由它构建而 来。D触发器的描述包含 了VHDL对时序电路的最 基本和典型的表达方式, 同时也包含了VHD为上升沿的时候,Q输 出D的值;否则,Q保持原值不变

• 设计清0,置数信号的D触发 器 • D触发器由输入的时钟信号 (CLK)、数据输入口(D) 和数据输出(Q)构成。本程 序通过进程监视CLK和D\,当 CLK为上升沿的时候,将D赋 值给Q,要完成这个赋值操作, 必须再借助一个信号S来进行 值的传递

程序

library ieee; use ieee.std_logic_1164.all; entity dff1 is port(clk,d,clr,reset:in std_logic; q:out std_logic); end dff1; architecture exx of dff1 is begin process(clk,clr,reset) begin if (clr='1') then q<='0'; elsif( clk'event and clk='1')then if( reset='0') then q<='1'; else q<=d; end if; end if; end process; end exx

第4章 VHDL设计初步

结构体有三种描述方式 *行为描述(behavioral):

高层次的功能描述,不必考虑在电路中到底是怎样实现的。

*数据流描述(dataflow):

描述输入信号经过怎样的变换得到输出信号

*结构化描述(structural):

【例4-2】-1 2选1多路选择器 ENTITY mux21a IS PORT ( a, b : IN BIT; s : IN BIT; y : OUT BIT ); END ENTITY mux21a;

功能:s = 0

s=1

y=a y =b

ARCHITECTURE one OF mux21a IS BEGIN 并行语句 y <= (a AND (NOT s)) OR (b AND s) ; END ARCHITECTURE one;

端口模式:

IN、OUT、INOUT、BUFFER描述端口数据的流向特征。

数据类型: 数据对象承载数据的类别:BIT的定义值为逻辑'1'和'0'。

信号赋值符: “<=”,用于信号数据的传输,仿真传输延时最短为一个。

条件比较符:

“=”,在条件语句表式中用于比较待测数据的关系。

延时: 模拟器最小分辨时间,或称延时 。

port:

*在层次化设计时,Port为模块之间的接口 *在芯片级,则代表具体芯片的管脚

数据通道输入端口

数据输出端

通道选择控制信号端

图4-1 mux21a实体

(2) 以关键词ARCHITECTURE引导,END ARCHITECTURE … 结尾的语句部分,称为结构体。 功能:通过若干顺序语句和并行语句来描述设计实体的逻辑功能(行为描述)