电子科技大学数字电路期末考试样题

数字电路2011期末考试题-参考解答

电子科技大学2010 -2011学年第二学期期末考试 A 卷课程名称:_数字逻辑设计及应用__ 考试形式:闭卷考试日期:20 11 年7 月7 日考试时长:_120___分钟课程成绩构成:平时30 %,期中30 %,实验0 %,期末40 %本试卷试题由__六___部分构成,共__6___页。

I. Fill your answers in the blanks(2’ X 10=20’)1. A parity circuit with N inputs need N-1XOR gate s. If the number of “1” in an N logic variables set, such as A、B、C、…W, is even number, then__________A B C W⊕⊕⊕⋅⋅⋅⋅⊕=0 .2. A circuit with 4 flip-flops can store 4bit binary numbers, that is, include 16 states at most.3. A modulo-20 counter circuit needs 5 D filp-flops at least. A modulo-288 counter circuit needs 3 4-bit counters of 74x163 at least.4. A 8-bit ring counter has 8 normal states. If we want to realize the same number normal states, we need a 4bit twisted-ring counter.5. If the input is 10000000 of an 8 bit DAC, the corresponding output is 5v. Then an input is 00000001 to the DAC, the corresponding output is 5/128 (0.0391) V; if an input is 10001000, the corresponding DAC output is 5.3125V.II. Please select the only one correct answer in the following questions.(2’ X 5=10)B ) chips of 4K ⨯4 bits RAM to form a 16 K ⨯ 8 bits RAM.A) 2 B) 8 C) 4 D) 162. To design a "01101100" serial sequence generator by shift registers, we need a( A)-bit shift register as least.A) 5 B) 4 C) 3 D) 63. For the following latches or flip-flops, ( B) can be used to form shift register.A) S-R latch B) master-slave flip-flop C) S-R latch with enable D) S’-R’ latch4. Which of the following statements is correct? ( C )A) The outputs of a Moore machine depend on inputs as well as the states.B) The outputs of a Mealy machine depend only on the states.C) The outputs of a Mealy machine depend on inputs as well as the states. D) A), B), C) are wrong.5. There is a state/output table of a sequential machine as the table 1, what the input sequences isdetected? ( D )A) 11110 B) 11010 C) 10010 D) 10110Table 1III.Analyze the sequential-circuit as shown in figure 1. [15’]1. Write out the excitation equations, transitionequations and output equation. [5’]2. Assume the initial state is Q 2Q 1=00, complete thetiming diagram for Q 2 ,Q 1 and Z.( Don ’t need consider propagation delay of each component)[10’]Figure-1解答:激励方程: D 1=Q 1⊕Q 2,D 2= Q /1+ Q /2转移方程:Q 1 *= D 1=Q 1⊕Q 2,Q 2 *=D 2= Q /1+ Q /2 输出方程:Z= Q 1•Q 2IV. Design a Mealy sequential detector with one input x and one output z. If and only if xdescribe the state meaning and finish the state/output table. [15] Example : x :0 1 0 1 1 1 1 0 0 1 1 0 0 1 1 1 1 1 z :0 0 0 0 0 0 1 0 0 1 0 0 0 1 0 0 1 1XState meaningS 0 1 Initial A A,0 B,0 Received 1 B C,0 D,0 Received 10 C E,0 B,0 Received 11 D C,0 F,0 Received 100 E A,0 B,1 Received 111 F C,0F,1S*,ZV. Analyze the circuit as shown below, which contains a 74x163 4-bit binary counter, a 74x138[15’] ’ output F. [5’]2. Write out the sequence of states for the 74x161 in the circuit. [7’]3. Describe the modulus(模) of the circuit. [3’]解答:F=D2=Y6/=(QDQCQBQA /)/ 状态序列:0,1,2,3,4,5,6,7,8,9,10,11,12,13,14,0,1,2,… M=15VI.the state transition sequence is 0→2→4→1→3→0→…with the binary code. 1. Fill out the transition/output table. [8’]2. Write out the excitation equations and output equation. [4’]3. List the complete transition/output table, and check the self-correct. [3’] transition/output table : 74X161的功能表输入 当前状态 下一状态 输出CLR_L LD_L ENT ENP QD QC QB QA QD* QC* QB* QA* RCO 0 X X X X X X X 0 0 0 0 1 0 X X X X X X D C B A 1 1 0 X X X X X QD QC QB QA 1 1 X 0 X X X X QD QC QB QA 1 1 1 1 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 1 0 0 1 0 1 1 1 1 0 0 1 0 0 0 1 1 1 1 1 1 0 0 1 1 0 1 0 0complete transition/output table:输出方程:Z=Q1Q0检查自启动:当Q2Q1Q0=101,可得下一状态为001;当Q2Q1Q0=110,可得下一状态为101;当Q2Q1Q0=111,可得下一状态为001。

电子科大模电期末真题10~11.doc

电子科大模电期末真题10~11学院___________________ 系别____________ 班次_____________ 学号__________ 姓名________________………….……密…..……….封……..……线………..…以………..…内………....答…………...题…………..无…….….效…..………………..电子科技大学二零一零至二零一一学年第 1 学期期末考试模拟电路基础课程考试题A卷(120 分钟)考试形式:开卷考试日期2011年1 月 5 日课程成绩构成:平时20 分,期中20 分,实验0 分,期末60 分一二三四五六七八九十合计复核人签名得分签名一、填空题(共30分,共 15个空格,每个空格2 分)1、共发射极放大器(NPN管),若静态工作点设置偏高,可能产生_饱和__失真,此时集电极电流会出现__上___(上、下)削峰失真。

2、某晶体管的极限参数P CM = 200 mW,I CM = 100 mA,U(BR)CEO = 30 V,若它的工作电压U CE为10 V,则工作电流不得超过20 mA;若工作电流I C = 1 mA,则工作电压不得超过30 V。

4、电路及直流测试结果如图1所示,分别指出它们工作在下列三个区中的哪一个区(恒流区、夹断区、可变电阻区)。

得图1(a) 恒流区 ; (b) 可变电阻区 。

5、由三端集成稳压器构成的直流稳压电路如图2所示。

已知W7805的输出电压为5V ,I Q =10 mA ,晶体管的β=50,|U BE |=0.7 V ,电路的输入电压U I =16 V ,三极管处于放大 (放大,饱和,截止)状态, R 1上的电压为 5.7 V ,输出电压U o 为 9 V 。

图26、设图3中A 均为理想运放,请求出各电路的输出电压值。

U 01= 6 V; U 02= 6 V; U 03= 4 V; U 04= 10 V; U 05= 2 V; U 06= 2 V 。

电子科大数字电路期末试题半期测验

电子科大数字电路期末试题半期测验————————————————————————————————作者:————————————————————————————————日期:电子科技大学二零零七至二零零八学年第二学期期中考试“数字逻辑设计及应用”课程考试题 期中卷(120分钟)考试形式:闭卷 考试日期 2008年4月26日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末60 分一 二 三 四 五 六 七 八 九 十 合计一、选择填空题(单选、每空2分,共30分)1-1.与十进制数 (0. 4375 )10 等值的二进制数表达是 ( A ) A. ( 0.0111 ) 2 B. ( 0.1001 ) 2 C. ( 0.0101 ) 2 D. ( 0.01101 ) 2 1-2. 与十六进制数(FD .A )16等值的八进制数是( A )8A. ( 375.5 )8B. ( 375.6 )8C. ( 275.5 )8D. ( 365.5)8 1-3.与二进制数(11010011) 2 对应的格雷码表达是 ( C ) GrayA. ( 11111010 ) GrayB. (00111010 ) GrayC. ( 10111010 )GrayD. (11111011 ) Gray 1-4.下列数字中与(34.42)8 相同 的是( B )A.(011010.100101)2B.(1C.88)16 C.(27.56)10D.(54.28)5 1-5.已知[A]补=(10010011),下列表达式中正确的是( C )A. [–A]反=(01101100)B. [A]反=(10010100)C. [-A]原=(01101101)D. [A]原=(00010011)1-6.一个十六路数据选择器,其选择控制输入端的数量为( A )A .4个 B. 6个 C. 8个 D. 3个1-7.四个逻辑相邻的最小项合并,可以消去( B )个因子。

数字电路期末考试题及答案

数字电路期末考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,最基本的逻辑关系是:A. 与逻辑(AND)B. 或逻辑(OR)C. 非逻辑(NOT)D. 异或逻辑(XOR)答案:C2. 下列哪个不是数字电路的特点?A. 精确度高B. 稳定性好C. 功耗大D. 抗干扰能力强答案:C3. 一个简单的触发器可以存储多少位二进制信息?A. 1位B. 2位C. 3位D. 4位答案:A4. 以下哪个是组合逻辑电路的特点?A. 有记忆功能B. 无记忆功能C. 可以进行算术运算D. 可以进行逻辑运算答案:B5. 在数字电路中,同步计数器与异步计数器的主要区别是:A. 同步计数器速度更快B. 同步计数器结构更复杂C. 同步计数器计数更准确D. 异步计数器计数更准确答案:A6. 一个4位二进制计数器最多能计数到:A. 15B. 16C. 8D. 4答案:B7. 以下哪个是数字电路中常用的存储元件?A. 电阻B. 电容C. 电感D. 晶体管答案:D8. 以下哪个不是数字电路中的逻辑门?A. NANDB. NORC. XORD. TRIAC答案:D9. 一个完整的数字电路设计流程包括以下哪些步骤?A. 需求分析B. 电路设计C. 仿真测试D. 所有选项答案:D10. 以下哪个是数字电路中的时序逻辑电路?A. 门电路B. 触发器C. 运算放大器D. 模数转换器答案:B二、简答题(每题5分,共20分)1. 简述数字电路与模拟电路的区别。

答案:数字电路主要处理离散的数字信号,具有逻辑功能,而模拟电路处理连续的模拟信号,主要用于信号放大、滤波等。

2. 解释什么是触发器,并说明其在数字电路中的作用。

答案:触发器是一种具有记忆功能的逻辑电路,能够存储一位二进制信息。

在数字电路中,触发器用于存储数据,实现计数、定时等功能。

3. 什么是组合逻辑电路?请举例说明。

答案:组合逻辑电路是由逻辑门组成的电路,其输出只依赖于当前的输入状态,不具有记忆功能。

电子科大数字电路,期末试题101102半期考试试卷-答案

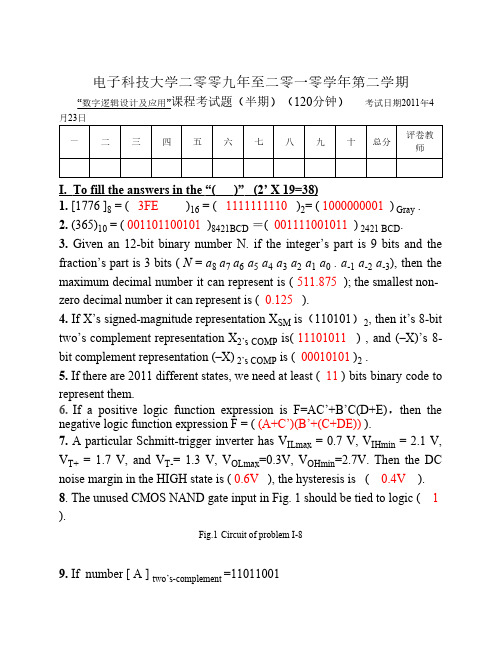

电子科技大学二零零九年至二零一零学年第二学期“数字逻辑设计及应用”课程考试题(半期)(120分钟)考试日期2011年4月23日一二三四五六七八九十总分评卷教师I. To fill the answers in the “( )” (2’ X 19=38)1. [1776 ]8 = ( 3FE )16 = ( 1111111110 )2= ( 1000000001 ) Gray .2. (365)10 = ( 001101100101 )8421BCD=( 001111001011 ) 2421 BCD.3.Given an 12-bit binary number N. if the integer’s part is 9 bits and the fraction’s part is 3 bits ( N = a8 a7 a6 a5 a4 a3 a2 a1 a0 . a-1 a-2 a-3), then the maximum decimal number it can represent is ( 511.875 ); the smallest non-zero decimal number it can represent is ( 0.125 ).4. If X’s signed-magnitude representation X SM is(110101)2, then it’s 8-bit two’s complement representation X2’s COMP is( 11101011 ) , and (–X)’s 8-bit complement representation (–X) 2’s COMP is ( 00010101 )2 .5. If there are 2011 different states, we need at least ( 11 ) bits binary code to represent them.6.If a positive logic function expression is F=AC’+B’C(D+E),then the negative logic function expression F = ( (A+C’)(B’+(C+DE)) ).7. A particular Schmitt-trigger inverter has V ILmax = 0.7 V, V IHmin = 2.1 V, V T+= 1.7 V, and V T-= 1.3 V, V OLmax=0.3V, V OHmin=2.7V. Then the DC noise margin in the HIGH state is ( 0.6V ), the hysteresis is ( 0.4V ). 8.The unused CMOS NAND gate input in Fig. 1 should be tied to logic ( 1 ).Fig.1Circuit of problem I-89. If number [ A ] two’s-complement =11011001and [ B] two’s-complement=10011101 , calculate[-A-B ]two’s-complement, [-A+B ]two’s-complement and indicate whether or not overflow occurs.[-A-B ] two’s-complement=[ 10001010 ], overflow: [ yes ][-A+B ] two’s-complement=[ 11000100 ], overflow: [ no ].10.The following logic diagram Fig.2 implements a function of 3-variable with a 74138. The logic function can be expressed as F (A,B,C) = ∑A,B,C ( 0,1,2 ).Fig.2 Circuit of problem I-10II. There is only one correct answer in the following questions.(3’ X 9 = 27)1. Which of the following Boolean equations is NOT correct? ( B )A) A+0=A B) A1 = AC) D)2. Suppose A2’s COMP =(1011),B2’s COMP =(1010),C2’s COMP =(0010). In the following equations, the most unlikely to produce overflow is( C )。

最新电子科大数字电路,期末试题-2006-1数电半期考试

电子科技大学二零零五至二零零六学年第二学期期中考试“数字逻辑设计及应用”课程考试题 期中卷(120分钟)考试形式:闭卷 考试日期 2006年4月22日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末60 分一、填空题(每空1分,共15分)1、( 323 )10 =( 101000011 ) 22、(0. 4375 )10 =( 0.0111 ) 23、(1101.0011) 2 = ( 13.1875 )104、(FD .A )16 = ( 11110000.1010 ) 2= ( 360.50 )85、( 4531 )10 = ( 0100 0101 0011 0001 ) 8421BCD 。

6、写出与下列十进制数对应的8-bit 原码(signed-magnitude),补码(two ’s-complement)和反码 (one ’s-complement)表达:7、已知二进制数 A = 10110100,对应的格雷码(GRAY CODE )表达为( 1110 1110 ) 8、与非逻辑门电路的未用输入端应接在( 高电平或某一个输入信号端 )上。

9、已知二进制数 A 的补码为:[A]补= 10110100,求 [-A]补=( 01001100 )二、填空题(每空3分,共30分)1、已知一个函数的积之和(与或式, The sum of productions )列表表达式为 F =∑ABC (1,4,5,6,7),问与其对应的最简积之和表达式为:F =( A + B ’C )。

2、对于按照逻辑式 F AC BC '=+ 实现的电路,存在静态( 1 )型冒险。

3、四变量逻辑函数F = ∑ABCD (2,4,5,7,9,14)的反函数 F ’=∏ABCD ( 2,4,5,7,9,14 )。

4、已知带符号的二进制数 X1 = +1110 ,X2 = -1011,求以下的表达,并要求字长为8位。

2020秋西安电子科技大学《数字逻辑电路》大作业期末试题及答案

学习中心/函授站_姓名学号西安电子科技大学网络与继续教育学院2020 学年下学期《数字逻辑电路》期末考试试题(综合大作业)题号一二三四总分题分30 10 30 30得分考试说明:1、大作业试题于2020 年10 月15 日公布:(1)毕业班学生于2020 年10 月15 日至2020 年11 月1 日在线上传大作业答卷;(2)非毕业班学生于2020 年10 月22 日至2020 年11 月8 日在线上传大作业答卷;(3)上传时一张图片对应一张A4 纸答题纸,要求拍照清晰、上传完整;2、考试必须独立完成,如发现抄袭、雷同均按零分计;3、答案须用《西安电子科技大学网络与继续教育学院标准答题纸》手写完成,要求字迹工整、卷面干净。

一、单项选择题(每小题2 分,共40 分)1、下列各数中与十进制数101 不相等的数是( D )。

A.(0100 0011 0100)余3BCD B.(141)8C.(1100101)2D.(66)162、八进制数(35)8的8421BCD 是( B )。

A.0011 1000B.0010 1001C.0011 0101D.0010 11003、为使与非门输出为1 则输入( A )。

A.只要有0 即可B.必须全为0C.必须全为1D.只要有1 即可4、函数F AC BC AB与其相等的表达式是( B )。

A.BC B.C+AB C.AC AB D.AB5、使函数F AB AC BC 等于 0 的输入 ABC 的组合是( C )。

A .ABC=111 B .ABC=110 C .ABC=100 D .ABC=0116、四变量的最小项ABCD 的逻辑相邻项是( A )。

A .ABCDB .ABCDC .ABCD D .ABCD 7、函数 F ABC B .C (A D )BC 的对偶式是( C )。

A .G (A B C )(B C )(AD B C )B .G A BC (B C )ADB CC .G A B C (B C )(AD B C )D .G A BC (B C )AD B C8、FA B C ADE BDE ABC 的最简式为( A )。

电子科技大学年数字电路试题

电子科技大学 2004年攻读工程硕士专业学位研究生入学试题 考试科目:数字电路 注意事项: 所有答案必须写在答题纸上,否则答案无效。

一、单项选择题(20分,每小题2分)1.(25.1)10的二进制数是( )。

A. 10011.0001B. 11001.0001C. 10011.1000D. 10011.10002.11101的补码是( )。

A. 00011B. 00010C. 10011D. 100103.正逻辑的“或”门在负逻辑中是( )门。

A. 或门B. 与门C. 或非门D. 与非门4.若输入变量A ,B 全为1时,输出F=0,则其输出与输入的关系是( )。

A. 异或B. 同或 C .与非 D. 或非5.已知F=BD ABC +,选出下列( )可以肯定使F=0的情况:A. A=0,BC=1B. B=1,C=1C. C=1,D=0D. BC=1,D=16.n 变量的最小项应有( )个。

A. nB. 2n C .n 2 D. 2n7.逻辑函数)(C A B A F +=的对偶函数'F 是 ( )。

A.)('C A B A F ++=B. )('C A B A F ++=C. )('C A B A F ++=D. )('C A B A F +=8.时序逻辑电路中一定包含( )。

A. 触发器B. 组合逻辑电路C. 移位寄存器D. 存储器 9.如右图所示逻辑电路的逻辑关系是( )。

A. A B B A F +=B. ))((B A B A F ++=C. B A AB F +=D.))((B A B A F ++= 10.))((C AB A F ++=,当B=0,且( )时,电路存在竞争-冒险。

A. 0=A B. 1=A C. 0=C D.1=C二、化简(10分,每小题5分)1. 用公式法化简下列逻辑函数为F 积之和式。

C AB C B BC A AC F ++=+2. 用卡若图法化简)15,11,7,5,3,1()13,9,6,4,0(),,,d m D C B A F ∑+∑=(为最简与或式。

电子科大数字电路_期末试题0708_2半期考试

电子科技大学二零零七至二零零八学年第二学期期中考试“数字逻辑设计及应用”课程考试题 期中卷(120分钟)考试形式:闭卷 考试日期 2008年4月26日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末60 分1-1.与十进制数 (0. 4375 )10 等值的二进制数表达是 ( A )A. ( 0.0111 ) 2B. ( 0.1001 ) 2C. ( 0.0101 ) 2D. ( 0.01101 ) 2 1-2. 与十六进制数(FD .A )16等值的八进制数是( A )8A. ( 375.5 )8B. ( 375.6 )8C. ( 275.5 )8D. ( 365.5)8 1-3.与二进制数(11010011) 2 对应的格雷码表达是 ( C ) GrayA. ( 11111010 ) GrayB. (00111010 ) GrayC. ( 10111010 )GrayD. (11111011 ) Gray 1-4.下列数字中与(34.42)8 相同 的是( B )A.(011010.100101)2B.(1C.88)16 C.(27.56)10D.(54.28)5 1-5.已知[A]补=(10010011),下列表达式中正确的是( C )A. [–A]反=(01101100)B. [A]反=(10010100)C. [-A]原=(01101101)D. [A]原=(00010011)1-6.一个十六路数据选择器,其选择控制输入端的数量为( A )A .4个 B. 6个 C. 8个 D. 3个1-7.四个逻辑相邻的最小项合并,可以消去( B )个因子。

A. ( 1 )B. ( 2 )C. ( 3 )D.( 4 )1-8.设A 补=(1001),B 补=(1110),C 补=(0010),在下列4种补码符号数的运算中,最不可能产生溢出的是 ( D )A. [A-C]补B. [B-C]补C. [A+B]补D. [B+C]补 1-9.能够实现“线与”的CMOS 门电路叫( D )A. ( 与门 )B. ( 或门 )C. (集电极开路门)D. (漏极开路门) 1-10.CMOS 三输入或非门的实现需要( C )个晶体管。

电子科大数字电路,期末试题0708-2半期考试

………密………封………线………以………内………答………题………无………效……电子科技大学二零零七至二零零八学年第二学期期中考试“数字逻辑设计及应用”课程考试题 期中卷(120分钟)考试形式:闭卷 考试日期 2008年4月26日课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末60 分1-1.与十进制数 (0. 4375 )10 等值的二进制数表达是 ( A ) A. ( 0.0111 ) 2 B. ( 0.1001 ) 2 C. ( 0.0101 ) 2 D. ( 0.01101 ) 2 1-2. 与十六进制数(FD .A )16等值的八进制数是( A )8A. ( 375.5 )8B. ( 375.6 )8C. ( 275.5 )8D. ( 365.5)8 1-3.与二进制数(11010011) 2 对应的格雷码表达是 ( C ) GrayA. ( 11111010 ) GrayB. (00111010 ) GrayC. ( 10111010 )GrayD. (11111011 ) Gray 1-4.下列数字中与(34.42)8 相同 的是( B )A.(011010.100101)2B.(1C.88)16 C.(27.56)10D.(54.28)5 1-5.已知[A]补=(10010011),下列表达式中正确的是( C )A. [–A]反=(01101100)B. [A]反=(10010100)C. [-A]原=(01101101)D. [A]原=(00010011)1-6.一个十六路数据选择器,其选择控制输入端的数量为( A )A .4个 B. 6个 C. 8个 D. 3个1-7.四个逻辑相邻的最小项合并,可以消去( B )个因子。

A. ( 1 )B. ( 2 )C. ( 3 )D.( 4 )1-8.设A 补=(1001),B 补=(1110),C 补=(0010),在下列4种补码符号数的运算中,最不可能产生溢出的是 ( D )A. [A-C]补B. [B-C]补C. [A+B]补D. [B+C]补 1-9.能够实现“线与”的CMOS 门电路叫( D )A. ( 与门 )B. ( 或门 )C. (集电极开路门)D. (漏极开路门) 1-10.CMOS 三输入或非门的实现需要( C )个晶体管。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子科技大学数字电路

期末考试样题

Company number:【0089WT-8898YT-W8CCB-BUUT-202108】

一、填空题

1.五个变量构成的所有最小项之和等于 ( )。

2.已知某数的二进制原码表示为 ( 110110) 2 , 则其对应的8-bit 补码表示为 ( )2。

3.已知∑=C B A F ,,)3,0(,则∑='C B A F ,,( )。

4.要使D 触发器按'*Q Q =工作,则D 触发器的输入D=( )。

5.用移位寄存器产生1101010序列,至少需要( )位的移位寄存器。

二、单项选择题:

1. 若要将一异或门当作反相器(非门)使用,则输入端A 、B 端的连接方式是( )。

A. A 或B 中有一个接“0”

B. A 或B 中有一个接“1”

C. A 和B 并联使用

D. 不能实现 2.组合电路的竞争冒险是由于( )引起的。

A. 电路不是最简

B. 电路有多个输出

C. 电路中使用不同的门电路

D. 电路中存在延时

3.某一逻辑函数真值表确定后,下面描述该函数逻辑功能的表达式中,具有唯一性的是( )。

A .该逻辑函数的最简与或式

B .该逻辑函数的积之和标准型

C .该逻辑函数的最简或与式

D .该逻辑函数的和之积式

4.若最简状态转换表中,状态数为n ,则所需状态变量数K 为 ( )的整数.

00

00

01

01

10

1011

11图 A .n K 2log = B .n K 2log < C . n K 2log ≥ D . n K 2log ≤

5.某计数器的状态转换图如图1所示,其该计数器的模为( )。

A . 八 B. 五 C. 四 D. 三

三、 组合电路分析:

1.求逻辑函数 Z Y X Y X Z X F ⋅'⋅+⋅+⋅'= 的最简积之和表达式。

2.已知逻辑函数∑=Z Y X F ,,)7,5,1(, 请写出该函数的标准和(最小项之和)表达式: 3.找出逻辑表达式X W Y W F ⋅+'⋅'=对应的电路的所有静态冒险。

四、组合电路设计:

1、试用一片三输入八输出译码器74X138和适当的与非门实现函数:

画出电路连接图。

译码器如右图所示。

2、一个多路复用器,具有4个2位输入总线P 、Q 、R 、T ,3个选择输入端S2~S0根据表1选定4个输入总线中的一个来驱动2位输出总线Y 。

如图2所示,可以使用一片74x153(四选一多路复用器)和一个码转换器实现该功能,试写出图2中“码转换器”对应的真值表和逻辑表达式。

1(21)C S S '=⋅,0(10)C S S '=⋅

五、 时钟同步状态机设计:

表1

S 2 S 1 S 0 选择的输入 0 0 0 P 0 0 1 P 0 1 0 P 0 1 1 Q 1 0 0 P 1 0 1 P 1 1 0 R 码

1、 写出一个3位同步格雷(GRAY )码计数器的转移/输出表:

Q2Q1Q0 Q2*Q1*Q0* Z

2、构造J-K 触发器的应用表。

已知某状态机的转移/输出表如表2所示,写出针对J-K 触发器的激励/输出表。

表2:转移/输出表 Q1Q0 X 0 1 00 01,0 10,0 01 11,0 01,0 11 01,1 00,0 10 01,0 11,0

Q1*Q0*,Z

3、已知某状态机针对D 触发器的激励/输出表如表3所示,请导出最小成本激励方程和输出方程。

101D Q X Q X =⋅+⋅,010D Q Q X ''=⋅⋅

六、时钟同步状态机分析:

1、已知电路

如图3所

示,写出电路的激励方程、转移方程并建立转移表

图3

激励/输出表 Q1Q0 X

0 1 00 0d,1d,0 1d,0d,0 01 1d,d0,0 0d,d0,0 11 d1,d0,1 d1,d1,0 10

d1,1d,0 d0,1d,0

J1K1,J0K0,Z

J-K 触发器的应用表 Q Q* J K 0 0 0 d 0 1 1 d 1 0 d 1 1

1

d

表3:激励/输出表

Q1Q

0 X 0 1 0 0 0 0 ,0 0 1 ,0 0 1 0 0 ,0 1 0 ,0 1 0 0 0 ,0 1 0 ,1 D1D0 , Z

2、已知某时序电路的转移/输出表如表4所示,请画出与输入波形对应的输出Y 的波形图(设起始状态为Q 1Q 0=00)。

/输出表。

A Z=0

B Z=0

D Z=1

C Z=0

X

X ’11Y

’Y ’

XY ’

七、设计一个MEALY 型序列检测器,当

且仅当输入X 是1111或1101时,输出Z 为1。

允许重叠。

写出最简状态/输出表或状态图。

比如:

X : 0 0 1 1 0 1 1 1 1 0 1 1 1 0 1 0 0 0 0 Z : 0 0 0 0 0 1 0 0 1 0 1 0 0 0 1 0 0 0 0 解:状态/输出表:

含义 S X

0 1 未收到1位有效码

A A ,0

B ,0 收到1个1 B A ,0

C ,0 收到11 C

D ,0

E ,0 收到110 D A ,0 B ,1 收到111

E

A ,0

E ,1

表4:转移/输出表

Q1Q 0 A

0 1 00 01,0 00,0 01 01,0 11,0 10 01,0 00,1 11

01,0

00,1 图4

状态/输出表 S

XY

Z

00 01

10

11

S*

八、74x163为同步清零,同步计数的4位二进制计数器,利用74x163和集成多路选择器74x151构成的序列发生器电路如图5所示。

1)试分析当M=0和M=1时,电路中Q2Q1Q0的输出序列以及计数器分别工作在几进制。

2)写出当M=0和M=1输出Y处产生的序列。

图5

解:1)M=0时,Q2Q1Q0的输出序列为:000001010011100101110111 000,为八进制计数器;

M=1时,Q2Q1Q0的输出序列为: 001010011100101110111001,为七进制计数器。

M=1时,输出Y处产生的序列:1011010。