以最简单的Hello程序为例 NIOSII开发的整个流程

NIOS2完整教程

NIOS2完整教程NIOS II 是一款高度可配置的32位嵌入式软核处理器,由Intel旗下的Altera(现在归属于英特尔)推出。

它具有低功耗、高性能和可扩展性的特点,适用于各种嵌入式应用领域。

下面是一份简要的NIOSII完整教程,帮助您了解如何开始使用NIOSII。

1. Nios II 架构Nios II 架构包括处理器核、总线接口、存储器和外设设备。

处理器核包括CPU和一些协处理器,如乘法器、除法器等。

总线接口用于连接处理器核、存储器和外设设备。

存储器用于存储指令和数据。

外设设备包括UART、GPIO、SPI、I2C等。

2. Nios II 开发环境搭建首先,您需要安装Altera的Quartus软件来进行Nios II的开发。

Quartus提供了一个开发工具套件,包括编译器、仿真器和调试器。

您还需要安装Nios II EDS,这是一个集成开发环境,用于配置和生成Nios II处理器的软件。

安装完软件后,您可以创建一个新的Nios II项目。

3. Nios II 项目配置在Quartus中创建新的Nios II项目时,您需要指定处理器类型、时钟频率和存储器大小等参数。

您还可以选择添加外设设备和协处理器。

一旦项目创建完成,您可以使用Nios II EDS来配置处理器和外设设备,并生成相关的软件。

4. Nios II 软件开发Nios II 支持多种软件开发工具,包括C/C++编译器、汇编器和调试器。

您可以使用C/C++编译器来编写和调试应用程序。

您还可以使用汇编器来编写高性能的关键代码。

调试器可以帮助您检测和修复应用程序中的错误。

5. Nios II 系统调试在开发过程中,您可能需要进行系统调试,以解决应用程序的问题。

Nios II 支持硬件和软件调试。

硬件调试通过连接JTAG接口进行,可以在硬件级别上进行调试。

软件调试使用Nios II调试器进行,可以在软件级别上进行调试。

6. Nios II 系统验证在完成软件开发和调试后,您可以进行系统验证,确保系统的正确性和稳定性。

NIOS II处理器c程序编写基本流程

NIOS II处理器c程序编写基本流程总结:对NIOS II处理器编写程序主要是用来控制NIOS II外围设备如片上存储器,PIO内核,定时器,SDRAM内核,UART内核,DMA内核以及用户自定义内核等。

其本质是对NIOS II外围设备的相关寄存器进行读写操作。

如下图所示NIOS II处理器即cpu的输入信号主要有时钟,复位信号,中断请求信号,读数据等。

Cpu输出信号主要有地址线,读使能,写使能,写数据,字节选择等。

NIOS II处理器c程序经过编译后产生.elf文件(其内容包括对存储器初始化的.hex文件)下载到FPGA中,其本质主要是将c程序(包括用户自定义的程序和系统自带的库)编译产生的机器代码存储到程序存储器里(一般为rom),为c程序中定义的变量(本质是通过寄存器间接寻址实现)在数据存储器(一般为ram)中分配存储空间。

异常程序的引导程序一般放在ram里以提高异常情况的处理速度。

NIOS II处理器的逻辑模块如下图所示,由此可知NIOS II处理器主要实现读取指令,翻译指令,读写数据,异常控制,中断控制等功能。

步骤一:打开ecplise软件。

步骤二:在QUARTUS II工程文件夹中新建workspace文件夹作为ecplise工作文件夹。

系统会在workspace中自动生成.metadata文件,.metadata文件包含如下图所示的几个文件夹。

步骤三:新建ecplise工程。

选择ecplise工程所需的.sopcinfo文件(之前建立NIOS II处理器系统时产生的文件,此处为mynios.sopcinfo),给ecplise工程命名(此处为mynios_software)。

此时系统自动生成software文件夹,software文件夹中包含以ecplise工程名命名的文件夹(此处为mynios_software)和以ecplise工程名_bsp命名的文件夹(此处为mynios_software_bsp)。

NIOS_II手把手入门

NIOS II手把手入门前言:NIOS II是什么?也许你第一次听到这个词。

通俗地讲,NIOS II其实是一个软核,那什么是软核?软核是一个基于哈佛结构的可配置处理器。

哈佛结构,联想到了吧,其实51单片机也是基于哈佛结构的处理器。

至于为什么是哈佛结构,我觉得可能是哈佛结构的处理速度较快,因为他可以在一个周期读取数据和指令。

(关于哈佛结构的详细信息请自己查阅!)因此NIOS II是把指令存储器和数据存储器分开的。

在此我想详细介绍下可配置处理器的概念。

我们都知道51单片机或者ARM里面的硬件资源都是固定的,是固化的,不能修改的。

但是软核可配置就不一样啦,它里面的CPU,外围器件都是可选择的。

因此我们可以根据实际的情况来选择需要的资源,这样可以提高利用率。

总之,大家把它当做单片机来学习就行了!讲了一大堆,相信大家还是有点模糊,下面就以流水灯介绍NIOS II吧,让我们进入NIOS II的神奇世界!(在此相信大家都已经掌握quartus的基本使用和安装了与quartus 同样版本的NIOS II软件!)Quartus环境操作:第一步:建立一个Quartus II工程和原理图文件第二步:打开配置NIOS II窗口第三步:配置NIOS II内核和外围器件(双击system contents窗口中component library下拉菜单的Nios II processor)接下来选择程序存储区和数据存储器还有通用8位IO 口。

然后配置通用IO口:(下面是选择器件区窗口,可以看到上面配置的器件!!)双击CPU,把复位矢量和异常矢量分配好:第四步:好了,到现在为止我们已经配置好一个简单的NIOS II内核,接下来就是漫长的等待吧!第五步:在原理图中添加内核symbol(其中内核复位信号是低电平复位!!)第六步:软件(C或C++)编程现在看一下NIOS II软件编写窗口吧,是不是跟单片机开发的有点类似!清空其他工程后,建立一个应用项目:file—new—Nios II C/C++ Application然后建立一个C程序文件:大家可以先把程序写下来,按下保存!等下会有相应的解释。

NiosII软件设计与运行流程

NiosII软件设计与运行流程本实验是于实验1相连的,本实验主要完成在NiosII硬件系统完成及下载于FPGA中的基础上,进行软件开发、下载和调试,具体流程如下:1、向FPGA下载配置文件。

以下的实验将更多地与SOPC实验系统联系。

本次实验是使用清华大学电工电子实验中心的GW48-SOPC实验系统(康芯公司),下载前连接好下载通信线,打开电源,打开光盘上关于此实验系统的PDF/PPT默认设置说明,确认实验系统所有开关和跳线处于默认设置位置。

用10芯通信线将实验系统左侧的“Byterblaster II”接口与适配板上的JTAG Port口相连;将实验系统左侧的跳线短路帽接插“ByBt II”端,编程电压选择跳线短路帽插3.3V(此电压接错不会损坏系统)。

按动实验系统左下角的电路模式控制键,选择模式5(在上方的数码管会显示5字),这时实验系统将进入附录中附图1的电路连接模式(有12中不同的可选硬件电路模式)。

注意模式5的8个键控特点:每按键一次,输出电平反相一次,电平高低由此键上方的发光管显示;还注意到此时FPGA输出的32个I/O口接了8个数码管,每4个I/O口接一个数码管,且在每一数码管外接了一个16进制至7段译码的译码器,这样可以大大节省I/O口的耗用。

FPGA的主要端口是用标准信号名PIOx标注的,具体引脚号在引脚锁定时查阅附录的附表1;例如附图1中连接FPGA的键8端口标准信号名是“PIO7”,查附表1,横项GW48-SOPC对应Pin240。

现在可以开始下载配置文件,以便在FPGA中建立NiosII硬件环境。

打开QuartusII,再打开实验一的工程,选择菜单Tools→Programmer,弹出图2-1所示窗口,首先选择接口模式,对于Mode栏确认选择JTAG模式;如果是首次安装并使用该软件,要作下载接口模式选择:点击图2-1左侧的Hardware Setup按纽,将弹出图2-2所示窗口。

NIOS 2 软件开发手册

NIOS II 软件开发手册本文仅限于个人学习使用版权所有编辑:DiDy2006-11-29Email:wedidy@目录第一部分 Nios II软件的发展 (4)第一章概述 (4)1.1引言 (4)1.2 Nios II简介 (4)1.3开发环境 (4)1.4第三方支持 (5)1.5第一代Nios处理器的移植 (6)第二章 Niso II IDE (7)引言 (7)Nios II IDE 工作台 (7)建立新的工程 (7)组建并编辑工程: (9)运行和调试程序 (10)编辑Flash (13)帮助系统 (14)第二部分 HAL系统库 (16)第三章 HAL系统库简介 (16)引言 (16)开始设计 (16)HAL的结构 (16)第四章使用HAL进行程序开发 (19)引言: (19)Nios II IDE工程结构 (19)System.h系统说明文件 (20)数据宽度和HAL类型定义 (20)UNIX风格的接口 (21)文件系统 (22)使用字符模式器件 (23)使用定时器器件 (24)使用Flash器件 (26)使用DMA器件 (30)缩减代码 (34)引导程序序列和入口 (36)存储器的使用 (37)HAL系统库文件路径 (41)第一部分 Nios II软件的发展这一部分主要介绍Nios II软件发展的相关信息。

包括以下两章:第一章 概述第二章 Nios II IDE 简介第一章概述1.1引言这一章从较高的角度为Nios II软件开发人员总体介绍Nios II处理器。

对Nios II软件的开发环境,用户可以使用的工具和相应的设计过程进行讲解。

1.2 Nios II简介基于Nios II处理器同使用其他微处理器的软件设计相似。

最简单有效的方法是从Altera公司购买一套开发工具,其中包括相应的文档,开发板和编写Nios II程序相应的开发工具。

Nios II软件开发者手册是针对那些对Nios II处理器有一定了解的用户。

NIOSII教程

NIOSII教程NIOS II 是一种基于软核的处理器,可用于 FPGA 设计中。

它是由Altera 公司所开发的。

NIOS II 可以在 FPGA 中进行快速原型设计,并且具有高度可配置性和可扩展性。

本文将介绍 NIOS II 的基本架构和使用方法。

NIOSII架构基于RISC架构,它是一个32位的处理器,并且具有可选的指令扩展。

它的流水线深度可以根据设计的需求进行配置,以实现不同的性能要求。

NIOSII支持多种功能,包括硬件中断、异常处理以及浮点运算等。

在开始使用NIOSII进行开发之前,首先要进行软核处理器的配置。

配置包括选择所需的指令集、流水线深度和其他性能参数。

配置完成后,可以将软核处理器添加到FPGA设计中。

一旦软核处理器被添加到FPGA设计中,就可以开始编写应用程序。

NIOSII支持标准的C/C++语法,并且还提供了一些特殊的函数和指令,用于访问FPGA的硬件资源。

例如,可以使用特殊函数来配置GPIO引脚、读取和写入存储器以及执行其他与硬件交互的操作。

使用NIOSII进行FPGA开发具有许多优点。

首先,它提供了一种快速原型设计的方法,可以大大加快开发进程。

其次,NIOSII的可扩展性和高度可配置性使得它适用于各种不同的FPGA设计需求。

最后,NIOSII的开发工具和调试接口使得开发和调试过程更加简单和高效。

总结起来,NIOS II 是一种基于软核的处理器,适用于 FPGA 设计中。

它具有灵活性和可配置性,可以使用 C/C++ 或 HDL 进行开发,并通过Altera 公司提供的工具链进行编译和调试。

NIOS II 提供了一种快速原型设计的方法,并且适用于各种不同的 FPGA 设计需求。

NIOSii配置及例程使用教程

NIOSii配置及例程使用教程NIOS ii 配置及例程使用教程本教程为nios ii在FPGA板上的配置入门教程,仅使用在xsyan 设计制作EP2C5/EP2C8开发板上。

下面将会详细的说明如何使用nios ii在FPGA上配置一个altera公司提供的CPU,并利用这个CPU 来调试和执行相应C程序。

并且,最后会有两个例程。

一,硬件要求:1,EP2C5/EP2C8开发板一块。

2,USB电源线一条。

3,并口线一条。

4,串口线一条。

二,软件要求:1,quartus II 7.0.2,MegaCore IP 7.0.3,Nios II EDS 7.0.三,主要步骤:1,在quartus上创建一个工程。

2,在此工程里面调用SOPC,并配置CPU。

3,创建cpu.4,定义FPGA引脚并综合。

5,调用NIOS,配置相应设置。

6,再次编译综合工程。

7,下载FPGA。

四,详细步骤:1,在quartus上创建一个工程。

a)打开quartus,选择File->New project wizard.b)在打开的窗口上选择Nextc)选择工程路径,并且指定工程名字。

d)添加文件,因为没有设计文档,所以跳过,直接Next。

e)选择器件,请根据自己的开发板选择EP2C5T144C8/ EP2C8T144C8f)然后直接点Finish,创建工程完毕。

2,用SOPC配置一个CPU。

a)在quartus里面调用SOPC。

b)在打开的SOPC里面,输入系统名字,选择HDL语言种类c)点确定后开始配置CPU,双击左边栏的Nios ii Processor.d)这里选择经济型,然后点Next,直到下个页面。

e)然后点finish,Process配置结束,双击UART,配置串口f)直接用默认配置,点Finish即可,然后双击on-chip-memory 配置memory。

g)配置如上图配一个8K内部ram后点Finish,用来存放程序代码和初始化代码,然后继续创建memory用来存放变量,再创建两个4K内部ram,步骤同上。

NIOS II Step by Step 图解

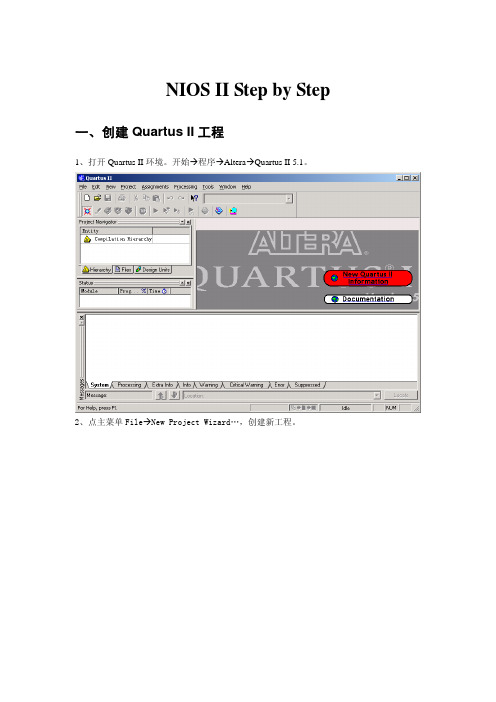

NIOS II Step by Step一、 创建Quartus II工程1、打开Quartus II环境。

开始Æ程序ÆAlteraÆQuartus II 5.1。

2、点主菜单FileÆNew Project Wizard…,创建新工程。

3、弹出如下窗口,点Next,进行下一步操作。

4、输入新建工程路径,工程名及工程顶层实体,点Next,下一步。

如所输入工程路径文件夹不存在,则会弹如下窗口,点“是”,创建工程文件夹。

5、弹出如下窗口,按默认,点Next,下一步操作。

6、选择目标板上对应的正确芯片型号,点Next,下一步操作。

7、设置适当工具选项,可按默认不设置,点Next,下一步。

8、点Finish,完成工程结构创建。

9、鼠标指向Project Navigator窗口中工程器件项,右击鼠标选择器件属性设置“Device…”10、选择Device & Pin Option,进行器件及管脚选项设置。

11、选择配置项Configuration,选择配置芯片与目标板上配置器件一致。

12、选择Unused Pins选项,把没用到管脚设为三态输入“As input tri-stated”,其它选项按默认,点确定,完成设置。

二、SOPC Builder创建系统模块1、在Quartus II环境中选择菜单ToolsÆSOPC Builder…,打开SOPC Builder向导。

2、创建新系统,输入系统模块名称,如“Techshine_EP1C12”,选择适当的目标描述语言。

3、在左端元件池窗口列表中选处理器项,点Add…或双击鼠标左键,添加CPU。

4、选择适当的NIOS II Core,推荐用“Nios II/s”模式,点Next,进一步设置5、对Cashes & Tightly Coupled Memories设置,可选择默认,点Next,下一步设置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本实验以最简单的Hello程序为例,演示NiosII开发的整个流程:废话不多说,我们来开始最简单、最基本的NiosII程序,首先打开quartusII

9.1,双击即可,打开如下界面:

点击File→New Project Wizard 如下图:

出现如图:

点击第一个后面的。

将新建的文件放入自己事先建好的文件夹hello内

千万记住路径中不能有中文

完成后如图:

再第二个填入hello中即可,之后点击next,出现如下图:

继续next,不要犹豫……

在Device family 中选择Cyclone III(因为我们的板子芯片是这个系列的),其他的不用动。

在available devices中选择EP3C10E144C8,完成后点击next,

这里我们不做仿真,直接点击next

点击finish,完成新建

真正的工作即将开始:

在这点击File→New都可跳出如下界面:

选择Block Diagram/Schematic File,双击,出现如下界面

在工具栏()中选择SOPC,单击,出现如下界面

其中的System Name 命名为kernal , Target HDL选为VHDL

将时钟改为100M,Name也改为clk(改不改都行)

下一步选择CPU,也就是nios的处理器,双击

选择完毕后,出现这样的对话框

对话框中可看到三种nios核(从e核最简单,占用空间最小,第三个f核是快速的,但是占用空间最大的,中间的S核是介于e和f之间的,性能和占用空间比较平衡的核。

)

这里我们选择f核(方便以后开发使用)

这里Memory后面可选的部分暂时没有东西,暂且放一边,待我们建立好SDRAM和EPCS再回来选择即可?

接下来,点击next

其中Data cache 选择none(原因在后面介绍?)

点击next

点击next

继续next

其中有很多级别,这里我们选择level1即可

点击完成,出现如下界面

其中cpu_0即为我们要使用的核,右键rename改为cpu,

下面要做的就是接外设,让cpu工作起来

首先加入sdram

双击sdram,出现

选择Presets:Custom; Data with:16,其他的都不变。

继续next

没有要改的,点击完成,出现下面的界面了

同之前一样,将sdram_0改为sdram

下面我们要选择一个将程序固化到flash中的东西,板子上用的是Epcs,下面我们来选择epcs

双击,出现如下图:

点击完成

继续Rename,改为epcs,如图:

接下来选择:System ID Peripheral

双击

通过此时间戳,可以知道quartus工程和nios工程师相互对应的

点击Finish,

同样改下名字为:sysid

下面我们还需要一些东西,serial的东西

双击

啥别说了,next

好吧,finish ?

改名哦,rename→jtag_uart

Jtag是开发板上的jtag,uart是将板子上的信息反馈到nios II IDE中显示出来

不要一部很重要的没有完成,?

想起来了吧,在cpu中的设置

其中上面选择epcs,下面选sdram,如图

原因很简单,当上电复位时,复位从上电不掉电的位置flash,放到adram 中运行

点击finish

下面空白框中出现 No errors orwarnings

下面将epcs的基地址(Base)改为首地址,如图,点击右键锁定

接下来分配其他的基地址system→Auto-Assign Base-Adresses

由于还有中断的使用,因此要分配一下,以免发生错误:system→

Auto-Assign IRQs

完成后如图:

点击next

点击generate,出现的对话框,点Save,过程可能比较慢,耐心等待一下哈 ?

完成后就出现

最后一行提示generate成功了,哈哈

接下来点击exit

回到quartus中的界面

在空白的地方双击:

选择project中的kernal

还需要自己建时钟,在空白处继续双击,建立一个锁相环,在这里

选择MegaWizard Plug-In Manager

点击next

在I/O中选择ALTPLL,在What name do you want for the output file?在 \ 之后填入PLL,Which type of output file do you want to create?下面选择VHDL(你要是用的Verilog,就选择第三个)

之后点击next

外部时钟是50M的需要修改一下,之后点击next

Optional inputs和lock output中不需要,将中间的对号都去掉,之后点击next

点击next,看不到下面的next就直接点回车

Next

我们需要100M的时钟,只需将图中第一个框中的 1 改为2 即可得到100M 的,

如图

我们还需要一个时钟,注意此部分,

点击clk c1,同样改为100M的时钟,同时让两个时钟有一定的相移,左面第三个框改为 -75

如图

一直next下去,直到finish出现,点击finish

点击ok

下面进行连线

上面的时钟是为了给sdram的双击空白处搜索output,kernal模块的引脚可以单击右键generate pins for symbol ports 自动会生成引脚

为了使引脚和硬件实际相连,需要对照脚本文件修改上图中的各引脚名。

(先保存一下,默认路径即可)。