微机原理重点考试习题Chapter 3

第三章微机原理习题答案

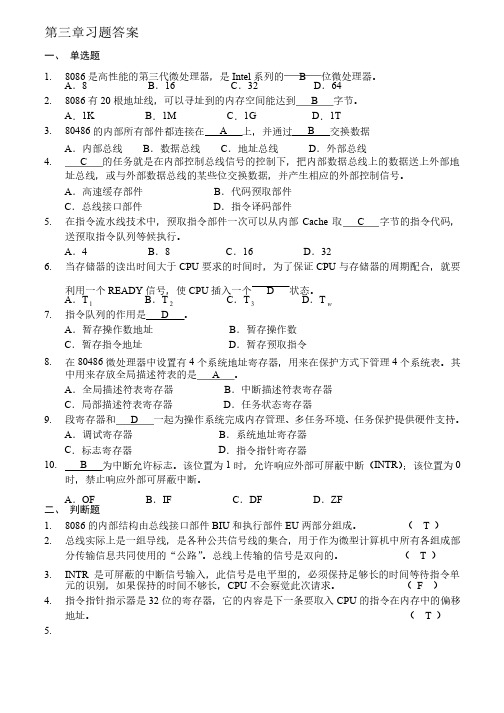

第三章习题答案一、 单选题1. 8086是高性能的第三代微处理器,是Intel 系列的系列的 B 位微处理器。

位微处理器。

A .8 B .16 C .32D .64 2. 8086有20根地址线,可以寻址到的内存空间能达到根地址线,可以寻址到的内存空间能达到 B 字节。

字节。

A .1KB .1MC .1GD .1T 3. 80486的内部所有部件都连接在的内部所有部件都连接在 A 上,并通过上,并通过 B 交换数据交换数据A .内部总线.内部总线B .数据总线.数据总线C .地址总线.地址总线D .外部总线.外部总线4. C 的任务就是在内部控制总线信号的控制下,把内部数据总线上的数据送上外部地址总线,或与外部数据总线的某些位交换数据,并产生相应的外部控制信号。

址总线,或与外部数据总线的某些位交换数据,并产生相应的外部控制信号。

A .高速缓存部件.高速缓存部件B .代码预取部件.代码预取部件C .总线接口部件.总线接口部件D .指令译码部件.指令译码部件5. 在指令流水线技术中,预取指令部件一次可以从内部Cache 取 C 字节的指令代码,送预取指令队列等候执行。

送预取指令队列等候执行。

A .4B .8C .16D .32 6. 当存储器的读出时间大于CPU 要求的时间时,为了保证CPU 与存储器的周期配合,就要利用一个READY 信号,使CPU 插入一个插入一个 D 状态。

状态。

A .T 1 B .T 2 C .T 3D .T w 7. 指令队列的作用是指令队列的作用是D 。

A .暂存操作数地址.暂存操作数地址 B .暂存操作数.暂存操作数C .暂存指令地址.暂存指令地址D .暂存预取指令.暂存预取指令8. 在80486微处理器中设置有4个系统地址寄存器,用来在保护方式下管理4个系统表。

其中用来存放全局描述符表的是中用来存放全局描述符表的是A 。

A .全局描述符表寄存器.全局描述符表寄存器B .中断描述符表寄存器.中断描述符表寄存器C .局部描述符表寄存器.局部描述符表寄存器D .任务状态寄存器.任务状态寄存器9. 段寄存器和段寄存器和 D 一起为操作系统完成内存管理、一起为操作系统完成内存管理、多任务环境、多任务环境、多任务环境、任务保护提供硬件支持。

微机原理第3章习题与答案

9.若AL、BL中是压缩BCD数,且在执行ADD AL, BL之后,(AL)=0CH,CF=1,AF=0。再执行DAA后,(AL)=_____。

A.02HB.12HC.62HD.72H

答案:B

10.执行下列程序后AL的内容为_____。

MOV AL, 25H

SUB AL, 71H

DAS

A.B4HB.43HC.54HD.67H

答案:0300H

5.假定(DS)=4000H, (DI)=0100H, (40100H)=55H, (40101H)=AAH,执行指令LEA BX, [DI]后,BX中的内容是_______。

答案:0100H

6.如果TABLE为数据段3400H单元的符号名,其中存放的内容为0505H,当执行指令MOV AX, TABLE后,(AX)=_______;而执行指令LEA AX, TABLE后,AX=______。

A.SHLAL, CXB.XCHGAL, BLC.MOV BX, [SI]D.AND AX, BX

答案:A

14.串操作指令中,有REP前缀的串操作指令结束的条件是________。

A.ZF=1 B.ZF=0 C.CX>0 D.CX=0

答案:D

15.对于下列程序段:

AGAIN:MOV AL, [SI]

答案:B

5.设(SP)=0100H,(SS)=2000H,执行PUSH BP指令后,栈顶的物理地址是_____。

A.200FEHB.0102HC.20102HD.00FEH

答案:A

6.指令LEA BX, TAB执行后,其结果是______。

A.将TAB中内容送BXB.将TAB的段基址送BX

C.将TAB的偏移地址送BXD.将TAB所指单元的存储内容送BX

微机原理第3章习题与答案

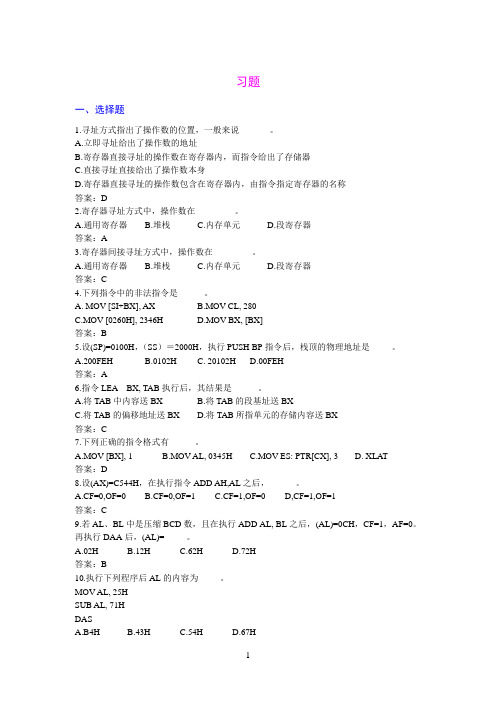

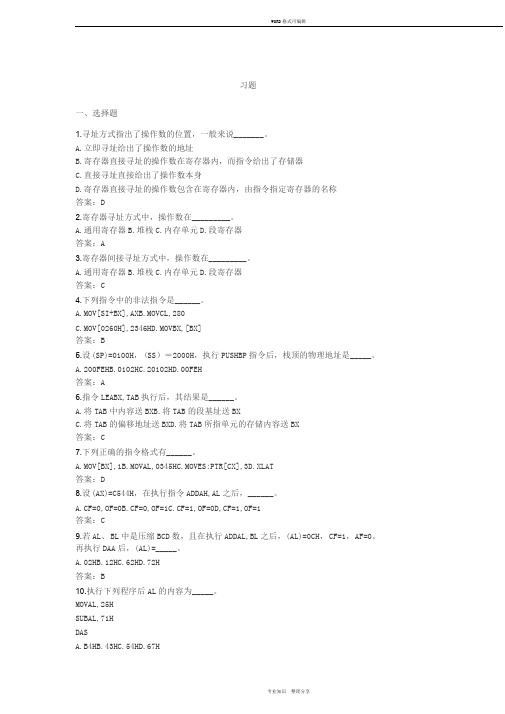

习题一、选择题1.寻址方式指出了操作数的位置,一般来说_______。

A.立即寻址给出了操作数的地址B.寄存器直接寻址的操作数在寄存器内,而指令给出了存储器C.直接寻址直接给出了操作数本身D.寄存器直接寻址的操作数包含在寄存器内,由指令指定寄存器的名称答案:D2.寄存器寻址方式中,操作数在_________。

A.通用寄存器B.堆栈C.内存单元D.段寄存器答案:A3.寄存器间接寻址方式中,操作数在_________。

A.通用寄存器B.堆栈C.内存单元D.段寄存器答案:C4.下列指令中的非法指令是______。

A.MOV[SI+BX],AXB.MOVCL,280C.MOV[0260H],2346HD.MOVBX,[BX]答案:B5.设(SP)=0100H,(SS)=2000H,执行PUSHBP指令后,栈顶的物理地址是_____。

A.200FEHB.0102HC.20102HD.00FEH答案:A6.指令LEABX,TAB执行后,其结果是______。

A.将TAB中内容送BXB.将TAB的段基址送BXC.将TAB的偏移地址送BXD.将TAB所指单元的存储内容送BX答案:C7.下列正确的指令格式有______。

A.MOV[BX],1B.MOVAL,0345HC.MOVES:PTR[CX],3D.XLAT答案:D8.设(AX)=C544H,在执行指令ADDAH,AL之后,______。

A.CF=0,OF=0B.CF=0,OF=1C.CF=1,OF=0D,CF=1,OF=1答案:C9.若AL、BL中是压缩BCD数,且在执行ADDAL,BL之后,(AL)=0CH,CF=1,AF=0。

再执行DAA后,(AL)=_____。

A.02HB.12HC.62HD.72H答案:B10.执行下列程序后AL的内容为_____。

MOVAL,25HSUBAL,71HDASA.B4HB.43HC.54HD.67H11.下列四条指令中,需要使用DX寄存器的指令是______。

微机原理习题集(3章)

一.单项选择题:1、在存取数据时,默认的段地址存放在____寄存器中。

A CSB DSC SSD ES2、指令____的目的操作数的寻址方式为直接寻址。

A MOV [2000H],ALB IN AL,DXC XOR AL,2000HD MOV AX,[BX]3、8086的堆栈栈顶由____来指示。

A CS∶IPB SS∶IPC SS∶SPD CS∶SP4、下面叙述正确的是____;A 地址分段方法主要是为了解决CPU地址总线条数与地址寄存器位数不同的问题而产生的。

B 访问存储器时,段地址是由用户指定的寄存器提供的。

C 访问存储单元时,需要获得的地址是段地址。

D 任意相邻的两个段地址至少相距32个存储单元。

5、数据寄存器中可以用作累加器的是____;A AXB BXC CXD DX6、已知(DS)=0100H,(SS)=1000H,(BP)=0050H,(SI)=0001H,disp=000AH,则经过基址变址寻址后获得的物理地址是____;A 0105BHB 01051HC 1005BHD 10051H7、8086CPU标志寄存器中的进位标志位是____;A CFB SFC PFD AF8、下面叙述错误的是____;A 段寄存器的内容不都是用传送指令置入的。

B 取指令时,段寄存器一定是CS。

C 存取数据时,段寄存器一定是DS。

D 进行堆栈操作时,段寄存器一定是SS。

9、在8086/8088的基址加变址的寻址方式中,基址寄存器是指____;A AX,BX,CX,DXB BX,BPC SI,DID CS,DS,ES,SS10、设(DS)=426AH,偏移量为86H,该字节的物理地址是____;A 43F00HB 42726HC 42706HD 42720H11、由段寄存器、段偏移地址所确定的物理地址是这样产生的____;A物理地址=段寄存器的内容×8+偏移地址B物理地址=偏移地址×8C物理地址=段寄存器内容×20+偏移地址D物理地址=段寄存器内容×16+偏移地址12、8086 最大寻址空间是____;A 64KB B 640KBC 1MBD 512KB13、寄存器寻址的操作数包含在____中。

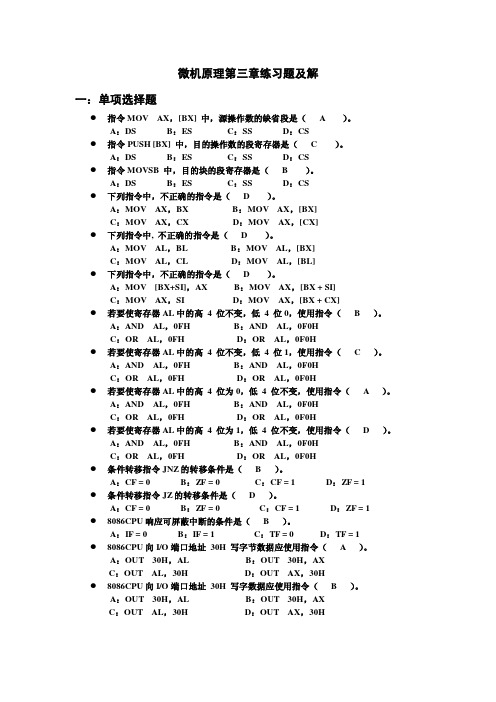

微机原理第三章练习题及解答

微机原理第三章练习题及解一:单项选择题●指令MOV AX,[BX] 中,源操作数的缺省段是( A )。

A:DS B:ES C:SS D:CS●指令PUSH [BX] 中,目的操作数的段寄存器是( C )。

A:DS B:ES C:SS D:CS●指令MOVSB 中,目的块的段寄存器是( B )。

A:DS B:ES C:SS D:CS●下列指令中,不正确的指令是( D )。

A:MOV AX,BX B:MOV AX,[BX]C:MOV AX,CX D:MOV AX,[CX]●下列指令中, 不正确的指令是( D )。

A:MOV AL,BL B:MOV AL,[BX]C:MOV AL,CL D:MOV AL,[BL]●下列指令中,不正确的指令是( D )。

A:MOV [BX+SI],AX B:MOV AX,[BX + SI]C:MOV AX,SI D:MOV AX,[BX + CX]●若要使寄存器AL中的高4 位不变,低4 位0,使用指令( B )。

A:AND AL,0FH B:AND AL,0F0HC:OR AL,0FH D:OR AL,0F0H●若要使寄存器AL中的高4 位不变,低4 位1,使用指令( C )。

A:AND AL,0FH B:AND AL,0F0HC:OR AL,0FH D:OR AL,0F0H●若要使寄存器AL中的高4 位为0,低4 位不变,使用指令( A )。

A:AND AL,0FH B:AND AL,0F0HC:OR AL,0FH D:OR AL,0F0H●若要使寄存器AL中的高4 位为1,低4 位不变,使用指令( D )。

A:AND AL,0FH B:AND AL,0F0HC:OR AL,0FH D:OR AL,0F0H●条件转移指令JNZ的转移条件是( B )。

A:CF = 0 B:ZF = 0 C:CF = 1 D:ZF = 1●条件转移指令JZ的转移条件是( D )。

A:CF = 0 B:ZF = 0 C:CF = 1 D:ZF = 1●8086CPU响应可屏蔽中断的条件是( B )。

微机原理第3章习题(答案)

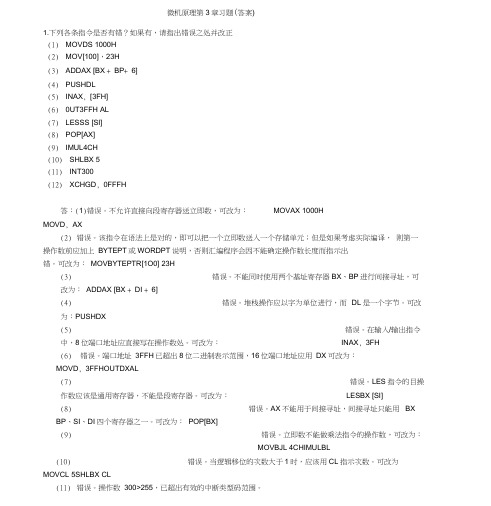

微机原理第3章习题(答案)1.下列各条指令是否有错?如果有,请指出错误之处并改正(1)MOVDS 1000H(2)MOV[100],23H(3)ADDAX [BX + BP+ 6](4)PUSHDL(5)INAX, [3FH](6)0UT3FFH AL(7)LESSS [SI](8)POP[AX](9)IMUL4CH(10)SHLBX 5(11)INT300(12)XCHGD, 0FFFH答:(1)错误。

不允许直接向段寄存器送立即数,可改为:MOVAX 1000HMOVD, AX(2)错误。

该指令在语法上是对的,即可以把一个立即数送入一个存储单元;但是如果考虑实际编译,则第一操作数前应加上BYTEPT或WORDPT说明,否则汇编程序会因不能确定操作数长度而指示出错。

可改为:MOVBYTEPTR[1O0] 23H(3)错误。

不能同时使用两个基址寄存器BX、BP进行间接寻址,可改为:ADDAX [BX + DI + 6](4)错误。

堆栈操作应以字为单位进行,而DL是一个字节。

可改为:PUSHDX(5)错误。

在输入/输出指令中,8位端口地址应直接写在操作数处。

可改为:INAX, 3FH(6)错误。

端口地址3FFH已超出8位二进制表示范围,16位端口地址应用DX可改为:MOVD, 3FFHOUTDXAL(7)错误。

LES指令的目操作数应该是通用寄存器,不能是段寄存器。

可改为:LESBX [SI](8)错误。

AX不能用于间接寻址,间接寻址只能用BXBP、SI、DI四个寄存器之一。

可改为:POP[BX](9)错误。

立即数不能做乘法指令的操作数,可改为:MOVBJL 4CHIMULBL(10)错误。

当逻辑移位的次数大于1时,应该用CL指示次数。

可改为MOVCL 5SHLBX CL(11)错误。

操作数300>255,已超出有效的中断类型码范围。

(12)错误。

XCHG指令不允许立即数做它的操作数。

可改为:MOVC, 0FFFHXCHGDXCX2•请指出以下各指令的源、目的操作数所使用的寻址方式(1)MOVSI 2100H(2)SBBDISP[BX], 7(3)AND[DI] , AX(4)ORAX [609EH](5)MOV[BXb DI + 30H], CX(6)PUSHES [BP](7)CALL[DI]DISP(8)JNZShort_label答:(1)源操作数:立即数寻址;目的操作数:寄存器寻址(2)源操作数:立即数寻址;目的操作数:基址寻址(3)源操作数:寄存器寻址;目的操作数:寄存器间接寻址(4)源操作数:直接寻址;目的操作数:寄存器寻址5)源操作数:寄存器寻址;目的操作数:(带位移量的)基址变址寻址(6)源操作数:带段超越的寄存器间接寻址;目的操作数:隐含寻址(7)只有一个操作数,为变址寻址(8)只有一个操作数,为相对寻址3. 已知DS=2000H 有关的内存单元值为:(21000H)=00H,(21001H)=12H,(21200H)=00H,(21201H)=10H,(23200H)=20H,(23201H)=30H,(23400H)=40H,(23401H)=30H,(23600H)=60H,(23601H)=30H,符号COUNT 勺偏移地址为1200H。

微机原理第三章及答案

第三章习题集二.选择题(每小题1分,共15分)1. 逻辑地址1000:2000对应的物理地址为( B )。

A、1200HB、12000HC、2100HD、21000H2. 下面哪个寄存器使用时的默认段寄存器为SS( C )。

A、AXB、BXC、SPD、SI3. 当使用BP寄存器作基址寻址时,若无指定段替换,则内定在( B )段内寻址。

4.在下面四组寄存器中,第 D 组都可用于对存储器间接寻址方式的寄存器。

A. AX,BX,CX,IP;B. BX,SP,DX,SIC. IP,SP,BP,AXD. BP,BX,SI,DI5. 含有立即数的指令中,该立即数被存放在 A 。

A. 累加器中B. 指令操作码后的内存单元中C. 指令操作码前的内存单元中D. 由该立即数所指定的内存单元中6. 用段基值及偏移量来指明内存单元地址的方式称为( C )。

A、有效地址B、物理地址C、逻辑地址D、相对地址7. 已知物理地址为0FFFF0H,且段内偏移量为0B800H,若对应的段基地址放在DS中,则DS=( B )。

A、0FFFFHB、0F47FHC、2032HD、0F000H8. 含有立即数的指令中,该立即数被存放在 B 。

A. 累加器中B. 指令操作码后的内存单元中C. 指令操作码前的内存单元中D. 由该立即数所指定的内存单元中9.寄存器间接寻址方式中,操作数在 C 中。

A. 通用寄存器B. 堆栈C. 存储单元D. 段寄存器10.下列指令中,有语法错误的指令是(B D)。

A. MOV AX,[1000H]B. LEA AL,1000HC. MOV [1000H],ALD. MOV 1000H,AX11. 下列指令语法有错的是:CA. MOV AX,1000HB. MOV AX,BXC. MOV [AX],[1000H]D. MOV AX,[1000H]12. 8086/8088中除___C___两种寻址方式外,其它各种寻址方式的操作数均在存储器中。

微机原理重点考试习题Chapter 3

第3章 80x86微处理器一、自测练习题㈠选择题1.因为8086 CPU的字数据既可以存放在内存的偶地址单元,也可以安排在奇地址单元,所以其堆栈指针SP( )。

A.最好指向偶地址单元 B.可以指向任何地址单元C.只能指向偶地址D.只能指向奇地址2.8086/8088微处理器内部能够计算出访问内存储器的20位物理地址的附加机构是( )。

A.ALU B.加法器C.指令队列 D.内部通用寄存器3.8086CPU外部的数据总线和地址总线分别为( )位。

A.16,16 B.20,16 C.16,20 D.20,20 4.指令代码的地址存放在寄存器( )中。

A.DS和SI B.BX和BP C.ES和DI D.CS和IP5.最大方式中,控制总线的信号来自( )。

A.8282 B.8284 C.8288 D.82866.在8086中,一个基本的总线周期由( )个时钟周期组成。

A.1 B.2 C.3 D.47.在8086CPU中,数据地址引脚( )采用时分复用。

A.AD0~AD15 B.AD0~AD9 C.AD0~AD20 D.AD10~AD28.8086CPU把1MB空间划分为若干逻辑段,每段最多可含( )的存储单元。

A.1KB B.8KB C.16KB D.64KB9.当标志寄存器FLAGS中OF位等于1时,表示带有符号的字运算超出数据( )范围。

A.-128~+127 B.-32768~+32767C.000~FFFFH D.0~FFH10.总线写周期中,在( )时不需要像读周期时要维持一个周期的浮空状态以作缓冲。

A.-32767~+32767 B.-32767~+32768C.-32768~+32767 D.-32766~+3276911.CPU执行指令过程中,BIU每完成一次对存储器或I/O端口的访问过程,称为( )。

A.时钟周期 B.总线周期 C.总线读周期 D.总线写周期12.BHE与A0配合以决定访问存储器的数据是高字节还是低字节工作,其BHE仅在总线周期开始的( )周期有效。

微机原理第三章习题与参考答案

第三章习题与参考答案3.1 已知 (DS) = 1000H,(ES) = 2000H,(SS) = 3000H,(SI) = 0050H,(BX) =0100H,(BP) =0200H,数据变量DISP的偏移地址为1000。

指出下列指令的寻址方式和物理地址。

(1) MOV AX,0ABH 立即寻址无(2) MOV AX,BX 寄存器寻址无(3) MOV AX,[l000H] 直接寻址 10000H(4) MOV AX,DATA 直接寻址 (DS*16+DATA )(5) MOV AX,[BX] 寄存器间接寻址 10100H(6) MOV AX,ES:[BX] 寄存器间接寻址 20100H(7) MOV AX,[BP] 寄存器间接寻址 30200H(8) MOV AX,[SI] 寄存器间接寻址 10050H(9) MOV Ax,[BX+l0] 寄存器相对寻址 1010AH(10) MOV AX,DISP[BX] 寄存器相对寻址 11100H(1l) MOV AX,[BX+SI] 基址变址寻址 10150H(12) MOV AX,DISP[BX][SI] 相对基址变址寻址 11150H3.2 分别说明下例指令采用的寻址方式和完成的操作功能。

(1) MOV CX,2000H 立即寻址将立即数2000H送CX寄存器(2) MOV DS,AX 寄存器寻址将AX寄存器内容送DS段寄存器(3) AND CH,[1000H] 直接寻址将[DS*16+1000H]单元的内容送CH寄存器(4) ADD [DI],BX 寄存器间接寻址将CL寄存器的内容送[DS*16+DI]单元(5) MOV SS:[3000H],CL 直接寻址将CL寄存器的内容送[SS*16+3000H]单元(6) SUB [BX][SI],1000H 直接寻址将立即数1000H送[DS*16+BX+SI+50H]单元(7) ADD AX,50H[BX][SI] 相对基址变址寻址将[DS*16+BX+SI+50H]单元的内容送AX寄存器(8) PUSH DS 寄存器寻址将DS寄存器的内容送[SS*16+SP]单元(9) CMP [BP][DI],AL 寄存器寻址将AL寄存器的内容送[SS*16+DI+BP]单元3.3 判断下列指令正误,如果错误请指出原因。

大学微机原理第三章习题

大学微机原理第三章习题8086/8088的寻址方式和指令系统习题一.单项选择题1.设置BX=2000h,Si=3000h,指令movax的源操作的有效地址[BX+Si+8]为()。

a、5000hb.5008hc.23008hd.32022h2.设ds=1000h,es=2000h,bx=3000h,指令addal,[bx]的源操作数的物理址为()。

a.13000hb.23000hc.33000hd.3000h3.设ds=2000h,es=3000h,si=200h,指令moves:[si],al的目的操作数的物理地址为()。

a.20210hb.30200hc.50200hd.200h4.指令movmem[bx],ax中的mem是()。

a.原码b.反码c.补码d.移码5.用来作为寄存器间接寻址的寄存器有()个。

a.8b.6c.5d.46.指令mov[BX+Si],Al中的目标操作数使用()段寄存器。

a、 csb.dsc.ssd.es7.指令movbx,[bp+5]中的源操作数使用()段寄存器。

a.csb.dsc.ssd.es8.段内间接寻址只改变()中的内容。

a、 csb之间的间接寻址。

ipc。

政务司司长和知识产权署。

psw9。

仅更改()中的内容。

a.csb.ipc.cs和ipd.psw10.下述指令中不改变psw的指令是()。

a.movax,bxb.andal,0fhc.shrbx,cld.addal,bl11.下述指令中不影响cf的指令是()。

a.shlal,1b.inccxc、添加[bx],ald.subax,bx12.两个整数补码9ch和7ah相加运算后,会产生()。

a.无溢出且无进位b.无溢出但有进位c.有溢出且有进位d.有溢出但无进位13.指令jmpwordptr[bx]属于()寻址。

a、段内直接B.段内间接C.段间直接D.段间间接14。

指令movax的源操作数[BX+Si+8]属于()寻址。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第3章 80x86微处理器

一、自测练习题

㈠选择题

1.因为8086 CPU的字数据既可以存放在内存的偶地址单元,也可以安排在奇地址单元,所以其堆栈指针SP( )。

A.最好指向偶地址单元 B.可以指向任何地址单元

C.只能指向偶地址D.只能指向奇地址

2.8086/8088微处理器内部能够计算出访问内存储器的20位物理地址的附加机构是( )。

A.ALU B.加法器C.指令队列 D.内部通用寄存器3.8086CPU外部的数据总线和地址总线分别为( )位。

A.16,16 B.20,16 C.16,20 D.20,20 4.指令代码的地址存放在寄存器( )中。

A.DS和SI B.BX和BP C.ES和DI D.CS和IP

5.最大方式中,控制总线的信号来自( )。

A.8282 B.8284 C.8288 D.8286

6.在8086中,一个基本的总线周期由( )个时钟周期组成。

A.1 B.2 C.3 D.4

7.在8086CPU中,数据地址引脚( )采用时分复用。

A.AD0~AD15 B.AD0~AD9 C.AD0~AD20 D.AD10~AD2

8.8086CPU把1MB空间划分为若干逻辑段,每段最多可含( )的存储单元。

A.1KB B.8KB C.16KB D.64KB

9.当标志寄存器FLAGS中OF位等于1时,表示带有符号的字运算超出数据( )范围。

A.-128~+127 B.-32768~+32767

C.000~FFFFH D.0~FFH

10.总线写周期中,在( )时不需要像读周期时要维持一个周期的浮空状态以作缓冲。

A.-32767~+32767 B.-32767~+32768

C.-32768~+32767 D.-32766~+32769

11.CPU执行指令过程中,BIU每完成一次对存储器或I/O端口的访问过程,称为( )。

A.时钟周期 B.总线周期 C.总线读周期 D.总线写周期

12.BHE与A0配合以决定访问存储器的数据是高字节还是低字节工作,其BHE仅在总线周期开始的( )周期有效。

A.T1 B.T2 C.T3 D.T4

13.最小方式下原8086微处理器最大方式下S2、S1、S0引脚应改为( )。

A.M/IO、DEN、DT/R B.DT/R、M/IO、DEN

C.M/IO、DT/R、DEN D.DEN、M/IO、DEN

14.最大方式下引脚25号和24号分别为QSo和QSl,若工作于最小方式下则分别为( )。

A.INTA和ALE B.ALE和INTA C.TEST和INTA D.DEN和ALE

15.复位时,由于( )被清零,使从INTR输入的可屏蔽中断就不能被接受。

A.标志寄存器B.通用寄存器C.暂存寄存器 D.内部通用寄存器

16.如果8086CPU引脚状态为M/IO=1,WR=0,那么此时执行的操作为( )。

A.读存储器 B.读外设C.写存储器 D.写外设

17.在8086最小方式的读操作中,外设将要输入的数据送上AD线后,在( )的前沿,此数据被采样送入CPU。

A.T1 B.T2 C.T3 D.T4

PUSH AX

PUSH BX

POP AX

A.(SP)=010EH B.(SP)=010AH C.(SP)=0116H D.(SP)=0108H

18.8086微处理器被设计为两个独立的部件,它们是( )。

A.运算器和控制器B.总线接[3BIU和执行部件EU

C.寄存器组和标志寄存器 D.分析指令和执行指令部件

19. 8086CPU中标志寄存器FLAGS的主要作用是( )。

A.检查当前指令执行的正确与错误

B.纠正当前指令执行的正确与错误

C.产生影响或控制某些后读指令所需的标志

D.决定是否停机

20.8086CPU中的IP的作用是( )。

A.保存放置在数据总线上的数据

B.装有将要执行的下一条指令的段内地址

C.保存被译码的指令操作码

D.装有当前正在执行指令的段内地址

㈡填空题

1.总线接口部件BIU同外部总线连接为( )完成所有的总线操作,并计算形式20位的内存物理地址。

2.执行部件EU由( )、标志寄存器、运算器(ALU)和( )等组成。

3.8086的指令队列是( )字节长,而8088 指令队列是( )字节长。

4.在8086的通用寄存器中,SP用来确定( )在内存中的地址,即用来存放在现行堆栈段的一个数据区的( )。

5.在标志寄存器FLAGS中,中断允许标志IP表示系统是否允许响应外部的可屏蔽中断,如果IF=( ),表示允许响应。

6.8086系统中把可直接寻址的1MB内存空间分为称作“段”的逻辑区域,每个段的物理长度最大为( )字节。

7.8086微处理器有20条地址线,可以配置1MB(1048 576字节)的内存储器,地址编号为( )。

8.8086程序把1MB的存储空间看成一组存储段,各段的功能由具体用途而定,分别为( )、( )、( )和( )。

9.8086微处理器是Intel公司的第三代微处理器——16位微处理器,它采用( )引脚的DIP(双列直插)封装,8086的和40条引脚信号按功能可分为4部分:( )、( )、( )以及其他(时钟与电源)。

10.8086的控制总线中有一条( )(33号引脚)线,即最小/最大方式控制线,用来控制8086的工作方式。

11.ALE为( ), INTA为( )。

12.8088的地址/数据复用线为8条,即( )。

13.当8086 CPU的MN/MX引脚接( )电源时,8086CPU工作于最小方式,用于构成( )。

14.当8086 CPU的MN/MX引脚( )时,8086 CPU工作于最大方式,用于构成( )。

15.( )是8086CPU工作在最大方式下构成系统中必不可少的支持芯片。

16.8086 CPU在最小方式下的HOLD和HLDA引脚在最大方式时成为( )和( )信号线,这两条引脚通常同8087(协处理器)或8089(I/O处理器)相连接,用于8086同它们之间传送总线请求与总线应答信号。

17.8086 CPU与外部交换信息是通过( )进行的。

18.8086 CPU的总线周期至少由( )个时钟周期组成。

19.一个总线周期完成一次数据传输。

至少要有( )和( )两个过程。

20.当8086 CPU的( )引脚上为有效电平(高电平),且标志寄存器中IF=( ),则8086CPU在执行完当前的指令后响应中断。

21.80386有3种存储地址空间:( )、( )和( )。

22.80386有3种工作方式:( )、( )和( )。

23.Pentium片内有两个8KB的Cache(双路Cache结构),一个是( ),一个是( )。

24.“奔腾Ⅱ”处理器采用了新的封装技术:( )插盒。

25.在P3 中新增加了几十条SSE指令,SSE是Streaning SIMD Extension的缩写,其意思是()。

二、自测练习题参考答案

㈠选择题

1.A 2.B 3.A 4.D 5.C

11.B 12.A 13.C 14.B 15.A

㈡填空题

1.执行部件EU

3.6,4

5.1

7.00000H~FFFFFH

9.40,地址总线,数据总线,控制总线

11.地址锁存允许信号,中断响应信号

13.+5V,小型的单处理机系统

15.8288总线控制器

17.总线

19.传送地址,传送数据

21.逻辑地址,线性地址,物理地址

23.指令Cache,数据Cache

25.流水式单指令多数据扩展。