基于嵌入式ADSP-BF533的实时先天性心脏病心音分析处理系统

基于ADSP-BF533的音频处理系统设计

基于ADSP-BF533的音频处理系统设计

王莹;李学生;项多云;李爽

【期刊名称】《电声技术》

【年(卷),期】2006(000)008

【摘要】进行数字信号处理运算的微处理器用于实时快速地实现数字信号处理算法.针对ADSP-BF533的特点介绍了基于该芯片的音频处理系统电路设计,主要包括复位电路、电源单元、存储器单元及模数/数模转换单元等,可作为音频信号处理的通用系统.

【总页数】4页(P32-35)

【作者】王莹;李学生;项多云;李爽

【作者单位】电子科技大学,机械电子工程学院,四川,成都,610054;电子科技大学,机械电子工程学院,四川,成都,610054;西昌卫星发射中心,四川,西昌,615606;西昌卫星发射中心,四川,西昌,615606

【正文语种】中文

【中图分类】TN91

【相关文献】

1.基于ADSP-BF533的家庭安全系统设计 [J], 李利军;张佩;张晓曦

2.基于ADSP-BF533的视频监测系统设计 [J], 姚爱琴;张东宁;单永利

3.基于ADSP-BF533的最小系统设计 [J], 赵博;闫达远;张栋;马思博;周雅

4.基于ADSP-BF533的视频监测系统设计 [J], 姚爱琴;张东宁;单永利

5.基于ADSP-BF533的音频处理设计及实现 [J], 周相阳;尚朝轩;何强

因版权原因,仅展示原文概要,查看原文内容请购买。

基于ADSP-BF533光纤熔接监控设计

第30卷 第2期2007年4月电子器件Ch inese Jou r nal Of Elect ro n DevicesVol.30 No.2Ap r.2007Design of Fused Fiber Splicing Mon itor ing Technology B ased on ADSP 2BF5333Z H AO Wen 2xi a n ,L I U J in 2ga o ,L I W ai 2y un(Dept.of Elect ronics Sci ence Technol ogy ,East Chi na Normal Uni versit y ,S hang hai 200062,China)Abstract :A systemic design to remot el y monitor fused fi ber splicing ba se d on AD I ADSP 2B F533wit h real -t ime characteri stics a nd hi gh p reci sion i s descri bed.The analog video si gnal i s di gitized i n t he video deco de module ADV7183B and t he digit al vi deo signal i s encoded i n t he video encode module ADV7171.Hi gh ca 2paci t y exter nal SDRAM memory i s use d to buffer t he digit al video f rame.The cent ral cont rol a nd di gital vi deo da ta processi ng unit is complet ed i n ADSP 2B F533.The system ca n do real time video compression ,so analog video from different vi dicons can display on t he same mo nitor and t he f used fi ber splici ng process can be re motel y monitored.K ey w or ds :ADSP 2B F533;ADV7183B ;ADV7171;vi deo decode ;video encode EEACC :1265;6430;6140基于ADSP 2BF533光纤熔接监控设计3赵雯娴,刘锦高,李外云(华东师范大学电子科学技术系,上海200062)收稿日期62323基金项目上海市科研计划项目的资助(5)作者简介赵雯娴(82)女,华东师范大学信息学院电子系在读硕士研究生,主要研究通信与信息系统,5@摘 要:介绍了在光纤熔接监控系统中基于ADI ADSP -B F533的设计方法,用于实时地、高图像精度地远程监控光纤熔接过程.其中视频解码模块ADV7183B 完成模拟视频信号数字化,视频编码模块ADV7171完成数字视频信号模拟化,同时采用外部SDRAM 存储器作为数字视频帧缓存,整个系统以ADSP 2B F533为核心模块进行视频编解码的控制和数字视频数据的处理.此系统可以进行实时的视频压缩处理,完成多个视频源的模拟视频同时显示在一台模拟监控器上,分辨率高,达到了远程实时监控光纤熔接过程的目的.关键词:ADSP 2BF533;ADV7183B ;ADV7171;视频解码;视频编码中图分类号:TN 27 文献标识码:A 文章编号:100529490(2007)022******* 光纤熔接监控系统可以用于远程控制光纤的熔接,和一般的监控系统相比具有实时性强和图像精度高的特点,这就要求核心芯片必须具备强大的MCU 功能,能够对视频编解码芯片进行很好的配置,同时还必须具备强大的DSP 功能,尤其要在数字视频数据处理方面性能突出,经过项目组的再三斟酌,最后决定选用ADI 公司的ADSP 2B F533作为核心芯片实现对视频编解码芯片的控制和数字视频数据的处理.系统结构框图如图1所示.系统的工作流程大致如下:两个模拟视频摄像头分别从两个角图1 系统结构框图度对光纤的熔接过程进行拍摄,摄取的模拟视频信号经过ADV7183B 视频解码,解码后的数字视频数据存储在外部SDRAM 中,并通过ADSP 2B F533进:20001:012:.行数字视频数据处理,处理后的数字视频数据经过ADV7171视频编码,最后实现在模拟监视器上同时显示两个角度的视频,从而达到监控的目的.1 主要功能模块介绍1.1 A DSP 2BF533美国模拟器件公司(ADI)是全世界领先的高性能信号处理集成电路制造商,是全球主要的可编程DSP 芯片供应商之一.Bl ackfin DSP 是该公司16位产品的一个大系列,采用ADI 和Intel 联合开发的微信号体系结构(MSA),集DSP 和MCU 功能于一身,指令集增加了专门指令以支持多媒体视频和音频功能,特别适合于完成视频、音频等数字信号处理.ADS P 2B F533是Blackfi n DSP 系列的一个成员,拥有16位定点DSP 内核,可以实现600M Hz 的持续工作,内核包括2个16位乘法器,2个40位累加器,2个40位算术逻辑单元(AL U ),4个8位视频ALU ,以及1个40位移位寄存器.ADSP 2B F533的结构体系将存储器构造成统一的4G B 地址空间,用32位地址寻址.包括内部存储器、外部存储器、PCI 地址空间和I/O 控制寄存器在内的所有资源,在这个统一的地址空间中独立占据各自的一段.此外,ADSP 2B F533还有12通道的DMA ,3个支持PWM 的定时/计数器以及满足I TU 2656数字视频格式的并行外部接口(PPI)[1].1.2 视频解码芯片ADV 7183BADV7183B 是ADI 公司推出的模拟视频解码芯片,能够将兼容国际标准N TSC 、PAL 或S E 2CAM 的模拟基带视频信号转换成兼容I TU 2656标准的8/16位YCrCb 型4∶2∶2数字视频数据.ADV7183B 集成了3个54M Hz 、10位的模数转换器(ADC ),具有12路模拟视频输入信道.ADV7183B 处理功能强大,能够处理CVB S ,Y/C 和YPr Pb 等不同格式的模拟视频信号,实现对输入模拟视频信号的亮度色度分离、采样,同步信号的抽取等功能.ADV7183B 采用I 2C 与微处理器实现通信[2].1.3 视频编码芯片ADV 7171ADV7171是ADI 公司推出的综合数字视频编码芯片.ADV7171具有4个高质量的10位视频数字模拟转换器(DAC ),可将兼容ITU 2656标准的8/16位Y Cr Cb 型4∶2∶2数字视频数据转换成兼容国际标准的N TS 、L 等制式的模拟视频信号,其中D 输出VBS 信号,D B 输出BL U VB S U 信号,D 输出R D S 2V C/V 信号,DAC D 输出G R EEN/S 2Vi deo Y/Y 信号.每个DAC 都可以独立工作和进行单独控制,而不影响其他DAC 的输出.ADV7171同样采用I 2C 与微处理器进行通信[3].2 系统实现2.1 ADSP 2BF533和编解码芯片的I 2C 通信过程ADSP 2B F533通过I 2C 通信对ADV7183B 和ADV7171进行配置.由于编解码芯片的ALSB 接地,所以读写ADV7183B 的器件地址分别为0X41(读操作)和0X40(写操作);读写ADV7171的器件地址分别为0X 55(读操作)和0X54(写操作).I 2C 通信数据传输时序如图2所示,其中S 是开始信号,P 是结束信号.图2 I 2C 通信时序图ADS P 2B F533和编解码芯片的通信流程大致如下:①B F533发送开始信号,实现方法是在保持SCL K 线高时,SDA 线由高变低;②BF533发送8位器件写操作地址(ADV7183B 为0X40,ADV7171为0X 54);③B F533等待AC K 信号,AC K 信号是在第9个时钟脉冲时SDA 线被拉低;④B F533发送8位编解码芯片寄存器地址值;⑤B F533等待AC K 信号;⑥B F533发送8位寄存器配置值;⑦B F533等待AC K 信号;⑧B F533发送结束信号,实现方法是在保持SCL K 线高时,SDA 线由低变高.2.2 编解码芯片的配置2.2.1 解码芯片的配置ADV7183B 的12路模拟视频输入信道通过不同的配置可以支持11路CVB S 信号、3路Y C 信号和2路YPr Pb 信号.通过INSEL 寄存器位可控制输入的类型和信道的选择.整个处理过程通过I 2C 通信对相关寄存器进行配置.下面是部分配置程序:void Init_ADV (void){ int te mp Reg ;te mpReg =3p Fla shA_Port A_Out ;clr_bit (tempReg ,R ST_7171);3p FlashA_PortA_Out =temp Re g |(1<<RST_7183)|(1<<P PICL K_ADV7183_SEL ECT );te mpReg =3p FIO_IN EN ;3FIO_IN N =R |(<<DV 83_O );设置B F533的F 寄存器R =3FIO_DIR ;506第2期赵雯娴,刘锦高等:基于ADSP 2B F533光纤熔接监控设计C PA AC A C AC E/C /AC C E /ideop E temp eg 1A 71E //P te mp eg p3p F IO_DIR=te mpReg|(1<<ADV7183_O E);//设置B F533的P F2引脚为输出引脚tempRe g=3pF IO_FL AG_C;3p FIO_FLA G_C=tempReg|(1<<ADV7183_OE);} 2.2.2 编码芯片的配置ITU2656YCrCb型4:2:2数据以27M Hz的速率输入到ADV7171之后,被分成Y、Cr、Cb三路信号,Y信号范围为16到235,CrCb信号范围为16到240.通过正确的寄存器配置,产生需要的模拟基带视频信号.下面是部分配置程序:void Init_DAV(void){ int tempReg,i;tempRe g=3pFlashA_Po rtA_Out;clr_bit(tempReg,R ST_7183);clr_bit(tempReg,PPICL K_ADV7183_SEL ECT);3pFlashA_PortA_Out=tem pReg|(1<<RS T_7171);} 2.3 ADSP2BF533并行通信接口PP IPPI是半双工形式的并行外部接口,具有双向端口,最大可输入/输出16位数据.它有1个专用的时钟引脚、3个帧同步引脚、4个专用的数据引脚和12个P F复用的数据引脚.应用系统中的ADV7183B和ADV7171共用P PI接口数据引脚PP[3:0],并通过程序配置将B F533芯片的P F管脚PF[15:12]设为PP I数据管脚,从而实现8位PPI数据传送.ADV7183B、ADV7171和B F533的连接如图3所示.图3 BF533P PI连接图 PP I支持ITU2656[4]输入的3种模式和输出的1种模式.ITU2656的3种输入模式是:活动视频模式、VBI模式和整场模式.应用系统采用活动视频模式,在该模式中,PP I不读入图像结束数据EA V和开始数据SAV之间的所有数据以及V=1时的所有数据,同时插入在消隐信号中的控制字被PPI过滤掉,P PI只有在检测到SAV信号时才开始读入数据,在PP I_FRAME寄存器中设置每帧活动视频的行数.在这种模式下,发送视频流之前数据和控制代码必须在内存中设置好.输出以二维DMA的方式实现.2.4 直接存储访问方式DMABF533通过使用二维DMA方式实现存储器空间和编解码器之间的数字视频数据传送.数据传送使用PP I通道,由于B F533只有一个半双工PPI收发的DMA通道[7],同时进行数据收发容易产生数据冲突,所以系统采用不同的读取方式进行和编解码器之间的数据传送;DV83B的数据输入到B F533存储器采用单次数据传送,即一次传输任务完成之后,自动停止该DMA通道,此时运行状态标志位DMA_RU N从1变为0,但DMA配置寄存器的DMA使能位没有变化.若要重新启动该DMA 通道,只要重新设置DMA配置寄存器即可.将B F533存储器图像数据输出到ADV7171时采用自动缓冲模式,即当一个传输任务完成之后,控制寄存器将被它们的原始设置值重载,这样DMA可以不断重复同一个操作,直到将DMA配置寄存器的DMA使能位清零为止.DMA初始化程序大致如下[526]:void Init_DMA_Input(void){3pDMA0_CON FI G=0;3pDMA0_S TAR T_ADDR=SDRAM INADD;//DMA目标地址3pDMA0_X_COUNT=X_RAM_Length_In;//X_RAM_ Le ngth_In个32位数字图像数据传输3pDMA0_X_MODIF Y=0x4;//32位数字图像数据传输3DM_Y_OUN T=Y_R M_L_IN;Y_R M_ L_IN个3位数字图像数据传输3DM_Y_MODIF Y=x;3位数字图像数据传输606电 子 器 件第30卷A71p A0C A ength//A e ngth2p A004//23pDMA0_PERIP HERAL_MAP=0x0;//使用PP I外设3pDMA0_CONF IG=DMAEN|DI_EN|WNR|WD2 S IZE_32|R ES TAR T|DMA2D|DI_EN;//设置DMA配置寄存器}void Init_DMA_Output(void){3pDMA0_CONF IG=0x1090;3pDMA0_S TAR T_ADDR=SDRAMOU TADD;3pDMA0_X_COUN T=X_RAM_Lengt h_out;3pDMA0_X_MODIF Y=0x1;3pDMA0_Y_COUN T=Y_RAM_Length_out;3pDMA0_Y_MODI F Y=0x1;}2.5 数字视频数据处理应用系统处理存储在外部SDRAM中的I TU2 656YCr Cb型4∶2∶2格式的数字视频数据,过程如下:两个模拟摄像头同步摄取的两场模拟视频经过ADV7183B解码成为数字视频数据之后通过B F533的PP I DMA通道,滤除消隐数据保留活动数字视频数据,将这两场活动数字视频数据存储在SDRAM的一段连续空间中.然后B F533对其中一场的第一行进行奇数位像素数据的采样,采样数据存储在SDRAM的另一段空间中,紧接着对另一场的第一行进行偶数位像素数据的采样,采样数据紧接着前一段采样数据连续存储.用同样的方法依次采样两场数字视频的剩余行.最终存储的采样数据经过ADV7171编码就可以实现两个摄像头拍摄的画面在模拟监示器上左右同时显示的效果.采用不同的采样方法可以实现不同的显示效果,比如两幅画面上下显示或层叠显示等[8].外部SDRA M和B F533的引脚连接如图4所示.图4 外部SDRAM和ADSP-B F533引脚连接图3 结束语应用系统在Blackfi n系列的软件开发环境Vi s2 ual DSP++3.5下开发和调试.系统的设计充分利用了ADSP2B F533强大的控制和数字信号处理功能,结合视频编解码芯片,实现了监控光纤熔接过程的目的,实时性好,图像精度高,能够用于远程控制光纤的熔接.该系统后续开发的空间很大,在今后的设计中可以考虑增加更为复杂完善的功能.参考文献:[1] Analo g Devices[R],ADSP2B F533Blackfin TM Pro cessorHardware Reference,Preli m i nary Revi s io n,2003.3:2452503.[2] Analog Devices[R],Mul tifor m at SD TV Vi deo Deco derADV7183B Data Sheet,Revi s io n0,2004.9:60289.[3] Analo g Devi ces[R],Di gi t al PAL/N TSC Video Encoder wit h102Bit SSAF and Advanced Power Managem ent ADV7170/ADV7171Dat a Sheet,Revi s i on A,2001:21223.[4] I TU2R B T.65624.Int erfaces for Digit al C o m po nent Vi deo Sig2nal s i n5252li ne and6252li ne Televi sion Syst ems Op erati ng att he4:2:2L evel of Recommendatio n ITU2R B T.601,1998[S].[5] Cappell ini V,C o nst anti ni des A.G.Digit al S i gnal Processing[M].Academic Press Inc.L td,1980:822109.[6] Samuel D Steams,Rut h A David.S i gnal Proces s i ng Algo2ri t hms[M].Prentice Hall,1988:2012206.[7] 陈峰.Blackfin系列DSP原理与系统设计[M].北京:电子工业出版社,2004:612119.[8] 张新芝.电视技术[M].北京:高等教育出版社,2003:102100.706第2期赵雯娴,刘锦高等:基于ADSP2B F533光纤熔接监控设计。

基于ADSP-BF533的H.264解码器的优化实现的开题报告

基于ADSP-BF533的H.264解码器的优化实现的开题报告1. 研究背景和研究意义随着现代多媒体技术的不断发展,视频压缩技术已经成为了广泛应用的一项基础技术。

H.264是一种先进的视频编码标准,其优秀的压缩性能和图像质量已经使其成为了当前最流行的视频编码标准之一。

因此,H.264解码器的实现已成为当前研究的热点之一。

ADSP-BF533是ADI公司的一种基于Blackfin处理器的低功耗、高性能DSP芯片,具有优秀的计算能力和低功耗的优势,可用于多媒体解码器的实现。

本研究将基于ADSP-BF533平台,对H.264解码器的优化实现进行研究,并探索系统性能的优化和资源的利用,为实现高效率和低成本的视频解码器提供技术支持。

2. 研究内容和方法2.1 研究内容本研究将基于ADSP-BF533平台,对H.264解码器进行优化实现。

具体而言,研究内容包括以下几个方面:(1)H.264压缩编码原理的研究和分析,包括码流结构、帧内预测和帧间预测等关键技术的原理和实现方法。

(2)通过对控制流和数据流的优化,实现H.264解码器的高效、低功耗的运行。

(3)基于DM6446平台,通过对多线程并行计算、采用快速算法等优化策略,进一步提升H.264解码器的性能。

(4)通过实验和仿真,验证所设计的H.264解码器的性能。

2.2 研究方法本研究将采用以下研究方法:(1)文献调研和实践分析。

对现有的H.264解码器实现进行调研和剖析,明确其优点和不足之处,为本研究提供参考和基础。

(2)系统设计和优化。

通过对H.264压缩编码原理的研究和分析,以及对ADSP-BF533平台的深入了解,进行H.264解码器的系统设计和资源利用的优化。

(3)软件编程实现。

采用C语言,编写H.264解码器程序,并进行有效性测试。

(4)实验评估和性能测试。

通过设计实验评估平台,测试H.264解码器的性能,并进行实验数据的分析和评估。

3. 预期成果和创新点3.1 预期成果通过本研究,预期可以实现在ADSP-BF533平台上的高速H.264解码器。

基于ADSP-BF533的图像匹配处理机的硬件平台设计

( .天津大学 1 摘 天津 307 ; 2 0 0 2 .太原理工大 学 太原 002) 30 4

要 :图像 匹配处理 机是 目标 识别系统的重要组成部 分 , 是机器人视觉 系统 的核心技术 , 在现 代信号处理特别 是 图 、 l h和 双端 口 Fa s

Ab ta t Pitr thn n i o tn ato a g trc g io y tm. I h e c n lg f mp trvso sr c: cu emac ig i a s mp ra tp r f r e e o nt ns se t i t st ek yt h oo yo i e o c u e iin

关键 词 :A PB 5 3 DS -F 3 ;图像处理 ;图像匹配

中 图 分 类 号 :T 3 1 4 P 9.1 文 献 标 识 码 :A

Ha d r sg fpit r a c ng s se a e o ADS BF5 3 DS r wa ede i n o c u em thi y t m b s d n P- 3 P

维普资讯

电

子

测

量

技

术

第3 0卷 第 1 期

ELE r R0NI M EAs 乐 EM [ r TECHN0L C I E r 0GY

20 0 7年 1月

基 于 ADS - F 3 P B 5 3的 图像 匹配 处 理 机 的硬 件 平 台设 计

像处理 中占有 重要地 位 。本文 提 出 了 以 A PB 53作 为核 心 处 理器 并 配 以外 围器件 s 、_ F 3 【

R AM 组 成图像匹配处理机的硬件方案 。本 文对该硬 件设计 方案 进行 了详 细分 析 和论 述 , 给 出了硬件 总体 实现框 并 图。该处理 机硬件 系统结构简单 , 实时性好 , 可靠性高 。实验结果证 明, 本系统完全可 以实时可靠地完成图像匹配任务 。

基于嵌入式系统的多功能便携式电子听诊器

2021年第40卷第3期传感器与微系统(Transducer and MicrosystemTechnologies )65D O I :10. 13873/J . 1 000-9787(2021)03-0065-04基于嵌入式系统的多功能便携式电子听诊器+王毅德程洁姚飞、张浩、徐伟3,黄成军^(1.中国科学院微电子研究所健康电子研发中心,北京100029;2.中国科学院大学电子信息与技术学院,北京100029 ;3.湖北警官学院,湖北武汉430034)摘要:设计制作了一种基于S T M 32嵌人式微处理器的便携式多功能电子听诊器。

首先通过对不同型 号麦克风的对比测试,选择采声效果最好的O B 4015L 麦克风作为采声器件,并通过有限元仿真分析对听 诊头的结构进行了优化;然后搭建嵌人式系统,实现了对心音的实时听诊、存储回放、音量控制等功能;所采集信号可通过蓝牙或串口发送至上位机进行波形显示和存储。

该设备带宽600 H z ,覆盖了心音信号所 在的频段范围,最高可将心音信号放大1倍,信噪比达到51 d B ,设备直径6. 5 c m ,重量122 g ,轻巧便携。

与传统机械式听诊器相比,该电子听诊器不仅能够实现听诊功能,清晰的可视化反映人体微弱的生物信 号,而且在数字化、智能化方面具备独特优势。

关键词:电子听诊器;有限元仿真;嵌人式;麦克风;心音信号中图分类号:T N 70; T P 212文献标识码:A文章编号:1000-9787(2021)03-0065-04P o r t a b l e m u l t i f u n c t i o n a l e l e c t r o n i c s t e t h o s c o p eb a s e d o n e m b e d d e d s y s t e m *WANG Yide1’2,CHENG Jie1’2,YAOFei1,ZHANGHao1,XU Wei3,HUANGChengjun1’2(1. Health Electronics Research & Development Center,Institute of Microelectronics,Chinese A c a d e m y of Sciences,Beijing 100029,China ; 2. School of Electronic Information and Technology,University of ChineseA c a d e m y of Sciences,Beijing 100049,China ; 3. Hubei University of Police , W u h a n 430034, China )Abstract : A portable multifunctional electronic stethoscope based on S T M 32 embedded microprocessor i s designed and manufactured . Different types of microphones i s compared ’ and an OB 4015L i s selected for the stethoscope application . The structure of the auscultation head i s optimized by using f i n i t e element simulation , and then an embedded system i s built t o realize real-time auscultation,storage and playback of heart sounds,volume control and other functions . The collected signals can be furthersent t o thehost computer fostorage throughBluetooth orserialport . The devicchas abandwidth o f600 H z ,which coversthe heart sound signal,and an amplification up t o 11 times with a signal -to-noise ratio of 51 d B . The device has a portable design with a diameter of 6. 5 c m and a weight of 122 g . Compared with the traditional mechanical stethoscopes,the electronic stethoscope can notonlyrealizethe auscultationfunction andclearlbiological signals of human body,but also has unique advantages in digitalization and intelligentization .Keywords : electronicstethoscope ; f i n i t e element simulation ; embedded ;microphone ;heartsound0引言传统的机械式听诊器,将脏器的声音通过听筒、软管等 传导到医生的耳朵,并进而做出诊断,该方法简便易行,但 是也存在诸多局限性,如灵敏度不高、易受环境噪音干扰、 可视化差、对操作手法依赖性强等。

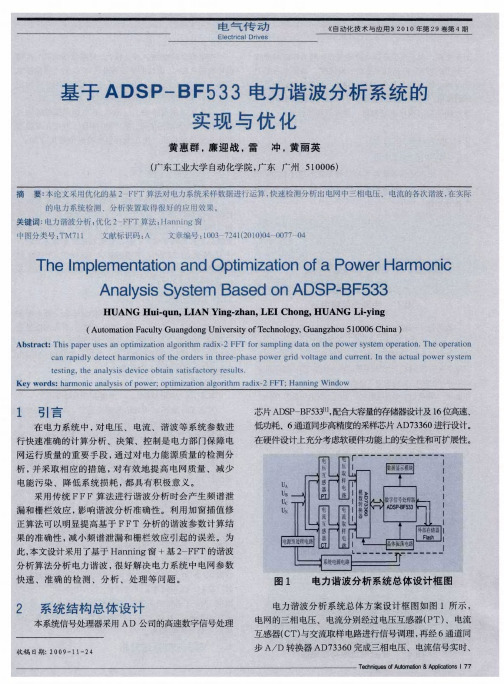

基于ADSP-BF533电力谐波分析系统的实现与优化

频率附近波动 。用 F T进行谐波 测量时 , F 首先对 信号进 行采样 , 然后建立数据 窗 口, 获取一组 F T分析的数据 , F 经过 F T 变换 , F 得到谐波结果 。在 以上过程 中, 为避免

引起 混 叠 , 须 满 足 采 样 定 律 [ 必 。

l E 这—干扰, 可在电源输入端并接一个 2D 8K压敏电阻R, 0 61

自动 化 技 术 与 应 用 2 1 0 第 2 0年 9卷第 4期

序流程 图如图 5 并在 电力谐波分析系统 中运行 良好 , , 有效

算 法等方法 , 以提 高谐波分析 系统的总体性 能、准确性 和快 速性 。系统投运后取得 了 良好的运行效 果 , 通过对 用户 的用 电负荷状 态进行分析 、 比较 , 有效地 掌握用户

数)取 k=1, , 就可在 个采样数据之中均匀抽取 l 8个 2

U。

数据, 满足了采样 频率和信号频率同步 。从 中可以看 出, 采样频率越 高,z , 越大 , 数据抽取越均匀 。从而实现采样

频 率和信 号频率 同步 。

U

图 4 交流 电压取样 电路 图

4 3 基 2 F T 法分析 . 一F算

和栅栏 效应l , 4 影响谐波 测量 准确度 。 1

l A 1

I ^ 2

在 系统 中采用基 一 2的 1 2 0 4点 F T算法 , 8 F 即 个信 号周 期 ,每一 个 信号 周 期需 要 采 集 128个 数据 。把

A 730 D 36 的采样速率置为8;s,S  ̄ D P从信号上升期过 /

电阻值的大小可 以根据压敏电阻的特性选择 ; 为防止供 电电 网电压内带有高频干扰源对系统的同步振荡电路及数据采集 等电路产生影响, 电源中并联电容器 C, 在 电容器可以通低频 阻高频 ; 在每相上串接共模 电感 L 防 I , 卜 系统共模信号的干扰。

基于ADSP—BF533的Boot Loader的移植分析

U B o 源代码 目录结构 如图 1 示。 .ot 所

当处理器上 电启动时 , 首先执行一个预定地址处的指令 , 该 地址 一般 是只读 内存 , 中存放 系统初 始化或引导程序 , 其 它在 一 般P C机中就是 BO 。BO I S I S执行低 级 的 C U初始 化并 配置 有 P

图 1 U.otA S B o( D P—B 53) 码 结 构 F3 源

的启动代码 , B o La e。这些代码 不像 P 即 ot odr C中 的 BO I S那样 灵活 , 仅仅是一 种硬件配 置方案 , 同时还 具有一定 的调试功能 。 B o La e 初始化 目标板硬件 , 供给嵌 入式操 作系统 目标 板 ot odr 提

Ke wor s: o a e ; - o ; o i ; y d Bo tLo d r U・ Bo t p r ng ADS - t P・ BF5 33

B o L ae 是 系统上 电后 运行 的第 一段 软件代码 , ot dr o 它是底 层硬件 和上层应用 软件 之 间的一个 中间软件 , 用来 完成 系统启 动和 系统 软件加 载工作 。它 可 以屏 蔽底层硬 件 的差 异 , 使上层

a ay e , n e p r n t o n r c s n a mb d e y tm o r a e n t e ADS — 5 3 C U a e d s r e . h p n lz d a d t o t g meh d a d p o e s i n e e d d s se b a d b s d o h h i P BF 3 P r e c b d T e a — i p iai n s o s ta Bo tr n tb e a d a c r t h e h oo y a d me h d d p e n t e p r n r c s r r c ia l t h w h tU— o u ssa l n c u a e T e tc n l g n t o s a o t d i h o t g p o e sa e p a t 1 e o i c

基于ADSP BF533和FPGA的接口设计

信号 产生 组件 、 定位 通信组 件 、 电源 、 终端 、 数据 处理

组件 、 线 座及 天线 驱动 等部分 组成 。 天

由于 主 站 和用 户 机 组成 结 构 大致 相 同 , 给 出 特 其 中主站 系统 简要 框 图 , 图 1所 示 。从 图 中 容易 如 看 出 : 系统 主要 由终端 、 此 数据 处 理 组 件 、 位通 信 定

( 址解码模块) 地

数 据 采 集 模 块

图 2 FP GA 软 件 流 程 图

图 3 地 址 解 析 模 块

从 图 2中 较 易 看 出 , P F GA 与 AD P B 5 3连 S —F3

表 1 地 址 解 析 表

地 址 低 四位

0 0 00

0 001 O O O1 O O11

的相 应 模 块 选 择 情 况 。

西 悦 , 一 雠 j 一

一

接 口模 块 的 F GA 软 件 流 程 如 图 2 示 。 P 所

一。… 。 。 一 一~~

一

地 址 总 线 ≥ 片 选 信 号 线

A D D RESS ECO D E D

数 据 发 送 模 块 门 限设 置 模 块

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ADI创新设计竞赛

创

意

书

项目名称:基于嵌入式ADSP-BF533的实时先天性心脏病心音分析处理系统

参赛学校:(如实填写)

参赛队员:(如实填写)

参赛项目:基于嵌入式ADSP-BF533的实时先天性心脏病心音分析处理系统参赛队员情况表:

所采用芯片:ADSP-BF533SKBC600,AD8220,AD8618,AD8544,AD7792等

项目预算:该项目总的研制费用约为 3330 元,其中包括外协装配费以及各元器件材料费(详细清单见下表)

内容要求:所有参赛申请必须为一个基本完整的设计。

设计方案在3000字左右方案须包含以下内容:

1、设计目标:描述所设计的项目;

2、系统框图:所设计项目的框图,图中标明个各关键部分,并附上简单说明;

3、所采用芯片型号及初步资金预算;。