EDA工程实践报告附录电路图 (1)

EDA实验报告(DOC)(word文档良心出品)

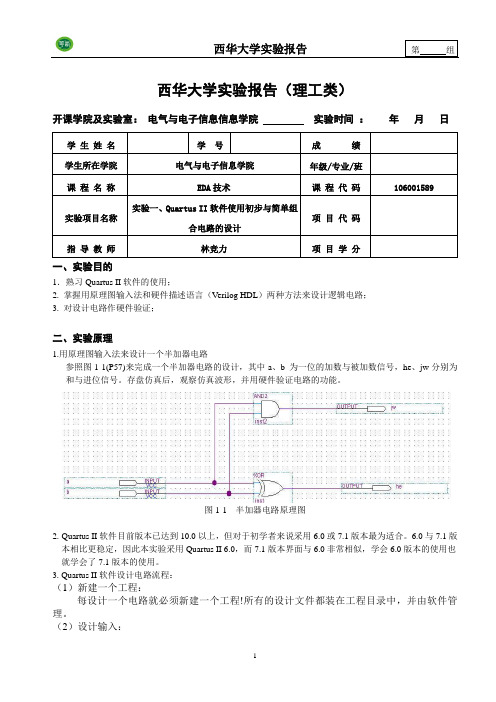

西华大学实验报告西华大学实验报告(理工类)开课学院及实验室:电气与电子信息信息学院实验时间:年月日学生姓名学号成绩学生所在学院电气与电子信息学院年级/专业/班课程名称EDA技术课程代码106001589 实验项目名称实验一、Quartus II软件使用初步与简单组合电路的设计项目代码指导教师林竞力项目学分一、实验目的1.熟习Quartus II软件的使用;2. 掌握用原理图输入法和硬件描述语言(Verilog HDL)两种方法来设计逻辑电路;3. 对设计电路作硬件验证;二、实验原理1.用原理图输入法来设计一个半加器电路参照图1-1(P57)来完成一个半加器电路的设计,其中a、b 为一位的加数与被加数信号,he、jw分别为和与进位信号。

存盘仿真后,观察仿真波形,并用硬件验证电路的功能。

图1-1 半加器电路原理图2.Quartus II软件目前版本已达到10.0以上,但对于初学者来说采用6.0或7.1版本最为适合。

6.0与7.1版本相比更稳定,因此本实验采用Quartus II 6.0,而7.1版本界面与6.0非常相似,学会6.0版本的使用也就学会了7.1版本的使用。

3. Quartus II软件设计电路流程:(1)新建一个工程:每设计一个电路就必须新建一个工程!所有的设计文件都装在工程目录中,并由软件管理。

(2)设计输入:第组告诉软件你要设计的电路是什么。

A.原理图设计方法-----用原理图编辑器画出电路图。

B.本文输入-----用文本编辑器采用硬件语言描述电路(电路主流设计方式)。

(3)编译将设计电路的功能与PLD芯片结合,并提取出仿真所需的时序参数。

(4)仿真软件验证电路功能是否实现。

(5)编程、配置与硬件测试用下载电缆完成器件的编程与配置,做硬件测试。

原理图输入法设计半加器电路与描述语言设计3-8译码器区别在于流程的第二步设计输入。

三、实验设备、仪器及材料电脑、EDA软件(Quartus II)、实验箱、下载电缆、连接导线。

EDA实验报告

EDA 实验报告实验一:组合电路的设计实验内容是对2选1多路选择器VHDL 设计,它的程序如下:ENTITY mux21a ISPORT ( a, b : IN BIT; s : IN BIT; y : OUT BIT ); END ENTITY mux21a;ARCHITECTURE one OF mux21a IS SIGNAL d,e : BIT; BEGIN d <= a AND (NOT S) ; e <= b AND s ; y <= d OR e ;END ARCHITECTURE one ;Mux21a 仿真波形图以上便是2选1多路选择器的VHDL 完整描述,即可以看成一个元件mux21a 。

mux21a 实体是描述对应的逻辑图或者器件图,图中a 和b 分别是两个数据输入端的端口名,s 为通道选择控制信号输入端的端口名,y 为输出端的端口名。

Mux21a 结构体可以看成是元件的内部电路图。

最后是对仿真得出的mux21a 仿真波形图。

Mux21a 实体Mux21a 结构体实验二:时序电路的设计实验内容D触发器的VHDL语言描述,它的程序如下:LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY DFF1 ISPORT (CLK : IN STD_LOGIC ;D : IN STD_LOGIC ;Q : OUT STD_LOGIC );END ;D触发器ARCHITECTURE bhv OF DFF1 ISBEGINPROCESS (CLK)BEGINIF CLK'EVENT AND CLK = '1'THEN Q <= D ;END IF;END PROCESS ;END bhv;D触发器的仿真波形图最简单并最具代表性的时序电路是D触发器,它是现代可编程ASIC设计中最基本的时序元件和底层元件。

EDA实习报告

EDA技术及其应用实训报告学院:电气与控制工程学院班级:自动化1202班姓名:李锦涛学号: 27指导老师:杨占社许琼时间:2015年1月15日电子电路EDA实训一、课程设计的目的及任务EDA课程设计是工科院校电类专业学生进行的一次较全面的设计能力训练实践课程。

通过本课程设计重点掌握一种EDA 软件--Multisim软件在模拟电路和数字电路的设计和仿真应用,训练学生综合运用学过的电子电路的基本知识,独立设计比较复杂的电路的能力。

软件平台是NI Multisim,便于开展综合性的设计和实验,有利于培养综合分析能力、开发和创新的能力。

通过课程设计,学生要掌握使用EDA工具设计电路的方法,包括图形设计输入、编译、软件仿真和分析等全过程。

1.培养理论联系实际的设计思想,训练综合运用电子设计自动化和有关先修课程的理论,结合生产实际分析和解决工程实际问题的能力,巩固、加深和扩展有关电子电路设计方面的知识。

2.通过系统学习NI Multisim,利用软件的方法虚拟电子与电工元器件,虚拟电子与电工仪器和仪表,制定设计方案实现原理电路设计、电路功能测试,仿真和分析,达到掌握电子电路分析和设计全过程和实验。

3.进行设计基本技能的训练。

结合所学电工电子理论进行软件电路设计,熟悉和运用设计资料以及使用经验数据、进行经验估算和处理数据的分析和设计能力。

二、课程设计的基本要求通过学习与实践,使学生接触、了解、进而初步掌握先进的电子系统设计技术,学习基于NI Multisim EDA软件的一般方法和设计思想,并培养学生的抽象思维能力和创新意识;提高学生学习应用电子技术课程知识解决实际问题的能力,锻炼学生应用EDA解决小型系统设计的能力。

1、通过课程设计使学生能熟练掌握EDA软件(NI Multisim)的使用方法,能熟练进行设计输入、管脚分配、仿真、分析等过程。

2、通过课程设计使学生能利用EDA软件进行电子技术综合问题的设计。

EDA实验报告

实验1 Max+plusⅡ软件的使用一、实验目的:1、学习Max+plusⅡ的设计流程全过程,分别采用VHDL和原理图输入方式设计一个简单的三人表决器,学习简单组合电路的设计、仿真。

2、了解VHDL程序的基本结构。

二、实验条件1、PC机一台。

2、开发软件:Max+plusⅡ。

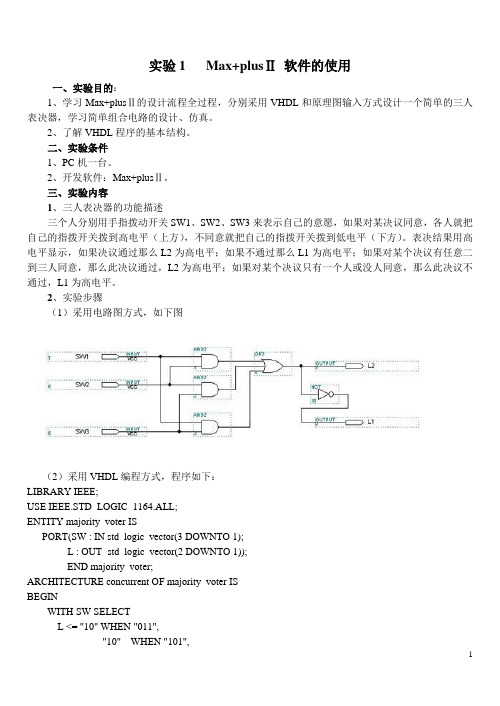

三、实验内容1、三人表决器的功能描述三个人分别用手指拨动开关SW1、SW2、SW3来表示自己的意愿,如果对某决议同意,各人就把自己的指拨开关拨到高电平(上方),不同意就把自己的指拨开关拨到低电平(下方)。

表决结果用高电平显示,如果决议通过那么L2为高电平;如果不通过那么L1为高电平;如果对某个决议有任意二到三人同意,那么此决议通过,L2为高电平;如果对某个决议只有一个人或没人同意,那么此决议不通过,L1为高电平。

2、实验步骤(1)采用电路图方式,如下图(2)采用VHDL编程方式,程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY majority_voter ISPORT(SW : IN std_logic_vector(3 DOWNTO 1);L : OUT std_logic_vector(2 DOWNTO 1));END majority_voter;ARCHITECTURE concurrent OF majority_voter ISBEGINWITH SW SELECTL <= "10" WHEN "011","10" WHEN "101","10" WHEN "110","10" WHEN "111","01" WHEN OTHERS;END concurrent;。

四、仿真结果:五、结论通过仿真波形可以看出三人表决器的图形方式和VHDL编程两种方式的正确性。

eda课程设计报告

eda课程设计报告一、课程目标知识目标:1. 学生能理解EDA(电子设计自动化)的基本概念,掌握EDA工具的使用方法。

2. 学生能运用EDA软件进行电路设计与仿真,理解并掌握数字电路的设计原理。

3. 学生了解并掌握基础的硬件描述语言(如VHDL/Verilog),能完成简单的数字系统设计。

技能目标:1. 学生通过EDA软件的操作,培养电子电路设计、仿真与验证的实际操作能力。

2. 学生通过小组合作完成设计项目,提高团队协作与沟通技巧。

3. 学生能够运用所学知识解决实际问题,具备一定的创新意识和动手能力。

情感态度价值观目标:1. 学生在EDA课程学习中,培养对电子科学技术的兴趣和探究精神。

2. 学生通过课程实践,增强自信心和成就感,激发进一步学习的动力。

3. 学生在学习过程中,树立正确的工程伦理观念,认识到技术发展对社会的责任和影响。

课程性质:本课程为电子信息工程及相关专业高年级学生的专业核心课程,旨在通过理论与实践相结合的教学,提高学生的电子设计能力。

学生特点:学生已具备一定的电子技术基础,具有较强的学习能力和实践欲望,对新技术和新工具充满好奇心。

教学要求:结合学生特点,注重培养实际操作能力,鼓励学生创新思维,提高解决实际问题的能力。

通过课程目标分解,确保学生在知识、技能和情感态度价值观方面的全面成长。

后续教学设计和评估将以此为基础,关注学生的学习成果。

二、教学内容根据课程目标,教学内容分为以下三个模块:1. EDA基本概念与工具使用- 教材章节:第一章 EDA技术概述,第二章 EDA工具简介- 内容列举:EDA发展历程,常用EDA软件介绍,软件安装与配置,基本操作流程。

2. 数字电路设计与仿真- 教材章节:第三章 数字电路设计基础,第四章 仿真技术- 内容列举:数字电路设计原理,EDA软件电路设计流程,仿真参数设置,波形分析与验证。

3. 硬件描述语言与数字系统设计- 教材章节:第五章 硬件描述语言,第六章 数字系统设计实例- 内容列举:硬件描述语言基础,VHDL/Verilog语法要点,简单数字系统设计方法,设计实例分析与实操。

电子线路EDA实验报告

电子线路E D A实验报告-CAL-FENGHAI.-(YICAI)-Company One1实验一五人表决器的设计一、实验目的1.了解和初步掌握ISPLENVER软件的基本操作方法,Abel语言的编写。

2.加深电路设计的概念以及了解计算机辅助设计分析的过程。

二、实验内容及步骤本实验要求利用ISPLEVER软件完成对五人表决器的设计及仿真,表决的规则是:多数胜少数。

分析题意,我们可以知道此次仿真应有五个输入端口,一个输出端口。

分别设置其A、B、C、D、E为输入端口,F为输出端口。

可分析:五人中任意三人通过则表决通过,故得到其逻辑表达式为:F=ABC+ABD+ABE+ACD+ACE+ADE+BCD+BCE+BDE+CDE实验步骤1、打开IPSPLEVER软件,新建一个项目,命名为vote.syn。

2、在新建项目的基础上新建一个原理图文件,命名为vote51.sch。

运用软件按绘制原理图如下所示:图1:五人表决器原理图3、在顶层原理图的基础上,为模块编写ABEL语言程序,原理图中建立了V3模块,新建立一个程序V3.abl文件。

MODULE V3A,B,C,D,E PIN;F PIN ISTYPE 'com';EQUATIONSF=A&B&C#A&B&D#A&B&E#A&C&D#A&C&E#A&D&E#B&C&D#B&C&E #B&D&E#C&D&E;END4、编写此项目的仿真文件程序vote50.abv得到:MODULE vote50A,B,C,D,E,F PIN;X=.X.;TEST_VECTORS([A,B,C,D,E]->[F])[1,1,1,1,1]->[X];[1,1,0,1,1]->[X];[1,1,0,0,1]->[X];[1,1,0,0,0]->[X];[0,0,0,0,1]->[X];[0,0,0,0,0]->[X];END5、对此项目文件进行仿真,得到仿真结果如图:图2:实验结果仿真分析三、实验结果分析本次实验为五人表决器的设计,要求A、B、C、D、E五个输入中不少于三个为1,那么实验结果输出即为1。

EDA实验报告含结果图

EDA电子课程实验报告专业:班级:姓名:学号:实验一四人表决器一实验目的1、熟悉Quartus II软件的使用。

2、熟悉EDA-IV实验箱。

3、熟悉EDA开发的基本流程。

二硬件需求1、RC-EDA-IV型实验箱一台;2、RC-EDA-IV型实验箱配套USB-Blaster下载器一个;3、PC机一台。

三实验原理所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

四人表决器顾名思义就是由四个人来投票,当同意的票数大于或者等于3人时,则认为同意;反之,当否决的票数大于或者等于2人时,则认为不同意。

实验中用4个拨挡开关来表示4个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

四实验内容VHDL程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--------------------------------------------------------------------entity EXP3 isport(k1,K2,K3,K4 : in std_logic;ledag : out std_logic_vector(3 downto 0);m_Result : out std_logic);end EXP3;--------------------------------------------------------------------architecture behave of EXP3 issignal K_Num : std_logic_vector(2 downto 0); signal K1_Num,K2_Num: std_logic_vector(2 downto 0); signal K3_Num,K4_Num: std_logic_vector(2 downto 0);beginprocess(K1,K2,K3,K4)beginK1_Num<='0'&'0'&K1;K2_Num<='0'&'0'&K2;K3_Num<='0'&'0'&K3;K4_Num<='0'&'0'&K4;end process;process(K1_Num,K2_Num,K3_Num,K4_Num,)beginK_Num<=K1_Num+K2_Num+K3_Num+K4_Num;end process;process(K_Num) beginif(K_Num>2) thenm_Result<='1';elsem_Result<='0';end if;end process;end behave;实验电路实验二格雷码转换一实验目的1、了解格雷码变换的原理。

EDA实验及程序原理图

实验四原理图实验五:Light实验library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity light isport(clk1: in std_logic;light: buffer std_logic_vector(11 downto 0)); end light;architecture behv of light isconstant len: integer:=11;signal banner: std_logic:='0';signal clk,clk2: std_logic;beginclk<=(clk1 and banner) or (clk2 and not banner);process(clk1)beginif clk1'event and clk1='1' thenclk2<=not clk2;end if;end process;process(clk)variable flag: bit_vector(2 downto 0):="000";beginif clk'event and clk='1' thenif flag="000" thenlight<='1' & light(len downto 1);if light(1)='1' thenflag:="001";end if;elsif flag="001" thenlight<=light(len-1 downto 0) & '0';if light(10)='0' thenflag:="010";end if;elsif flag="010" thenlight(len downto 6)<=light(len-1 downto 6)&'1';light(len-6 downto 0)<='1'&light(len-6 downto 1);if light(1)='1' thenflag:="011";end if;elsif flag="011" thenlight(len downto 6)<='0'&light(len downto 7);light(len-6 downto 0)<=light(len-7 downto 0)&'0';if light(2)='0' thenflag:="100";end if;elsif flag="100" thenlight(len downto 6)<='1'&light(len downto 7);light(len-6 downto 0)<='1'&light(len-6 downto 1);if light(1)='1' thenflag:="101";end if;elsif flag="101" thenlight<="000000000000";flag:="111";elsif flag="111" thenbanner<=not banner;flag:="000";end if;end if;end process;end behv;实验结构框图LED阵列结构--元件例化library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity ledall isport(clkin :in std_logic;outera:out std_logic_vector(15 downto 0); outerb:out std_logic_vector(3 downto 0));end ledall;architecture beh of ledall iscomponent pinport(f1m :in std_logic;f800 :out std_logic);end component;component source1port(clk :in std_logic;outer:out std_logic_vector(7 downto 0));end component;component source2port(clk :in std_logic;iner :in std_logic_vector(3 downto 0);outer:out std_logic_vector(3 downto 0));end component;component rom1port(address:in STD_LOGIC_VECTOR (7 DOWNTO 0);inclock:in STD_LOGIC ;q :out STD_LOGIC_VECTOR (15 DOWNTO 0));end component;signal sig0,sig1,sig2:std_logic;signal temp:std_logic_vector(7 downto 0);beginsig1<=not sig0;sig2<=not sig0;U1:source1 port map(sig0,temp(7 downto 0));U2:source2 port map(sig1,temp(3 downto 0),outerb(3 downto 0)); U3:rom1 port map(temp(7 downto 0),sig2,outera(15 downto 0)); U4:pin port map(clkin,sig0);end beh;--分频程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity pin isport(f1m:in std_logic;f800:out std_logic);end pin;architecture behave of pin issignal Count : integer range 0 to 4999;beginDivideCLK :process(f1m)--对1M的信号1000分频 1KHzbeginif (f1m'event and f1m = '1')thenif Count<2499 then f800<='0';Count<=Count+1;elsif Count<4999 then f800<= '1';Count <= Count+1;elsif Count>=4999 then f800<='0';Count<=0; end if;end if;end process;end behave;ROM1程序:LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY rom1 ISPORT(address : IN STD_LOGIC_VECTOR (7 DOWNTO 0);inclock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (15 DOWNTO 0));END rom1;ARCHITECTURE SYN OF rom1 ISSIGNAL sub_wire0 : STD_LOGIC_VECTOR (15 DOWNTO 0);COMPONENT lpm_romGENERIC (lpm_width : NATURAL;lpm_widthad : NATURAL;lpm_address_control : STRING;lpm_outdata : STRING;lpm_file : STRING);PORT (address : IN STD_LOGIC_VECTOR (7 DOWNTO 0);inclock : IN STD_LOGIC ;q : OUT STD_LOGIC_VECTOR (15 DOWNTO 0));END COMPONENT;BEGINq <= sub_wire0(15 DOWNTO 0);lpm_rom_component : lpm_romGENERIC MAP (LPM_WIDTH => 16,LPM_WIDTHAD => 8,LPM_ADDRESS_CONTROL => "REGISTERED",LPM_OUTDATA => "UNREGISTERED",LPM_FILE => "rom1.mif")PORT MAP (address => address,inclock => inclock,q => sub_wire0);END SYN;rom1:rom1_inst : rom1 PORT MAP(address => address_sig,inclock => inclock_sig,q => q_sig);Soucel:library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;entity source isport(clk:in std_logic;outer:out integer range 0 to 255);end source;architecture behave of source isbeginprocess(clk)variable temp:integer range 0 to 255;beginif(clk'event and clk='1')then temp:=temp+1; end if;outer<=temp;end process;end behave;soucel1:--Source1 地址寻址信号library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity source1 isport(clk:in std_logic;outer:out std_logic_vector(7 downto 0));end source1;architecture behave of source1 issignal temp1:std_logic_vector(3 downto 0);--temp1为地址低4位代表一帧数据signal temp2:std_logic_vector(3 downto 0);--temp1为地址高4位代表帧数signal time:integer range 0 to 15;--time为帧循环次数计数每帧扫16遍beginprocess(clk)beginif(clk'event and clk='1')thenif temp1="1111" thenif time<15 then time<=time+1;else time<=0;temp2<=temp2+'1';end if;end if;temp1<=temp1+'1'; --转为下帧数据end if;end process;outer<=temp2 & temp1;end behave;八位十进制频率计实验:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity freq isport(clk :in std_logic;--1Hz 标准时钟fs_in :in std_logic;--被测时钟dout :out std_logic_vector (31 downto 0)--被测时钟频率值);end freq;architecture ex4 of freq issignal clr_cnt :std_logic;--清零测频计数器signal en_cnt :std_logic;--使能测频计数器signal load :std_logic;--加载测量值signal div2clk :std_logic;signal d_temp :std_logic_vector (31 downto 0);--被测时钟频率值缓存器signal c :std_logic_vector (7 downto 0);--进位链component cnt10 isport(clk :in std_logic;--计数时钟clr :in std_logic;--复位ena :in std_logic;--使能qout :out std_logic_vector (3 downto 0);--10进制计数输出car_out :out std_logic --进位);end component;begin--2分频clkprocess(clk)beginif clk'event and clk = '1' thendiv2clk <= not div2clk;end if;end process;--产生控制信号clr_cnt <= '1' when clk = '0' and div2clk = '0' else'0';load <= not div2clk;en_cnt <= div2clk;process(load)beginif load'event and load = '1' thendout <= d_temp;end if;end process;u1 : cnt10 PORT MAP(clk=>fs_in,clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(3 downto 0),car_out=>c(0));u2 : cnt10 port map(clk=>c(0), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(7 downto 4),car_out=>c(1));u3 : cnt10 port map(clk=>c(1), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(11 downto 8),car_out=>c(2));u4 : cnt10 port map(clk=>c(2), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(15 downto 12),car_out=>c(3));u5 : cnt10 port map(clk=>c(3), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(19 downto 16),car_out=>c(4));u6 : cnt10 port map(clk=>c(4), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(23 downto 20),car_out=>c(5));u7 : cnt10 port map(clk=>c(5), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(27 downto 24),car_out=>c(6));u8 : cnt10 port map(clk=>c(6), clr=>clr_cnt,ena=>en_cnt,qout=>d_temp(31 downto 28),car_out=>c(7)); end ex4;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt10 isport(clk :in std_logic;--计数时钟clr :in std_logic;--复位ena :in std_logic;--使能qout :out std_logic_vector (3 downto 0);--10进制计数输出car_out :out std_logic --进位);end cnt10;architecture ex5 of cnt10 issignal qout_t :std_logic_vector (3 downto 0);begin--10进制计数process(clk,clr)beginif clr = '1' thenqout_t <= x"0";elsif clk'event and clk = '1' thenif ena = '1' thenif qout_t < 9 thenqout_t <= qout_t + '1';elseqout_t <= x"0";end if;end if;end if;end process;--产生进位car_out <= '1' when qout_t = x"9" else'0';qout <= qout_t;end ex5;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity LED isport(din :in std_logic_vector (3 downto 0);dout :out std_logic_vector (7 downto 0) );end entity;architecture ex3 of LED isbeginprocess(din)begincase din iswhen "0000"=> dout <= "00111111";--"0"when "0001"=> dout <= "00000110";--"1"when "0010"=> dout <= "01011011";--"2"when "0011"=> dout <= "01001111";--"3"when "0100"=> dout <= "01100110";--"4"when "0101"=> dout <= "01101101";--"5"when "0110"=> dout <= "01111101";--"6"when "0111"=> dout <= "00000111";--"7"when "1000"=> dout <= "01111111";--"8"when "1001"=> dout <= "01101111";--"9"when "1010"=> dout <= "01110111";--"a"when "1011"=> dout <= "01111100";--"b"when "1100"=> dout <= "00111001";--"c"when "1101"=> dout <= "01011110";--"d"when "1110"=> dout <= "01111001";--"e"when "1111"=> dout <= "01110001"; --"f"when others => dout <= "00000000";end case;end process;end architecture;数字时钟原理图library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clock isport(clk:in std_logic;--时钟输入20MHzclr:in std_logic;--清零端en:in std_logic;--暂停信号mode:in std_logic;--控制信号,用于选择模式inc:in std_logic;--置数信号seg7:out std_logic_vector(6 downto 0);--7段显示控制信号scan:out std_logic_vector(5 downto 0));--数码管地址选择信号end;architecture one of clock issignal state:std_logic_vector(1 downto 0);--定义4种状态signal qhh,qhl,qmh,qml,qsh,qsl:std_logic_vector(3 downto 0);--小时、分、秒的高位和地位signal data:std_logic_vector(3 downto 0);signal cnt:integer range 0 to 5;--扫描数码管的计数器signal clk1khz,clk1hz,clk2hz:std_logic;--1kHz、1Hz、2Hz的分频信号signal blink:std_logic_vector(2 downto 0);--闪烁信号signal inc_reg:std_logic;signal sec,min:integer range 0 to 59;signal hour:integer range 0 to 23;beginprocess(clk)--20000分频,产生1kHz信号,用于扫描数码管variable count:integer range 0 to 9999;beginif clk'event and clk='1' thenif count=9999 then clk1khz<=not clk1khz;count:=0;else count:=count+1;end if;end if;end process;process(clk1khz)--1000分频,产生1Hz信号,用于计时variable count:integer range 0 to 499;beginif clk1khz'event and clk1khz='1' thenif count=499 then clk1hz<=not clk1hz;count:=0;else count:=count+1;end if;end if;end process;process(clk1khz)--500分频,产生2Hz信号,用于数码管闪烁variable count:integer range 0 to 249;beginif clk1khz'event and clk1khz='1' thenif count=249 then clk2hz<=not clk2hz;count:=0;else count:=count+1;end if;end if;end process;process(mode,clr)--模式转换beginif clr='1' then state<="00";elsif mode'event and mode='1' thenstate<=state+1;end if;end process;process(clk1hz,state,en,clr,hour,sec,min)--状态控制beginif en='1' thenhour<=hour;min<=min;sec<=sec;elsif clr='1' thenhour<=0;min<=0;sec<=0;elsif clk1hz'event and clk1hz='1' then case state iswhen "00"=> --模式0,正常计时if sec=59 then sec<=0;if min=59 then min<=0;if hour=23 then hour<=0;else hour<=hour+1;end if;else min<=min+1;end if;else sec<=sec+1;end if;when "01"=> --模式1,设定小时时间if inc='1' thenif inc_reg='0' then inc_reg<='1';if hour=23 then hour<=0;else hour<=hour+1;end if;end if;else inc_reg<='0';end if;when "10"=> --模式2,设定分钟时间if inc='1' thenif inc_reg='0' then inc_reg<='1';if min=59 then min<=0;else min<=min+1;end if;end if;else inc_reg<='0';end if;when "11"=> --模式3,设定秒钟时间if inc='1' thenif inc_reg='0' then inc_reg<='1';if sec=59 then sec<=0;else sec<=sec+1;end if;end if;else inc_reg<='0';end if;end case;end if;end process;process(state,clk2hz)--当进行时间设定时,令数码管闪烁begincase state iswhen"00"=>blink<="000";when"01"=>blink<=(2=>clk2hz,others=>'0');when"10"=>blink<=(1=>clk2hz,others=>'0');when"11"=>blink<=(0=>clk2hz,others=>'0');when others=>null;end case;end process;process(sec)--秒计数的十进制转BCD码begincase sec iswhen 0|10|20|30|40|50=>qsl<="0000";when 1|11|21|31|41|51=>qsl<="0001";when 2|12|22|32|42|52=>qsl<="0010";when 3|13|23|33|43|53=>qsl<="0011";when 4|14|24|34|44|54=>qsl<="0100";when 5|15|25|35|45|55=>qsl<="0101";when 6|16|26|36|46|56=>qsl<="0110";when 7|17|27|37|47|57=>qsl<="0111";when 8|18|28|38|48|58=>qsl<="1000";when 9|19|29|39|49|59=>qsl<="1001";when others=>null;end case;case sec iswhen 0|1|2|3|4|5|6|7|8|9=>qsh<="0000";when 10|11|12|13|14|15|16|17|18|19=>qsh<="0001";when 20|21|22|23|24|25|26|27|28|29=>qsh<="0010";when 30|31|32|33|34|35|36|37|38|39=>qsh<="0011";when 40|41|42|43|44|45|46|47|48|49=>qsh<="0100";when 50|51|52|53|54|55|56|57|58|59=>qsh<="0101";when others=>null;end case;end process;process(min)--分计数的十进制转BCD码begincase min iswhen 0|10|20|30|40|50=>qml<="0000";when 1|11|21|31|41|51=>qml<="0001";when 2|12|22|32|42|52=>qml<="0010";when 3|13|23|33|43|53=>qml<="0011";when 4|14|24|34|44|54=>qml<="0100";when 5|15|25|35|45|55=>qml<="0101";when 6|16|26|36|46|56=>qml<="0110";when 7|17|27|37|47|57=>qml<="0111";when 8|18|28|38|48|58=>qml<="1000";when 9|19|29|39|49|59=>qml<="1001";when others=>null;end case;case min iswhen 0|1|2|3|4|5|6|7|8|9=>qmh<="0000";when 10|11|12|13|14|15|16|17|18|19=>qmh<="0001";when 20|21|22|23|24|25|26|27|28|29=>qmh<="0010";when 30|31|32|33|34|35|36|37|38|39=>qmh<="0011";when 40|41|42|43|44|45|46|47|48|49=>qmh<="0100";when 50|51|52|53|54|55|56|57|58|59=>qmh<="0101";when others=>null;end case;end process;process(hour)--小时计数的十进制转BCD码begincase hour iswhen 0|10|20=>qhl<="0000";when 1|11|21=>qhl<="0001";when 2|12|22=>qhl<="0010";when 3|13|23=>qhl<="0011";when 4|14=>qhl<="0100";when 5|15=>qhl<="0101";when 6|16=>qhl<="0110";when 7|17=>qhl<="0111";when 8|18=>qhl<="1000";when 9|19=>qhl<="1001";when others=>null;end case;case hour iswhen 0|1|2|3|4|5|6|7|8|9=>qhh<="0000";when 10|11|12|13|14|15|16|17|18|19=>qhh<="0001";when 20|21|22|23=>qhh<="0010";when others=>null;end case;end process;process(clk1khz)--数码管动态扫描计数beginif clk1khz'event and clk1khz='1' thenif cnt=5 then cnt<=0;else cnt<=cnt+1;end if;end if;end process;process(cnt,qhh,qhl,qmh,qml,qsh,qsl,blink)begincase cnt iswhen 0=>data<=qsl or (blink(0)&blink(0)&blink(0)&blink(0));scan<="000001";when 1=>data<=qsh or (blink(0)&blink(0)&blink(0)&blink(0));scan<="000010";when 2=>data<=qml or (blink(1)&blink(1)&blink(1)&blink(1));scan<="000100";when 3=>data<=qmh or (blink(1)&blink(1)&blink(1)&blink(1));scan<="001000";when 4=>data<=qhl or (blink(2)&blink(2)&blink(2)&blink(2));scan<="010000";when 5=>data<=qhh or (blink(2)&blink(2)&blink(2)&blink(2));scan<="100000";when others=>null;end case;end process;process(data)--7段译码begincase data iswhen "0000"=>seg7<="1111110";when "0001"=>seg7<="0110000";when "0010"=>seg7<="1101101";when "0011"=>seg7<="1111001";when "0100"=>seg7<="0110011";when "0101"=>seg7<="1011011";when "0110"=>seg7<="1011111";when "0111"=>seg7<="1110000";when "1000"=>seg7<="1111111";when "1001"=>seg7<="1111011";when others=>seg7<="0000000";end case;end process;end;。

eda实验报告完整版

EDA实验报告焦中毅201300121069实验1 4选1数据选择器的设计一、实验目的1.学习EDA软件的基本操作。

2.学习使用原理图进行设计输入。

3.初步掌握器件设计输入、编译、仿真和编程的过程。

4.学习实验开发系统的使用方法。

二、实验仪器与器材1.EDA开发软件一套2.微机一台3.实验开发系统一台4.打印机一台三、实验说明本实验通过使用基本门电路完成4选1数据选择器的设计,初步掌握EDA设计方法中的设计输入、编译、综合、仿真和编程的过程。

实验结果可通过实验开发系统验证,在实验开发系统上选择高、低电平开关作为输入,选择发光二极管显示输出电平值。

本实验使用Quartus II 软件作为设计工具,要求熟悉Quartus II 软件的使用环境和基本操作,如设计输入、编译和适配的过程等。

实验中的设计文件要求用原理图方法输入,实验时,注意原理图编辑器的使用方法。

例如,元件、连线、网络名的放置方法和放大、缩小、存盘、退出等命令的使用。

学会管脚锁定以及编程下载的方法等。

四、实验要求1.完成4选1数据选择器的原理图输入并进行编译;2.对设计的电路进行仿真验证;3.编程下载并在实验开发系统上验证设计结果。

五、实验结果4选1数据选择器的原理图:仿真波形图:管脚分配:实验2 四位比较器一、实验目的1.设计四位二进制码比较器,并在实验开发系统上验证。

2.学习层次化设计方法。

二、实验仪器与器材1.EDA 开发软件 一套 2.微机 一台 3.实验开发系统 一台 4.打印机 一台 5.其它器件与材料 若干 三、实验说明本实验实现两个4位二进制码的比较器,输入为两个4位二进制码0123A A A A 和0123B B B B ,输出为M (A=B ),G (A>B )和L (A<B )(如图所示)。

用高低电平开关作为输入,发光二极管作为输出,具体管脚安排可根据试验系统的实际情况自行定义。

四、实验要求1.用硬件描述语言编写四位二进制码 比较器的源文件; 2.对设计进行仿真验证; 3.编程下载并在实验开发系统上进行 硬件验证。

EDA实验实验报告2

EDA实验实验报告学号:姓名:彭文勇院系:微电子技术系专业:嵌入式教师:李海2010年12月实验一一位全加器的设计实验地点:第二实验楼405同组人员:孙腾坤一、实验目的通过次实验我们逐步了解、熟悉和掌握FPGA开发软件Quartus II 的使用及Verilog HDL的编程方法。

学习用Verilog HDL语言以不同的方式来描述1位全加器及电路的设计仿真和硬件测试。

二、实验原理和内容本实验的内容是建立一个1位全加器。

具体内容包括:(1)使用Quartus II建立工程、编写程序;(2)进行波形仿真验证;(3)进行硬件测试。

通过SmartSOPC试验箱上的按键KEY1~KEY3输入信号,分别为A、B和cin,并通过LED1~LED3指示相应的状态。

输出Sum和cout通过LED7和LED8指示(灯亮表示输入或输出为“1”)。

三、实验步骤(1)启动Quartus II建立一个空白工程,然后命名为full_add。

(2)新建Verilog HDL源文件full_add.v,输入程序代码并保存,然后进行综合编译。

若在编译过程中发现错误,则找出并更正错误,直至编译成功为止,并生成图形符号文件full_add.bdf。

(3)波形仿真验证。

(4)新建图形设计文件命名为full_add.bdf并保存。

微电子技术系(5)选择目标器件并对相应的引脚进行锁定,我们选Altera公司Cyclone系列的EP1C6Q240C8芯片,引脚锁定方法参考实验书后面的附录A引脚分配。

将为使用的引脚设置为三态输入(一定要设置否则可能损坏芯片)。

(6)将full_add.bdf设置为顶层实体。

对该工程文件进行全程便已处理。

若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

(7)将跳线短接帽调解到JP6的KEY1~KEY3、LED0~LED2、LED6和LED7,使KEY1~KEY3、LED1~LED3、LED7、LED8与芯片对应的引脚相连。