DM9000网口收发数调试程序v001

驱动网卡芯片DM9000调试过程及其具体的单片机程序

驱动网卡芯片D M9000调试过程及其具体的单片机程序(总25页)本页仅作为文档封面,使用时可以删除This document is for reference only-rar21year.March驱动网卡芯片DM9000A的过程及具体驱动程序一、电路连接DM9000E网卡芯片支持8位、16位、32位模式的处理器,通过芯片引脚EEDO(65脚)和WAKEUP(79脚)的复位值设置支持的处理器类型,如16位处理器只需将这两个引脚接低电平即可,其中WAKEUP内部有60K下拉电阻,因此可悬空该引脚,或作为网卡芯片唤醒输出用。

其它型号请参考相应的数据手册。

图1 DM9000引脚如图所示,对处理器驱动网卡芯片来说,我们比较关心的有以下几个引脚:IOR、IOW、AEN、CMD(SA2)、INT、RST,以及数据引脚SD0-SD15-SD31和地址引脚SA4-SA9。

其中,地址引脚配合AEN引脚来选通该网卡芯片,对于大多数的应用来说没有意义,因为在我们的应用中一般只用一个网卡芯片,而这些地址引脚主要用于在多网卡芯片环境下选择其中之一。

DM9000工作的默认基地址为0x300,这里我们按照默认地址选择,将SA9、SA8接高电平,SA7-DA4接低电平。

多网卡环境可以根据TXD0-TXD3配置SA4-SA7来选择不同的网卡,这里不做介绍,有兴趣的朋友请参考应用手册和数据手册。

数据引脚SD0-SD31则根据前面所讲的配置处理器模式与处理器的数据总线进行选择连接即可,没用到的引脚悬空。

那么,除了地址、数据引脚外,剩下的与处理器有关引脚对我们来说及其重要了,而与处理器无关的引脚,只需按照应用手册连接即可。

IOR和IOW是DM9000的读写选择引脚,低电平有效,即低电平时进行读(IOR)写(IOW)操作;AEN是芯片选通引脚,低电平有效,该引脚为低时才能进行读写操作;CMD的命令/数据切换引脚,低电平时读写命令操作,高电平时读写数据操作。

DM9000A中文手册完整版

DAVICOM Semiconductor, Inc.DM9000AEthernet Controllerwith General Processor InterfaceDATA SHEET(中文数据手册)PreliminaryVersion: DM9000A-DS-P03Apr. 21, 2005目录1. 概述 (5)2. 模块图 (5)3. 特性 (5)4. 引脚配置 (6)4.1(16位模式) (6)4.2(8位模式) (7)5. 引脚描述 (7)5.1处理器接口 (7)5.1.1 8位模式引脚 (8)5.2 EEPROM接口 (8)5.3时钟引脚 (9)5.4 LED接口 (9)5.5 10/100 PHY/Fiber (9)5.6其他 (10)5.7电源引脚 (10)5.8捆绑引脚列表(Strap pins table) (10)6. 控制和状态寄存器列表 (10)6.1网络控制寄存器(NCR) (12)6.2网络状态寄存器(NSR) (13)6.3发送控制寄存器(TCR) (13)6.4数据包1发送状态寄存器1(TSR I) (13)6.5数据包2发送状态寄存器2(TSR II) (14)6.6接收控制寄存器(RCR) (14)6.7接收状态寄存器(RSR) (15)6.8接收溢出计数寄存器(ROCR) (15)6.9背压阈值寄存器(BPTR) (15)6.10流控制阈值寄存器(FCTR) (16)6.11接收/发送流控制寄存器(RTFCR) (16)6.12 EEPROM与PHY控制寄存器(EPCR) (17)6.13 EEPROM与PHY地址寄存器(EPAR) (17)6.14 EEPROM与PHY数据寄存器(EPDRL/EPDRH) (18)6.15唤醒控制寄存器(WCR) (18)6.16物理地址(MAC)寄存器(PAR) (18)6.17多播地址寄存器(MAR) (19)6.18通用目的控制寄存器(GPCR) (19)6.19通用目的寄存器(GPR) (19)6.20 TX SRAM读指针地址寄存器(TRPAL/TRPAH) (20)6.21 RX SRAM写指针地址寄存器(RWPAL/RWPAH) (20)6.22厂家ID寄存器(VID) (20)6.23产品ID寄存器(PID) (20)6.24芯片版本寄存器(CHIPR) (20)6.25发送控制寄存器2(TCR2) (20)6.26操作测试控制寄存器(OCR) (21)6.27特殊模式控制寄存器(SMCR) (21)6.28即将发送控制/状态寄存器(ETXCSR) (22)6.29校验和控制寄存器(TCSCR) (22)6.30接收校验和控制状态寄存器(RCSCSR) (22)6.31内存数据预取读命令寄存器(地址不加1)(MRCMDX) (23)6.32内存数据读命令寄存器(地址不加1)(MRCMDX1) (23)6.33内存数据读命令寄存器(地址加1)(MRCMD) (23)6.34内存数据读地址寄存器(MRRL/ MRRH) (23)6.35内存数据写命令寄存器(地址不加1)(MWCMDX) (23)6.36内存数据写命令寄存器(地址加1)(MWCMD) (24)6.37内存数据写地址寄存器(MWRL/ MWRH) (24)6.38发送数据包长度寄存器(TXPLL/TXPLH) (24)6.39中断状态寄存器(ISR) (24)6.40中断屏蔽寄存器(IMR) (24)7.EEPROM格式 (25)8.PHY寄存器描述 (26)8.1基本模式控制寄存器(BMCR) (27)8.2基本模式状态寄存器(BMSR) (28)8.3 PHY ID标识符寄存器#1(PHYID1) (29)8.4 PHY ID标识符寄存器#2(PHYID1) (29)8.5自动协商通知寄存器(ANAR) (30)8.6自动协商连接对象寄存器(ANLPAR) (31)8.7自动协商扩展寄存器(ANER) (32)8.8 DAVICOM指定配置寄存器(DSCR) (33)8.9 DAVICOM指定配置和状态寄存器(DSCSR) (34)8.10 10BASE-T配置/状态(10BTCSR) (36)8.11掉电控制寄存器(PWDOR) (36)8.12指定配置寄存器(SCR) (37)9. 功能描述 (38)9.1 主机接口(HI) (38)9.2 直接内存访问控制(DMAC) (38)9.3 数据包发送(PT) (38)9.4 数据包接收(PR) (38)9.5 100Base-TX操作 (39)9.5.1 4B5B编码器 (39)9.5.2扰频器(Scrambler) (39)9.5.3 并--串转换 (39)9.5.4 NRZ码到NRZI码转换 (39)9.5.5 NRZI码到MLT-3码转换 (39)9.5.6 MLT-3驱动 (39)9.5.7 4B5B编码 (40)9.6 100Base-TX接收器 (40)9.6.1 信号检测 (41)9.6.2 自适应补偿 (41)9.6.3 MLT-3到NRZI解码 (41)9.6.4 时钟复原模块 (41)9.6.5 NRZI 到NRZ (41)9.6.6 串-并转换 (41)9.6.7 扰频器 (41)9.6.8 编码组对齐模块 (41)9.6.9 4B5B解码 (42)9.7 10Base-T操作 (42)9.8 冲突检测 (42)9.9 载波检测 (42)9.10 自动协商 (42)9.11 省电模式 (42)9.11.1 掉电模式 (43)9.11.2 降低发送损耗模式 (43)10 DC与AC电器特性 (43)10.1 最大绝对额定值 (43)10.1.1 工作条件 (43)10.2 DC电器特性(VDD=3.3V) (44)10.3 AC电器特性与时序 (44)10.3.1 TP接口 (44)10.3.2 晶振/振荡时钟 (44)10.3.3 I/O读时序 (45)10.3.4 I/O写时序 (45)10.3.5 EEPROM接口时序 (46)11应用说明 (46)11.1网络接口信号接线 (46)11.2 10Base-T/100Base-TX自动MDIX应用 (47)11.3 10Base-T/100Base-TX无自动MDIX变压器应用 (47)11.4电源退偶电容 (47)11.5地平面布局 (48)11.6电源平面分割 (49)11.7铁氧体磁珠选择指导 (50)11.8晶振选择指导 (50)12封装信息 (50)13订购信息 (52)DM9000A翻译人:许建华、刘煜、程志成2009-9-1版权:翻译版权归作者三方所有,不得随意传播。

DM9000网卡驱动

DM9000网卡驱动笔记网卡芯片为DM9000,ARM开发板用的是S3C6410,PC机装的是RED HAT ENTERPRISE LINUX 5.5.网卡接入soc上并没有接入到专门的驱动ic上,而是接入到了SROM的控制器上,所以需要配置的寄存器就需要配置SROM的寄存器。

S3C6410支持6页的SROM,DM9000的片选连接到了SROM控制的bank1,地址线连接的是addr2,也就是以后地址线上发出去的数据,第2位为0,数据为地址,第2位为1,数据为数据(这比较难理解)。

根据这样的地址数据的读写,操作DM9000中的寄存器,配置好网卡芯片,arm端封装一个arp请求包,在PC机上用tcpdump命令看能不能接收到如果能接受,网卡配置就算比较成功了附上源码:#include "up.h"#define INDEX (0x18000000)#define DATA (0x18000004)int (*printf)(char *, ...) = 0x57e11d4c;void (*udelay)(int ) = 0x57e00a98;struct ethhdr{unsigned char dest[6];unsigned char source[6];unsigned short type;};struct arphdr{unsigned short hw_type;unsigned short pro_type;unsigned char hw_len;unsigned char pro_len;unsigned short op;unsigned char src_mac[6];unsigned char src_ip[4];unsigned char dest_mac[6];unsigned char dest_ip[4];};void write_dm9000(unsigned char reg, unsigned short val); unsigned short read_dm9000(unsigned char reg);void init_dm9000();void send_data(unsigned char *buff, int len);int create_arp(unsigned char *buff);void *memset(void *s, int c, int len);unsigned short htons(unsigned short);int main(){/*set XM0bank1*/SROM_BW = (1 << 4);SROM_BC1 = (4 << 4) | (5 << 16);unsigned char buff[1024] = {0};int len = create_arp(buff);init_dm9000();send_data(buff, len);return 0;}void write_dm9000(unsigned char reg, unsigned short val) {*(unsigned char *)INDEX = reg;*(unsigned short *)DATA = val;}unsigned short read_dm9000(unsigned char reg) {*(unsigned char *)INDEX = reg;unsigned char c = *(unsigned char *)DATA;return c;}void init_dm9000(){//application notes//step 1: p22write_dm9000(0x1f, 0x00);//step 2:write_dm9000(0x00, 0x01);udelay(10);write_dm9000(0x00, 0x00);//step 3:write_dm9000(0x00, (1 << 3));//step 4:write_dm9000(0xff, 0xff);//step 5://step 6:write_dm9000(0x10, 0x11);write_dm9000(0x11, 0x22);write_dm9000(0x12, 0x33);write_dm9000(0x13, 0x44);write_dm9000(0x14, 0x55);write_dm9000(0x15, 0x66);//step 7://step 8:write_dm9000(0x01, (1 << 2) | (1 << 3) | (1 << 5));write_dm9000(0xfe, 0x3f);printf("3\n");//step 9://step 10:write_dm9000(0xff, 0xff);//step 11:write_dm9000(0x05, 0x01);//step 12:}void send_data(unsigned char *buff, int len){//p28://step 1:unsigned char c = read_dm9000(0xfe);if(c >> 7)printf("8 bit mode\n");elseprintf("16 bit mode\n");//step 2*(unsigned char*)INDEX = 0xf8;int tmp = (len + 1) >> 1;int i = 0;for(i=0; i<tmp; i++){*(unsigned short *)DATA = ((unsigned short*)buff)[i];}//step 3write_dm9000(0xfd, (len >> 8) & 0xff);write_dm9000(0xfc, len & 0xff);//step 4write_dm9000(0x02, 0x01);}int create_arp(unsigned char *buff){int len = 0;struct ethhdr *eth = (struct ethhdr *)buff;eth->dest[0] = 0xff;eth->dest[1] = 0xff;eth->dest[2] = 0xff;eth->dest[3] = 0xff;eth->dest[4] = 0xff;eth->dest[5] = 0xff;eth->source[0] = 0x11;eth->source[1] = 0x22;eth->source[2] = 0x33;eth->source[3] = 0x44;eth->source[4] = 0x55;eth->source[5] = 0x66;eth->type = htons(0x0806);struct arphdr *arp = (struct arphdr *)(buff + sizeof(struct ethhdr));arp->hw_type = htons(1);arp->pro_type = htons(0x0800); arp->hw_len = 6;arp->pro_len = 4;arp->op = htons(1);arp->src_mac[0] = 0x11;arp->src_mac[1] = 0x22;arp->src_mac[2] = 0x33;arp->src_mac[3] = 0x44;arp->src_mac[4] = 0x55;arp->src_mac[5] = 0x66;arp->src_ip[0] = 192;arp->src_ip[1] = 168;arp->src_ip[2] = 1;arp->src_ip[3] = 2;arp->dest_mac[0] = 0xff;arp->dest_mac[1] = 0xff;arp->dest_mac[2] = 0xff;arp->dest_mac[3] = 0xff;arp->dest_mac[4] = 0xff;arp->dest_mac[5] = 0xff;arp->dest_ip[0] = 192;arp->dest_ip[1] = 168;arp->dest_ip[2] = 1;arp->dest_ip[3] = 1;len = sizeof(struct ethhdr) + sizeof(struct arphdr);return len;}void *memset(void *s, int c, int len){int i = 0;for(i=0; i<len; i++)((unsigned char *)s)[i] = c;}unsigned short htons(unsigned short data){unsigned short ret = 0;ret = ((data >> 8) & 0xff) | ((data << 8) & 0xff00);return ret;。

三种网卡驱动

· Web动效研究与实践

//PacketPagePointer的定义

#define CS8900_PDATA *(volatile CS8900_REG *)(CS8900_BASE+0x06*CS8900_OFF)

//PacketPageData Port

复制代码

通过如下函数对cs8900a设置

复制代码

驱动关键如下:

读端口与写端口的宏

#define DM9000_outb(d,r) ( *(volatile u8 *)r = d )

#define DM9000_outw(d,r) ( *(volatile u16 *)r = d )

#define DM9000_outl(d,r) ( *(volatile u32 *)r = d )

}

复制代码

其中CS8900_BASE为基址与硬件连接有关。硬件原理图决定在S3C2410的地址空间中,CS8900A的基地址为x19000000。那么在I/O模式下,CS8900A的内部寄存器默认基地址为0x300h,在S3C2410的地址空间中的地址为0x19000300。

#define CS8900_BASE 0x19000300

/* "shutdown" to show ChipID or kernel wouldn't find he cs8900 。。。 */

get_reg_init_bus(PP_ChipID);

}

复制代码

二、rtl8019

RTL8019AS 是高度集成以太网控制器,为了提供完全解决即插即用方案,RTL8019AS 在集成10BASET 收发器,BNC,和AUI 接口之间的自动检测功能。此外,8 条IRQ 总线和16 条基本地址总线为大资源情况下提供了宽松的环境。

dm9000a嵌入式网卡芯片故障调试技术相关

DM9000AEP调试的时候注意事项:1.首先要判断芯片的真假。

常见的方法是读取芯片的ID号。

当然有些工程师朋友的寄存器设置,以及时序设置有问题,读取芯片的ID号就会错。

读取ID是最基本的操作。

2.其次确认芯片无质量问题后,再确定是硬件,还是软件方面的问题。

一般软件方面,问题很容易解决。

硬件问题,需要注意:网络变压器的CT端,一般要接DM9000AEP的管脚2,9脚输出的2.5V,输出的时候一般要加一个稳压电容以及一个滤波电容,稳压电容至少200uf。

另外可以通过10M下是否有连接,来判断网络变压器是否连接正确。

不同的网络变压器,连接电路一般有差异,要注意兼容性。

3.其次发送和接收的几个50欧姆的电阻,电阻值一定要正确,如果不正确,会有丢包现象。

或者网络时断时续。

4.DM9000AEP的datasheet,必须要看,不看的工程师,自己瞎琢磨,一般会耽误时间的。

5.在驱动程序里最好要添加打印信息,打印信息可以反馈硬件的故障,对分析问题,解决问题很有帮助。

6.一般晶振,网络变压器,最好要买真货,如果买到假的,通常很难从电路上分析出问题,通常要经过很长时间的测试,才发现。

最好不要在电子市场买东西,假的东西很多。

亲身经历。

特别是Pluse的H1102很多假冒的。

7.网络变压器的49.9的电阻,不用接任何电源。

8.PWRST复位引脚,如果是通过GPIO控制,应该是下拉电阻,不是上拉电阻。

Davicom高速以太网路晶片1、10/100/1000M 超高速以太网络芯片DM9702 - 超高速以太网络三合一单芯片. (Coming Soon)2、10/100M 高速以太网络芯片DM9000A (DM9000AE/DM9000AEP) - DM9000A Ethernet Controller With General Processor Interface DM9000E - (SMSC LAN91C111 Equivalent)ISA接口高速以太网络三合一单芯片(含 MII / RMII 接口).DM9000K - 研发套件DM9601 - USB接口高速以太网络三合一单芯片.DM9102D - PCI 接口高速以太网络三合一单芯片(Auto-MDIX). 0.25umDM9102A - PCI 接口高速以太网络三合一单芯片. 0.35um3、10/100M 高速以太网络实体层收发器DM9161 - 低功率, 高速以太网络实体层收发器. 48-pin 0.35um.DM9161A - 低功率, 高速以太网络实体层收发器. Auto-MDIX. 48-pin 0.25um.DM9331 - 100M高速以太网络光纤实体层媒体转换器. 48-pin.DM9301 - 100M高速以太网络光纤实体层媒体转换器.4、10M 以太网络芯片DM9008 - ISA接口以太网络三合一单芯片(性价比优于RTL8019AS,CS8900A )DM9009 - 最经济, 最有效率PCI 接口以太网络三合一单芯片 (含MII/RMII/7-wired GPSI 接口).DM9081 - 最经济, 最有效率以太网络 (8+2) 集线器芯片.。

基于MSP430和DM9000的以太网接口设计_刘亚萍

基于MSP430和DM9000的以太网接口设计刘亚萍,甄国涌,刘东海(中北大学电子测试技术国家重点实验室,太原030051)摘要:为提高以太网的数据传输效率,设计了以MSP430FG4618为核心的控制单元,驱动以太网接口芯片DM9000EP 的嵌入式系统的以太网接口。

通过单片机完成网卡芯片的初始化、数据的封装、接收和发送控制等,而网卡芯片则负责以太网数据的接收和发送。

测试结果表明了UDP 数据传输过程,经自行裁剪的UD P /IP 协议栈,提高了UDP 传输效率。

该接口具有硬件接口简单、外围器件少、价格低廉、开发周期短等特点,同时也能满足测试、采集等高速数据传输系统的要求。

关键词:MSP430;DM9000;以太网接口;UDP ;数据传输中图分类号:TP393.02文献标志码:ADesign of Ethernet Interface Based on MSP430and DM9000LIU Ya-ping ,ZHEN Guo-yong ,LIU Dong-hai(National Key Laboratory for Electronic Measurement Technology ,North University of China ,Taiyuan 030051,China )Abstract :In order to improve the Ethernet data transmission efficiency ,it designed a embedded Ethernet interface ,whose core control unit is MSP430FG4618to drive the Ethernet interface chip DM9000EP.Through the MCU to com-pleted the initializatioin of the Ethernet card chip ,data package ,the control of receiving and sending ;while the Eth-ernet card chip is used to receive and send data from Ethernet.The test result s showed that the transmission process of UDP data ;and UDP transmission efficiency is increased through cutting the UD P /IP protocol stack.W ith simple de-sign ,low price ,little peripheral equipment and short development cycle ,the interface can satisfy some requires from the testing ,data acquisition systems of high speed data transmission.Key words :MSP430;DM9000;Ethernet interface ;UDP ;data transmission收稿日期:2010-03-15;修订日期:2010-04-07基金项目:国家自然科学基金项目(60871041)作者简介:刘亚萍(1985-),女,在读硕士研究生,研究方向为高速数字量设计;甄国涌(1971-),男,工学博士,副教授,研究方向为嵌入式系统、动态测试等;刘东海(1982-),男,硕士研究生,研究方向为动态测试、高速数据采集。

DM9000中文手册

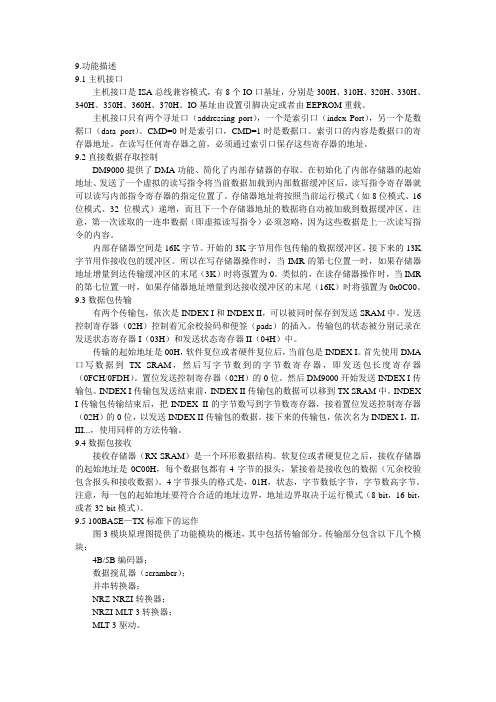

9.功能描述9.1主机接口主机接口是ISA总线兼容模式,有8个IO口基址,分别是300H、310H、320H、330H、340H、350H、360H、370H。

IO基址由设置引脚决定或者由EEPROM重载。

主机接口只有两个寻址口(addressing port),一个是索引口(index Port),另一个是数据口(data port)。

CMD=0时是索引口,CMD=1时是数据口。

索引口的内容是数据口的寄存器地址。

在读写任何寄存器之前,必须通过索引口保存这些寄存器的地址。

9.2直接数据存取控制DM9000提供了DMA功能、简化了内部存储器的存取。

在初始化了内部存储器的起始地址、发送了一个虚拟的读写指令将当前数据加载到内部数据缓冲区后,读写指令寄存器就可以读写内部指令寄存器的指定位置了。

存储器地址将按照当前运行模式(如8位模式、16位模式、32位模式)递增,而且下一个存储器地址的数据将自动被加载到数据缓冲区。

注意,第一次读取的一连串数据(即虚拟读写指令)必须忽略,因为这些数据是上一次读写指令的内容。

内部存储器空间是16K字节。

开始的3K字节用作包传输的数据缓冲区。

接下来的13K 字节用作接收包的缓冲区。

所以在写存储器操作时,当IMR的第七位置一时,如果存储器地址增量到达传输缓冲区的末尾(3K)时将强置为0。

类似的,在读存储器操作时,当IMR 的第七位置一时,如果存储器地址增量到达接收缓冲区的末尾(16K)时将强置为0x0C00。

9.3数据包传输有两个传输包,依次是INDEX I和INDEX II,可以被同时保存到发送SRAM中。

发送控制寄存器(02H)控制着冗余校验码和便签(pads)的插入。

传输包的状态被分别记录在发送状态寄存器I(03H)和发送状态寄存器II(04H)中。

传输的起始地址是00H,软件复位或者硬件复位后,当前包是INDEX I。

首先使用DMA 口写数据到TX SRAM,然后写字节数到的字节数寄存器,即发送包长度寄存器(0FCH/0FDH)。

DM9000寄存器功能详细介绍

DM9000寄存器功能详细介绍提交者: a00 日期: 1/20 16:09 阅读: 15DM9000(A)是一个全集成、功能强大、性价比高的快速以太网MAC控制器,它带有一个通用处理器接口、EEPROM接口、10/100 PHY和16KB的SRAM(13KB作为接收FIFO,3KB作为发送FIFO)。

它采用单电源供电,可兼容3.3V、5V的IO接口电平。

DM9000(A)同样支持MII(Media Independent Interface 介质无关)接口,连接到HPNA (Home Phone-line Networking Alliance 家用电话网络联盟)设备上或其它支持MII的设备。

DM9000(A)包含一系列可被访问的控制状态寄存器,这些寄存器是字节对齐的,他们在硬件或软件复位时被设置成初始值。

以下为DM9000的寄存器功能详解:NCR (00H):网络控制寄存器(Network Control Register )7:EXT_PHY:1选择外部PHY,0选择内部PHY,不受软件复位影响。

6:WAKEEN:事件唤醒使能,1使能,0禁止并清除事件唤醒状态,不受软件复位影响。

5:保留。

4:FCOL:1强制冲突模式,用于用户测试。

3:FDX:全双工模式。

内部PHY模式下只读,外部PHY下可读写。

2-1:LBK:回环模式(Loopback)00通常,01MAC内部回环,10内部PHY 100M模式数字回环,11保留。

0:RST:1软件复位,10us后自动清零。

NSR (01H):网络状态寄存器(Network Status Register )7:SPEED:媒介速度,在内部PHY模式下,0为100Mbps,1为10Mbps。

当LINKST=0时,此位不用。

6:LINKST:连接状态,在内部PHY模式下,0为连接失败,1为已连接。

5:WAKEST:唤醒事件状态。

读取或写1将清零该位。

不受软件复位影响。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

//setting phy of dm9000 phy_write(0x00 , 0x8000); DELAY_US(100000);

phy_write(0x04 , 0x01e1 | 0x0400); DELAY_US(100000);

iow(DM_NCR , 0X01); DELAY_US(10000); iow(DM_NCR , 0X00);

//clear the RX/TX flag iow(DM_NSR, 0x2C); iow(DM_ISR, 0x3F);

// //write the NODE_ADDR to physical register iow(DM_PAB0 , NODE_ADDR[0]); iow(DM_PAB1 , NODE_ADDR[1]); iow(DM_PAB2 , NODE_ADDR[2]); iow(DM_PAB3 , NODE_ADDR[3]); iow(DM_PAB4 , NODE_ADDR[4]); iow(DM_PAB5 , NODE_ADDR[5]);

//关闭RX中断 iow(DM_IMR , 0x80);

//write length to internal sram //将包的长度写入到寄存器中; len = datalen * 2; iow(DM_TXPLH , ((len&0xff00)>>8)); iow(DM_TXPLL , len&0x00ff);

//--------------------------------------------------------------------//DM9000 初始化 void DM9000_INIT(){

//开启PHY iow(DM_GPR , 0X00);

//softerware reset and setting as normal mode(TWICE) iow(DM_NCR , 0X01); DELAY_US(10000); iow(DM_NCR , 0X00);

//open the rx interrupt iow(DM_IMR , 0x81);

-3-

2016年11月22日 16:33

G:\controlSUITE\device_support\F2837xD\v180\F2837xD_examples_Cpu1\emif1_16bit_asram\cpu01\emif1_16bit_asram.c

//set back presure threshold register iow(DM_BPTR , 0x3F); iow(DM_FCTR , 0x3A); iow(DM_RTFCR , 0xFF); iow(DM_SMCR , 0x00);

//clear all flags agin iow(DM_NSR, 0x2C); iow(DM_ISR, 0x3F);

DELAY_US(20); }

//--------------------------------------------------------------------// 读取DM9000内部寄存器的值 Uint16 ior(Uint16 IOADDR){

DELAY_US(20); *ADDR_POINT = IOADDR; DELAY_US(20); return(*DATA_POINT); }

G:\controlSUITE\device_support\F2837xD\v180\F2837xD_examples_Cpu1\emif1_16bit_asram\cpu01\emif1_16bit_asram.c

2016年11月22日 16:33

//-------------------------------------------------------------------------------------------//DSP28377 利用EMIF控制网口DM9000芯片收发数据 //--------------------------------------------------------------------------------------------

-2-

2016年11月22日 16:33

G:\controlSUITE\device_support\F2837xD\v180\F2837xD_examples_Cpu1\emif1_16bit_asram\cpu01\emif1_16bit_asram.c

iow(DM_EPCR , PHY_RCMD);

//---------------------------------------------------------------------------------------//接受网络包 //在调试的过程中;通过一片DSP发送1040个数据(8bit);并设置发送长度为1040;但对于接受的网络包 而言;不仅仅会在接收到的网络包前包含4个 //信息byte;分别是接受准备;接受状态位;帧长度(2byte);后面跟随1040个数据(byte);后面还会 跟随4个byte位;作用不知;同时接受到的 //帧长度为1044个;所以在读取数据是必须读取完成整个1044个数据;rx指针才会自动跳转到SRAM的首地址 等待下一次触发

0X08

#define DM_FCTR

0X09

#define DM_RTFCR 0X0A

#define DM_EPCR

0X0B

#define DM_EPAR

0X0C

#define DM_EPDRL 0X0D

#define DM_EPDRH 0X0E

#define DM_PAB0

0X10

#define DM_PAB1

extern void setup_emif1_pinmux_async_16bit(Uint16);

//地址指定;通过操作指针实现地址对应数据操作 Uint16 *ADDR_POINT = (Uint16 *)(ASRAM_CS3_START_ADDR); Uint16 *DATA_POINT = (Uint16 *)(ASRAM_CS3_START_ADDR + 1);

while((ior(DM_EPCR) & 1));

DELAY_US(200);

iow(DM_EPCR , 0x08);

returndata = ior(DM_EPDRH); returndata = (returndata << 8) | ior(DM_EPDRL);

return returndata; }

*ADDR_POINT = IOADDR; DELAY_US(20); *DATA_POINT = REGDARA;

-1-

G:\controlSUITE\device_support\F2837xD\v180\F2837xD_examples_Cpu1\emif1_16bit_asram\cpu01\emif1_16bit_asram.c

//start transmit iow(DM_TCR , 0X01);

// wait transmit complit while((ior(DM_NSR) & 0x0c) == 0);

DELAY_US(20);

//clear the tx flag iow(DM_NSR , 0X2C);

//oprn rx intterupt iow(DM_IMR , 0x81); }

#define DM_MRCMD 0XF2

#define DM_MWCMD 0XF8

#define DM_TXPLH 0XFD

#define DM_TXPLL 0XFC

#define DM_ISR

0XFE

#define DM_IMR

0XFF

#define PHY_BADDR #define PHY_WCMD #define PHY_RCMD

//--------------------------------------------------------------------//读物理接口PHY寄存器的值 Uint16 phy_reaad(Uint16 offset , Uint16 REGIN){

Uint16 returndata=0; iow(DM_EPAR , (offset | PHY_BADDR));

//--------------------------------------------------------------------// 往固定地址写值 void outw(Uint16 REGDATA , Uint16 addr_data_type){

if(addr_data_type == 1) *DATA_POINT = REGDAR_POINT = REGDATA; DELAY_US(50); }

iow(DM_EPAR , (offset | PHY_BADDR)); iow(DM_EPDRH , (REGIN >> 8) & 0x00ff); iow(DM_EPDRL , (REGIN & 0x00ff)); iow(DM_EPCR , PHY_WCMD); while((ior(DM_EPCR) & 1)); DELAY_US(200); iow(DM_EPCR , 0x08); }

#include "F28x_Project.h"

// Device Headerfile and Examples Include File

void Emif1Initialize(void);

//emif 映射地址 #define ASRAM_CS3_START_ADDR 0x37FFF0 #define ASRAM_CS3_SIZE 0x8000