8.18 电子琴程序设计与仿真

简易电子琴电路的设计仿真与实现

目录1 Pspice的简介 (1)1.1 PSPICE的起源与发展 (1)1.2 PSPICE的组成 (1)1.3 PSPICE的模拟功能 (2)2 设计原理及电路选取 (4)2.1 基本乐理知识 (4)2.2 设计原理 (4)3 设计方案 (7)3.1设计电路图 (7)3.2参数推导 (8)3.3仿真参数和仿真电路图 (8)4.仿真曲线 (10)5.仿真结果分析 (13)6.硬件焊接与调试 (14)6.1元器件的选择 (14)6.2焊接过程与调试 (15)7.课程设计心得 (16)8.参考文献 (18)本科生课程设计成绩评定表 (19)1 Pspice的简介1.1 PSPICE的起源与发展用于模拟电路仿真的SPICE软件于1972年由美国加州大学伯克利分校的计算机辅助设计小组利用FORTR AN语言开发而成,主要用于大规模集成电路的计算机辅助设计。

SPICE 的正式版SPICE 2G在1975年正式推出,但是该程序的运行环境至少为小型机。

1985年,加州大学伯克利分校用C语言对SPICE软件进行了改写,并由MICROSIM公司推出。

1988年SPICE被定为美国国家工业标准。

与此同时,各种以SPICE为核心的商用模拟电路仿真软件,在SPICE的基础上做了大量实用化工作,从而使SPICE成为最为流行的电子电路仿真软件。

PSPICE是较早出现的EDA软件之一,在电路仿真方它的功能可以说是最为强大,在国内被普遍使用。

1.2 PSPICE的组成1.2.1 电路原理图编辑程序SchematicsPSPICE的输入有两种形式,一种是网单文件形式,一种是电路原理图形式,相对而言后者比前者较简单直观,它既可以生成新的电路原理图文件,又可以打开已有的原理图文件。

电路元器件符号库中备有各种原器件符号,除了电阻,电容,电感,晶体管,电源等基本器件及符号外,还有运算放大器,比较器等宏观模型级符号,组成电路图,原理图文件后缀为.sch。

电子琴的仿真设计课程设计

电子琴的仿真设计课程设计一、课程目标知识目标:1. 学生能理解电子琴的基本原理,掌握仿真设计的基本概念。

2. 学生能描述电子琴音色、节奏及演奏效果的产生过程。

3. 学生了解电子琴仿真设计中所涉及的电子元件和电路。

技能目标:1. 学生能运用所学的电子琴仿真设计知识,独立设计简单的电子琴音色。

2. 学生能通过实践操作,熟练使用仿真软件进行电子琴设计。

3. 学生具备分析电子琴仿真设计问题,并提出解决方案的能力。

情感态度价值观目标:1. 学生对电子琴仿真设计产生兴趣,培养对音乐和电子技术的热爱。

2. 学生在团队协作中学会相互尊重、沟通与协作,培养集体荣誉感。

3. 学生通过课程学习,认识到科技发展对音乐领域的影响,增强创新意识。

课程性质:本课程为实践性较强的电子技术课程,旨在让学生通过动手实践,掌握电子琴仿真设计的基本技能。

学生特点:学生处于高中阶段,具有一定的电子技术基础,好奇心强,喜欢动手实践。

教学要求:注重理论与实践相结合,关注学生的个体差异,引导他们主动探索、积极实践,提高电子琴仿真设计能力。

在教学过程中,关注学生的情感态度价值观培养,帮助他们形成良好的学习习惯和团队合作精神。

通过具体的学习成果分解,为后续教学设计和评估提供依据。

二、教学内容1. 电子琴基本原理:电子琴的工作原理、音色生成、节奏控制及演奏效果。

- 教材章节:第1章 电子琴概述2. 电子琴仿真设计基础:仿真设计概念、仿真软件使用、基本电子元件及电路。

- 教材章节:第2章 电子琴仿真设计基础3. 电子琴音色设计:音色合成原理、音色参数调整、音色库应用。

- 教材章节:第3章 电子琴音色设计4. 电子琴演奏功能设计:演奏控制、节奏编程、音效处理。

- 教材章节:第4章 电子琴演奏功能设计5. 实践操作:使用仿真软件进行电子琴设计,包括音色设计、演奏功能设计等。

- 教材章节:第5章 实践操作教学内容安排和进度:第1周:电子琴基本原理学习第2周:电子琴仿真设计基础学习第3-4周:音色设计理论与实践第5-6周:演奏功能设计理论与实践第7-8周:实践操作,完成电子琴仿真设计作品教学内容注重科学性和系统性,结合教材章节安排,循序渐进地引导学生学习电子琴仿真设计知识。

c语言电子钢琴课程设计

c语言电子钢琴课程设计一、课程目标知识目标:1. 学生能理解C语言在电子钢琴程序设计中的应用,掌握基础编程语法和结构。

2. 学生能运用C语言中的函数、循环和条件语句等编写简单的电子钢琴程序。

3. 学生了解声音产生原理,掌握利用C语言模拟生成不同音调的方法。

技能目标:1. 学生能够运用所学的C语言知识,独立设计并编写出具有基本功能的电子钢琴程序。

2. 学生通过实践操作,培养解决问题的能力和逻辑思维能力。

3. 学生能够进行程序调试,优化程序性能,提高代码质量。

情感态度价值观目标:1. 学生在学习过程中,培养对编程的兴趣和热情,树立编程改变生活的观念。

2. 学生通过团队合作,培养沟通协作能力和团队精神。

3. 学生在创作电子钢琴程序的过程中,体验创新乐趣,提高自信心和成就感。

课程性质:本课程为实践性较强的课程,结合C语言编程和电子钢琴知识,培养学生编程技能和实际应用能力。

学生特点:学生处于高中年级,具备一定的逻辑思维能力和编程基础,对新鲜事物充满好奇心,喜欢动手实践。

教学要求:教师应注重理论与实践相结合,引导学生主动参与,激发学生兴趣,提高学生的编程能力和创新能力。

在教学过程中,关注学生的个体差异,给予个性化指导。

通过课程目标的设定,使学生在学习过程中有明确的成果导向,便于教学设计和评估。

二、教学内容1. C语言基础语法复习:变量定义、数据类型、运算符、控制结构(循环、条件语句)。

相关教材章节:第一章至第三章。

2. 函数的定义与调用:理解函数的作用,掌握函数的定义、调用和参数传递。

相关教材章节:第四章。

3. 数组与指针:了解数组的使用,认识指针的概念,学会指针操作。

相关教材章节:第五章、第六章。

4. 声音产生原理:介绍声音的基本概念,理解音频信号的产生与处理。

相关教材章节:附录部分或拓展资料。

5. 电子钢琴程序设计:利用C语言编写电子钢琴程序,实现不同音调的模拟。

教学安排:5.1 设计电子琴界面,实现键盘与音调的对应关系。

8.18 电子琴程序设计与仿真 修改

8.18.4程序设计与仿真电子琴VHDL程序包含有:顶层程序、音阶发生器程序、数控分频模块程序和自动演奏模块程序。

1.顶层程序与仿真(1)顶层VHDL程序--文件名:top.vhd--功能:顶层文件--最后修改日期:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity top isPort ( clk32MHz :in std_logic; --32MHz系统时钟handTOauto : in std_logic; --键盘输入/自动演奏code1 :out std_logic_vector(6 downto 0); --音符显示信号index1 :in std_logic_vector(7 downto 0); --键盘输入信号high1 :out std_logic; --高低音节信号spkout :out std_logic); --音频信号end top;architecture Behavioral of top iscomponent automusicPort ( clk :in std_logic;Auto: in std_logic;index2:in std_logic_vector(7 downto 0);index0 : out std_logic_vector(7 downto 0));end component;component tonePort ( index : in std_logic_vector(7 downto 0);code : out std_logic_vector(6 downto 0);high : out std_logic;tone0 : out integer range 0 to 2047);end component;component speakerPort ( clk1 : in std_logic;tone1 : in integer range 0 to 2047;spks : out std_logic);end component;signal tone2: integer range 0 to 2047;signal indx:std_logic_vector(7 downto 0);beginu0:automusic port map(clk=>clk32MHZ,index2=>index1,index0=>indx,Auto=>handtoAuto); u1: tone port map(index=>indx,tone0=>tone2,code=>code1,high=>high1);u2: speaker port map(clk1=>clk32MHZ,tone1=>tone2,spks=>spkout);end Behavioral;(2)仿真顶层文件仿真图如图8.18.2所示。

基于Multisim八音阶电子笨的设计与仿真

基于Multisim八音阶电子笨的设计与仿真兰羽;周茜【摘要】介绍了以RC串并联选频网络为主振电路的电子琴设计方法,给出了八音阶电子琴电路参数的设计方法和一组参数值。

并采用MultisimlO对RC串并联正弦波振荡电路进行了设计仿真。

结果证明,用模拟电路方法制作电子琴结构简单,而且成本低廉,符合C音调基准音标准。

%The design method of an electronic piano is introduced, which works selection frequency RC network with series and parallel collection as its oscillator circuit. It gives the design method of circuit parameters and a set of values of eight-scale electronic piano. And there is a simulation design to RC series and parallel sine wave oscillator circuit with multisim10. The resuhs show that it is simple to make electronic piano with the approaches of analogue circuits, and the cost is low, it can accord with the standard of C-tone as its datum tone.【期刊名称】《电子设计工程》【年(卷),期】2012(020)012【总页数】3页(P52-54)【关键词】电子琴;RC振荡电路;电路参数设计;Muhisim仿真【作者】兰羽;周茜【作者单位】陕西工业职业技术学院,陕西咸阳712000;陕西工业职业技术学院,陕西咸阳712000【正文语种】中文【中图分类】TN75Multisim10是加拿大图像交互技术公司推出最新版电子仿真软件,它提供了强大元件库、虚拟仪器库,设计界面简洁,适合模拟/数字电路的设计仿真。

简易电子琴的VHDL仿真与实现

简易电子琴的VHDL仿真与实现电子琴是一种应用广泛的乐器,而现在,电子琴的制造已经从纯硬件逐渐过渡到硬件加软件的方式。

VHDL是一种硬件描述语言,它可以方便地描述各种硬件逻辑功能,而且还可以帮助设计者实现FPGA的目标硬件。

本文主要介绍简易电子琴的VHDL仿真与实现。

一、设计思路简易电子琴的设计基本上就是将钢琴的琴键和生产声音的部件(如电子光电元件或电子开关等)结合在一起。

琴键的设计分为两个部分:按下和弹起。

按下部分是由一个简单的开关连接到FPGA引脚的输入端。

当琴键被按下时,开关闭合,产生一个低电平信号,这个信号作为FPGA的输入。

弹起部分用一个气压传感器检测琴键是否已经弹起。

生产声音的部件由一个数字-模拟转换器(Digital-to-Analog Converter,简称DAC)处理FPGA通过一个计数器输出的数字信号,将它转换成模拟信号。

这样,设计思路就非常清晰明了。

二、VHDL仿真的步骤1. 创建虚拟设计:在仿真之前,我们需要创建一个虚拟的设计,包括引脚、组件、实体、测试模块,以及其他必需的部件。

这些将精确地模拟真实世界中的电路元素。

2. 创建设计模块:VHDL仿真涉及到多个模块。

在这种情况下,我们有两个模块:数字模块和组件模块。

我们将数字模块设计为接收一个8位的计数器并输出模拟信号。

组件模块包括DAC芯片和琴键开关,这些组件分别接收输入信号,经过逻辑处理后,通过计数器和气压传感器输出压缩后的模拟信号。

3. 配置实体接口:为了确保VHDL仿真的准确性,我们必须配置模块实体接口,这里有两个实体:数值模块和组件模块。

它们需要定义数据量和接收输入端口。

4. 定义测试激励波形:这些波形定义从测试模块输入到仿真环境中的数字信号序列。

因此,我们需要定义输入数据以及时钟信号。

5. 编写测试模块:测试模块是用来检测VHDL仿真环境的激励波形。

它包括测试模块、实体、配置、激励波形和仿真模块。

三、VHDL实现的步骤1. 设计和构建硬件:在这一阶段,我们将实现FPGA硬件。

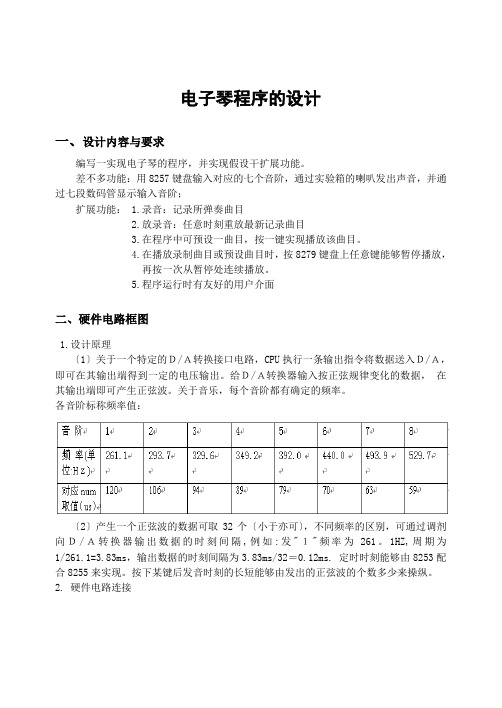

电子琴程序的设计

电子琴程序的设计一、设计内容与要求编写一实现电子琴的程序,并实现假设干扩展功能。

差不多功能:用8257键盘输入对应的七个音阶,通过实验箱的喇叭发出声音,并通过七段数码管显示输入音阶;扩展功能: 1.录音:记录所弹奏曲目2.放录音:任意时刻重放最新记录曲目3.在程序中可预设一曲目,按一键实现播放该曲目。

4.在播放录制曲目或预设曲目时,按8279键盘上任意键能够暂停播放,再按一次从暂停处连续播放。

5.程序运行时有友好的用户介面二、硬件电路框图1.设计原理〔1〕关于一个特定的D/A转换接口电路,CPU执行一条输出指令将数据送入D/A,即可在其输出端得到一定的电压输出。

给D/A转换器输入按正弦规律变化的数据,在其输出端即可产生正弦波。

关于音乐,每个音阶都有确定的频率。

各音阶标称频率值:〔2〕产生一个正弦波的数据可取32个〔小于亦可〕,不同频率的区别,可通过调剂向D/A转换器输出数据的时刻间隔,例如:发"1"频率为261。

1HZ,周期为1/261.1=3.83ms,输出数据的时刻间隔为3.83ms/32=0.12ms. 定时时刻能够由8253配合8255来实现。

按下某键后发音时刻的长短能够由发出的正弦波的个数多少来操纵。

2. 硬件电路连接三、软件设计1.主程序流程图开始显示缓存区,初始化8279初始化调用发音子程序调用键盘子程序键盘码送缓存区是否9键是否0键是否S键是否R键录音子程序放录音子程序放歌子程序返回DOS YNN N Y Y YN2. 键盘显示子程序流程图3.显示子程序流程图4.部分参考程序KEYBORD PROC NEAR ;键盘子程序MOV DX,PORT1MOV AL,0D1HOUT DX,AL ;CLEAR DISPLAYWREP: CALL DISPMOV DX,PORT1IN AL,DX ;读状态AND AL,07H ;判定是否有按键JZ WREPKEYN: MOV DX,PORT0 ;下一次的按键IN AL,DX ;读数据MOV BL,ALAND AL,07HAND BL,38HMOV CL,03SHR BL,CLCMP BL,00HJNZ LINE1ADD AL,08HJMP QUIT1LINE1: CMP BL,01HJNZ LINE2JMP QUIT1LINE2: ADD AL,10HQUIT1: RETKEYBORD ENDPDISP PROC NEAR ;显示子程序PUSH SIPUSH CXPUSH DXMOV AX,DATAMOV DS,AXMOV DX,PORT1MOV AL,90HOUT DX,AL ;写地址为0000的显示缓存区命令,每次写入后地址自动加1指向下一次写入地址MOV SI,OFFSET SEC1MOV CX,0001MOV BX,OFFSET LEDDISP1: CLDLODSBMOV AH,ALXLAT ;键盘码转显示码MOV DX,PORT0OUT DX,AL ;显示LOOP DISP1POP DXPOP CXPOP SIQ:RETDISP ENDP。

简易电子琴的VHDL仿真与实现

简易电子琴的VHDL仿真与实现随着科技的发展,电子琴已成为一种十分普及的音乐乐器。

除了可以通过购买市面上的电子琴来使用外,我们还可以自己动手制作一台简易的电子琴。

本文将介绍使用VHDL仿真与实现一台简易电子琴的方法。

首先,我们需要了解VHDL(VHSIC Hardware Description Language)是一种硬件描述语言,用于描述数字电路和系统。

VHDL可以描述数字电路和系统的行为、结构和时间性质,并且可以转化为硬件和软件实现。

因此,我们可以使用VHDL来描述电子琴的结构和行为,然后将其实现在FPGA上。

在电子琴的设计中,我们需要考虑最基础的功能:音符的产生和声音的输出。

因此,我们需要将电子琴拆分成两部分来考虑:输入和输出。

输入部分主要负责产生音符,音符的产生需要考虑按键的位置、按键的压力等因素。

由于VHDL主要用来描述数字电路,我们可以将输入部分简化为一组称为“开关矩阵”的二维数组。

在这个开关矩阵中,我们可以设置每个按键的位置和状态(即是否按下),并通过数字电路来判断按键状态的变化。

输出部分则负责将产生的声音输出到扬声器上。

在FPGA 中,我们可以通过PWM(Pulse-Width Modulation)技术来实现声音的输出。

PWM技术可以将模拟信号转化为数字信号,然后通过FPGA输出数字信号的高低电平来模拟模拟信号的频率和幅度,从而实现声音的输出。

接下来,我们需要考虑如何将输入和输出部分结合起来。

我们可以将输入部分和输出部分放在同一个模块中,并通过端口来连接。

在这个模块中,我们可以设置一个时钟,根据时钟的脉冲来判断按键状态是否改变,并且触发PWM来输出声音。

在设计完成后,我们需要进行VHDL仿真来验证我们的电子琴是否正确。

仿真可以模拟电路的行为和输出,以验证电路是否按照预期工作。

我们可以通过仿真来测试输入部分的工作状态,例如测试按键是否可以正确响应。

同时,我们也可以测试输出部分的工作状态,例如测试声音的频率和幅度是否符合预期。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

8.18电子琴程序设计与仿真顶层程序与仿真,音阶发生器程序与仿真,数控分频模块程序与仿真,自动演奏模块程序与仿真设计例见随书所附光盘中文件:8.17电子琴VHDL程序与仿真。

1.顶层程序与仿真(1)顶层VHDL程序--文件名:top.vhd--功能:顶层文件--最后修改日期:2004.3.20library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity top isPort ( clk32MHz :in std_logic; --32MHz系统时钟handTOauto : in std_logic; --键盘输入/自动演奏code1 :out std_logic_vector(6 downto 0); --音符显示信号index1 :in std_logic_vector(7 downto 0); --键盘输入信号high1 :out std_logic; --高低音节信号spkout :out std_logic); --音频信号end top;architecture Behavioral of top iscomponent automusicPort ( clk :in std_logic;Auto: in std_logic;index2:in std_logic_vector(7 downto 0);index0 : out std_logic_vector(7 downto 0));end component;component tonePort ( index : in std_logic_vector(7 downto 0);code : out std_logic_vector(6 downto 0);high : out std_logic;tone0 : out integer range 0 to 2047);end component;component speakerPort ( clk1 : in std_logic;tone1 : in integer range 0 to 2047;spks : out std_logic);end component;signal tone2: integer range 0 to 2047;signal indx:std_logic_vector(7 downto 0);beginu0:automusic port map(clk=>clk32MHZ,index2=>index1,index0=>indx,Auto=>handtoAuto); u1: tone port map(index=>indx,tone0=>tone2,code=>code1,high=>high1);u2: speaker port map(clk1=>clk32MHZ,tone1=>tone2,spks=>spkout);end Behavioral;(2)仿真顶层文件仿真图如图8.17.2所示。

图8.17.2 顶层文件仿真图2. 音阶发生器程序与仿真(1)音阶发生器VHDL程序--文件名:tone.vhd。

--功能:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity tone isPort ( index : in std_logic_vector(7 downto 0); --音符输入信号code : out std_logic_vector(6 downto 0); --音符显示信号high : out std_logic; --高低音显示信号tone0 : out integer range 0 to 2047); --音符的分频系数end tone;architecture Behavioral of tone isbeginsearch :process(index) --此进程完成音符到音符的分频系数译码,音符的显示,高低音阶begincase index iswhen "00000001" => tone0<=773;code<="1001111";high<='1';when "00000010"=> tone0<=912;code<="0010010";high<='1';when "00000100" => tone0<=1036;code<="0000110";high<='1';when "00001000" => tone0<=1116;code<="1001100";high<='1';when "00010000" => tone0<=1197;code<="0100100";high<='1';when "00100000" => tone0<=1290;code<="0100000";high<='0';when "01000000" => tone0<=1372;code<="0001111";high<='0';when "10000000" => tone0<=1410;code<="0000000";high<='0';when others => tone0<=2047;code<="0000001";high<='0';end case;end process;end Behavioral;(2)音阶发生器程序仿真音阶发生器程序仿真图如图8.17.3所示。

图8.17.3 音阶发生器仿真图3. 数控分频模块程序与仿真(1)数控分频模块VHDL程序--文件名:speaker.vhd。

--功能:实现数控分频。

--最后修改日期:20004.3.19。

library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity speaker isPort ( clk1 : in std_logic; --系统时钟tone1 : in integer range 0 to 30624; --音符分频系数spks : out std_logic); --驱动扬声器的音频信号end speaker;architecture Behavioral of speaker issignal preclk,fullspks:std_logic;beginpulse1:process(clk1) --此进程对系统时钟进行4分频variable count:integer range 0 to 8;beginif clk1'event and clk1='1' then count:=count+1;if count=2 then preclk<='1';elsif count=4 then preclk<='0';count:=0;end if;end if;end process pulse1;genspks:process(preclk,tone1)--此进程按照tone1输入的分频系数对8MHz的脉冲再次分频,得到所需要的音符频率variable count11:integer range 0 to 30624;beginif preclk'event and preclk='1' thenif count11<tone1 then count11:=count11+1;fullspks<='1';else count11:=0;fullspks<='0';end if;end if;end process;delaysps:process(fullspks) --此进程对fullspks进行2分频variable count2 :std_logic:='0';beginif fullspks'event and fullspks='1' then count2:=not count2;if count2='1' then spks<='1';else spks<='0';end if;end if;end process;end Behavioral;(2)数控分频模块程序仿真数控分频模块程序仿真图如图8.17.4所示。

图8.17.4 数控分频模块仿真图4. 自动演奏模块程序与仿真(1)自动演奏模块VHDL程序--文件名:automusic.vhd--功能:实现自动演奏功能。

--最后修改日期:2004.3.19。

library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity automusic isPort ( clk,Auto : in std_logic; --系统时钟;键盘输入/自动演奏index2 : in std_logic_vector(7 downto 0); --键盘输入信号index0 : out std_logic_vector(7 downto 0)); --音符信号输出end automusic;architecture Behavioral of automusic issignal count0:integer range 0 to 31;--changesignal clk2:std_logic;beginpulse0:process(clk,Auto) --此进程完成对系统时钟8M的分频,得到4Hz的信号clk2 variable count:integer range 0 to 8000000;beginif Auto='1' then count:=0;clk2<='0';elsif clk'event and clk='1' then count:=count+1;if count=4000000(4)then clk2<='1';elsif count=8000000 (8)then clk2<='0';count:=0;end if;end if;end process;music:process(clk2) --此进程完成自动演奏部分曲的地址累加beginif clk2'event and clk2='1' thenif count0=31 then count0<=0;else count0<=count0+1;end if;end if;end process;com1:process(count0,Auto,index2)beginif Auto='0' thencase count0 is --此case语句:存储自动演奏部分的曲when 0 => index0<="00000100"; --3when 1 => index0<="00000100"; --3when 2 => index0<="00000100"; --3when 3 => index0<="00000100"; --3when 4 => index0<="00010000"; --5when 5 => index0<="00010000"; --5when 6 => index0<="00010000"; --5when 7 => index0<="00100000"; --6when 8 => index0<="10000000"; --8when 9 => index0<="10000000"; --8when 10 =>index0<="10000000"; --8when 11=> index0<="00000100"; --3when 12=> index0<="00000010"; --2when 13=> index0<="00000010"; --2when 14=> index0<="00000001"; --1when 15=> index0<="00000001"; --1when 16=> index0<="00010000"; --5when 17=> index0<="00010000"; --5when 18=> index0<="00001000"; --4when 19=> index0<="00001000"; --4when 20=> index0<="00001000"; --4when 21=> index0<="00000100"; --3when 22=> index0<="00000010"; --2when 23=> index0<="00000010"; --2when 24=> index0<="00010000"; --5when 25=> index0<="00010000"; --5when 26=> index0<="00001000"; --4when 27=> index0<="00001000"; --4when 28=> index0<="00000100"; --3when 29=> index0<="00000100"; --3when 30=> index0<="00000010"; --2when 31=> index0<="00000010"; --2when others => null;end case;else index0<=index2; --键盘输入音符信号输出end if;end process;end Behavioral;(2)自动演奏模块程序仿真自动演奏模块仿真图如图8.17.5所示。