数字电路与逻辑设计第五章

(完整版)数字电路与逻辑设计课后习题答案蔡良伟(第三版)

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

3-6

3-7

3-8

3-9

3-10

求减数的补码,然后与被减数相加即可。电路图如下:

3-11

3-12

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

3-13

(1)真值表:

(2)电路图

3-14

3-15

第四章习题

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

4-10

RSDRSJK RST

4-11

(1)转换真值表

1 1 0 1

1 1 1 0

1 1 1 1

1 0 1 0

0 0 0 0

0 0 0 1

0 0 1 0

00 11

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

××××

××××

××××

××××

××××

1×0×1×0×

0×0×0××1

0×0××1 1×

0×0××0×1

0××1 1×1×

VHDL硬件描述语言与数字逻辑电路设计 (5)[88页]

![VHDL硬件描述语言与数字逻辑电路设计 (5)[88页]](https://img.taocdn.com/s3/m/d12544e5a45177232f60a29e.png)

第5章 VHDL构造体的描述方式

5.1 构造体的行为描述方式 5.2 构造体的寄存器传输(RTL)描述方式 5.3 构造体的结构描述方式 习题与思考题

第5章 VHDL构造体的描述方式

5.1 构造体的行为描述方式

什么样的描述属于行为描述方式,这一点目前还没有确 切的定义,所以在不同的书刊中,对相同或相似的某些用 VHDL描述的逻辑电路的程序有不同的说明。有的说明为行 为描述方式,有的说明为寄存器传输描述方式。但是,有一 点是明确的,行为描述方式是对系统数学模型的描述,其抽 象程度比寄存器传输描述方式和结构描述方式更高。

第5章 VHDL构造体的描述方式

5.1.2 延时语句 在VHDL中存在两种延时类型:惯性延时和传输延时。

这两种延时常用于VHDL的行为描述方式。 1.惯性延时 在VHDL中,惯性延时是缺省的,即在语句中如果不作

特别说明,产生的延时一定是惯性延时,这是因为大多数器 件在行为仿真时都会呈现这种惯性延时。

第5章 VHDL构造体的描述方式

第5章 VHDL构造体的描述方式

在例5-2中用了两个语句:第一个语句是选择语句,第 二个语句是代入语句。这两个语句是条件代入类型语句。也 就是说,只有WHEN后面所指定的条件得到满足时,指定的 代入值才被代入信号量sel或输出量q。

当第一个语句执行时,将使用选择信号。根据选择信号 sel的当前值,后跟的5种状态下的值i0~i3、'X' 中的一个值 将通过输出端口q输出。在正常情况下,q端将选择i0~i3之 一输出,在非正常情况下将输出 'X' 值。

第5章 VHDL构造体的描述方式

几乎所有器件都存在惯性延时,因此,硬件电路的设计 人员为了逼真地仿真硬件电路的实际工作情况,在代入语句 中总要加上惯性延时时间的说明。例如:

数字电路与逻辑设计课后习题答案蔡良伟(第三版)

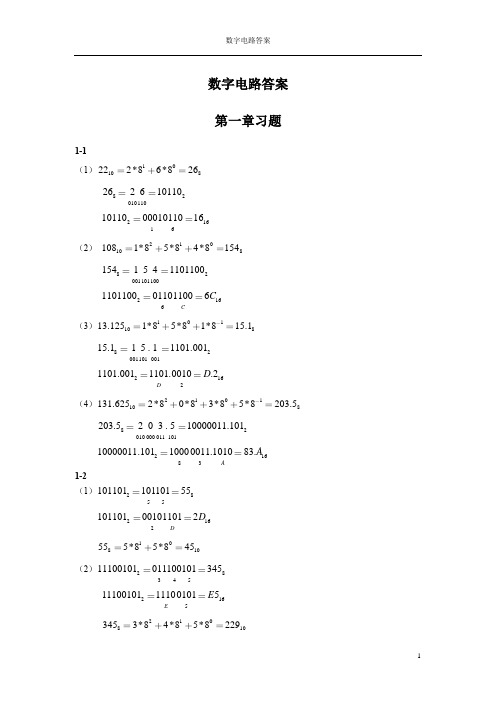

数字电路答案 第一章习题1-1 (1)10108222*86*8268201011026261011021616101100001011016(2) 211081081*85*84*81548200110010115415411011002166110110*********6CC(3)10110813.1251*85*81*815.18200100110115.115.11101.00121621101.0011101.0010.2DD(4)211108131.6252*80*83*85*8203.582010000011101203.5203.510000011.1012168310000011.10110000011.101083.AA1-2(1)285510110110110155 2162101101001011012DD10810555*85*845(2)2834511100101011100101345 216511100101111001015EE2108103453*84*85*8229(3)28514101.0011101.0011005.14 21653101.00110101.00115.30128105.145*81*84*85.1875(4)28744100111.101100111.10147.421627100111.10100100111.101027.AA101018625.398*58*78*45.47=++=-1-3 (1)10810161*86*8148200111016161110 21611101110EE(2)218101721*87*82*812282001010111172172111101016727101001111111010A A==(3)101281061.536*81*85*83*849.6728200111010101161.5361.53110001.101011 21631110001.10101100110001.1010110031.AC AC(4)21012810126.741*82*86*87*84*886.937582001010100110111126.74126.741010110.1111216561010110.111101010110.111156.FF1-4 (1)1620010101022101010A A28521010101010105210810525*82*842(2)16210110010111122101100101111B F B F2875451011001011111011001011115457321081054575*84*85*87*82863(3)1621101111000113.3.11010011.111D E D E28732311010011.111011010011.111323.72101810323.73*82*83*87*8211.875(4)162000111111100001110011 3.913.9111000011.11111001C F C F28770362111000011.11111001111000011.111110010703.762210123810703.7627*80*83*87*86*82*8451.97261-5(1)AC AB C B A +=+)(左式=右式,得证。

《数字电子技术基础》课后习题答案

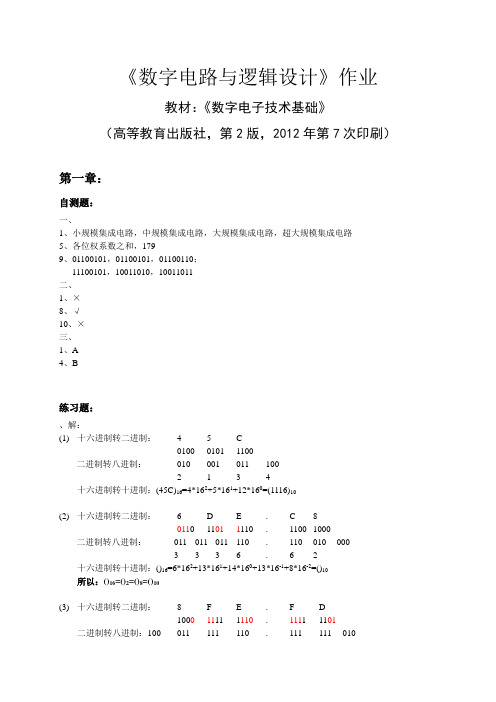

《数字电路与逻辑设计》作业教材:《数字电子技术基础》(高等教育出版社,第2版,2012年第7次印刷)第一章:自测题:一、1、小规模集成电路,中规模集成电路,大规模集成电路,超大规模集成电路5、各位权系数之和,1799、01100101,01100101,01100110;11100101,10011010,10011011二、1、×8、√10、×三、1、A4、B练习题:、解:(1) 十六进制转二进制: 4 5 C0100 0101 1100二进制转八进制:010 001 011 1002 13 4十六进制转十进制:(45C)16=4*162+5*161+12*160=(1116)10(2) 十六进制转二进制: 6 D E . C 80110 1101 1110 . 1100 1000 二进制转八进制:011 011 011 110 . 110 010 0003 3 3 6 . 6 2十六进制转十进制:()16=6*162+13*161+14*160+13*16-1+8*16-2=()10所以:()16=()2=()8=()10(3) 十六进制转二进制:8 F E . F D1000 1111 1110. 1111 1101二进制转八进制:100 011 111 110 . 111 111 0104 3 7 6 . 7 7 2十六进制转十进制:(8FE.FD)16=8*162+15*161+14*160+15*16-1+13*16-2=(2302.98828125)10 (4) 十六进制转二进制:7 9 E . F D0111 1001 1110 . 1111 1101二进制转八进制:011 110 011 110 . 111 111 0103 6 3 6 . 7 7 2十六进制转十进制:(79E.FD)16=7*162+9*161+14*160+15*16-1+13*16-2=(1950. 98828125)10 所以:()16.11111101)2=(363)8=(1950.98828125)10、解:(74)10 =(0111 0100)8421BCD=(1010 0111)余3BCD(45.36)10 =(0100 0101.0011 0110)8421BCD=(0111 1000.0110 1001 )余3BCD(136.45)10 =(0001 0011 0110.0100 0101)8421BCD=(0100 0110 1001.0111 1000 )余3BCD (374.51)10 =(0011 0111 0100.0101 0001)8421BCD=(0110 1010 0111.1000 0100)余3BCD、解(1)(+35)=(0 100011)原= (0 100011)补(2)(+56 )=(0 111000)原= (0 111000)补(3)(-26)=(1 11010)原= (1 11101)补(4)(-67)=(1 1000011)原= (1 1000110)补第二章:自测题:一、1、与运算、或运算、非运算3、代入规则、反演规则、对偶规则二、2、×4、×三、1、B3、D5、C练习题:2.2:(4)解:(8)解:2.3:(2)证明:左边=右式所以等式成立(4)证明:左边=右边=左边=右边,所以等式成立(1)(3)2.6:(1)2.7:(1)卡诺图如下:BCA00 01 11 100 1 11 1 1 1所以,2.8:(2)画卡诺图如下:BC A 0001 11 100 1 1 0 11 1 1 1 12.9:如下:CDAB00 01 11 1000 1 1 1 101 1 111 ×××10 1 ××2.10:(3)解:化简最小项式:最大项式:2.13:(3)技能题:2.16 解:设三种不同火灾探测器分别为A、B、C,有信号时值为1,无信号时为0,根据题意,画卡诺图如下:BC00 01 11 10A0 0 0 1 01 0 1 1 1第三章:自测题:一、1、饱和,截止7、接高电平,和有用输入端并接,悬空;二、1、√8、√;三、1、A4、D练习题:、解:(a)Ω,开门电阻3kΩ,R>R on,相当于接入高电平1,所以(e) 因为接地电阻510ΩkΩ,R<R off,相当于接入高电平0,所以、、解:(a)(c)(f)、解: (a)、解:输出高电平时,带负载的个数2020400===IH OH OH I I N G 可带20个同类反相器输出低电平时,带负载的个数78.1745.08===IL OL OL I I NG反相器可带17个同类反相器EN=1时,EN=0时,根据题意,设A为具有否决权的股东,其余两位股东为B、C,画卡诺图如下,BC00 01 11 10A0 0 0 0 01 0 1 1 1则表达结果Y的表达式为:逻辑电路如下:技能题::解:根据题意,A、B、C、D变量的卡诺图如下:CD00 01 11 10AB00 0 0 0 001 0 0 0 0 11 0 1 1 1 10 0 0 0 0电路图如下:第四章:自测题:一、2、输入信号,优先级别最高的输入信号7、用以比较两组二进制数的大小或相等的电路,A>B 二、 3、√ 4、√ 三、 5、A 7、C练习题:4.1;解:(a),所以电路为与门。

数字电路与逻辑设计复习

第二章 逻辑函数及其简化 公式法化简

① F=(A⊕B)(B⊕C) ●A+B+A+C

解: F=[(A⊕B)(B⊕C) +A+B] ●(A+C) =[(AB+AB)(BC+BC)+A+B) ●(A+C)

第二章 逻辑函数及其简化 1 若A、B、C、D、E为某逻辑函数输入变量,函数的最大项表达式 所包含的最大项的个数不可能是: A 32 B 15 C 31 D 632 2 以下表达式中符合逻辑运算规则的是: A. C●C=C2 B. 1+1=10 C. 0﹤1 D. A+1=1 3 符合逻辑运算规则的是: A. 1×1=1 B. 1+1=10 C. 1+1=1 D. 1+1=2 4 逻辑函数F=AB+CD+BC的反函数F是:_____;对偶函数F﹡是:____; 5 逻辑代数的三个重要规则是:_________,__________,_________ 当逻辑函数有n个变量时,共有____种变量取值组合。 6 异或与同或在逻辑上正好相反,互为反函数,对吗? 7 逻辑变量的取值,1比0大,对吗? 8 F=A⊕B⊕C=A⊙B⊙C,对吗? 答案:1. D 2. D 3. C 4. ___ 5. ____ ____ 6. √ 7. × 8. √

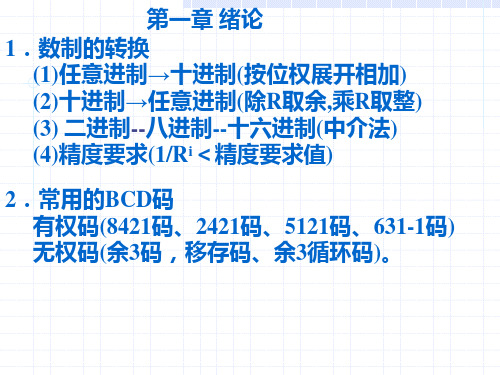

第一章 绪论 1.数制的转换 (1)任意进制→十进制(按位权展开相加) (2)十进制→任意进制(除R取余,乘R取整) (3) 二进制--八进制--十六进制(中介法) (4)精度要求(1/Ri<精度要求值) 2.常用的BCD码 有权码(8421码、2421码、5121码、631-1码) 无权码(余3码,移存码、余3循环码)。

数字电路与逻辑设计总复习题

(2)若F(A,B,C)= ∏M( 3, 5, 6, 7) , 则F(A,B,C)=∑m(?)。 解: ∵ F(A,B,C)= ∏M( 3, 5, 6, 7) , 则 F(A,B,C)= ∑ m( 0 , 1 , 2 , 4 ) F(A,B,C)= ∑m( 3, 5, 6, 7)

(5)试写出下列各函数表达式F的F和F′的最小项表 达式。 (1) F ABCD ACD BC D (2) F AB A B BC

=∏(0,1,3)

(3)F(A,B,C)=1⊕A⊕BC=∑m(?)

解: F(A,B,C)= A ⊕ BC

= A· + A · BC BC =A (B + C ) +ABC = A B +A C +ABC

F(A,B,C)= ∑( 0, 1, 2 ,7 )

八、若F1(A,B,C)=∑m(0, 1, 2, 3) , F2(A,B,C)=∏M(0, 1, 2, 3) , 则F1⊕ F2=( ? )。 解:

= A (B C + B) + B + C =A( B +C ) + B + C =A+ B + C + B + C =A+ 1 = 1

解: F=A B( C + D )+B C+A B+A C+B C+B C D =A B C+A B D+B+A B+A C +B C D =A C+A D + B + A +A C +C D =C + D +B +A +C D

ABCD=0001 F=0⊕0⊕0⊕0=0 ABCD=0010 F=0⊕0⊕1⊕1=0

时序逻辑电路51概述52时序逻辑电路的状态转换表

数字电路与逻辑设计

④ 列状态表: 状态表的已知条件是电路的 外输入和各触发器的原状态;待求量是该时序电 路的原状态所对应的外输出和各触发器的新状态. ⑤ 根据状态表画状态图(或时序图)。并分 析电路的逻辑功能。 ⑥ 对该时序逻辑电路进行电路分析,检查 自启动性能。

数字电路与逻辑设计

例5.3.1:分析下图5.3.1所示同步时序电路

(2)写出次态方程:

Q 0 n 1 J 0 Q 0 n K 0 Q 0 n Q1 n 1 J1 Q1 n K1Q1 n

数字电路与逻辑设计

(3)列出状态转换真值表,见下表5.3.2所示。

输入 现状

Q 1n Q 0n

触发器输入

输出

次态

Q1n+1 Q0n+1

X 0

0 0 0

数字电路与逻辑设计

第五章 时序逻辑电路

5. 1 概述 5. 2 时序逻辑电路的状态转换表、状态转换 图和时序图 5. 3 同步时序逻辑电路的分析和设计方法 5. 4 异步时序电路的分析和设计方法 5. 5 几种常用的时序逻辑电路 5. 7 时序逻辑电路的VHDL描述

数字电路与逻辑设计

5.1概述

逻辑电路

数字电路与逻辑设计

图5.2.2 图5.1.3电路的时序图

数字电路与逻辑设计

5.3 同步时序电路的分析与设计

同步时序电路的分析,就是已知具体电路, 通过分析其工作状态变化的过程及输入与输出之 间的关系,从而弄清该电路的逻辑功能,并给出 适当的文字描述,以便正确地使用这些电路。

数字电路与逻辑设计

5.3.1 同步时序逻辑电路的分析方法 同步时序电路分析的一般步骤如下: ① 从给定的逻辑图中写出每个触发器的驱 动方程(亦即存储电路中每个触发器输入信号的 逻辑函数式)。 ② 把得到的这些驱动方程代入相应触发器 的特性方程,得出每个触发器的状态方程,从而 得到由这些状态方程组成的整个时序电路的状态 方程组。 ③ 根据逻辑图写出电路的输出方程。

数字电路与逻辑设计第5章时序逻辑电路

图5-1时序逻辑电路的组成框图

根据图5-1,可以列出以下3个逻辑 方程组:

(5-1) (5-2) (5-3)

其中,式(5-1)称为输出方程,式 (5-2)称为驱动方程(或激励方程), 式(5-3)称为状态方程。

qn1,qn2,…,qnj表示存储电路每个触发 器的初态,qn+11,qn+12,…,qn+1j表示存 储电路每个触发器的次态。

表5-2 74LS175的状态转换表

图5-7 74LS175的引脚排列图

5.3.2移位寄存器

在数字电路系统中,由于运算的需 要,常常要求输入寄存器的数码能逐位 移动,这种具有移位功能的寄存器,称 为移位寄存器。

移位寄存器的逻辑功能和电路结构 形式较多。

根据移位方向可分为单向移位寄存 器和双向移位寄存器两种;根据接收数 据的方式可分为串行输入和并行输入两 种;根据输出方式可分为串行输出和并 行输出。

所谓串行输入,是指将数码从一个 输入端逐位输入到寄存器中,而串行输 出是指数码在末位输出端逐位出现。

1.单向移位寄存器

单向移位寄存器,是指数码仅能作 单一方向移动的寄存器。可分为左移寄 存器和右移寄存器。如图5-8所示是由D 触发器组成的4位串行输入、串并行输出 的左移寄存器。

图5-8 4位左移寄存器

分析同步时逻辑电路的一般步骤如 下。

(1)写出存储电路中每个触发器的驱 动方程; (2)将驱动方程分别代入各触发器的 特性方程,得出每个触发器的状态方 程; (3)根据逻辑电路写出输出方程。

5.2.2时序逻辑电路的一般分析方法

实际上,从驱动方程、状态方程和 输出方程这3个方程中,还不能对时序逻 辑电路的逻辑功能有一个完全的了解, 还需要通过另外一些更直观的方法来分 析和描述时序逻辑电路的逻辑功能。这 里主要介绍3种比较重要而且常用的方法 ,分别是状态转移表、状态转移图、时 序图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.次态函数表达式:次态函数用来反映同步时序电路的 次态yn+1与激励函数Y和电路现态y之间的关系,它与触发器类 型相关。其函数表达式为 y ln+1 = kl(Yj,yl) j=1,2,…,r ; l =1,2 ,…,s

第五章 同步时序逻辑电路

二.状态表 状态表:反映同步时序电路输出Z、次态yn+1与电路 输入x、现态y之间关系的表格,又称为状态转移表。

第五章 同步时序逻辑电路

时序逻辑电路的状态y1,…,ys是存储电路对过 去输入信号记忆的结果,它随着外部信号的作用 而变化。

次态与现态的概念:

在对电路功能进行研究时,通常将某一时刻 的状态称为“现态”,记作yn,简记为 y; 将在某一现态下,外部信号发生变化后到达 的新的状态称为 “次态”,记作 yn+1。

第五章 同步时序逻辑电路

5.2

同步时序逻辑电路分析

分析方法概述

5.2.1

分析同步时序电

路有两种常用的方法, 一种是表格法,另一 种是代数法。

第五章 同步时序逻辑电路

一. 表格分析法的一般步骤

1.写出输出函数和激励函数表达式;

2.借助触发器功能表列出电路次态真值表;

3.作出状态表和状态图(画出时间图);

注意:次态与现态的概念是相对的!

第五章 同步时序逻辑电路

三.特点

● 由组合电路和存储电路组成,具有对过去 输入进行记忆的功能;

● 包含反馈回路,通过反馈使电路功能与

“时序”相关; ● 输出由电路当时的输入和状态(过去的输入) 共同决定。

第五章 同步时序逻辑电路

5.1.2 时序逻辑电路的分类

通常按照电路的工作方式、电路输出对输入的依从关系或 者输入信号的形式进行分类。

4.归纳出电路的逻辑功能。

第五章 同步时序逻辑电路

二. 代数分析法的一般步骤

1.写出输出函数和激励函数表达式;

2.把激励函数表达式代入触发器的次态方 程,导出电路的次态方程组;

3.作出状态表和状态图(画出时间图);

4.归纳出电路的逻辑功能。

第五章 同步时序逻辑电路

5.2.2 分析举例

例1 用表格法分析下图所示同步时序逻辑电路。 解: 电路由两个J-K触 发器和一个异或门组成, 电路的输入为x,电路的状 态(即触发器状态)用y2、y1 表示。电路的输出即状态 变量,因此,该电路属于 Moore型电路的特例。 1. 写出输出函数和激励函数表达式 该电路的输出即为状态,各触发器的激励函数表达式为 J1 = K1 = 1 ; J2 = K2 = x⊕y1

一.逻辑函数表达式

同步时序电路的结构和功能,可用3组逻辑函数表达式描述。 1.输出函数表达式: Zi = fi(x1,…,xn ,y1,…,ys) i=1,2,…,m(Mealy型电路) Zi = fi(y1,…,ys) i=1,2,…,m (Moore型电路)

第五章 同步时序逻辑电路

2.激励函数表达式: 激励函数又称为控制函数,它反映 了存储电路的输入Y与外部输入x和电路状 态y之间的关系。其 函数表达式为 Yj = gj(x1,…,xn,y1,…,ys) j =1,2,…,r

第五章 同步时序逻辑电路

第五章 同步时序逻辑电路

第五章 同步时序逻辑电路

本章知识要点:

时序逻辑电路的基本概念; 同步时序逻辑电路的分析和设计方法; 典型同步时序逻辑电路的分析和设计。

第五章 同步时序逻辑电路

5.1

5.1.1

概

述

时序逻辑电路的定义、结构和特点

一.定义 若逻辑电路在任何时刻产生的稳定输出信号 不仅与电路该时刻的输入信号有关,还与电路 过去的输入信号有关,则称为时序逻辑电路。

00 01 10 11

00/0 10/0 00/0 00/0

01/0 01/0 01/0 01/0

演示动画

第五章 同步时序逻辑电路

4.

说明电路的逻辑功能

设电路初始状态为“00”,输入x为脉冲信号,其输入 序列为010110100。根据状态图可作出电路的状态响应序 列和输出响应序列如下: CP: 1 2 3 4 5 6 7 8 9 x: 0 1 0 1 1 0 1 0 0 y2: 0 0 0 1 0 0 1 0 1 y1: 0 0 1 0 1 1 0 1 0 y2n+1: 0 0 1 0 0 1 0 1 0 y1 n+1: 0 1 0 1 1 0 1 0 0 Z: 0 0 0 1 0 0 1 0 0 由输入、输出序列可以看出,一旦输入x出现信号“101”, 输出Z便产生一个相应的1,其他情况下输出Z为0。因此,该 电路是一个“101”序列检测器。

第五章 同步时序逻辑电路

(2) 现态与次态 同步时序电路中的现态与次态是针对某个时钟脉冲而言的。 现态----指时钟脉冲作用之前电路所处的状态。 次态----指时钟脉冲作用之后电路到达的状态。 注意:前一个脉冲的次态即后一个脉冲的现态!

(3) 对时钟的要求 脉冲的宽度:必须保证触发器可靠翻转; 脉冲的频率:必须保证前一个脉冲引起的电路响应完全结 束后,后一个脉冲才能到来。 2. 异步时序逻辑电路 异步时序逻辑电路的存储电路可由触发器或延时元件组成, 电路中没有统一的时钟信号同步,电路输入信号的变化将直接 导致电路状态的变化。

第五章 同步时序逻辑电路

三.状态图

状态图:是一种反映同步时序电路状态转换规律及相应输 入、输出取值关系的有向图。

在状态图中,用圆圈表示电路的状态,连接圆圈的有向线 段表示状态的转换关系,箭头的起点表示现态,终点表示次态, 当箭头起止于同一状态时,表明在指定输入下状态不变。

第五章 同步时序逻辑电路

第五章 同步时序逻辑电路

Moore型电路状态表的格式如左下表所示。

现态 y y

次态yn+1 输入 x yn+1 Moore型

输出 Z

Z

考虑到Moore型电路的 输出Z仅与电路的现态y有 关,为了清晰起见,将输 出单独作为一列,表示其 值完全由现态确定。

状态表是同步时序电路分析和设计中常用的工具,它非常 清晰地给出了同步时序电路在不同输入和现态下的次态和输出。

第五章 同步时序逻辑电路

2.列出电路次态真值表 根据激励函数表达式和D触发器的功能表,可作出该电路 的次态真值表如下表所示。

第五章 同步时序逻辑电路

3.作出状态表和状态图 根据输出函数表达式和次态真值表,可作出该电路的状 态表和状态图如下。

现 态 次态/输出(y2n+1y1n+1/Z) y2 y1 X=0 X=1

第五章 同步时序逻辑电路

若一个时序逻辑电路没有专门的外部输出信号,而是以 电路状态作为输出,则可视为Moore型电路的特殊情况。 无论是同步时序逻辑电路或是异步时序逻辑电路,均有 Mealy型和Moore型两种模型。 同步时序逻辑电路中两种模型的结构框图如下图所示。

第五章 同步时序逻辑电路

三.按输入信号形式分类

第五章 同步时序逻辑电路

2.列出电路次态真值表

J 2 K 2 x y1

输入 x 0 0 0 0 1 1 1 1 现态 y2 y1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 激励函数 J2 K2 JI K1 0 1 0 1 1 0 1 0 0 1 0 1 1 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 次 态

次态 x=0 0 1 1 0 1 0 1 0

n yn +1 y1 +1 2

x=1 1 0 0 1 1 0 1 0

演示动画

第五章 同步时序逻辑电路

4.描述电路的逻辑功能。 由状态图可知,该电路是一个2 位二进制数可逆计数器。 当输入x=0 时,可逆计数器进行加1计数,其计数序列为 00 01 10 11

第五章 同步时序逻辑电路

二.结构

时序逻辑电路由组合电路和存储电路两部分组成,通过反馈 回路将两部分连成一个整体。

图中,x1,„,xn为输入信号;Z1,„,Zm为输出信号;y1,„ ,ys为时 序逻辑电路的“状态”;Y1,„,Yr为时序逻辑电路中的激励信号;CP为时 钟脉冲信号,是否存在CP,取决于时序逻辑电路的类型。

现态 y 次态yn+1/输出Z 输入 x yn+1/Z

y

Mealy型

表格的上方从左到右列出一 位输入x的全部取值组合,表格 左边从上到下列出电路的全部状 态y,表格的中间列出对应不同 输入组合和现态下的次态yn+1和 输出Z。

表中,列数 = 一位输入的所有取值组合数; 行数 = 触发器的状态组合数。

用状态图描述同步时序电路的逻辑功能具有直观、形象 等优点。 状态图和状态表示是同步时序电路分析和设计的重要工具, 相比之下,状态表更规范,状态图更形象。

四.时间图

时间图是用波形图的形式来表示输入信号、输出信号和 电路状态等的取值在各时刻的对应关系,通常又称为工作波 形图。在时间图上,可以把电路状态转换的时刻形象地表示 出来。

激励函数 J2 K2 JI K1 0 1 0 1 1 0 1 0 0 1 0 1 1 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

次 态

n yn +1 y1 +1 2

0 1 1 0 1 0 0 1

1 0 1 0 1 0 1 0

现态 y2 y1 0 0 1 1 0 1 0 1

当输入x=1时,可逆计数器进行减1计数,其计数序列为 00 01 10 11

在时序逻辑电路分析中,除了状态图和状态表之外,通常 还用到时间图。

第五章 同步时序逻辑电路

作时间图的一般步骤: ● 假设电路初始状态,并拟定一典型输入序列; ● 作出状态和输出响应序列; ● 根据响应序列画出波形图。

设电路的初始状态y2y1=00,输入x为电平信号,典型输 入序列为111100000,根据状态图可作出电路的状态响应序 列如下: CP: x : y2 : y1 : y2n+1: y1n+1: 1 1 0 0 1 1 2 1 1 1 1 0 3 1 1 0 0 1 4 1 0 1 0 0 5 0 0 0 0 1 6 0 0 1 1 0 7 0 1 0 1 1 8 0 1 1 0 0 9 0 0 0 0 1