第8章 输入输出接口(1)

D8Z输入输出接口

2、条件传送方式 CPU 通过执行程序不断读取并测试外设状态,如果输 入外设处于已准备好状态或输出外设为空闲状态时,则CPU 执行传送信息指令。由于条件传送方式是CPU在不断调查外 设的当前状态后才进行信息传送,所以也称为“查询式传 送”。因此,条件传送方式的接口电路应包括:传送数据端 口及传送状态端口。当输入信息时,查询到外设准备好后, 则使接口的“准备好”标志位置1。当输出信息时,外设取 定一个数据后,传送状态端口使标志为“空闲”状态,可以 接收下一个数据。

8.3 ቤተ መጻሕፍቲ ባይዱ编程并行通信接口片8255A

一、8255的内部结构及其功能 1、8255的引脚 参见图5.13(a),共有40条引线。电源与地线2条;与外 设相连的有24条;与CPU相连的有14条。

图5.13 8255引脚和功能示意图

2、8255的功能

如图5.13(b)所示,接口的左边与CPU连接,右 边与外设连接,有A、B、C三个8位端口,而C口 可分成两个4位的端口。每个端口都可以通过编 程设定为输入端口或输出端口,但有各自不同的 方式和特点。端口C可以独立使用,但通常是配 合端口A和端口B工作,为这两个端口的输入输 出提供联络信号。

三、DMA方式

利用程序中断方式,虽然可以提高CPU的工作效率,但它 仍需要由程序来传送数据,并在中断处理时要“保护现场”和 “恢复现场”等,要占用一定时间,是每传送一个字节大约要 几十微秒到几百微秒,这对于高速外设就显得太慢了。 DMA方式是一种由专门的硬件电路执行I/O交换的传送方式, 它让外设接口与内存直接进行高速的数据交换,而不必经过 CPU,实现对存储器的直接存取。这种专门的硬件叫DMA控制器, 简称DMAC。当接口准备好就向DMAC发DMA请求,CPU通过HOLD引 脚接收DMAC发出的总线请求;CPU在完成当前总线操作后,就 发出HLDA的总线响应信号给DMAC, DMAC收到此信号后便接管 对总线的控制权,开始DMA操作。当DMA传送结束,DMAC将HOLD 信号变成低电平,并放弃对总线的控制权。CPU检测到HOLD为 低后,也将HLDA变成低,并恢复对总线的控制权。

微机原理第八章 串行通信及串行接口

1. 可编程串行接口典型结构

✓状态寄存器

✓控制寄存器

✓数据输入寄存器--串行输入/并行 输出移位寄存器

✓数据输出寄存器--并行输入/串行 输出移位寄存器

2. 串行通信基本概念

在串行通信时,数据和联络信号使用同一条信号线 来传送,所以收发双方必须考虑解决如下问题: ❖ 波特率---双方约定以何种速率进行数据的发送和接收 ❖ 帧格式---双方约定采用何种数据格式 ❖ 帧同步---接收方如何得知一批数据的开始和结束 ❖ 位同步--- -接收方如何从位流中正确地采样到位数据 ❖ 数据校验--- -接收方如何判断收到数据的正确性 ❖差错处理---收发出错时如何处理 收发双方必须遵守一些共同的通信协议才能解决上述问题。

串行通信适于长距离、中低速通信

并行通信

将数据的各位同时在多根并行传输线上进行传输。

D0 0

D1 1

D2 0

源

D3 1

D4 D5

0 1

D6 1

D7 0

D0 D1 D2 D3 目 D4 的 D5 D6 D7

数据的各位同时由源到达目的地 → 快 多根数据线 → 短距离(远程费用高)

并行通信适于短距离、高速通信

工作方式下。

(8)错误检测 • 传输错误 • 覆盖错误

二、 接口与系统的连接

从结构上,可把接口分为两个部分,其中和 外设相连的接口结构与具体外设的传输要求及数 据格式相关,因此,各接口的该部分互不相同; 而与系统总线相连的部分,各接口结构类似,一 般都包括:

1. 总线收发器和相应的逻辑电路

2. 联络信号逻辑电路

接收端需要一个时钟来测定每一位的

时间长度。

波特率/位传输率---每秒传输的离散信号 的数目/每秒传输的位数。 波特率因子---

第八章-输入输出系统(共64张PPT)全文编辑修改

3、中断类型:

– 按中断产生的位置: • 外部中断:CPU以外的部件引起的中断。 外中断又可分为不可屏蔽中断和可屏蔽中断 两种。不可屏蔽中断优先级较高,常用于 应急处理,如掉电、内存读写校验错等。 可屏蔽中断级别较低,常用于一般I/O设 备的数据传送。

• 内部中断:由CPU内部硬件或软件引起的中 断,如单步中断、溢出中断。

路之前,还要受到屏蔽触发器的控制。

当MASK=1,表示对应中断源的请求被屏蔽。 当MASK=0,才允许对应中断源的请求参与排队判优

中断屏蔽寄存器的作用

INT

≥1

由程序 控制

中断屏蔽 0 1 0 1 0 1 0 1 寄存器 &

向 量 地 址

……

编 码 器

排 队 逻 辑

&

&

& 0 1 0 1 0 1 0 1 中断请求 寄存器

程序查询方式——程序流程图

设置计数值

修改计数器

设置内存缓冲区首址

比如指令系统中的软中断指令INT n。 中断处理次序和中断响应次序是两个不同的概念:

否

中断事件在提出中断请求的同时,通过硬件向主机提供中断服务程序的入口地址,即向量地址。 传送完?

CPU等候输入设备的数据成为有效

(2)数据通道中断源,也称直接启存动储外器设存放(DMA)操作。

3级

4级

则 只 需 使 中 断 屏 蔽 码 改 (1)一般的输入、输出外围设备。

一般是故障引起的中断最优先;

为: 第1级 1 1 1 1 (4)DMA传送速度快,CPU和外设并行工作,提高了系统的效率;

先由主机通过启动指令启动外设工作,启动后主机用测试指令不断查询外设工作状态,当输入设备处于准备好状态或输出设备处于空闲状态时,

IBM—PC(80x86)汇编语言与接口技术-第8章 输入输出程序设计

8259A

76 5 4

中断屏蔽寄存器21H

打 印 机

3210

IN AL, 21H AND AL,0FDH

键定 时

盘器

OUT 21H,AL

76 5 4

中断命令寄存器20H

EOI

3 2 1 0 MOV AL, 20H OUT 20H, AL

11

中断向量表

00000 类型0的(IP) 类型0的(CS)

00004 类型1的(IP) 类型1的(CS)

speaker_on endp

speaker_off proc push ax in al, 61h and al, 0fch out 61h, al pop ax ret

speaker_off endp

end

8

3. 中断传送方式

中断源:引起中断的事件

外中断(硬中断):

外设的 I/O 请求 —— 可屏蔽中断 电源掉电 / 奇偶错 —— 非屏蔽中断

15

例:用 DOS 功能调用存取中断向量

MOV AL, N

MOV AH, 35H

INT 21H

PUSH BX

; 保存原中断向量

PUSH DS

MOV AX, SEG INTHAND

MOV DS, AX

MOV DX, OFFSET INTHAND

MOV AL, N

MOV AH, 25H

08 系统定时器 09 键盘 0A 彩色/图形接口 0B 保留 0C 串行通讯口 0D 保留 0E 软盘 0F 打印机

10

中断的条件:

设置CPU中断允许位:

FLAGS 中的 IF 位 = 1 允许中断 ( STI ) = 0 禁止中断 ( CLI )

长沙理工大学微机原理题目答案

长沙理⼯⼤学微机原理题⽬答案3.1 8086CPU与8088CPU有哪些相同之处:⼜有哪些区别?3.2 8086系统的物理地址是如何得到的?假如CS=2000H,IP=2100H其物理地址应是多少?3.3 什么是总线周期?8086CPU的⼀个总线周期包括多少时钟周期,什么情况下插⼊Tw等待周期:插⼊多少个Tw取决于什么因素?第四章习题4.1 需要定时刷新的存储器是(B ).A.SARMB.DRAMC.EPROMD.EEPROM4.2利⽤容量为4K×2b的SRAM芯⽚构成从A4000H到B7FFFH的内存,⽤这样的芯⽚需要( C ).A.40⽚B.60⽚C.80⽚D.100⽚4.3 突然断电后,计算机__C___中的数据将全部丢失.A.硬盘B.ROM和RAMC.RAMD.ROM4.4 下⾯的说法中,正确的是___D___.A.EPROM是不能改写的.B.EPROM是可以改写的,所以也是⼀种读写存储器.C.EPROM只能改写⼀次.D.EPROM是可以改写的,但他不能作为读写存储器.4.5 可直接存取16M字节内存的微处理器,其地址总线需_A___条.A.24B.16C.204.6某微机系统的存储器地址空间为A8000H~CFFFFH,若采⽤单⽚容量为16K×1位的SRAM芯⽚构成,回答以下问题:(1)系统存储容量为多少?(2)组成该存储系统共需该类芯⽚多少个?(3)整个系统应分为多少个芯⽚组:解4.6:(1)系统存储容量=CFFFFH-A80000H+1=28000H(B)=160(KB).(2)所需芯⽚=160K×8位/16K×1位=80(个).(3)该芯⽚字长不⾜8位,应以8位为⼀组构成字节单元.所以80个芯⽚应分成80/8=10个芯⽚组.4.7下列RAM各需要多少条地址线进⾏寻址,多少条数据I/O线?(1)64K×1 (2)256K×4解4.7: (1)16条地址线,⼀条数据I/O线.(2)需要18条地址线,4条数据I/O线.5.1、设DS=6000H,ES=2000H,SS=1500H,SI=00A0H,BX=0800H,BP=1200H,数据变量V AR为0050H。

计算机组成原理习题 第八章输入输出系统

第八章输入输出系统一、填空题;1.直接内存访问(DMA)方式中,DMA控制器从CPU完全接管对的控制,数据交换不经过CPU,而直接在内存和之间进行。

2.通道是一个特殊功能的,它有自己的专门负责数据输入输出的传输控制。

3.并行I/O接口和串行I/O接口是目前两个最具有权威性的标准接口技术。

4.在计算机系统中,CPU对外围设备的管理,除了程序查询方式、程序中断方式外,还有方式、方式和方式。

5.程序中断方式控制输入输出的主要特点是,可以使A 和B 并行工作。

6.DMA控制器按其A 结构,分为B 型和C 型两种。

7.通道是一个特殊功能的A ,它有自己的B 专门负责数据输入输出的传输控制,CPU只负责C 功能。

8.通道有三种类型:A 通道、B 通道、C 通道。

9.二、选择题:1.下面有关“中断”的叙述,______是不正确的。

A.一旦有中断请求出现,CPU立即停止当前指令的执行,转而去受理中断请求B.CPU响应中断时暂停运行当前程序,自动转移到中断服务程序C.中断方式一般适用于随机出现的服务D.为了保证中断服务程序执行完毕以后,能正确返回到被中断的断点继续执行程序,必须进行现场保存操作2.中断向量地址是______。

A. 子程序入口地址B. 中断服务例行程序入口地址C. 中断服务例行程序入口地址的地址D. 主程序返回地址3.在数据传送过程中,数据由串行变并行或由并行变串行,其转换是通过______。

A. 移位寄存器B. 数据寄存器C. 锁存器D. 指令寄存器4.下述I/O控制方式中,主要由程序实现的是______。

A. PPU(外围处理机)方式B. 中断方式C. DMA方式D. 通道方式5.采用DMA方式传送数据时,每传送一个数据要占用______的时间。

A. 一个指令周期B. 一个机器周期C. 一个时钟周期D. 一个存储周期6.发生中断请求的条件是______。

A. 一条指令执行结束B. 一次I/O操作开始C. 机器内部发生故障D. 一次DMA操作开始7.中断向量地址是______。

微机原理与接口技术课件全 (9)

(2)键的识别 通常有两种方法可识别被按之键:一种是“行扫描”法; 一种是“反转”法。 1)行扫描法 依次对每一行进行扫描,选使被扫描的行为低电平,其它 所有的行均为高电平,接着检测各列线的状态(称为“列”)。 若各列码均为高电平(即列码为全1),则被按之键不在这行。 继续扫描下一行;若列线不全为高电平(即列码为非全1),则 被按之在此行。根据行扫描码及列码就可知被按之键的坐标值 (即位置码)。再根据位置码通过查表可得到它的键值。查表 法的扫描子程序流程图如图7-6所示。

四、输入/输出寻址方式

当主机执行I/O操作时,应先对I/O接口中的端口进行寻址, 其寻址方式有如下两种: 此时,I/O端口单独编址。CPU指令系统中有专门用于I/O操 作的指令——I/O指令,CPU访问I/O端口时发出I/O读命令或写 命令,访问内存时发存储器读或写命令。因此,端口地址与存 储单元地址可重叠。此时,I/O端口不占用存储空间且与访问 I/O设备指令有别。 这种寻址方式中,将I/O端口与存储单元统一编址,即CPU 把I/O端口作为存储单元对待,I/O端口占用一定的存储空间。 采用这种寻址方式的CPU指令系统中没有专门的I/O指令,

微型机中常外设有LED显示器、CRT显示器、键盘、打印机、软 磁盘存储器等。单片机应用系统中常设置LED显示器、拔盘、键 盘、点阵式打印机等外设。

§8-2 键盘及其接口

返回

在微型机系统中,键盘是最常用的输入设备,键盘通常由 数字键和功能键组成,其规模取决于系统的要求。

键盘可分为编码键盘和非编码键盘两种,前者有检测键闭 合,去抖动及产生相应键编码的硬件电路,而后者则没有这些 硬件,上述功能在有少量的硬件支持下由软件来完成。由此可 见编码键盘产生键编码的速度快且基本上不占用CPU时间,但硬 件开销大,电路复杂,成本高;非编码键盘则硬件开销省,电 路简单,成本低,但占用CPU时间较长。

大学理科课件 第8章 IO接口与DMA技术

8.1.2 I/O接口的基本结构

I/O接口的基本结构如图8.1所示。

I/O接口 数据总线 数据输入寄存器

数据输出寄存器

地址总线 外 状态寄存器 控制寄存器 中断控制逻辑 围 设 备

cpu

控制总线

图8.1 I/O 接口的基本结构

8.1.3 I/O端口的编址方式

输入输出接口包含一组称为I/O端口的寄存器。为了让 CPU能够访问这些I/O端口,每个I/O端口都需有自己 的端口地址(或端口号)。 在一个微型计算机系统中,如何编排这些I/O接口的端 口地址,称为I/O端口的编址方式。

I/O端口和存储器单独编址的地址空间分布如图8.3所 示。

存储单元

存储器 地址空间

I/O 端口

I/O 地址空间

图8.3 I/O 端口和存储器单独编址

这种编址方式的优点是: 第一,I/O端口不占用存储器地址,故不会减少用户的 存储器地址空间; 第二,单独I/O指令的地址码较短,地址译码方便, I/O指令短,执行速度快; 第三,采用单独的I/O指令,使程序中I/O操作和其他 操作层次清晰,便于理解。

内存

CPU 和总线 控制逻辑

(6) 内存把数据送数据总线

HOLD HLDA 数 据 总 线

接口

I/O 设备

(7) 接口锁存数据

地 址 总 线

(5) DMA响应 (2) 发总线请求 控 制 总 线 (3) 总线允许

(1) 接口准备就绪,发 DMA请求

DMA 控制器

(4) DMA控制器把地址送地址总线 (8)DMA 控制器撤销总线请求 (9) CPU收回总线控制权

控制寄存器 状态寄存器 地址寄存器 字节计数寄存器

单片机实用教程_8 89C51单片机并行输入输出

P3 口的第二功能

口线 P3.0 P3.1 信号 RXD TXD 功 能 串行口数据输入(接收数据) 串行口数据输出(发3.5

P3.6 P3.7

INT0 INT1 T0 T1

WR RD

外部中断0输入 外部中断1输入 定时器0的外部输入(计数输入) 定时器1的外部输入(计数输入)

外部数据存储器写选通控制输出 外部数据存储器读选通输出控制

8.2 并行输入/输出端口P0、P1、P1和P3 8.2.1 P0端口 ⑴ P0口的结构: P0口有8位, 每一位由一个输出锁存器、两个三态 输入缓冲器和输出驱动电路及控制电路组成。

⑵ P0口作通用的I/O口使用

P0口是漏极开路的8位准双向I/O口. P0口为特殊功能寄存器, 既可以用直接寻址方式对P0口进行字节操作, 也可以按按位寻址方式,进行位操作。

P2端口及其各位的地址

位地址/位定义 A5H P2.5 A4H P2.4 A3H P2.3 A2H P2.2 A1H P2.1 LSB A0H P2.0 字节地址 A0H

P2口作输出时,直接用传送指令进行操作。 例如: MOV P2 ,A P2口作输入时, 要先写“1”, 然后读入(准双向口)。 例如: MOV P2 ,#0FFH MOV A ,P2

表8.1 P0端口及其各位的地址

SFR MSB 位地址/位定义 LSB 字节地址

P0

87H

P0.7

86H

P0.6

85H

P0.5

84H

P0.4

83H

P0.3

82H

P0.2

81H

P0.1

80H

P0.0

80H

P0口作输出时,直接用传送指令进行操作。 例如: MOV P0 ,A P0口作输入时,要先写“1”,然后读入(准双向口)。 例如: MOV P0 ,#0FFH MOV A ,P0

08_通用数字输入输出端口

2,模拟输入 P1口可配置为ADC1的模拟输入引脚,将P1口的相应引 脚PnMDIN位清零即可。当引脚配置为模拟输入时,不 参与交叉开关配置,在交叉开关配置中会自动跳过相应 引脚。

8.1.3 配置无引出脚的端口

尽管P4、P5、P6 和P7 在C8051F021/3 中没有对应的引脚, 但端口数据寄存器仍然存在并可为软件所用。 由于数字输入通路保持活动状态,所以建议不要将这些引脚 处于“浮空”状态,以避免因输入浮空为一个无效逻辑电平 而导致不必要的功率消耗。 下面的任何一种措施都可以防止这种情况出现:

P3:端口3 数据寄存器

位7-0: P3.[7:0]:端口3 输出锁存器位。 (写 - 输出出现在I/O 引脚,根据XBR0、XBR1 和XBR2 寄 存器的设置) 0:逻辑低电平输出。 1:逻辑高电平输出。(若相应的P3MDOUT.n 位 = 0,则为 漏极开路)。 (读-与XBR0、XBR1 和XBR2 寄存器的设置无关) 0:P3.n 为逻辑低电平。 1:P3.n 为逻辑高电平。 注:P3.[7:0] 可以由外部数据存储器接口驱动(在复用方式 作为AD[7:0]或在非复用方式作为D[7:0])。

注意: 1. P1.[7:0]可以被配置为ADC1 的输入AIN1.[7:0]。在这 种情况下,交叉开关的引脚分配将跳过这些引脚,它们的 数字输入通路被禁止,由P1MDIN寄存器决定。

2. P1.[7:0] 可以由外部数据存储器接口驱动( 在非复用 方式作为地址A[15:8])。

P1MDIN:端口1 输入方式寄存器

P3MDOUT:端口3 输出方式寄存器

位7-0: P3MDOUT.[7:0]:端口3 输出方式位。 0:端口引脚的输出方式为漏极开路。 1:端口引脚的输出方式为推挽。 注:当SDA、SCL、RX0(当UART0 工作于方式0 时)和 RX1(当UART1工作于方式0 时)出现在端口引脚时,总是 被配置为漏极开路输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

8.2 常用I/O接口芯片

第8章 输入输出接口

74LS373

第8章 输入输出接口

8.2 常用I/O接口芯片

第8章 输入输出接口

74LS244

第8章 输入输出接口

8.3 CPU与外设之间的数据传送方式 CPU与外设之间的数据传送方式一般有:

程序控制方式 中断方式 直接存储器存取方式 通道控制方式

第8章 输入输出接口

8.1.3 I/O接口的结构

数据端口:用于数据信息I/O的端口。CPU通过数据接收端口输 入数据,有的能保存外设发往CPU的数据;CPU通过数据输出 端口输出数据,一般能将CPU发往外设的数据锁存。 状态端口:CPU通过状态端口了解外设或接口部件本身的状态。 控制端口:CPU通过控制端口发出控制命令,以控制接口部件 或外设的动作。

第8章 输入输出接口

优点:

CPU对外设的操作可使用全部的存储器操作指 令,故指令多,使用方便。如可以对外设中的 数据(存于外设的寄存器中)进行算术和逻辑 运算,进行循环或移位等。 内存和外设的地址分布图是同一个。 不需要专门的输入输出指令以及区分是存储器 还是I/O操作的控制信号。

缺点:

外设占用了内存单元,使内存容量减小。

第8章 输入输出接口

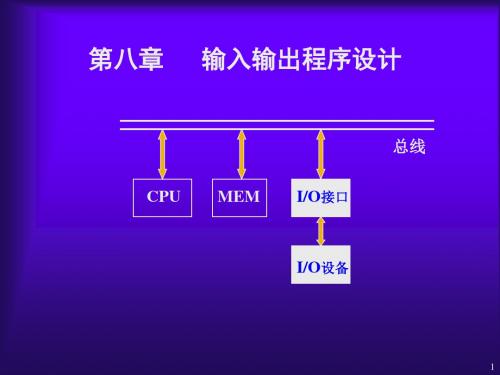

8.3.3 直接存储器存取(DMA)方式

AB DB CB

CPU

DMAC

RAM/ROM

I/O

第8章 输入输出接口

8.3.4 通道控制方式和I/O处理器 在大、中型计算机系统中,配置的I/O设备 很多,输入输出操作十分频繁,如果仅用 DMA控制器,则需要CPU不断地对各个DMA控 制器进行设置,影响CPU的正常工作。 将DMA控制器的功能增强,使其能够按CPU 的意图自行设置操作方式,控制数据传送 。于是,DMA控制器发展成了通道控制器。

第8章 输入输出接口

计算机系统中接口的位置

第8章 输入输出接口

8.1.1 CPU与I/O设备之间的接口信息 1.数据(Data)

数字量 模拟量 开关量

2.状态信息(Status) 3.控制信息(Control)

第8章 输入输出接口

8.1.2 I/O接口的主要功能 1.对输入输出数据进行缓冲和锁存 2.对信号的形式和数据的格式进行变换 3.对I/O端口进行寻址 4.提供联络信号

第8章 输入输出接口

2. I/O处理器(IOP) I/O处理器(I/O Processor)由通道控制 器发展而来,也称为I/O处理机。 主要由一个进行I/O操作的CPU、内部寄存 器、局部存储器和设备控制器组成。在一 个通道处理器中可有多个通道,分别与多 个设备控制器连接;而一个设备控制器可 控制多台外设工作。 在实际使用中,I/O处理器与主CPU构成多 处理器(或称多处理机)系统,相互并行 工作。

第8章 输入输出接口

8.3.3 直接存储器存取(DMA)方式 DMA方式由硬件自动实现的,并不需要程序进 行控制。 DMAC(称为DMA控制器)芯片来完成相关工作 ,如内存地址的修改、字节长度的控制。当

CPU放弃数据总线、地址总线及控制总线的控

制权时,由DMAC实现外设和内存间的数据交

换,同时也包括与CPU之间必要的连接。

DELAY

PROC NEAR PUSH CX WAIT0: MOV CX,2801 WAIT1: LOOP WAIT1 DEC BX JNZ WAIT0 POP CX RET DELAY ENDP

;延时子程序DELAY

第8章 输入输出接口

2.程序查询方式 也称为条件传输方式,常用于慢速设备与 CPU交换数据。 CPU与外设传输数据之前,先检查外设状态 ,如果外设处于“准备好”状态(输入设备 )或“空闲”状态(输出设备),才可以传 输数据。 为此,接口电路中除了数据端口外,还必须 有状态端口。

第8章 输入输出接口

MOV AL,0AH ;是回车且接收字符个数≤81,存换行符 MOV [SI],AL JMP EXIT ;转程序结束处理 OVERFLOW: MOV CX,17 ;初始化输出字符个数 LEA SI,MESS ;初始化显示字符串首址 OUTPUT: IN AL,36H ;读状态端口 TEST AL,01H ;测输出状态D0位 JZ OUPUT ;输出缓冲器未空,转OUTPUT MOV AL,[SI] ;取出输出字符 INC SI OUT 34H,AL ;输出字符 LOOP OUTPUT EXIT:

0 7

. .

74LS244 1Y1 2Y1 1A1 1A2

+5V

.

K0

.

. . .

K1

. .

.

2G 1G

2A4

.

K7

74LS373 LED0 D0~D7 Q0 Q1 G LED1

≥1

. .

IOWC OE Q7

. . .

LED7

第8章 输入输出接口

【例8-2】硬件连接如前例图所示,要求LED0~LED7循环 电亮。 MOV DX,200H ;设置I/O端口 MOV CL,01H ;设置输出初值 AGAIN: • 方式1:K0闭合,则退出循环。 „„ • 方式2:有一个开关闭合,则 MOV AL,CL 退出循环。 OUT DX,AL ;输出控制LED MOV BX,100 ;参数,实现1秒软延时 CALL DELAY ROL CL,1 ;循环左移1位 JMP AGAIN EXIT: RET 第8章 输入输出接口

第8章 输入输出接口

MESS DB ‘BUFFER OVERFLOW’,0DH,0AH BUFFER DB 82 DUP(?) 。。。。。。 LEA SI,BUFFER MOV CX,81 INPUT: IN AL,36H ;读状态端口 TEST AL,02H ;测输入状态D1位 JZ INPUT ;未“准备好”转INPUT IN AL,32H ;读取输入字符 MOV [SI],AL ;输入字符存缓冲区 INC SI CMP AL,0DH ;输入字符为回车否? LOOPNE INPUT ;不是回车且接收字符个数未超过81,转INPUT JNE OVERFLOW ;不是回车且接收字符个数超过81,转OVERFLOW

第8章 输入输出接口

8.1.4 输入输出的寻址方式 2. I/O映像的I/O寻址

I/O端口地址与存储单元地址分开编址。CPU有专门的I/O指 令,用地址来区分不同的外设。 但要注意实际上是以端口(Port)作为地址单元,因为一 个外设不仅有数据寄存器还有状态寄存器和控制命令寄存器,它 们各需要一个端口才能加以区分,故一个外设往往需要数个端口 地址。

第8章 输入输出接口

本章主要内容

1

2 3

I/O接口概述 常用I/O接口芯片 CPU与外设之间的数据传送方式

第8章 输入输出接口

8.1 I/O接口概述 输入和输出设备是计算机系统的重要组成 部分,完成输入/输出(简称I/O)操作的 部件称为输入/输出接口。 各种外部设备通过输入输出接口与系统相 连,并在接口电路的支持下实现数据传输 和操作控制。

第8章 输入输出接口

程序查询方式的一般过程为:

CPU从接口中读取状态字; CPU检测状态字的相应位,是否满足“就绪” 条件,如不满足,则转1); 如状态位表明外设已处于“就绪”条件,则传 输数据。

第8章 输入输出接口

【例8-3】 从终端往缓冲区输入1行字符, •当遇到回车符(0DH)或超过81个字符时,输入结束, 并自动加上一个换行符(0AH)。如果在输入的81个字符 中没有回车符,则在终端上输出信息“BUFFER OVERFLOW”。 •已知终端接口的数据输入端口地址为32H,数据输出端口 地址为34H,状态端口地址为36H •若状态端口的D1=1,表示输入缓冲器已准备好数据, CPU可读取数据; •若状态端口的D0=1,表示输出缓冲器已空,CPU可往 终端输出数据。 •终端接口电路具有根据相应操作对状态寄存器自动置1和 清0功能。

第8章 输入输出接口

8.3.1 程序控制方式 采用程序控制方式时,状态和数据的传输 由CPU执行一系列指令完成。 这种方式又可分为无条件传输方式和程序 查询方式。

第8章 输入输出接口

1.无条件传输方式 CPU不需要了解外设状态,直接与外设传输 数据,适用于按钮开关、发光二极管等简 单外设与CPU的数据传送过程。 这种传输方式的特点是硬件电路和程序设 计都比较简单,一般用于能够确信外设已 经准备就绪的场合。

.

≥1

.

2G 1G

2A4

.

K7

74LS373 LED0 D0~D7 G IOWC OE Q7 LED7 Q0 Q1 LED1

. .

. . .

第8章 输入输出接口

AGAIN: MOV DX,200H D ~D IN AL,DX ;读开关状态 ≥1 NOT AL IORC OUT DX,AL ;输出 Y . JMP AGAIN

第8章 输入输出接口

8.3.2中断方式 CPU不主动去查询外设的状态,而是让外设在 数据准备好之后再通知CPU。 这样,CPU在没接到外设通知前只管做自己的 事情,只有接到通知时才执行与外设的数据

传输工作,从而大大提高CPU的利用率。

第8章 输入输出接口

8.3.2中断方式

主 程 序

中断申请信号

第8章 输入输出接口

8.1.4 输入输出的寻址方式 1.存储器映像的I/O寻址

存储单元和I/O端口的地址统一编址。把一个外设端口作为 存储器的一个单元来对待,故每一个外设端口占有存储器的一个 地址。 从外部设备输入一个数据,作为一次存储器读的操作;而 向外部设备输出一个数据,则作为一次存储器写的操作。

第8章 输入输出接口

第8章 输入输出接口

1. I/O 通道( I/O Channel ) 早期的“通道”是由一些简单的、主要用 于数据输入输出的CPU构成,可配置简单的 输入输出程序。 主CPU只需使用简单的通道命令启动通道, 二者即可并行工作。输入输出程序可以在 主存中,也可以在通道的局部存储器中。 主CPU一旦启动通道工作,通道控制器即从 主存或通道存储器中取出相应的程序,控 制数据的输入输出。