数字设计原理与实践(第四版)课后各章节习题答案

数字设计原理与实践答案整理

1.3ASIC Application-Specific Integrated CircuitCAD Computer-Aided DesignCD Compact DiscCO Central OfficeCPLD Complex Programmable Logic DeviceDIP Dual In-line PinDVD Digital Versatile DiscFPGA Field-Programmable Gate ArrayHDL Hardware Description LanguageIC Integrated CircuitIP Internet ProtocolLSI Large-Scale IntegrationMCM Multichip ModuleMSI Medium-Scale IntegrationNRE Nonrecurring EngineeringPBX Private Branch ExchangePCB Printed-Circuit BoardPLD Programmable Logic DevicePWB Printed-Wiring BoardSMT Surface-Mount TechnologySSI Small-Scale IntegrationVHDL VHSIC Hardware Description LanguageVLSI Very Large-Scale Integration1.4ABEL Advanced Boolean Equation LanguageCMOS Complementary Metal-Oxide SemiconductorJPEG Joint Photographic Experts GroupMPEG Moving Picture Experts GroupOK 据说是Oll Korrect(All Correct)的缩写。

数字设计原理与实践第四版

数字设计原理与实践第四版

1. 引言:数字设计原理与实践第四版简介

2. 数字电路基础概念介绍

3. 逻辑门及其应用案例

4. 组合逻辑电路设计与实现

5. 时序逻辑电路设计与实现

6. 存储器和寄存器的设计和使用

7. 有限状态机设计与实现

8. CPU和指令集设计原理

9. 使用Verilog进行数字电路仿真和验证

10. FPGA的原理和应用

11. 高级数字电路设计技术

12. 数字系统和嵌入式系统设计原理

13. 数字信号处理和通信系统设计

14. 数字设计中的优化和可靠性考虑

15. 数字电路测试和故障诊断技术

16. 未来数字电路设计的发展趋势

17. 结语:数字设计原理与实践的重要性和应用前景

18. 附录A:数字电路设计常用表格和参考资料

19. 附录B:数字电路布线和布板设计技巧

20. 附录C:数字电路设计软件工具的介绍与使用指南。

数字电子技术基础. 第四版. 课后习题答案详解

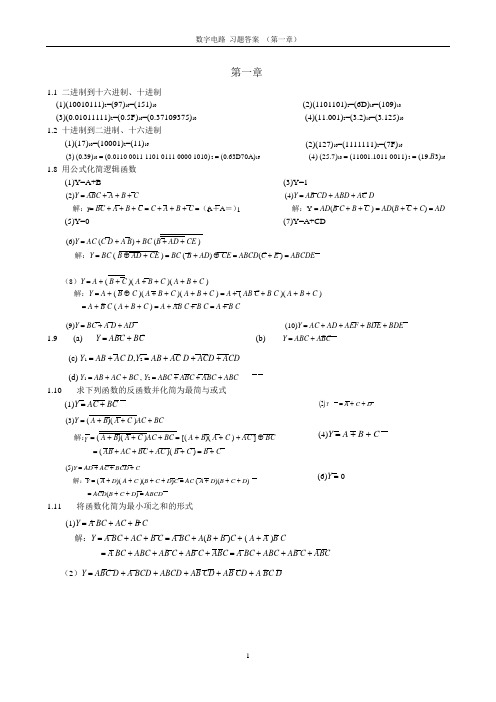

(1)Y=A+B

(2)YABCABC

解:BCABCCABC(A+A=)

(5)Y=0

(2)(1101101)2=(6D)16=(109)10

(4)(11.001)2=(3.2)16=(3.125)10

(2)(127)10=(1111111)2=(7F)16

(4) (25.7)10(11001.1011 0011)2(19.B3)16

1.12

将下列各函数式化为最大项之积的形式

(1)Y(ABC)(ABC)(ABC)

(3)YM0⋅M3⋅M4⋅M6⋅M7

(5)YM0⋅M3⋅M5

(2)Y(ABC)(ABC)(ABC)

(4)YM0⋅M4⋅M6⋅M9⋅M12⋅M13

1.13

用卡诺图化简法将下列函数化为最简与或形式:

(3)Y(AB)(AC)ACBC

(2)Y

ACD

解:(AB)(AC)ACBC[(AB)(AC)AC]⋅BC

(ABACBCAC)(BC)BC

(5)YADACBCDC

解:Y(AD)(AC)(BCD)CAC(AD)(BCD)

ACD(BCD)ABCD

(4)YABC

(6)Y0

1.11

将函数化简为最小项之和的形式

(3)Y=1

(4)YAB CDABDAC D

解:YAD(B CBC)AD(BCC)AD

(7)Y=A+CD

(6)YAC(C DA B)BC(BADCE)

解:YBC(B⋅ADCE)BC(BAD)⋅CEABCD(CE)ABCDE

(8)YA(BC)(ABC)(ABC)

解:YA(B⋅C)(ABC)(ABC)A(AB CB C)(ABC)

数字设计原理与实践第2章答案

2.2将下面的八进制数转换成二进制数和十六进制数:(a) 12348=10100111002=29C16(c) 3655178=111101011010011112=1EB4F16(e) 7436.118=111100011110.0010012=F1E.24162.3将下面的十六进制数转换成二进制数和八进制数:(a) 102316=10000001000112=100438(c) ABCD16=10101011110011012=1257158(e) 9E36.7A16=1001111000110110.01111012=117066.364 82.5 将下面的数转换成十进制:(e) 10100.11012=20.812510(f) F3A516=6237310(g) 120103=13810(i) 71568=3694102.6 完成下面的数制转换:(e) 13210=100001002(f) 2385110 =5D2B16(g) 72710=104025(i) 143510=263382.7 将下面的二进制数相加,指出所有的进位:解:2.8利用减法而不是加法重复训练题2.7,指出所有的借位而不是进位。

解:2.9 将下面的八进制数相加:(b) 5 7 7 3 4+ 1 0 6 6解:(b) C 1 1 1 1 05 7 7 3 4+ 1 0 6 66 1 0 2 22.10 将下面的十六进制数相加:(b) 4 F 1 A 5+ B 8 D 5解:(b) 4 F 1 A 5+ B 8 D 55 A A 7 A2.11 写出下面每个十进制数的8位符号—数值、二进制补码、二进制反码表示:+25、+120、+82、42、6、111。

解:对正数来说,规定其符号—数值、二进制补码、二进制反码表示相同,符号位为0。

对负数,规定其符号—数值码为对应整数的符号—数值码符号位取反,其二进制补码为对应整数的补码,其二进制反码为对应整数的反码。

数字设计原理与实践 第四版

数字设计原理与实践第四版

数字设计原理与实践第四版是一本介绍数字电路设计基础知识和实践的教材。

本书主要分为五个部分,分别是数字系统基础、组合逻辑设计、时序逻辑设计、专用逻辑器件与PLD设备以及数字系统的设计示例。

在数字系统基础部分,本书首先介绍了数字系统的基本概念和表示方法,包括二进制数表示、布尔代数和逻辑运算。

接着讲解了数字电路的基本组成部分,如逻辑门、多路选择器、译码器等,并介绍了常用的编码方式如BCD码和格雷码。

在组合逻辑设计部分,本书详细介绍了基本的组合电路设计方法,包括真值表、卡诺图和最小化布尔函数等。

同时还介绍了常见的组合逻辑器件和集成电路,如多输入AND、OR和XOR门等。

在时序逻辑设计部分,本书介绍了时钟信号的基本概念和使用方法,同时还详细讲解了触发器、计数器、移位寄存器等时序电路的设计和应用。

在专用逻辑器件与PLD设备部分,本书介绍了常见的专用逻辑器件如加法器、比较器和MUX等,并详细介绍了可编程逻辑器件(PLD)的原理和应用,包括可编程逻辑阵列(PLA)和可编程逻辑芯片(CPLD)等。

在数字系统的设计示例部分,本书通过实际案例分析和设计实例,将前面所学的知识应用到具体的数字系统设计中,如计算

机CPU设计、外设接口设计等。

综上所述,数字设计原理与实践第四版是一本全面介绍数字电路设计原理和实践的教材,内容丰富、结构清晰,适合作为数字电路设计和相关专业学生的教材和参考书。

数字设计原理与实践 第四版 (john F.Wakerly ) 课后答案

3.65 在图 3-32(b)中,有多少电流与功率被浪费了。 解:浪费的电流为流过 4kΩ电阻的电流:

I=(5-0.24)/4=1.19 mA 浪费的功率为上述电流经过两个电阻产生的功率: P = RI2 = 4.2 x (1.19)2 = 5.95 mW

解:由图中可以看到,输出 3.5V 对应的输入为 2.4V,输出 1.5V 对应 的输入为 2.5V; 所以,高态噪声容限为:3.5-2.5=1 V ;低态噪声 容限为:2.4-1.5=0.9 V。

3.26 利用表 3-3 计算 74HC00 的 p 通道和 n 通道的导通电阻。 解:采用极端值计算(对商用芯片,最低电源电压设为 4.75V) 表中所列输出电压与电流关系如图所示:

=157255.5756748 2.5 将下面的数转换成十进制数。

(a) 11010112=107 (b) 1740038=63491 (c) 101101112=183

(d) 67.248=55.3125 (e)10100.11012=20.8125 (f)F3A516=

62373

(g) 120103=138

(h) AB3D16=43837

(i) 71568=3694

(j) 15C.3816=348.21875

2.6 完成下面的数制转换。

(a) 125= 1 111 1012 (b) 3489= 66418 (c) 209= 11 010 0012

(d) 9714= 227628

(e) 132= 10 000 1002 (f) 23851= 5D2B16

(g) 727= 104025

(h) 57190=DF6616 (i) 1435=26338

数字设计原理与实践第四版课后习题答案

数字设计原理与实践 (第四版 )_课后习题答案数字设计原理与实践 (第四版) 是一本广泛使用于电子工程、计算机科学等领域的教材,它介绍了数字电路的基础知识和设计方法。

课后习题是巩固学习内容、提高理解能力的重要部分。

下面是一些课后习题的答案,供参考。

第一章绪论1. 什么是数字电路?数字电路是一种使用二进制数表示信息并通过逻辑门实现逻辑功能的电路。

2. 简述数字系统的设计过程。

数字系统的设计过程包括需求分析、系统规格说明、逻辑设计、电路设计、测试和验证等步骤。

3. 简述数字电路的分类。

数字电路可以分为组合逻辑电路和时序逻辑电路两类。

组合逻辑电路的输出只取决于当前输入,时序逻辑电路的输出还受到过去输入的影响。

4. 什么是门电路?门电路是由逻辑门组成的电路,逻辑门是实现逻辑运算的基本模块。

第二章组合逻辑电路设计基础1. 简述一下布尔代数的基本概念。

布尔代数是一种用于描述逻辑运算的数学系统。

它包括逻辑变量、逻辑表达式、逻辑运算等概念。

2. 简述编码器和译码器的功能和应用。

编码器用于将多个输入信号转换为较少的输出信号,译码器则将少量输入信号转换为多个输出信号。

它们常用于数据压缩、信号传输和地址译码等应用中。

3. 简述多路选择器的功能和应用。

多路选择器根据选择信号选择其中一个输入信号并输出,它可以实现多个输入信号的复用和选择。

它常用于数据选择、信号传输和地址译码等应用中。

第三章组合逻辑电路设计1. 简述组合逻辑电路的设计方法。

组合逻辑电路的设计方法包括确定逻辑功能、编写逻辑表达式、绘制逻辑图和验证电路正确性等步骤。

2. 请设计一个3位二进制加法器。

一个3位二进制加法器可以通过将两个2位二进制加法器和一个与门连接而成。

3. 简述半加器和全加器的功能和应用。

半加器用于实现两个二进制位的相加,它的输出包括和位和进位位。

全加器则用于实现三个二进制位的相加,它的输出包括和位和进位位。

它们常用于二进制加法器的设计。

第四章时序逻辑电路设计基础1. 简述触发器的功能和应用。

数字设计原理与实践第四版中文答案

42.E1F=2100 100.011 110 001 111=811.6347 )e(

61

1DABA=2100 010 110 101 110 101 01=81235352 )d(

61

F 4 B E 1 = 2 1 1 1 1 0 0 1 0 1 1 0 1 0 1 1 1 1 = 87 1 5 5 6 3 ) c (

14 66 =9843 ) b(

2

10 1 111 1 =52 1 )a (

。 换 转 制 数的 面 下 成 完 6 . 2

57812.843=6183.C51 )j( 4 9 6 3 = 86 5 1 7 ) i ( 7 3 8 3 4 = 6 1D 3 B A ) h ( 831=301021 )g( 37326 = 615 A 3 F ) f ( 5 2 1 8 . 0 2 =2 1 0 1 1 . 0 0 1 0 1 ) e ( 1 9 4 3 6 = 83 0 0 4 7 1 ) b ( 5213.55=842.76 )d(

') D ⋅ C ⋅ ) B + A (( = Z �解

。 图 辑 逻 的应 对 出 画 V N I , R O � D N A 用 采 � 图 路 电 I A O 的 示 所 � b � 1 1 . 3 X 图对 2 1 . 3

。限容声噪 CD 的态低与态高定确�性特器相反的示所 12.3X 图 对 � V 5 . 3 和 V 5 . 1 为 置 设 别 分值 阈 平 电 高 和 值 阈 平 电 低 出 输 若 1 2 . 3

3 8 1 = 21 1 1 0 1 1 0 1 ) c (

701=21101011 )a(

。 数 制 进 十 成 换 转 数 的 面 下 将 5. 2

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.11 对图X3.11(a)所示的AOI 电路图,采用AND,OR,INV 画出对应的逻辑图。

解:Z = (A⋅B + C + D)'3.12 对图X3.11(b)所示的OAI 电路图,采用AND,OR,INV 画出对应的逻辑图。

解:Z = ((A + B)⋅C ⋅D)'13 画出NOR3 对应的电路图。

解:3 输入端或非门结构应为:上部3 个P 管串联,下部3 个N 管并联,结构如图所示。

3.15 画出OR2 所对应的电路图。

解:在NOR2 电路的输出端后面级联一个INV。

3.59 画出图X3.59 逻辑图所对应的电路图。

解:3.21 若输出低电平阈值和高电平阈值分别设置为1.5V 和3.5V,对图X3.21 所示的反相器特性,确定高态与低态的DC 噪声容限。

解:由图中可以看到,输出3.5V 对应的输入为2.4V,输出1.5V 对应的输入为2.5V;所以,高态噪声容限为:3.5-2.5=1 V ;低态噪声容限为:2.4-1.5=0.9 V。

3.26 利用表3-3 计算74HC00 的p 通道和n 通道的导通电阻。

解:采用极端值计算(对商用芯片,最低电源电压设为4.75V)表中所列输出电压与电流关系如图所示:根据电流定律,高态输出时可以建立下列方程:p n R R0.35 0.02 = 4.4 ⎟⎟⎠⎞⎜⎜⎝⎛−p n R R0.91 4 = 3.84 ⎟⎟⎠⎞⎜⎜⎝⎛−联立求解可得:R = 0.151kΩ = 151Ωp低态输出时可以建立下列方程:n p R R0.1 0.02 = 4.65 ⎟⎟⎠⎞⎜⎜⎝⎛−n p R R0.33 4 = 4.42 ⎟⎟⎠⎞⎜⎜⎝⎛−联立求解可得:R = 0.060kΩ = 60Ωn3.27 对于表3-3 所列的74HC00 ,若设V OLmax=0.33V,V OHmin=3.84V,Vcc=5V,对于下列电阻负载,确定该系列的商用器件是否能够驱动(任何情况下输出电流不能超出I OLmax 和I OHmax).解:根据表3-3,对于选定的输出电压,最大输出电流限制为4mA.c)820Ω接地:考虑高态输出,等效电路如下:I=3.84/0.82=4.683 > 4mA 不能驱动。

e) 1kΩ接Vcc:考虑低态输出,等效电路如下:I=(5-0.33)/1=4.67 > 4mA 不能驱动。

f) 1.2kΩ接Vcc, 820Ω接地:需要分别考虑低态输出和高态输出。

低态输出等效电路如下:I=(2.03-0.33)/0.487 = 3.49 < 4mA 可以驱动。

高态输出等效电路如下:I=(3.84-2.03)/0.487 = 3.72 < 4mA 可以驱动。

3.40 一个发光二极管导通时的电压降约为2.0V,正常发光时需要约5mA 的电流。

当发光二极管如图3-54(a)那样连接时,确定上拉电阻的适当值。

解:根据3.7.5 所给的条件,低态输出电平V OLmax=0.37V。

对应等效电路如下:R=(5-2-0.37)/5=0.526kΩ3.65 在图3-32(b)中,有多少电流与功率被浪费了。

解:浪费的电流为流过4kΩ电阻的电流:I=(5-0.24)/4=1.19 mA浪费的功率为上述电流经过两个电阻产生的功率:P = RI2 = 4.2 x (1.19)2 = 5.95 mW3.33 对于下列电阻电容的组合,确定时间常数RC解:a) 5ns b)705ns c)2.21ns d)100ns3.34 对于一个CMOS 电路,将电源电压增加5%,或者将内部电容和负载电容增加5%,哪种方式会导致更大的功率消耗。

答:CMOS 的电源消耗主要是动态消耗,其关系为P CV f D= 2 ;由该关系可以得出电源增加将导致更大的功率消耗。

3.68 分析图3-37 所示反相器的下降时间,设R L=900Ω,V L=2V。

解:该电路图可以等效为下列带开关的一阶电路图。

当输出从高态转为低态时,可以等效为开关K 从位置1 转到位置2。

按照一阶电路三要素法的分析方法,对于电容上的电压分析如下:初态:V H=4.45V 终态:V L=0.2V换路后的等效电阻:R=90Ω电路时间常数:τ= RC = 9ns输出电压随时间变化关系为:( ) t /τOUT L H L V = V + V −V e−由上式可以得出从3.5V 到1.5V 的下降时间为:nsVt VLL 9.11.5ln 3.5 ≈−−Δ =τ3.69 分析图3-37 所示反相器的上升时间,设R L=900Ω,V L=2V。

解:与上题类似进行分析,当输出从低态转为高态时,可以等效为开关K 从位置12 到位置1。

按照一阶电路三要素法的分析方法,对于电容上的电压分析如下:初态:V L=0.2V 终态:V H=4.45V换路后的等效电阻:R=164Ω电路时间常数:τ= RC = 16.4ns输出电压随时间变化关系为:( )(1 t /τ)OUT L H L V = V + V −V −e−由上式可以得出从1.5V 到3.5V 的上升时间为:nsVt VHH 193.5ln 1.5 ≈−−Δ =τ数字逻辑第四章参考解答:4-5 根据Demorgan 定理,X + Y ⋅Z 的补为X '⋅Y'+Z'。

但这两个函数在XYZ=110 时都等于1。

对于一个给定的输入组合,一个函数和其补函数怎么能都等于1 呢?出了什么错误?答:在利用定理时,没有考虑到运算先后顺序,正确的补函数应该为:(X +Y ⋅Z)'= X '⋅(Y ⋅Z)'= X '(Y'+Z') = X '⋅Y'+X '⋅Z'4.7 请写出下面各个逻辑函数的真值表.a) F = X '⋅Y + X '⋅Y '⋅Z可先简化为:F = X '⋅(Y + Y'Z ) = X '(Y + Z )c) F=W+X’·(Y’+Z)=W+X’·Y’+X’·ZW X Y Z F W X Y Z F0 0 0 0 1 1 0 0 0 10 0 0 1 1 1 0 0 1 10 0 1 0 0 1 0 1 0 10 0 1 1 1 1 0 1 1 10 1 0 0 0 1 1 0 0 10 1 0 1 0 1 1 0 1 10 1 1 0 0 1 1 1 0 10 1 1 1 0 1 1 1 1 1h) F=(((A+B)’+C’)’+D)’=A’·B’·D’+C’·D’A B C D F A B C D F0 0 0 0 1 1 0 0 0 10 0 0 1 0 1 0 0 1 00 0 1 0 1 1 0 1 0 00 0 1 1 0 1 0 1 1 00 1 0 0 1 1 1 0 0 10 1 0 1 0 1 1 0 1 00 1 1 0 0 1 1 1 0 00 1 1 1 0 1 1 1 1 04.25 证明OR(n)可以采用(n-1)个OR(2)实现;NOR 也能这样吗?证明你的结论。

解:根据逻辑定理:(x1+ x2 + x3+ x4 + x5 + ...) = ((((x1+ x2)+ x3)+ x4)+ x5)+ ... 第1 次运算实现2 个变量的OR,第2 次运算实现3 个变量的OR,第(n-1)次运算就可以实现n 个变量的OR。

NOR 不能这样做:以3 个变量为例:利用DeMorgan’s 定理((x1+ x2)'+x3)'= (x1'⋅x2'+x3)'≠(x1+ x2 + x3)'所以不能采用这种方式替换。

4.36 对于XNOR,写出真值表,积之和表达式以及对应的与或结构逻辑图。

解:真值表逻辑式:F = A⋅B + A'⋅B' 逻辑图:4.38 采用题设条件如何得到反相器(题略)。

答:只能利用XNOR 实现,在逻辑表达式F = A⋅B + A'⋅B'中,令B或A 等于0(将该输入端接地),即可实现反相器功能。

4.9 请写出下面各个逻辑函数的标准和与标准积.a) =Σ( ) =Π( )X Y X Y F , , 1,2 0,3标准和:F = X ⋅Y'+X '⋅Y标准积:F = (X +Y )⋅(X '+Y')b) =Π( ) =Σ( )A B A B F , , 0,1,2 3标准和:F = A⋅B标准积:F = (A+ B)⋅(A+ B')⋅(A'+B)c) =Σ( ) =Π( )A B C A B C F , , , , 1,2,4,6 0,3,5,7标准和:F = A'⋅B'⋅C + A'⋅B⋅C'+A⋅B'⋅C'+A⋅B⋅C'标准积:F = (A+ B +C)⋅(A+ B'+C')⋅(A'+B +C')⋅(A'+B'+C')d) =Π( ) =Σ( )W X Y W X Y F , , , , 0,2,3,6,7 1,4,5标准和:F =W'⋅X'⋅Y +W ⋅X'⋅Y'+W ⋅X'⋅Y标准积:F = (W + X +Y )⋅(W + X '+Y )⋅(W + X'+Y')⋅(W'+X'+Y )⋅(W'+X '+Y') e) = + ⋅ =Σ( ) =Π( )X Y Z X Y Z F X Y Z , , , , ' 0,1,2,3,7 4,5,6标准和:F = X'⋅Y'⋅Z'+X '⋅Y'⋅Z + X'⋅Y ⋅Z'+X'⋅Y ⋅Z + X ⋅Y ⋅Z标准积:F = (X '+Y + Z)⋅(X '+Y + Z')⋅(X'+Y'+Z)f) = + ( ⋅) = + + =Π( ) =Σ( ) V W X V W X F V W X V W X , , , , ' ' ' 20,1,3,4,5,6,7标准和:F =V'⋅W'⋅X '+V'⋅W'⋅X +V'⋅W ⋅X +V ⋅W'⋅X '+V ⋅W'⋅X +V ⋅W ⋅X '+V ⋅W ⋅X标准积:F =V +W'+X4.11 若“1”不是质数,重新写出4 位质数检测器的最小项列表,规范和以及对应的逻辑图。