CameraLink接口数字相机图像显示装置解读

CameraLink接口数字相机图像显示装置解读ppt课件

“雪亮工程"是以区(县)、乡(镇) 、村( 社区) 三级综 治中心 为指挥 平台、 以综治 信息化 为支撑 、以网 格化管 理为基 础、以 公共安 全视频 监控联 网应用 为重点 的“群 众性治 安防控 工程” 。

VGA接口的结构

VGA接口是一种D型接口, 上面共有15针空,分成 三排,每排五个。 其中,

乒乓缓存介绍

当SDRAM1中缓存满了一帧图像数据后,开 始读取数据,读SDRAM1时写SDRAM2。当 SDRAM2中写满一帧图像数据后,控制器对 两个SDRAM进行读写切换,读SDRAM2时 写SDRAM1。

“雪亮工程"是以区(县)、乡(镇) 、村( 社区) 三级综 治中心 为指挥 平台、 以综治 信息化 为支撑 、以网 格化管 理为基 础、以 公共安 全视频 监控联 网应用 为重点 的“群 众性治 安防控 工程” 。

CameraLink接口技术的特点 CameraLink接口的结构 CameraLink接口的原理

缓存部分介绍

SDRAM介绍 乒乓缓存简介

算法方案介绍

算法概述 算法方案

VGA接口介绍

VGA的技术特点 VGA接口的结构

结论

“雪亮工程"是以区(县)、乡(镇) 、村( 社区) 三级综 治中心 为指挥 平台、 以综治 信息化 为支撑 、以网 格化管 理为基 础、以 公共安 全视频 监控联 网应用 为重点 的“群 众性治 安防控 工程” 。

“雪亮工程"是以区(县)、乡(镇) 、村( 社区) 三级综 治中心 为指挥 平台、 以综治 信息化 为支撑 、以网 格化管 理为基 础、以 公共安 全视频 监控联 网应用 为重点 的“群 众性治 安防控 工程” 。

谢谢! 请提宝贵意见。

CameraLink协议和FPGA的数字图像信号源设计

CameraLink协议和FPGA的数字图像信号源设计关键字: FPGA Camera Link 标准 CMOS1 引言目前,各种图像设备已广泛应用到航空航天、军事、医疗等领域。

图像信号源作为地面图像采集装置测试系统中的一部分,其传输方式及信号精度都是影响系统性能的重要因素。

由于图像信号的传输速率高,数据量大,在传输过程中,其精度和传输距离易受影响。

为了提高信号传输距离和精度设计了由FPGA内部发出图像数据,并通过FPGA进行整体时序控制;输出接口信号转换成符合Camera Link标准的低电压差分信号(LVDS)进行传输。

该图像信号源已成功应用于某弹载记录器的地面测试台系统中。

2 Camera Link接口及图像数据接口信号Camera Link标准是由国家半导体实验室(National Semiconductor)提出的一种Channel Link技术标准发展而来的,该接口具有开放式的接口协议,使得不同厂家既能保持产品的差异性,又能互相兼容。

它在传统LVDS传输数据的基础上又加载了并转串发送器和串转并接收器,可在并行组合的单向链路、串行链路和点对点链路上,利用SER,DES(串行化,解串行化)技术以高达4.8 Gb,s的速度发送数据。

CameraLink标准使用每条链路需两根导线的LVDS传输技术。

驱动器接收28个单端数据信号和1个时钟信号,这些信号以7:1的比例被串行发送,也就是5对LVDS信号通道上分别传输4组LVDS数据流和1组LVDS时钟信号,即完成28位数据的同步传输只需5对线,而且在多通道66 MHz像素时钟频率下传输距离可达6 m。

Camera Link是在Channel Link的基础上增加了一些相机控制信号和串行通信信号,定义出标准的接头也就是标准化信号线,让Camera及影像卡的信号传输更简单化,同时提供基本架构(Base Configuration)、中阶架构(Medium Configuration)及完整架构(Full Configuration)三种:基本架构属单一Camera Link元件,为单一接头;中阶架构属双组Camera Link元件,为双组接头;完整架构属三组Camera Link元件,为三组接头。

cameralink布线规则

cameralink布线规则

CameraLink接口是目前工业数字相机的主要图像输出接口之一,该种接口具有实时性好、抗干扰的优点,可满足大部分相机的数据流量要求。

其布线时,通常需要注意以下几点:- 信号走线应该尽可能短,以减少信号延迟和信号衰减。

- 信号差分对应的两条走线应该保持长度相等,以避免信号失配。

- 信号走线应该避免与电源线和地线交叉,以避免噪声干扰。

- PCB的布局应该尽可能紧凑,以减少信号传输的路径和干扰。

- 在信号传输的起始和终止点应该加上合适的阻抗匹配电路,以保证信号的完整性和稳定性。

如果有高速信号需要传输,可以考虑使用阻抗控制的微带线或同轴线,以减少信号的反射和失真。

具体的布线规则还需要根据具体的Cameralink标准和应用场景来确定。

3-CameraLink接口-时序控制

CameraLink接口

1.CameraLink接口简介

1.1CameraLink标准概述

CameraLink技术标准是基于NationalSemiconductor公司的ChannelLink标准发展而来的,而ChannelLink标准是一种多路并行LVDS传输接口标准。

低压差分信号(LVDS)是一种低摆幅的差分信号技术,电压摆幅在350mV左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在1.923Gbps。

90年代美国国家半导体公司(NationalSemiconductor)为了找到平板显示技术的解决方案,开发了基于LVDS物理层平台的

如图

位

5路LVDS

恢复成

A、B 和C

口G和芯

E和H,

那么

H的8

从

中读取处FPGA DDR 包括2RAM 另外,

子模块来完成位宽的转换。

2.4modelsim仿真结果

图2.4modelsim仿真结果

如图2.4,被测FPGA每来一个行同步,CameraLink模块获取行地址后读取DDR2中的数据写入缓存模块,等到下一个行同步来的时候把所读的数据从缓存模块中输出。

实际要求的是每个行同步来后要读取一行数据,大小为2048x12bit,为了缩小仿真时间,仿真时没一行的数据长度为:80x12bit。

图2.5五路CameraLink仿真输出

如图2.5,当下个行同步来的时候缓存数据输出,输出的数据时连续的。

cameralink 双路full 用法 -回复

cameralink 双路full 用法-回复CameraLink是一种数字相机接口标准,用于高速数据传输。

相比于常见的USB和FireWire接口,CameraLink可以提供更高的数据传输速度和更稳定的性能。

在CameraLink标准中,双路full是一种信号配置模式,可以实现更高的带宽和灵活性。

本文将详细介绍CameraLink双路full的用法。

首先,我们需要了解CameraLink的基本原理和组成部分。

CameraLink 主要包括三个组件:CameraLink相机、CameraLink框架抓取卡和连接线缆。

CameraLink标准定义了相机和框架之间的电子、机械和协议接口。

这样,我们可以将不同厂家生产的CameraLink相机与任何符合标准的框架卡连接起来,实现高速图像数据传输。

在传统的CameraLink连接方式中,常用的信号配置是单路base或medium。

单路base配置可以提供最低的带宽,适合于相对简单的图像应用。

单路medium提供了更高的带宽,适合需要更高图像质量或更复杂的应用。

然而,随着计算机视觉和工业自动化领域的发展,对图像数据传输速度的需求不断增加。

这就引出了CameraLink双路full的概念。

双路full配置是CameraLink标准中的一种高级配置模式。

它使用了两个CameraLink连接通道,从而实现了双倍的传输带宽。

具体来说,双路full 配置可以实现每秒传输达到8.2GB的数据速率,这是单路base配置的四倍。

通过这样的配置,用户可以实现更高的图像帧率或更大的图像分辨率,从而满足更复杂应用的需求。

接下来我们将一步一步介绍CameraLink双路full配置的使用方法。

步骤一:选择双路full兼容的硬件设备。

要使用双路full配置,我们首先需要确保所选购的CameraLink相机和框架抓取卡都支持双路full模式。

通常,在产品说明或技术规格中可以找到相关信息。

CameraLink图像采集接口电路1(2)详解

CameraLink 图像采集接口电路1.Camera Link标准概述Camera Link 技术标准是基于 National Semiconductor 公司的 Channel Link 标准发展而来的,而 Channel Link 标准是一种多路并行 LVDS 传输接口标准。

低压差分信号( LVDS )是一种低摆幅的差分信号技术,电压摆幅在 350mV 左右,具有扰动小,跳变速率快的特点,在无失传输介质里的理论最大传输速率在 1.923Gbps 。

90 年代美国国家半导体公司( National Semiconductor )为了找到平板显示技术的解决方案,开发了基于 LVDS 物理层平台的 Channel Link 技术。

此技术一诞生就被进行了扩展,用来作为新的通用视频数据传输技术使用。

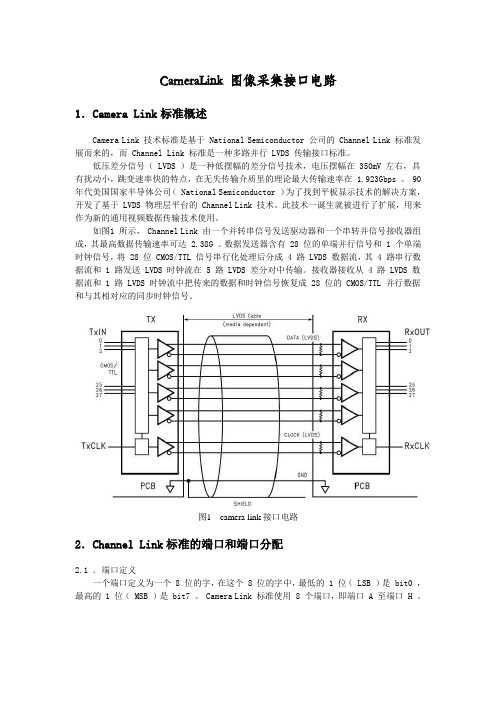

如图1 所示, Channel Link 由一个并转串信号发送驱动器和一个串转并信号接收器组成,其最高数据传输速率可达 2.38G 。

数据发送器含有 28 位的单端并行信号和 1 个单端时钟信号,将 28 位 CMOS/TTL 信号串行化处理后分成 4 路 LVDS 数据流,其 4 路串行数据流和 1 路发送 LVDS 时钟流在 5 路 LVDS 差分对中传输。

接收器接收从 4 路 LVDS 数据流和 1 路 LVDS 时钟流中把传来的数据和时钟信号恢复成 28 位的 CMOS/TTL 并行数据和与其相对应的同步时钟信号。

图1 camera link接口电路2.Channel Link标准的端口和端口分配2.1 .端口定义一个端口定义为一个 8 位的字,在这个 8 位的字中,最低的 1 位( LSB )是 bit0 ,最高的 1 位( MSB )是 bit7 。

Camera Link 标准使用 8 个端口,即端口 A 至端口 H 。

2.2 .端口分配在基本配置模式中,端口 A 、 B 和 C 被分配到唯一的 Camera Link 驱动器 / 接收器对上;在中级配置模式中,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上;在完整配置模式中,端口 A 、 B 和 C 被分配到第一个驱动器 / 接收器对上,端口 D 、 E 和 F 被分配到第二个驱动器 / 接收器对上,端口 G 和 H 被分配到第三个驱动器 / 接收器对上(见图2 )。

标准cameralink接口

标准cameralink接口Cameralink是一种数字接口标准,用于连接工业相机和数字信号处理器。

它提供了一种高速、可靠的方式来传输图像数据,适用于工业自动化、机器视觉和医疗成像等领域。

本文将介绍标准cameralink接口的基本原理、特点和应用。

1. 基本原理。

标准cameralink接口基于同步传输技术,采用了基于像素的并行数据传输方式。

它使用了三种不同的信号线,基础相机线、中继相机线和扩展相机线。

基础相机线用于传输图像数据、触发信号和相机控制信号,中继相机线用于传输额外的图像数据,扩展相机线用于传输高速图像数据。

通过这些信号线的组合,cameralink接口可以实现高速、稳定的图像数据传输。

2. 特点。

标准cameralink接口具有以下特点:高速传输,cameralink接口支持高达850MB/s的数据传输速率,能够满足工业相机对于高速图像采集的需求。

灵活性,cameralink接口可以支持不同分辨率、不同帧率的图像传输,适用于各种不同的应用场景。

可靠性,cameralink接口采用了差分信号传输技术,具有抗干扰能力强、传输稳定可靠的特点。

易于集成,cameralink接口标准化,各种厂家生产的工业相机和数字信号处理器都可以实现互操作性,方便用户进行系统集成。

3. 应用。

标准cameralink接口广泛应用于工业自动化、机器视觉和医疗成像等领域。

在工业自动化领域,cameralink接口可以实现高速、精准的图像采集和处理,用于产品质量检测、物体识别和测量等应用。

在机器视觉领域,cameralink接口可以实现高分辨率、高帧率的图像传输,用于无人驾驶、智能监控等应用。

在医疗成像领域,cameralink接口可以实现高清晰度、高对比度的图像传输,用于医学诊断、手术导航等应用。

总结。

标准cameralink接口是一种高速、可靠的数字接口标准,适用于工业相机和数字信号处理器之间的图像数据传输。

Cameralink简介

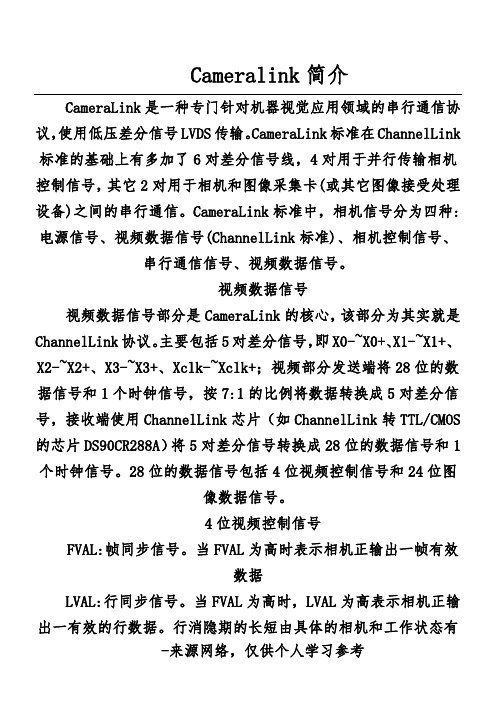

Cameralink简介CameraLink是一种专门针对机器视觉应用领域的串行通信协议,使用低压差分信号LVDS传输。

CameraLink标准在ChannelLink 标准的基础上有多加了6对差分信号线,4对用于并行传输相机设备:、1位图4位视频控制信号FVAL:帧同步信号。

当FVAL为高时表示相机正输出一帧有效数据LVAL:行同步信号。

当FVAL为高时,LVAL为高表示相机正输出一有效的行数据。

行消隐期的长短由具体的相机和工作状态有关。

DVAL:数据有效信号。

当FVAL为高并且LVAL为高时,DVAL 为高表示相机正输出有效的数据,该信号可用可不用,也可以作为数据传输中的校验位。

CLOCK:这一信号为图像的像素时钟信号,在行有效期内像素信号串行通信信号CameraLink标准定义了2对LVDS线缆用来实现相机与图像采集卡之间的异步串行通信控制。

相机和图像采集卡至少应该支持9600的波特率。

这两个串行信号是相机:SerTFG(相机串行输出端至图像采集卡串行输入端)SerTC(图像采集卡串行输出端至相机串行输入端) 其通信格式为:1位起始位、8位数据位、1位停止位、无奇偶校验位和握手位。

相机电源并不是由CameraLink连接器提供的,而是通过一个个4bits:;行有信号(DVAL),只有在数据有效信号为高电平时,图像采集卡才接受图像信息。

24bits图像数据可以是一个像素点的24-bitRGB数据、3个像素点的8-bit黑白图像数据、1到2个像素点的10-bit 或12-bit的黑白图像数据、一个像素点的14-bit或16-bit的黑白图像数据。

Medium模式需要两块Channe1Link的芯片和两个CameraLink 机械接口,发送器在每个像素时钟里发送4Obits数据,包括4bits 的图像使能信号和36bits的图像数据。

4bits图像使能信号与Base模式下相同。

36bits图像数据可以是一个像素点的36-bit 或到4个4bitsA口(8位))、)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Camera Link接口数字相机图像显示装置(技术)摘要:由于目前基于CameraLink接口的各种相机都不能直接显示,因此本文基于Xilinx公司的Spartan3系列FPGA XC3S1000-6FG456I设计了一套实时显示系统,该系统可以在不通过系统机的情况下,完成对相机CameraLink信号的接收、缓存、读取并显示。

系统采用两片SDRAM作为帧缓存,将输入的CameraLink信号转换成帧频为75Hz,分辨率为1,024×768的XGA格式信号,并采用ADV7123JST芯片实现数模转换,将芯片输出的信号送到VGA接口,通过VGA显示器显示出来。

设计的系统可以应用于各种基于CameraLink接口的相机输出信号的实时显示。

关键词:CameraLink; FPGA; SDRAM控制器;实时显示Research on the Real-time Display Technology Based on CameraLinkAbstract: All cameras based on the CameraLink interface cannot be displayed directly at present. Therefore, we designed a real-time display system based on the Xilinx Spartan3 FPGA XC3S1000-6FG456I.Our system could receive, store, read and display the CameraLink signal without the system computer. Two SDRAMs were used as frame storage. Input CameraLink signal was converted to XGA signal with 1024×768 pixles/frame at 75 frame/s. The ADV7123JST was used as D/A convertor. Its output signal was transmitted to the VGA interface and displayed on the screen of the VGA monitor. Our system could display the output signal of all cameras based on the CameraLink interface.Keywords: CameraLink; FPGA; SDRAM controller; real-time display目录第一章绪论 (3)1.1 引言 (3)1.2数字图像处理的发展 (3)1.3 目的及意义 (4)1.4 国内外研究现状 (5)第2章视频显示原理和显示格式的转换算法综述 (7)2.1视频显示的原理 (7)2.2目前视频显示格式转换算法综述 (8)2.2.1图像尺寸变换的插值方法综述 (9)2.2.2每秒帧数变换方法综述 (11)2.2.3插值算法选择判断的原则 (11)第三章视频显示格式转换的插值算法方案 (12)3.1图像尺寸变换采用的算法方案 (12)3.2每秒帧数变换采用的算法方案 (14)3.3视频显示格式转换中的像素处理方案 (16)第四章实时显示系统装置 (17)4.1.实时显示系统总体设计 (18)4.2 FPGA概述 (18)4.3 Camera Link结构与原理 (20)4.4 SDRAM控制器设计 (22)4.5 VGA显示接口设计 (24)参考文献 (25)第一章绪论1.1 引言Cameralink相机以其可靠性高,稳定性好,独立性好和易用等优势,成为现阶段工业大分辨率数字相机的必配接口,相机LVDS信号由专业图像采集卡解码通过一台性能良好的计算机计算最后在计算机显示器上完成图像显示或在计算机硬盘上存储等后续数字图像处理操作。

对于某些不需要复杂图像运算的场合,只要求将验证相机的显示效果如何,如此配置略显臃肿,所以提出基于Cameralink数字信号的便携显示思想。

针对上述不足,本文设计一个可以针对LVDS图像信号的实时显示装置。

该装置可以将接入的相机数字信号解码成普通CRT显示器可以支持的VGA视频格式,使用数模转换器将视频转换成模拟信号输出显示。

本设计使用FPGA做控制器和运算器,SDRAM做图像存储器,ADV7123做数模转换器,搭建实时图像显示平台,接收Cameralink相机的数字视频信号,完成解码、制式变换等数字图像处理最终得以在外部显示器中显示。

数字图像处理部分内容涉及到图像尺寸分辨率变换和帧率变换等基于图像输出的基础数字图像处理内容。

1.2数字图像处理的发展数字视频转换属数字图像处理领域,数字图像处理最早的应用之一是报纸业,当时,图像第一次通过海底电缆从伦敦传往纽约。

早在20世纪20年代曾引入Bartlane电缆图片传输系统,把横跨大西洋传送一幅图片所需的时间从一个多星期减少到3个小时。

后随着计算机技术的进步,大规模存储和显示系统的跟进发展,使数字图像处理技术应用到更多的领域中。

20世纪60年代早期,人类制造出第一台可以执行有意义的图像处理任务的大型计算机。

空间项目的开发也使人们把注意力转移到数字图像处理技术的潜能上。

1964年美国加利福尼亚的喷气推进实验室,就利用计算机技术改善空间探测器发回的月球图像,以校正航天器上摄像机中各种类型的图像失真。

在20世纪60年代末和70年代初,数字图像处理技术开始应用于医学图像、地球遥感检测和天文学领域。

在医学领域上,Godfrey N.Hounsfield先生和Allan M.Cormack教授基于数字图像处理技术发明了断层技术,由此而共同获得了1979年的诺贝尔医学奖。

从20世纪60年代至今,图像处理领域已得到了生机勃勃的发展。

除了医学和空间项目的应用外,数字图像处理技术现在已应用在了更广泛的范围。

计算机程序用于增强对比度或将亮度编码为彩色,以便于解释X射线和用于工业、医学及生物科学等领域的其他图像。

地理学用相同或相似的技术从航空和卫星图像中研究污染模式。

图像增强和复原过程用于处理不可修复物体的已损图像或者造价昂贵不可复制的实验结果。

在考古学领域,使用图像处理方法已成功地复原模糊的图片,这些图片是丢失或损坏的稀有物品唯一现存的记录。

在物理学和相关领域,计算机技术通常增强如高能等离子和电子显微镜方法等领域的实验图像。

图像处理技术也成功的应用在天文学、生物学、核医学、法律实施、国防以及工业领域中。

作为图像处理技术的实现载体,处理系统的器件性能的不断提升,来满足各种复杂图像处理的应用需要。

20世纪80年代中期,图像处理系统都是由主机及与主机箱配合的外设构成。

20世纪80年代末90年代初,出现将图像处理硬件设计与工业标准总线兼容并能配合工程工作站机箱和个人计算机的单板形式。

到目前为止,虽然针对大规模图像应用的大规模图像处理系统一直在不断销售,但随着技术进步,向着小型化和通用化的小机型并带有专用图像处理软件的混合型系统方向发展。

1.3 目的及意义目前,基于CameraLink接口的各种相机都不能直接显示,只能通过专用采集卡连接到系统机上在系统机的屏幕上显示,系统比较庞大,使用不方便。

针对上述不足,本文设计一个可以针对LVDS图像信号的实时显示装置。

该装置可以将接入的相机数字信号解码成普通CRT显示器可以支持的VGA视频格式,使用数模转换器将视频转换成模拟信号输出显示。

相比现有设备而言,成本降低,系统精简,便于携带。

1.4 国内外研究现状图像处理是计算机应用领域中一个极为活跃的领域,它的发展己有40余年的历史,在此期间,随着计算机、集成电路等技术的飞速发展,图像处理无论在算法上、系统结构上,还是在应用上以及普及的程度上都取得了长足的进展。

但是图像处理依然面临着许多挑战性的问题,其中最主要的问题就是如何提高解决实际复杂问题的综合能力,就当前的技术水平来说,这种综合能力包括图像处理的网络化、复杂问题的求解与图像处理速度的高速化。

图像处理的速度问题主要由图像数据的特点、图像处理算法的复杂性以及处理系统硬件结构和速度引起。

为提高图像处理系统速度,一方面可以改变图像数据特点,但这种方法通常是不可取的,因为处理系统往往需要充分利用图像数据中的信息;其次是选用高速处理器件,并尽量减化图像处理算法;再者可以采用并行处理技术,这种技术选用多个高速处理器件来完成同一任务,使得处理速度得到成倍提高。

图像并行处理技术是图像处理中的一个重要方面,是提高图像处理速度的最有效技术,其发展水平一直受到图像界的关注。

原因在于:一方面,图像并行处理技术的发展难度很大,这种难度不仅在于图像处理系统的硬件及系统结构本身,以及它对计算机技术和集成电路等技术的依赖关系,而且在于实际应用的复杂性和应用部门对系统价格的承受能力;另一方面,图像并行处理技术的发展所产生的效益也是十分显著的,它在处理速度上所获得的加速比是令人振奋的,其实际应用系统也将产生很大的经济效益和社会效益。

虽然许多实际的应用问题刺激着图像并行处理技术的发展,但实际应用的复杂性和图像并行处理系统昂贵的价格又制约着图像并行处理技术的实际应用,这是一对矛盾,也是一种挑战。

图1-1一种基于双TMS320C40的图像并行处理系统此前,国内外一些科研院所已研制出了一些图像并行处理系统,如天津大学研制的双TMS320C40的高速图像处理系统。

该系统的结实时图像处理构如图1-1所示:处理系统采用两个帧存储器,它们轮流对视频信号进行存储,其中每个帧存储器又分为前半帧和后半帧。

当前半帧结束时,处于空闲状态的TMS320C40开始对前半帧图像数据进行处理,并将处理结果送入数据存储器。

当它的工作完成后,它又处于等待状态,等待下一帧的前半帧图像数据的来临。

当后半帧结束时,另一片TMS320C40开始对后半帧图像数据进行处理,并将处理结果送入数据存储器。

它的工作完成后,就等待下一帧的后半帧图像数据的来临。

从整个系统设计来看,它是采用多片处理器分担相同任务的方法来达到提高系统处理速度的目的。

此外,加拿大Matrox公司采用TMS320C80芯片设计的GENESIS图像处理系统、英国INMOS公司设计的IMS A100级联信号处理器和清华大学研制的GIEB微机高速图像处理系统都是图像并行处理结构的典范。

但这些系统规模庞制。

大,价格昂贵,使得在一些领域的应用受到限[1]第2章视频显示原理和显示格式的转换算法综述2.1视频显示的原理在最理想的情况下,电视机上重现图像应该和原景物一样。