自动售票机电路设计报告

自动售票机、累加器电路图

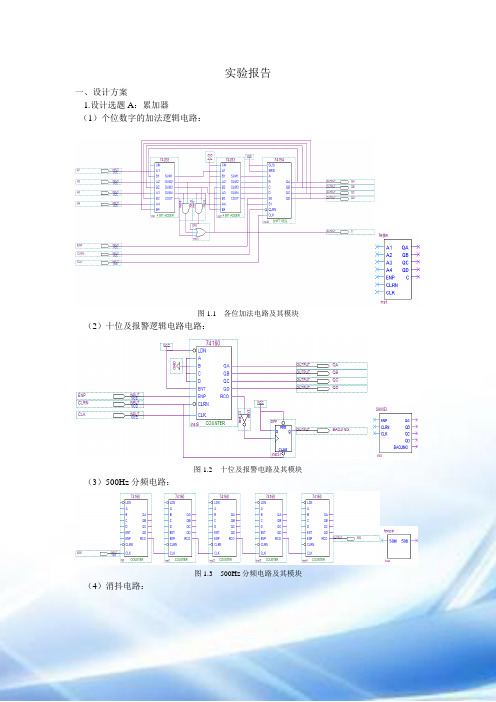

实验报告一、设计方案1.设计选题A:累加器(1)个位数字的加法逻辑电路:图1.1 各位加法电路及其模块(2)十位及报警逻辑电路电路:图1.2 十位及报警电路及其模块(3)500Hz分频电路:图1.3 500Hz分频电路及其模块(4)消抖电路:图1.4 消抖电路及其模块(5) 数码管显示电路:图1.5 数码管显示电路及其模块(6) 累加器逻辑电路总图、下载电路及管脚分配电路:图1.6 累加器电路总图2.设计选题C:自动售票机(1)500Hz分频电路及其模块如图1.3所示。

(2)消抖电路及其模块如图1.4所示。

(3)钱币的输入及邮票的设置电路:图2.1 数据输入电路及其模块(4)数据比较电路:图2.2 数据比较电路及其模块(5)减法找零电路:图2.3 减法找零电路及其模块(6)累加器电路:图2.4 累加器电路及其模块其中,累加器电路中用到的“leijia”模块和“SHIWEI”模块均来自于设计选题A:累加器。

(7)3s计数器电路:图2.5 3s计数器电路及其模块(8)数码管显示电路:图2.6 数码管显示电路及其模块(9)彩灯显示电路:图2.7 彩灯显示电路及其模块(10)自动售票机逻辑电路总图、下载电路及管脚分配电路图2.7 自动售票机电路总图二、实验数据及结论1.设计选题A:累加器(1)仿真波形①CLK为时钟信号,CLRN为异步清零端,A1/A2/A3/A4为四位BCD码输入,QD/QC/QB/QA为低四位累加结果,C为进位输出,ENP为使能端。

从仿真波形可以看出当CLRN和ENP都为高电平时,累加器正常工作,行使累加的功能;当ENP为低电平时,输出处于保持状态,当ENP回到高电平时,输出继续累加;当CLRN为低电平时,输出清零,当CLRN回到高电平时,输出从新开始累加。

图2.11 个位加法电路波形仿真②CLK为信号输入端,CLRN为异步清零端,ENP为使能端,QD/QC/QB/QA为累加结果的高四位输出,BAOJING为累加溢出时的报警信号。

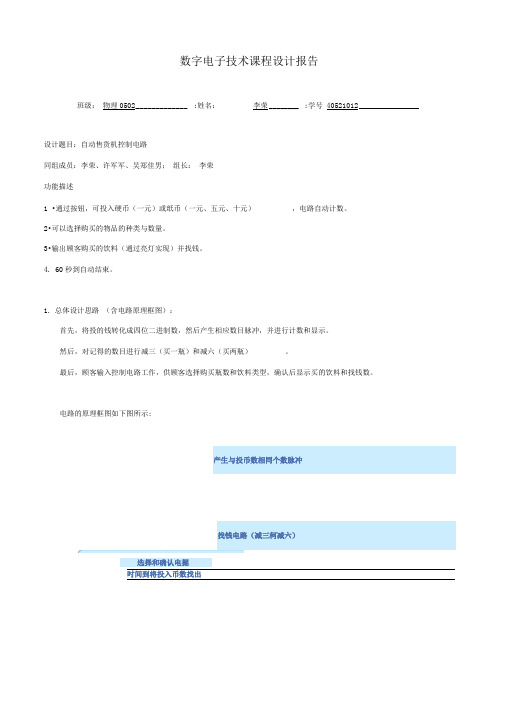

数字电子技术课程设计报告自动售货机控制电路

数字电子技术课程设计报告班级:物理0502 _____________ ;姓名:李荣________ ;学号40521012 _______________设计题目:自动售货机控制电路同组成员:李荣、许军军、吴郑佳男;组长:李荣功能描述1 •通过按钮,可投入硬币(一元)或纸币(一元、五元、十元),电路自动计数。

2•可以选择购买的物品的种类与数量。

3•输出顾客购买的饮料(通过亮灯实现)并找钱。

4. 60秒到自动结束。

1.总体设计思路(含电路原理框图):首先,将投的钱转化成四位二进制数,然后产生相应数目脉冲,并进行计数和显示。

然后,对记得的数目进行减三(买一瓶)和减六(买两瓶)。

最后,顾客输入控制电路工作,供顾客选择购买瓶数和饮料类型,确认后显示买的饮料和找钱数。

电路的原理框图如下图所示:产生与投币数相同个数脉冲找钱电路(减三柯减六)吋间到将投入币数找出选择和确认电掘输出饮料并找钱ra F~l F~O- 4 o <zrA 二二Z>EVCCQB A QA CLK< CT£N r RCO - ue MAX/MIN DCLOAE JQD CGNDD74工作情况:① 按1、2、3号开关投入1、5或10元钱,数码管显示投钱数。

② 顾客按K 键选择两种饮料,按A 选择买一瓶还是两瓶(只有当投的钱数够买相应饮料适才显示瓶 数)。

③ 按C 键确认后显示购买方案和找钱数。

④ 若超过60秒没有确认购买方案,则显示时间到,且找钱数显示为0,但是有电路找出所投币数。

2. 个人承担的工作:我承担的工作主要数钱(脉冲发生和计数)电路、以及方案的整体设计和电路连接以及功能完善。

该部分电路由三个开关电路实现投币,一片 74191实现计数脉冲产生和一片 74163芯片实现数钱。

具体思路:1. 用三个开关电路实现投币模拟(1开关表示投1块,2开关表示投5块,3开关表示投10块)。

2. 将投入的钱数转化为四位二进制数(用组合逻辑实现)送到74191置数端,如此同时将一低电平 送入LOAD ,向74191置数(此时时钟脉冲被限制),然后使74191下行计数(同时脉冲输入到 74163 芯片),直到数到0,将脉冲封锁。

自动售票机电路

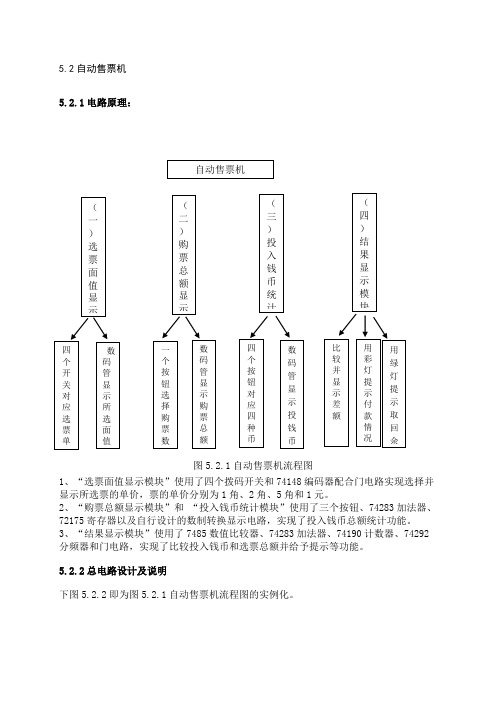

5.2自动售票机 5.2.1电路原理:图5.2.1自动售票机流程图1、“选票面值显示模块”使用了四个拨码开关和74148编码器配合门电路实现选择并显示所选票的单价,票的单价分别为1角、2角、5角和1元。

2、“购票总额显示模块”和 “投入钱币统计模块”使用了三个按钮、74283加法器、72175寄存器以及自行设计的数制转换显示电路,实现了投入钱币总额统计功能。

3、“结果显示模块”使用了7485数值比较器、74283加法器、74190计数器、74292分频器和门电路,实现了比较投入钱币和选票总额并给予提示等功能。

5.2.2总电路设计及说明下图5.2.2即为图5.2.1自动售票机流程图的实例化。

自动售票机(一)选票面值显示(二)购票总额显示(三)投入钱币统计(四)结果显示模块四个开关对应选票单数码管显示所选面值一个按钮选择购票数数码管显示购票总额四个按钮对应四种币数码管显示投钱币比较并显示差额用彩灯提示付款情况用绿灯提示取回余㈠选票面值显示模块电路:图5.2.3选票面值显示模块电路拨码开关拨到高电平,经过非门进入74148编码器,编出对应面值的数值,再通过7447显示译码器译出数字并由数码管显示出来。

此模块显示最近的选中票的面值,即选中多个单价后,不会出现乱码,而是显示最后选择的单价,同时为“购票总额显示模块”提供计算的单价数值。

㈡购票总额显示模块电路:“购票总额显示模块”电路与“投入钱币统计模块”的“数制转换显示电路”电路结构相同,如下图5.2.4所示。

㈢投入钱币统计模块电路:图5.2.5 投入钱币统计模块电路投入钱币的面值分别由指定按钮输入。

按下按钮,通过门电路把对应的数值输入74283加法器进行累加,输出数值后由74175寄存器保存前一次输入,待有下一个数值输入,即可再次累加,通过显示电路显示出来。

用门电路实现数制转换显示电路,与“购票总额显示模块”的显示电路功能相同。

㈣结果显示模块电路:“结果显示模块”电路。

EDA课程设计—自动售票机

燕山大学EDA课程设计报告书题目:自动售票机姓名:班级:学号:成绩:(注:此文件应以同学学号为文件名)一、设计题目及要求1.设计题目:自动售票机2.设计要求:⑴、每次投一枚硬币,但可以连续投入数枚硬币。

硬币种类两种:1元和5角,各用一个按键表示。

⑵、设定票价为2.5元,每次售一张票。

购票时先投入硬币,当投入的硬币总金额达到或超过票的面值时,用LED发出指示,这时可以按取票键取出票。

⑶、如果所投硬币超过票的面值则会有LED提示找零钱,取完票以后按找零键则可以取出零钱。

⑷、用两位数码管显示已投币金额,若刚好投币2.5元,取票后金额归零;若投币超过2.5元,取票后显示找零金额,按下找零键后金额再归零。

二、设计过程及内容(包括○1总体设计的文字描述,即由哪几个部分构成的,各个部分的功能及如何实现方法;○2主要模块比较详尽的文字描述,并配以必要的图片加以说明,但图片数量无需太多)1.总体结构如下:总体设计思路:此自动售票系统总共有5个主要模块,分别是:累加模块,比较器模块,找零模块,数字转换模块,显示器模块。

⑴、累加模块实现金额的累加功能。

实现方法:该模块设置3个输入口(包括5角、1元、复位),8个输出口(B1—B8)。

该模块将在给五角或一元高电平的同时实现金额的累加,复位则会将会对其进行清零。

该模块由一片8位的加法器,2片4位寄存器及简单门电路组成,利用8位加法器将输入的金额(5、10)进行二进制相加(00000101、00001010),通过寄存器后返回到加法器实现累加功能。

复位键则与寄存器复位清零短CLRN相连,实现复位的功能。

⑵、比较器模块实现与票价进行比较的功能。

实现方法:该模块设置了8个输入口(A0—A7)1个取票口,4个输出口。

该模块将累加的钱币与2.5元的票价比较,如果累加金额高于票价则黄灯亮,小于票价则红灯亮,等于票价则绿灯亮。

给取票输入端高电平则会出票。

该模块由一片八位比较器及门电路组成,输入的信号与二进制的票价相比较(00011001)。

自动售票机的涉及

电子技术基础课程设计报告自动售票机电路设计姓名:学号:专业班级:指导老师:所在院系:电气与信息工程学院日摘要本设计是自动售邮票机,自动售邮票机主要由输入(投币、选票)、复位、报警、累加钱、找钱、给票电路组成。

找钱(投钱、选票)电路是将投入的硬币转化成脉冲信号,若投入硬币时,端口显示出高电平,未投入硬币时,端口显示出低电平。

控制电路是用来控制电路运行并清零等。

报警电路是如果投入硬币钱数不足,则报警提示。

累加钱电路用以计算投入硬币累加值既而判断是否找钱,给票。

找钱电路找回多余的钱。

给票电路是在累加钱到所买邮票价格时给出邮票。

其中,累加钱电路要用数码管显示,显示2位即可。

给出邮票时,要用不同颜色的灯显示,用不同颜色的发光二极管就行。

找钱电路要用数码管显示出来,显示1位即可。

本设计采用的主要方法是设计单元电路。

总体方案化整为零,分解成若干子系统或单元电路,逐个设计。

其中,选票电路的设计是采用门电路、寄存器(74HC175N)等元件组成。

投币电路的设计是采用应用四个开关通过是否闭合输入对应的二进制信号的,开关闭合相当于输入高电平1,开关断开相当于输入低电平0,把投入1角、2角、5角、一元(10角)对应的投币信号转化成输出的二进制代码。

累加钱电路的设计是采用门电路、加法器(74LS283D)、寄存器(74LS183D)和数码管显示器等元件组成。

复位电路的设计是采用门电路、电容、开关等元件组成,当成功给票后,通过复位信号的输入来使电路清零。

找钱电路的设计是采用门电路、减法器、译码器、数码管显示器等元件组成的。

主要实现找钱的功能,而且找钱的多少可以通过数码管显示出来。

报警和给票电路的设计是采用门电路、数值比较器、蜂鸣器、译码器、发光二极管等元件构成。

当给出不同的票时会有不同颜色的二极管发光,如果投入的钱不足以买需要的票时蜂鸣器就会发出报警信号。

本设计取得的结果是设计出来的电路可以较好的完成设计要求,每按一次只能售出一张邮票,如果投入硬币钱数不足,则报警提示。

用VHDL设计的地铁自动售票机控制器

作者:杨海平,江南大学物联网工程学院微电子11级在网上看博文,偶然进入了EEFOCUS网站,感觉网站的气氛很好,由此我也萌生了写博文的念头,今天特地申请了账号,开始写第一篇博文,写些关于自己学习,自己思考的东西,希望能督促自己继续学习,勤于思考吧。

今天写的东西是学习VHDL中的一个小实验,自己用状态机实现了。

1.实验要求设计一个地铁自动售票机的控制器电路,要求如下:1)有两元,三元两种地铁车票。

只能用五角,一元两种硬币购票;2)预先选择车票的票价,投入硬币,数码管显示投入硬币的金额,“确认”后给出车票,找零,并置金额显示为零,并可按“取消”同样退还硬币,并置金额显示为零。

2.实验代码-------------------------------library ieee;use ieee.std_logic_1164.all;---------------------------------entity metro isport( st2,st3:in std_logic;--选择两元还是三元车票1有效clk,rst:in std_logic;--rst 1 有效coin1,coin2:in std_logic;--coin1表示5角硬币,coin2表示1元硬币1有效ok,cancel:in std_logic;--ok表示确认购票,cancel表示退换硬币0有效ssd1,ssd2:out std_logic_vector(7 downto 0);--两位数码管显示金额tout2,tout3:out std_logic;--给出两元,三元车票1有效mout:out std_logic--退出钱款1有效);end metro;-----------------------------------------architecture bhv of metro istype state is(s0,s5,s10,s15,s20,s25,s30);--s0表示没有投硬币,s5表示五角状态,s10表示一元状态,依次类推,最多只能投3元signal pre_state,next_state:state;begin-------------------------------------------------------------process(clk,rst)--复位操作beginif(rst = '1') thenpre_state <= s0;elsif(clk'event and clk = '1') thenpre_state <= next_state;end if;end process;------------------------------------------------------------process(rst,coin1,coin2,st2,st3,ok,cancel)--状态机的编写beginif(rst = '1') thentout2 <= '0';tout3 <= '0';mout <= '0';ssd1 <= "11000000";ssd2 <= "11000000";elsif(cancel = '1') thennext_state <= s0;ssd1 <= "11000000";ssd2 <= "11000000";elsecase pre_state iswhen s0 =>ssd1 <= "11000000";ssd2 <= "11000000";tout2 <= '0';tout3 <= '0';mout <= '0';if(coin1 = '1') then next_state <= s5;elsif(coin2 = '1') then next_state <= s10;end if;when s5 =>ssd1 <= "10010010";ssd2 <= "11000000";tout2 <= '0';tout3 <= '0';mout <= '0';if(coin1 = '1') then next_state <= s10;elsif(coin2 = '1') then next_state <= s15;end if;when s10 =>ssd1 <= "11000000";ssd2 <= "11111001";tout3 <= '0';mout <= '0';if(coin1 = '1') then next_state <= s15;elsif(coin2 = '1') then next_state <= s20;end if;when s15 =>ssd1 <= "10010010";ssd2 <= "11111001";tout2 <= '0';tout3 <= '0';mout <= '0';if(coin1 = '1') then next_state <= s20;elsif(coin2 = '1') then next_state <= s25;end if;when s20 =>ssd1 <= "11000000";ssd2 <= "10100100";if(coin1 = '1') then next_state <= s25;elsif(coin2 = '1') then next_state <= s30;elsif(st2 = '1' and ok = '1') then mout <= '0';tout2 <= '1';tout3 <= '0';next_state <= s0;end if;when s25 =>ssd1 <= "10010010";ssd2 <= "10100100";if(coin1 = '1') then next_state <= s30;elsif(st2 = '1' and ok = '1') then mout <= '1';tout2 <= '1';tout3 <= '0';next_state <= s0;end if;when s30 =>ssd1 <= "11000000";ssd2 <= "10110000";if(st2 = '1' and ok = '1') then mout <= '1';tout2 <= '1';tout3 <= '0';next_state <= s0;elsif(st3 = '1' and ok = '1') then mout <= '0';tout3 <= '1';tout2 <= '0';next_state <= s0;end if;end case;end if;end process;----------------------------------------------------------------------------------------------end bhv;3.仿真代码clk_gen:process--只列出了主要的代码,这是时钟产生激励beginclk <= '1';wait for 5 ns;clk <= '0';wait for 5 ns;end process clk_gen;--------------------------init : PROCESS --这是模拟先投两元硬币,买两元票,再投三元硬币,买三元票beginrst <= '1';cancel <= '0';ok <= '0';coin1 <= '0';coin2 <= '0';st2 <= '0';st3 <= '0';wait for 5 ns;coin2 <= '1';rst <= '0';wait for 10 ns;------------------coin2 <= '0';wait for 10 ns;coin2 <= '1';wait for 10 ns;coin2 <= '0';wait for 10 ns;coin2 <= '0';st2 <= '1';ok <= '1';wait for 10 ns;ok <= '0';st2<= '0';-----------coin2 <= '1';wait for 10 ns;coin2 <= '0';wait for 10 ns;coin2 <= '1';wait for 10 ns;coin2 <= '0';wait for 10 ns;coin2 <= '1';wait for 10 ns;coin2 <= '0';wait for 10 ns;st3 <= '1';ok <= '1';wait for 100 ns;wait;-- wait;END PROCESS init;仿真结果如下:(Quartus II环境下的仿真)结果与预期的一致,大家也可以自己编写试试看。

数电售票机实验报告

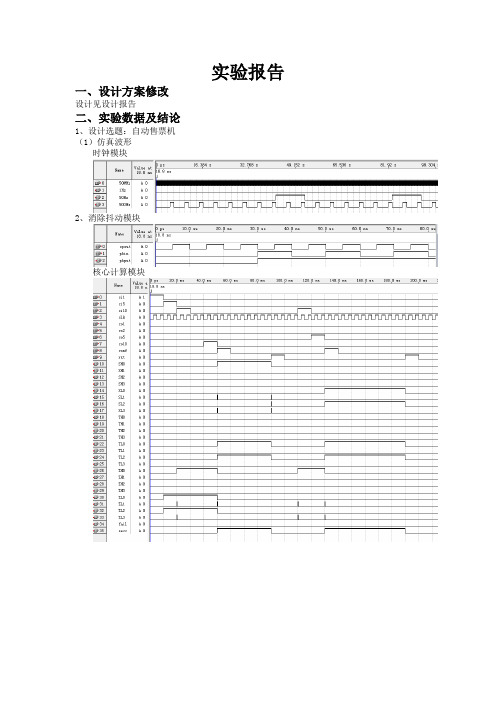

实验报告一、设计方案修改设计见设计报告二、实验数据及结论1、设计选题:自动售票机(1)仿真波形时钟模块2、消除抖动模块核心计算模块显示模块报警模块(2)硬件测试情况三个按键SW1,SW2,SW3输入分别代表1角,5角,1元硬币的投入情况,相应按动一次表示投入一枚硬币,记投入钱数为A,当有按键输入时,实验箱中前两位数码管显示A的数值。

四个拨码开关输入分别代表1角,2角,5角,1元的票额选择情况,拨动相应开关使其置一代表选择购买对应票额的车票,记选择票额为B。

在投入硬币和选择车票结束后,第四个按键SW4表示确定,当按下后代表购票结束。

分为以下两种情况一、A>B设A-B=C则此时实验箱中第三四个数码管显示C的数值,即找零钱数。

B=1角,实验箱上方红色LED灯点亮。

B=2角,实验箱上方黄色LED灯点亮。

B=5角,实验箱上方绿色LED灯点亮。

B=1元,实验箱右侧红色LED灯点亮。

实验箱第五六个数码管显示累计售票额。

二、A<B此时实验箱中所有红色LED灯同时点亮,并在三秒后同时熄灭。

实验箱中第三四个数码管显示A的数值,即退币钱数。

(3)实验结论由仿真波形和硬件和硬件测试表可知,计时器电路逻辑功能与要求完全符合,说明计时器功能正确,符合设计要求。

三、实验总结与体会1、通过本次数字电子技术基础实验,增加了对时序逻辑电路和组合逻辑电路的感性认识,在实际中了解并实践了综合逻辑电路设计的整个过程。

2、通过本次实验,加深了对计数器,译码器,触发器,等典型芯片以及Verilog语言实际应用的认识,了解了在实际中理论课所讲授的芯片应该如何使用,为以后运用数字电子技术知识进行实际问题解决积累了经验。

3、通过本次试验,我对书中的知识更加了解,为学习打好了基础。

从实际问题出发,进行逻辑抽象,进行相应芯片的功能查询和级联方式设计,从拿到问题开始,知道了从头了解解决一个实际问题的方法和过程。

4、对本次实验,一开始并不了解显示模块的工作方式,在其他同学的讲解下才逐渐懂得了它的工作方式,使得本次实验可以完成。

自动电子售票机.

课程设计课程名称_电子技术综合设计与实践题目名称自动电子售票机学生学院自动化学院专业班级学号学生姓名指导教师_____________________ 2013年12 月06日广东工业大学课程设计任务书一、课程设计的内容1)利用各种器件设计自动电子售票机。

2)利用DE2教学开发板对所设计电路进行验证。

3)总结电路设计结果。

二、课程设计的要求与数据设计要求包括:1. 售卖的票共有3种,每种的单价用1个LED显示(面额分别为3元、5元、8元);2. 用3个按键分别代表这3种面额的票,按下按键就表示选中该种面额的票。

3. 用1个按键表示表示购买票的数量,按1次数量加1;4. 用3个按键,分别代表投入的钱币的面值,共有3种情况:1元,2元,5元,每个按键可以按多次,按键的次数表示投入该种面值钱币的数量;5. 当投入的钱不够的时候,用1个红灯亮来表示,同时用LED显示所缺的钱数额;当投入的钱达到或者超过所需的金额时,用1个绿灯亮闪烁来表示,闪烁持续时间为0.5S,同时用LED显示应找回给用户的钱数额。

三、课程设计应完成的工作(一)设计思路1. 学习要求:序控制电路。

画出自动电子售票机的整机逻辑电路图,掌握自动电子售票机的工作原理及其设计方法,并对各种元器件的功能和应用有所了解。

并能对其在电路中的作用进行分析。

例如:全加器74LS283、数值比较器74LS85、RS锁存器74LS279以及十进制同步加/减计数器74LS192,乘法器模块mult4等。

2. 设计思路设定一个清零控制,用于清除上一次售票的显示,高电平清零。

可以用锁存器锁存不同种类票的面额。

投入钱币的面值总额可以用全加器累加得到。

数值比较器可以用来判断购票的钱币面值总额是否达到票款的总额。

由于DE2板上仅提供50MHz和27MHz的时钟,需设定lpm_counter分频器(或者74LS292、74LS56分频器)对系统时钟进行分频,再结合计数器得到0.5秒的时间长度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

河南城建学院电子技术基础课程设计报告

自动售票电路

姓名:尹祖亮

学号:091410147

专业班级:电气工程及其自动化

指导老师:樊晓红

所在院系:电气与电子工程系

2012年6月21 日

河南城建学院本科课程设计报告一、指导教师评语:

二、成绩:

河南城建学院本科课程设计报告

摘要

本设计是自动售票机,该电路的第一部分的作用即是产生邮票和发出少钱信号。

首先,就是用74HC148的8线—3线编码器来级连成16线—4线制的编码器来把1角,两角,五角,一元的邮票钱数转化成一个二进制代码的0或1,然后,通过输出组成或非门来控制寄存器的时钟信号,同时,输出与寄存器相连,经过寄存器来寄存邮票的钱数,之后和数值比较器相连与投币的钱数比较,得出是否出邮票。

同时把输出的信号经过与非电路连回到寄存器的复位端,并且给出一个找钱信号。

投币的电路用级连转化成二进制代码并与全加器相连,二者可以连续的相加,之后把相加的信号寄存到寄存器中,再通过数值比较器进行比较。

同时把累加得到的钱用数码管显示出来。

在经过找钱信号发出,邮票的钱数与累加得到的钱数进行相减,得到一个二进制代码,然后借到数码管上显示找出的钱数。

河南城建学院本科课程设计报告

目录

1 概述 (4)

1.1设计目的 (4)

1.2任务计划 (4)

1.3设计要求 (4)

2 系统总体方案及硬件设计 (5)

2.1电路的总体原理框图 (5)

2.2 工作原理 (5)

2.3 所需器件 (6)

3 各模块设计 (7)

3.1数字电子设计的部分结构图 (7)

3.2投币及累加部分的结构图 (7)

3.3找钱电路设计的部分结构图 (8)

4课程设计体会 (10)

参考文献 (10)

附1:系统原理图…………………………………………………………………

河南城建学院本科课程设计报告

1 概述

1.1 设计目的

1.学会应用数字电路课程的理论知识独立完成一个课程设计。

2.能够通过设计掌握独立分析和解决实际问题的能力。

3.通过设计掌握数字电路设计和制作的一般方法。

4.学会使用和查找设计有关的书籍和资料。

5.通过对实际电路的方案的分析比较、设计计算、元件选取、安装调试环节,初步掌握简单实用电路的分析方法和工程设计。

6.学会撰写课程设计总结报告,培养严肃认真的工作作风和严谨的科学态度。

1.2 任务计划

⒈以数字电子技术基础的基本理论为指导,将设计实验分为基础型和系统型两个层次,基础型指基本单元电路设计与调试,系统型指若干个模拟、数字基本单元组成并完成特定功能的电路设计、调试。

⒉学习EDA电路设计方法,能熟练掌握理论电路应用实际。

⒊学习电子系统电路的安装调试技术。

1.3 设计要求

1.设计一个自动售票机,此机只售1角、2角、5角和1元四种邮票。

售哪一种邮票按票额指令即可。

每按一次只能售出一张邮票。

2.如果投入硬币钱数不足,则报警提示。

如果投入硬币足够则自动送出一张邮票,并用不同颜色指示灯显示出来,多余的钱数可以找回,

3.找回的钱数同时用数码管显示出来。

4.售票机应有累加钱数的功能,累加的钱数用数码管显示出来。

河南城建学院本科课程设计报告

2 设计总体方案及硬件设计

1. 电路的总体原理框图

↘

↗

↗ ↘

→ → →

↓

图2—1总体电路框图

2. 工作原理

本设计的自动售票机原理电路采用软硬件相结合的方法,其原理框图如图1所示。

它由数据比较器,报警电路,累加电路,4位串行加法器,十进制计数器,单稳态触发器,传感器及各种控制电路组成。

判断电路用数字比较器组成,它会输出三种结果中的一种,第一种结果,当投入硬币面值小于所选邮票面值时,该端连接的报警器会自动报警,这里接红灯;第二种结果,当投入硬币面值等于所选邮票面值时,该端输出的信号分别和前面的邮票选择信号接与门,最后分别接一种颜色的指示灯;第三种结果,当投入硬币面值大于所选邮票面值时,在用不同的指示灯显示不同的邮票的同时,系统还要完成找钱功能。

把投币信号接在4位串行加法器的A 端,同时把选邮票信号连到B 端,然后把四位输出信号接一个BCD-七段显示译码器,而译码器的输出端连着数码显示器。

选票电路

识别电路

比较电路

报警显示电路

累加电路

显示电路

找钱电路

显示电路

3.所需器件

型号功能数量74AS08N 反相器9 74LS283 加法器 1 74LS183 全加器 1 DCD-HEX 数码显示器 3 LED 发光二极管 5 74LS85 数值比较器 1 74LS02 或非门10 74LS08 与门13 74LS175 寄存器 2 DIPSW 开关8

河南城建学院本科课程设计报告

3 各模块设计

3.1 数字电子设计的部分结构图:

首先是邮票的产生的结构图以及他们之间的发生关系,如下图所示:

图3—1出邮票与报警电路部分

分析所示,该电路图是产生有票的以及钱数少时会产生自动报警信号,电路的组成部分,有8线-3线的编码器,或非门与非门以及二极管和175寄存器,以及283的数字比较器,发光二极管等器件组成。

该功能可以表述成邮票的钱数与寄存器之间的关系,如果邮票的钱数比投进来的钱数大时就会自动报警,否则,就会出邮票并且会伴随着找钱现象。

这种情况下会发生下一种情况。

3.2 投币及累加部分的结构图

该电路图是投币的装置以及钱数之间的叠加功能和叠加到的钱用数码管来表示出来,其电路设计图如下图所示:

河南城建学院本科课程设计报告

图3—2投币及累加部分电路图

该电路的组成可以有283的全加器,和175组成寄存器,数码管显示器以及电源和电容和电阻,外加一个反相器,其结果组成就是这样。

该电路的结构功能所完成的是投入钱币的叠加之后通过相应的电路来完成其逻辑功能,投入钱的数目,首先会同投入的钱进行相加,之后经过寄存器把它们寄存到寄存器中来,然后通过数码管把累加到的钱显示出来,并且通过控制电路来实现寄存器的清零行动,使其回到初始的状态。

并且通过此电路还会产生一个找钱的信号,这样的话就可以用数码管来显示找出多余的钱。

3.3 找钱电路设计的部分结构图

该电路使用来找钱的,所以应用到减法器,该电路图如下:

河南城建学院本科课程设计报告

图3—3找钱部分电路图

分析其电路图我们不难看出,此电路图其实是一个全加器所组成的,其电路图是通过反相器来实现其逻辑功能的,首先是通过反相器把原码变换成补码的形式来进行相加减的,从而来实现其加法的工作原理的,其工作过程可以分成如下几步:当提示灯亮时,会发出一个低电平的信号使其所有的工作全部被低电平封住不能够正常的工作,使其不会产生一个找钱的信号,避免发生错误的信号,另一种情况就是那提示灯不会亮时会给出一个高电平的信号使其找钱电路可以完全的工作,不会受其他的信号影响。

河南城建学院本科课程设计报告

4 课程设计体会

经过三天的课程设计,我受益匪浅,我想这对于自己以后的学习和工作都会有很大的帮助。

在这次设计中遇到了很多实际性的问题,在实际设计中才发现,书本上理论性的东西与在实际运用中的还是有一定的出入的,所以有些问题不但要深入地理解,而且要不断地更正以前的错误思维。

一切问题必须要靠自己一点一滴的解决,而在解决的过程当中你会发现自己在飞速的提升。

在实验过程中,根据任务书的要求,查找资料,设计了电路方案,在差额计算模块、投币模块、选票模块,有几种预想方案,和同组人员仔细分析后确定了一套简单实用的方案。

在设计过程中,由于对电子芯片的了解较匮乏,在选择芯片的问题上花费了不少时间,在翻阅有关资料和上网搜索后,才确定了要选择那些器件,不过通过对这些资料的查看,也了解了很多课本上没有的东西,通过和同组人员的共同努力,我们终于设计好了各个模块的电路。

通过课程设计,我学到了很多,收获了很多,我觉得课程设计是一个从理论到实际应用的过程,也是和同组人员配合的实践,独自一人来设计一个东西是很困难的。

对我而言,知识上的收获重要,精神上的丰收更可喜,挫折是一份财富,经历是一份拥有。

参考文献

⑴清华大学电子学教研组阎石,等《数字电子技术基础》(第五版)高等教育出版社

⑵赵淑范,王宪伟《电子技术实验与课程设计》清华大学出版社

⑶清华大学电子学教研组童诗白,华成英,等《模拟电子技术基础》(第四版)高等教育出版社

⑷《电工与数字电子技术实验》河南城建学院出版。