EDA实训内容-实验报告

EDA实验报告

EDA实验报告班级:姓名:目录实验一:七段数码显示译码器设计 (1)摘要 (1)实验原理 (1)实验方案及仿真 (1)引脚下载 (2)实验结果与分析 (3)附录 (3)实验二:序列检测器设计 (6)摘要 (6)实验原理 (6)实现方案及仿真 (6)引脚下载 (7)实验结果与分析 (8)实验三:数控分频器的设计 (11)摘要 (11)实验原理 (11)方案的实现与仿真 (11)引脚下载 (12)实验结果及总结 (12)附录 (12)实验四:正弦信号发生器 (14)摘要 (14)实验原理 (14)实现方案与仿真 (14)嵌入式逻辑分析及管脚下载 (16)实验结果与分析 (17)附录 (18)实验一:七段数码显示译码器设计摘要:七段译码器是一种简单的组合电路,利用QuartusII的VHDL语言十分方便的设计出七段数码显示译码器。

将其生成原理图,再与四位二进制计数器组合而成的一个用数码管显示的十六位计数器。

整个设计过程完整的学习了QuartusII的整个设计流程。

实验原理:七段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA\CPLD中来实现。

本实验作为7段译码器,输出信号LED7S的7位分别是g、f、e、d、c、b、a,高位在左,低位在右。

例如当LED7S 输出为“1101101”时,数码管的7个段g、f、e、d、c、b、a分别为1、1、0、1、1、1、0、1。

接有高电平段发亮,于是数码管显示“5”。

实验方案及仿真:I、七段数码显示管的设计实现利用VHDL描述语言进行FPGA上的编译实现七段数码显示译码器的设计。

运行QuartusII在G:\QuartusII\LED7S\下新建一个工程文件。

新建一个vhdl语言编译文件,编写七段数码显示管的程序见附录1-1。

eda技术实验报告

EDA技术实验报告1. 背景介绍EDA(Exploratory Data Analysis)是指探索性数据分析,是数据科学和机器学习中一项重要的任务。

通过EDA技术,我们可以对数据集进行可视化和统计分析,从而深入了解数据的特征和结构,为后续的数据处理和建模提供指导。

2. 实验目的本实验旨在通过使用EDA技术来分析一个给定的数据集,并从中获取有价值的信息。

通过实践,我们将深入了解EDA技术的应用和优势。

3. 实验步骤步骤1:导入数据首先,我们需要将实验所需的数据导入到Python的数据分析库中。

我们可以使用pandas库读取数据集,并将其存储为DataFrame对象,以便后续的分析和处理。

import pandas as pd# 读取数据集data = pd.read_csv('data.csv')步骤2:数据概览在进行数据分析之前,我们先要对数据进行整体的了解。

我们可以通过以下几个步骤来获取数据的概览信息:1.查看数据的前几行,了解数据的结构和格式。

data.head()2.查看数据的基本统计信息,包括均值、标准差、最小值、最大值等。

data.describe()3.检查数据中是否存在缺失值或异常值。

data.isnull().sum()步骤3:数据可视化EDA技术的核心之一是数据可视化。

通过可视化数据,我们可以更直观地理解数据的分布和关系。

下面是几种常用的数据可视化方法:1.直方图:用于展示数值型数据的分布情况,可以帮助我们了解数据的集中趋势和离散程度。

data['column'].plot.hist()2.散点图:用于展示两个数值型变量之间的关系,可以帮助我们发现数据的相关性。

data.plot.scatter(x='column1', y='column2')3.条形图:用于展示类别型数据的分布情况,可以帮助我们比较不同类别之间的差异。

EDA技术及应用实训报告

EDA技术及应用实训报告

1.设计自动化技术

设计自动化技术(Design Automation)是一项将新科技与新技术结合在一起的实际工程学科,它将工程设计和制造过程的各个方面进行自动建模、自动仿真、自动集成,从而实现对制造技术的模拟和控制,实现优化系统设计和提高设计效率的目的。

设计自动化是达到设计自动化的途径之一,它强调了“从设计中抽象出规则、流程、模型和算法”,并对它们进行自动化,从而克服了手动设计中的过程繁琐、重复劳动的缺点,为设计师提供了更快、更准、更节劳的方法。

2、EDA技术

EDA(电子设计自动化)是在电子产品设计的整个流程中使用计算机软件和硬件工具来实现设计自动化的过程,也称之为电子产品设计自动化(EDA)。

EDA技术已经发展到成熟阶段,&&主要用于电路板设计、电路仿真、CAD/CAM设计、电路布线和测试等领域。

EDA实验报告(12份).pdf

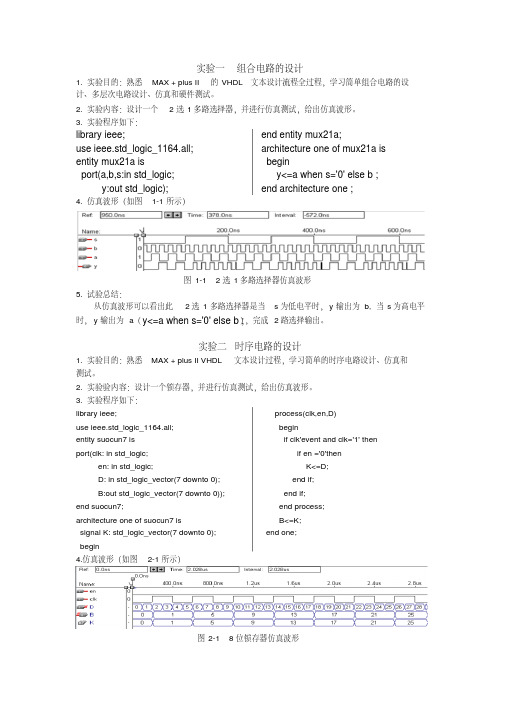

实验一组合电路的设计1. 实验目的:熟悉MAX + plus II 的VHDL 文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

2. 实验内容:设计一个2选1多路选择器,并进行仿真测试,给出仿真波形。

3. 实验程序如下:library ieee;use ieee.std_logic_1164.all; entity mux21a isport(a,b,s:in std_logic;y:out std_logic); end entity mux21a; architecture one of mux21a is beginy<=a when s='0' else b ; end architecture one ;4. 仿真波形(如图1-1所示)图1-1 2选1多路选择器仿真波形5. 试验总结:从仿真波形可以看出此2选1多路选择器是当s为低电平时,y输出为b, 当s为高电平时,y输出为a(y<=a when s='0' else b ;),完成2路选择输出。

实验二时序电路的设计1. 实验目的:熟悉MAX + plus II VHDL文本设计过程,学习简单的时序电路设计、仿真和测试。

2. 实验验内容:设计一个锁存器,并进行仿真测试,给出仿真波形。

3. 实验程序如下:library ieee;use ieee.std_logic_1164.all;entity suocun7 isport(clk: in std_logic;en: in std_logic;D: in std_logic_vector(7 downto 0);B:out std_logic_vector(7 downto 0)); end suocun7;architecture one of suocun7 issignal K: std_logic_vector(7 downto 0); beginprocess(clk,en,D)beginif clk'event and clk='1' thenif en ='0'thenK<=D;end if;end if;end process;B<=K;end one;4.仿真波形(如图2-1所示)图2-1 8位锁存器仿真波形此程序完成的是一个8位锁存器,当时钟上升沿到来(clk'event and clk='1')、使能端为低电平(en ='0')时,输出为时钟上升沿时的前一个数,从仿真波形看,实现了此功能。

EDA实验报告

EDA实验报告一、实验目的本实验旨在通过使用EDA(数据探索性分析)技术,进一步了解和分析所研究数据的特征、分布、关系以及可能存在的异常值等,从而为后续的数据建模和决策提供更加准确的依据。

二、实验步骤1. 数据收集与加载从数据源中获取所需数据集,并使用相应的数据加载工具将数据集导入到实验环境中。

多种数据源包括文件、数据库、API请求等方式均可。

2. 数据检查与预处理对导入的数据进行初步检查,包括数据类型、缺失值、异常值等方面的处理。

根据具体需求,对缺失值可以进行填充或删除操作,对异常值可以通过替换、删除或者修复的方式进行处理。

3. 数据探索性分析a) 描述性统计分析对各个变量进行描述性统计,包括计算均值、中位数、标准差等指标,以直观地了解数据的分布和变异程度。

b) 单变量分析对每个变量进行分析和探索,绘制直方图、箱线图、概率密度图等,以帮助我们了解变量的分布情况、异常值等。

c) 多变量分析使用散点图、柱状图、热力图等方式,对不同变量之间的关系进行分析。

可以通过相关性分析、协方差矩阵等方法来探索变量之间的线性关系。

4. 结果可视化在数据分析过程中,可以使用适当的可视化方法将分析结果直观地展示出来,如绘制折线图、散点图、热力图等。

可视化可以更好地理解数据的特征和趋势。

5. 异常检测与处理在探索性分析过程中,发现异常值后,需要进一步分析和决定如何处理它们。

可以采用剔除、修复等方式,使得数据能够更加符合实际情况。

6. 相关性分析对于关键变量之间的相互关系,可以使用相关性分析等统计方法来衡量它们的相关程度。

这可以帮助我们理解变量之间的影响和作用,以及它们与问题或目标变量之间的关系。

三、实验结果通过对所研究数据集的EDA实验,我们得出以下结论:1. 数据集的缺失值情况较为严重,需要进行适当的处理,以避免因缺失数据引起的结果不准确或失真的问题。

2. 变量A和变量B之间存在较强的正相关关系,即当A增加时,B 也会相应地增加;变量C则与变量A和B之间的关系较弱。

EDA实验报告完结版

EDA实验报告完结版一、实验目的本次 EDA 实验的主要目的是通过实际操作和设计,深入理解和掌握电子设计自动化(EDA)技术的基本原理和应用。

具体而言,包括熟悉 EDA 工具的使用方法,学会运用硬件描述语言(HDL)进行逻辑电路的设计与描述,以及通过综合、仿真和实现等流程,将设计转化为实际的硬件电路,并对其性能进行评估和优化。

二、实验环境本次实验所使用的 EDA 工具为_____,该工具提供了丰富的功能模块和强大的设计支持,包括原理图编辑、HDL 代码编写、综合、仿真和下载等。

实验所使用的硬件平台为_____开发板,其具备多种接口和资源,便于对设计的电路进行实际验证和测试。

三、实验内容1、基本逻辑门电路的设计与实现使用 HDL 语言(如 Verilog 或 VHDL)设计常见的基本逻辑门电路,如与门、或门、非门等。

通过编写代码,对逻辑门的输入输出关系进行描述,并进行综合和仿真,验证设计的正确性。

2、组合逻辑电路的设计与实现设计并实现较为复杂的组合逻辑电路,如加法器、减法器、编码器、译码器等。

运用 HDL 语言描述电路的功能,进行综合和仿真,确保电路在各种输入情况下的输出结果符合预期。

3、时序逻辑电路的设计与实现设计常见的时序逻辑电路,如计数器、寄存器、移位寄存器等。

在设计过程中,考虑时钟信号、同步复位和异步复位等因素,通过仿真验证时序逻辑的正确性,并对电路的性能进行分析。

4、有限状态机(FSM)的设计与实现设计一个有限状态机,实现特定的功能,如交通信号灯控制器、数字密码锁等。

明确状态转移条件和输出逻辑,通过编写 HDL 代码实现状态机,并进行综合和仿真,验证其功能的准确性。

5、综合与优化对设计的电路进行综合,生成门级网表,并通过优化工具对电路进行面积、速度等方面的优化,以满足特定的设计要求。

6、硬件实现与测试将综合后的设计下载到硬件开发板上,通过实际的输入输出信号,对电路的功能进行测试和验证。

观察电路在实际运行中的表现,对出现的问题进行分析和解决。

eda实习报告

eda实习报告一、实习概况我在xxx公司进行了为期两个月的EDA工具的实习。

在实习期间,我主要负责对公司EDA工具的测试与优化,参与了多个项目的研发,并对公司的EDA工具有了更深入的了解。

二、实习内容1.测试与优化在实习期间,我主要负责对公司的EDA工具进行测试与优化。

通过对EDA工具使用场景的模拟和错误数据的引入,我发现了一些潜在的问题,并给出了优化建议。

通过与开发团队的沟通和合作,我参与到了多个版本的升级和维护,帮助公司的EDA工具在长期使用过程中具有更高的稳定性和可靠性。

2.项目研发我也参与了公司多个项目的研发。

在项目的初期,我主要负责需求分析和功能设计。

在需求分析环节,我通过与客户的交流了解其需求,并将之转化为可执行的需求文档;在功能设计环节,我根据需求文档和业界标准,设计了完整的功能逻辑图和实现流程。

在项目的后期,我则负责对代码和文档的完善和修改,确保项目的质量和效率。

三、工作收获在这次实习中,我收获了很多技术和经验。

首先,我掌握了EDA工具的基础原理和应用场景,在对公司的EDA工具进行测试和优化的过程中,得到了很多实践经验和真知灼见。

同时,我也掌握了一定的代码调试和优化技巧,在项目研发的过程中,能够较快地解决一些常见问题。

其次,我感受到了团队合作的重要性。

在每个项目中,我都需要与开发团队、测试团队和客户进行良好的沟通和协作。

通过这个过程,我学会了如何倾听和表达,如何与他人合作,以及如何分析和解决问题。

最后,我认为行动力和自我学习精神是一名工程师必备的素质。

在工作中,我需要快速适应各种场景和环境,积极主动地解决问题和提高自己的技术。

通过不断学习和尝试,我对EDA工具和项目研发的理解更加深刻和全面。

四、总结通过这次实习,我对EDA工具和项目研发有了更深入的了解,更全面的认识了工程师需要具备的素质和能力,并提升了自己的技能和经验。

我相信,这次实习对我未来的学习和发展具有很大的帮助和启示。

eda实验报告

eda实验报告

1. 实验目的

通过本次实验,了解EDA(Electronic Design Automation)的基本概念和应用模式,并通过实际操作掌握EDA工具的使用方法和流程。

2. 实验原理

EDA是电子设计自动化的缩写,是指通过计算机技术来实现电子系统设计的各个环节的自动化。

常用的EDA工具有电路仿真、电路布局、原理图设计、印刷电路板设计等。

3. 实验步骤

3.1 电路仿真

首先,我们需打开EDA工具,并导入所需的仿真器和电路元件库。

其次,我们需绘制电路图并进行仿真,根据仿真结果进一步分析和改进电路设计。

3.2 电路布局

在电路设计完成后,我们需进行电路布局,以便更精确地计算

电路性能和参数。

在布局过程中,我们需根据电路设计需求进行

元件排布,并考虑布局紧凑性和功耗等因素。

3.3 原理图设计

电路图设计是EDA工具中非常重要的一个环节,它可以帮助

我们全面了解电路设计的各个细节,确定电路元件的类型和参数,以及进一步优化电路性能。

3.4 印刷电路板设计

在进行电路仿真、布局、原理图设计后,我们需将电路设计转

化为印刷电路板(PCB)的形式。

在进行印刷电路板设计前,我

们需考虑各个细节,在选择印刷方式、器件布局、线路距离、阻

抗匹配等方面进行优化和调整。

4. 实验结论

通过本次实验,我深刻认识到EDA工具在电子设计中的应用

和重要性,并掌握了EDA工具的基本操作方法和流程。

此外,我

了解了EDA工具在电子设计和生产中的优势和局限性,对于今后

电子设计工作的开展和优化有很大的指导意义。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、课程设计的内容1、学习EDA仿真技术,并使用Multisim仿真软件完成指定训练内容。

2、学习SOPC技术,并在FPGA上完成相关内容,掌握和理解SOPC的真正内涵。

3、通过学习了解Synopsys软件,掌握IC设计基础。

二、课程设计的要求与数据1、严格按照分组情况进行实训;2、完成指定的设计任务;3、相关设计数据要填入指定表格;4、课程设计的报告严格按照学校指定格式执行;5、实训期间不得迟到早退,否则将严肃处理。

三、课程设计应完成的工作1、学习Multisim仿真软件,并完成以下设计任务:Lab1-4必做,Lab5-9选做任意数量。

2、学习SOPC技术,并完成以下设计任务:Task1-4选作一题,Task5必做。

3、学习IC设计技术基础,并完成以下设计任务:Synopsys IC设计基础,主要学习linux基本操作,IC设计基本流程,概念,完成Design Compiler综合工具实验。

四、课程设计进程安排五、各实验相关内容和结果。

A、SOPC技术运用SOPC技术运用这一实验要求完成的是task5和选做task1-4中的一个,这里选择的是task1. A1、Task5主要是学习创建Nios2系统和通过利用Nios开发板熟悉软件设计流程。

在软件设计流程时,改Buttons的值为0xe后点击resume运行if语句后variables的值将会改变,如图示:这里附上Nios2的原理图:A2、Task1主要完成对数据存储和读取电路的设计,这里数据存储和读取电路以一个双端口SRAM 为中心,用二进制计数器产生存取地址、以十进制计数器产生欲存储的数据,读出的数据经过LED 七段译码,送LED 数码管显示。

具体内容是用一个4 位二进制计数器产生存取地址;以一个 4位的十进制计数器产生欲存储的数据;读出的数据自然也是一个4位的十进制数,将它送给七段数码管显示出来。

这里我门主要设计4位的十进制计数器和4位的二进制计数器以及七段LED显示译码器LEDSP,这里要采用16×4bit的异步双端口SRAM模块DSRAM4而库里边的lpm. lpm_componets在这里边出了些问题,所以直接从Quartus的库里边直接找lpm_ram_dp模块。

这里附上数据存储和读取电路的原理图:仿真波形:A3、对SOPC技术运用实验的总结通过SOPC技术运用实验的磨练,我们初步了解了如何创建Nios2系统和通过利用Nios开发板设计软件的技术,也在原有的基础上对Quartus软件和其中的sopc有了更深一步的了解和熟练操作。

但在其中遇到的问题也不少,基本上都是因实验室提供的软件和指导书里所依赖的软件平台版本不一样而衍生的,细心点基本上都可以解决。

在Taks1的数据存储和读取电路设计的过程中,发现指导书提供的16×4bit的异步双端口SRAM模块DSRAM4中lpm.lpm_componets库并不能用,于是利用quartus提供的lpm_ram_dp0模块代替DSRAM4。

而在参照实验指导书创建Nios2系统过程中,当进行到从 Other组件文件夹里增加 Altera PLL组件到工程里边然后启动ALTPLL MegaWizard 并且配置PLL的时候,不时出现点击pll 选项里的Launch Atlera’s AL TPLL MegaWizard选项而不会出现PLL wiard的现象,这个问题重新做一次才有可能有反应,但到现在也不知道根本原因。

B、Multisim工具的使用与实验在这里lab1-4为必做,选做的是lab6和lab9B1、lab1 单级放大电路电路原理图如下:注意,在利用simulate/analyses/DC Operating Point设置Output的时候,$3就是电路图中三极管基级上的3,$4,$7分别是发射极和集电极上的4和7。

静态仿真数据:记录数据:其波形如下:它们的相位是相差(2k+1)π动态仿真二:删除负载电阻R6后,其波形如下:其中红色波形为输出,蓝色波形为输入,故:记录数据如下表:(注此表为RL为无穷)加入5.1k欧电阻后:加入330欧电阻后:其中蓝色为输入,红色为输出。

动态仿真三:测量输出电阻R0:1、如图:2、按ctrl+r,或者alt+y3、选中元件右键properties5、VIRTUAL表示虚拟的元件. 、B2 lab2射极跟随器测量电压放大倍数:思考题:1输入和输出波形如图示:其中蓝色波形为输入,红色为输出。

2射极跟随器具有下列性能和特点:电压放大倍数接近于1,没有电压放大作用,但有电流放大和功率放大作用;输入电压与输出电压同相;输入电阻高;输出电阻低。

B3 lab3负反馈放大电路直流工作点分析记录数据如下:负反馈对失真的改善:思考题:其输出波形如图示:B4 lab4 multisim电路仿真实验瞬态分析图形:切换J2,发现数码管显示不为0示波器波形1:示波器波形2图1时,发现数码管会变化,而图2时数码管不变。

附实验原理图:B5 lab9 二阶低通滤波器1低通滤波器幅频特性曲线图和相关图形:输出输入波形(绿入蓝出):2高通滤波器幅频特性曲线图和相关图形:输出输入波形(绿入蓝出):3.带通滤波器幅频特性曲线图和相关图形:输出输入波形(绿入蓝出):B6.对Multisim工具的使用与实验的总结通过Multisim工具对单级放大电路,射极跟随器,负反馈放大电路,Multisim电路仿真和二阶低通滤波器的相关设计和操作,除了对相关电路有了更深一步的了解之外,对Multisim工具也是有了比较熟练的操作,对我们以后运用Multisim工具来对相关电路进行分析也有了更好的基础。

C.Synopsys IC设计软件入门C1 Lab1:Basic Synthesis Design Flow这里对比较重要的步骤进行数据记录:4..在输入 USE “man#error_no”in dc_shell-xg-t后,将会出现错误如下:即出现ERROR MESSAGE:VER-952e the dv menu bar “design/compile design”to synthesize your design,after synthesis,we can see the window like the picture followed,出现lab_DW01_add_0是因为合成之后DC会将RTL CODE内的“+”用实际的DESIGNWARE LIBRARY 取代。

9 “create design schematic”to see the result after synthesis,we can see the window like the pocture followed:(we can see that one adders are there used after synthesizing,because it has used the resource sharing skill)10,we can guess it must be ripple adder from schematic view,and now we will afford the window related:11,to select the “lab1”,use “design/report design resources”to see what type of adder is used by design complier,and we can see the window followed:(warning:用report_design_resoure来观察的是rpl)e the dv menu bar “desing/report area”and “timing/report timing”to see the timing and area,we can see the window followed,and area=336um2,timing=0.86ns,14.pparch,因为我们有针对combination电路设定timing constraints,tool帮我们随意挑选一个可以满足1ns内完成计算的加法器。

15.we can set_implementation cla r248,and after setting we can synthtnizing again and the compile,16.“Design/report design resources”and we can see cla is the type of adder used by DC.17.”design/report area and timing/report timing”,and we can find out that area=413um2,and timing=1nsLAB 210.view the symbol view fo top,we can see the window followed:19.generate the port design to see whether the attributes have been property set,and we can see the window followed:2.2explore the schematic,“create design schematic”to see the result after synthesis,and we can see:25.check the area,timing,constraints,and we can see not all cot all of constrains meet,and the cell area of this design is cell area:1649um2,and the critical path:stat point:test->end point:timer/sec_lab_next_reg[0]/d27.generate another version of a timing report,timing->report timing,max paths per group:10,and we can find out that the longest path delay is only one,but still not hard to figure it out that many paths are close to critical path seriously.28.go back top,generate report of reference,hierarchy for top,like the window followed:29.before power optimization,we can see the timing and area power first,cell area=1520,timing=4.53,power=71.8746uw31.after power optimization,we can see the timing and area power,cellarea=1547,timing=4.80,power=66.7653,dynamic power improvecapability(%)=9.44%,and it really timing meet constraint,the truth is that the power is more perfect,but not matter timing or area are not influenced so seriouslyTHE DATA OR PICTURES OF LAB3 AND LAB4 ARE LOST,SO WE WON’T REMIND IT HERE.C2,对Synopsys IC设计软件入门实验的总结本实验主要通过相关的设计对Synopsys IC软件设计进行初步的了解。