DSP2812引脚说明

2812引脚图及原理

图1 主要元件位置示意图开发板采用一个TPS767D301芯片为整个系统供电,采用一个LED作为上电指示,添加了手动复位功能,将2812的全部引脚引出,开发板主要元件及其位置如图1所示。

标号功能描述P1~P4 DSP引脚引出P5 XMP/MCnP6 JTAGP7 电源输入表1 开发板插接件P1~P4将2812的全部有用引脚引出,以便用于扩展。

每个插接件的第一脚用方形焊盘表示。

下面图表分别描述了P1~P4的引脚排列及每个引脚的功能。

图2 P1的引脚排列引脚功能引脚功能1ADCINA72ADCINA63ADCINA54ADCINA4 5ADCINA36ADCINA2 7ADCINA18ADCINA0 9ADCINB110ADCINA0 11ADCINB312ADCINB2 13ADCINB514ADCINB4 15ADCINB716ADCINB6 17 3.3V_IO18GND 19MDRA20XA0 21MDXA22XD0 23MCLKRA24XD1 25XD226MFSXA 27MFSRA28MCLKXA 29 3.3V_IO30XD3 31GND32XD4 33SPICLKA34SPISTEA 35XD536XD6 37SPISIMOA38SPISOMI 39XRDn40XA1 41XZCS0AND1n42PWM7 43 3.3V_IO44GND表2 P1引脚功能描述图3 P2引脚排列引脚功能引脚功能1GND2 3.3V_IO 3XHOLDAn4T4CTRIP 5XWE6XA37CANTA8XZCS2n 9CANRA10SCITB 11SCIRB12PWM1 13PWM214PWM3 15PWM416XD12 17XD1318PWM519PWM620T1PWM 21XA422T2PWM 23CAP124CAP225XA526CAP327T1CTRIP28XA629GND30 3.3V_IO 31T2CTRIP32TDIRA33TCLKINA34XA735XCLKOUT36XA837C1TRIP38C2TRIP39C3TRIP40XA9表3 P2引脚功能描述图3 P3的引脚排列引脚功能引脚功能1 3.3V_IO2GND3XREADY4RESETn5XHOLDn6XA187SCIRA8XA179SCITA10XA1611XINT212XNMI/XINT13 13XINT114XA1515XD1516 3.3V_IO 17XA1418XA1319XPLLDISn20XD1421XA1222XZCS6AND7n 23XA1124XA10表4 P3引脚功能描述图5 P4引脚排列引脚功能引脚功能1XA22T3CTRIP3XD114GND5TCLKINB6XD107XD98TDIRB9XD810GND11C6TRIP12 3.3V_IO13C4TRIP14C5TRIP15CAP516CAP617T4PWM18CAP419T3PWM20XD721PWM1222XRW23PWM1024PWM1125PWM826PWM9表5 P4引脚功能描述P5为DSP的XMP/MCn选择跳线,P5不短接时,XMP/MCn引脚被下拉到GND,DSP 工作在微控制器模式,当P5被短接时DSP工作在微处理器模式。

2812引脚

图 1-2 179 引脚 BGA 封装底视图

被锁存在 XINTCNF2 寄存器中,通过软件

可以修改这种模式的状态。此信号是异步

输入,并与 XTIMCLK 同步

外部 DMA 保持请求信号。 XHOLD 为低

电平时请求 XINTF 释放外部总线,并把所

有的总线与选通端置为高阻态。当对总线

XHOLD E7

159

—

I

PU 的操作完成且没有即将对 XINTF 进行访

第1章 芯片结构及性能概述

·7·

图 1-3 176 引脚 LQFP 封装顶视图 图 1-4 128 引脚 PBK 封装顶视图

·8·

TMS320C28x系列DSP的CPU与外设(上)

名字

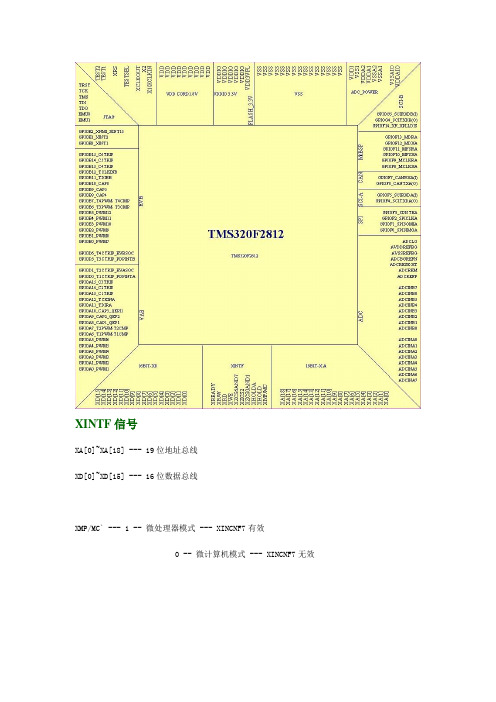

XA[18] XA[17] XA[16] XA[15] XA[14] XA[13] XA[12] XA[11] XA[10] XA[9] XA[8] XA[7] XA[6] XA[5] XA[4] XA[3] XA[2] XA[1] XA[0] XD[15] XD[14] XD[13] XD[12] XD[11] XD[10] XD[9] XD[8] XD[7] XD[6] XD[5] XD[4] XD[3] XD[2] XD[1] XD[0]

第1章 芯片结构及性能概述

z 强大的操作能力 z 迅速的中断响应和处理 z 统一的寄存器编程模式 z 可达 4 兆字的线性程序地址 z 可达 4 兆字的数据地址 z 代码高效(用 C/C++或汇编语言) z 与 TMS320F24x/LF240x 处理器的源代码兼容 4. 片内存储器 z 8K×16 位的 Flash 存储器 z 1K×16 位的 OTP 型只读存储器 z L0 和 L1:两块 4K×16 位的单口随机存储器(SARAM) z H0:一块 8K×16 位的单口随机存储器 z M0 和 M1:两块 1K×16 位的单口随机存储器 5. 根只读存储器(Boot ROM)4K×16 位 z 带有软件的 Boot 模式 z 标准的数学表 6. 外部存储器接口(仅 F2812 有) z 有多达 1MB 的存储器 z 可编程等待状态数 z 可编程读/写选通计数器(Strobe Timing) z 三个独立的片选端 7. 时钟与系统控制 z 支持动态的改变锁相环的频率 z 片内振荡器 z 看门狗定时器模块 8. 三个外部中断 9. 外部中断扩展(PIE)模块 z 可支持 96 个外部中断,当前仅使用了 45 个外部中断 10.128 位的密钥(Security Key/Lock) z 保护 Flash/OTP 和 L0/L1 SARAM z 防止 ROM 中的程序被盗 11.3 个 32 位的 CPU 定时器 12.马达控制外围设备 z 两个事件管理器(EVA、EVB)

DSP2812管脚详解

XINTF信号XA[0]~XA[18] --- 19位地址总线XD[0]~XD[15] --- 16位数据总线XMP/MC` --- 1 --微处理器模式--- XINCNF7有效0 --微计算机模式--- XINCNF7无效XHOLD` ---外部DMA保持请求信号。

XHOLD为低电平时请求XINTF释放外部总线,并把所有的总线与选通端置为高阻态。

当对总线的操作完成且没有即将对XINTF进行访问时,XINTF释放总线。

此信号是异步输入并与XTIMCLK同步XHOLDA` ---外部DMA保持确认信号。

当XINTF响应XHOLD的请求时XHOLDA呈低电平,所有的XINTF 总线和选通端呈高阻态。

XHOLD和XHOLDA信号同时发出。

当XHOLDA有效(低)时外部器件只能使用外部总线XZCS0AND1` --- XINTF区域O和区域1的片选,当访XINTF区域0或1时有效(低)XZCS2` --- XINTF区域2的片选,当访XINTF区域2时有效(低)XZCS6AND7` --- XINTF区域6和区域7的片选,当访XINTF区域6或7时有效(低)XWE` ---写有效。

有效时为低电平。

写选通信号是每个区域操作的基础,由XTIMINGX寄存器的前一周期、当前周期和后一周期的值确定XRD` ---读有效。

低电平读选通。

读选通信号是每个区域操作的基础,由xTIMINGX寄存器的前一周期、当前周期和后一周期的值确定。

注意:XRD`和XWE`是互斥信号XR/W` ---通常为高电平,当为低电平时表示处于写周期,当为高电平时表示处于读周期XREADY ---数据准备输入,被置1表示外设已为访问做好准备。

XREADY可被设置为同步或异步输入。

在同步模式中,XINTF接口块在当前周期结束之前的一个XTIMCLK时钟周期内要求XREADY有效。

在异步模式中,在当前的周期结束前XINTF接口块以XTIMCLK的周期作为周期对XREADY采样3次。

2812信号引脚详解

XINTF信号XA[0]~XA[18] --- 19位地址总线XD[0]~XD[15] --- 16位数据总线XMP/MC` --- 1 -- 微处理器模式 --- XINCNF7有效0 -- 微计算机模式 --- XINCNF7无效XHOLD` --- 外部DMA保持请求信号。

XHOLD为低电平时请求XINTF释放外部总线,并把所有的总线与选通端置为高阻态。

当对总线的操作完成且没有即将对XINTF进行访问时,XINTF释放总线。

此信号是异步输入并与XTIMCLK同步XHOLDA` --- 外部DMA保持确认信号。

当XINTF响应XHOLD的请求时XHOLDA呈低电平,所有的XINTF总线和选通端呈高阻态。

XHOLD和XHOLDA信号同时发出。

当XHOLDA有效(低)时外部器件只能使用外部总线XZCS0AND1` --- XINTF区域O和区域1的片选,当访XINTF区域0或1时有效(低)XZCS2` --- XINTF区域2的片选,当访XINTF区域2时有效(低)XZCS6AND7` --- XINTF区域6和区域7的片选,当访XINTF区域6或7时有效(低)XWE` --- 写有效。

有效时为低电平。

写选通信号是每个区域操作的基础,由XTIMINGX寄存器的前一周期、当前周期和后一周期的值确定XRD` --- 读有效。

低电平读选通。

读选通信号是每个区域操作的基础,由xTIMINGX寄存器的前一周期、当前周期和后一周期的值确定。

注意:XRD`和XWE`是互斥信号XR/W` --- 通常为高电平,当为低电平时表示处于写周期,当为高电平时表示处于读周期XREADY --- 数据准备输入,被置1表示外设已为访问做好准备。

XREADY可被设置为同步或异步输入。

在同步模式中,XINTF接口块在当前周期结束之前的一个XTIMCLK时钟周期内要求XREAD Y有效。

在异步模式中,在当前的周期结束前XINTF接口块以XTIMCLK的周期作为周期对XREAD Y采样3次。

DSP2812开发板说明书

CANL 1 2 CANH

11.2812开发板的中断

F2812有3个中断引脚:XINT1,XINT2和XNMI_INT13,每个中断可配置为上升沿或下降沿触 发,也可以被使能或禁止。

开发板板上有8个外部中断源:

EXINT[1..4] 外部扩展总线可屏蔽的中断源

EXNMI[1..2] 外部扩展总线不可屏蔽的中断源

第三章 TMS320F2812的基本系统

1. 时钟电路

开发板用30MHz外部晶体给DSP提供时钟,并使能F2812 片上PLL电路。PLL倍频系数由PLL 控制寄存器PLLCR的低4位控制,可由软件动态的修改。外部复位信号(RS)可将此4位清零(CCS 中的复位命令将不能对这4位清零)。TMS320F2812的CPU最高可工作在150M的主频下,也即是 对30M输入频率进行5倍频。

TMS320F2812的外部存储器接口包括:19位地址线,16位数据线,3个片选控制线及读 写控制线。这3个片选线映射到5个存储区域,Zone0,Zone1,Zone2,Zone6和Zone7。其中, Zone0和Zone1共用1个片选线XCS0AND1,Zone6和Zone7共用1个片选线XCS6AND7。这5个存 储区域可分别设置不同的等待周期。

7. McBSP

开发板上有一个多通道缓冲型同步串口McBSP,在板上与AIC23的同步串口相连接。

8. SPI

开发板上有一个SPI同步串口,在板上与74HC595相连接。

9. SCI

开发板上有两个SCI异步串口,经485和232电平转换芯片连接到485CON和232CON,供外部使用。

10.CAN

开发板上有一个增强型的CAN总线控制器,符合CAN2.0B接口规范,经CAN收发器驱动后连接到 CANCON,提供外部使用。CANCON连接器定义如下:

DSP2812引脚说明

O/Z

—

— 的前一周期、当前周期和后一周期的值确

定。注意: XRD 和 XWE 是互斥信号

XR/ W

N4

51

通常为高电平,当为低电平时表示处于写

—

O/Z

— 周期,当为高电平时表示处于读周期

第1章 芯片结构及性能概述

·3·

引脚号

名

字

179 针 176 针 128 针 I/O/Z

GHH PGF PBK

B13

133

XINTF 区域 6 和 7 的片选。当访问区域 6

—

O/Z

— 或 7 时有效(低)

写有效。有效时为低电平。写选通信号是

XWE

N11

84

每个区域操作的基础,由 XTIMINGx 寄存

—

O/Z

— 器的前一周期、当前周期和后一周期的值

确定

读有效。低电平读选通。读选通信号是每

XRD

M3

42

个区域操作的基础,由 XTIMINGx 寄存器

—

VSS

P8

70

53

VSS

M10 78

59

VSS

L11 86

62

VSS

K13 99

73

VSS

J14 105

—

VSS

G13 113

—

VSS

E14 120

88

VSS

B14 129

95

VSS

D10 142

—

VSS

C10 —

103

VSS VDDAIO VSSAIO

B8 153 109

B2

1

1

A2 176 128

ADC 参考电压输出(2V)。需要在该引脚 上接一个低 ESR(50mΩ~1.5Ω)的 10μF 陶 瓷旁路电容,另一端接至模拟地 ADC 参考电压输出(1V)。需要在该引脚 上接一个低 ESR(50mΩ~1.5Ω)的 10μF 陶 瓷旁路电容,另一端接至模拟地 ADC 外部偏置电阻(24.9kΩ) 测试引脚,为 TI 保留,必须悬空 ADC 模拟地 ADC 模拟电源(3.3V) 普通低侧模拟输入 ADC 模拟地 ADC 模拟地 ADC 模拟电源(3.3V) ADC 模拟电源(3.3V) ADC 数字地 ADC 数字电源(1.8V) I/O 模拟电源(3.3V) I/O 模拟地

APF控制器DSP2812控制引脚定义

APF 控制器的DSP2812控制引脚定义所研制的有源电力滤波器的控制器,主控芯片采用DSP2812,本文档将对其用于输入输出、控制和片选的引脚进行定义。

一 遥控、遥信信号本控制器将控制两个接触器的合切,同时采集两个接触器的常开触点信号和另外三个开闭信号。

所使用的2个输出口和5个输入口的定义如表1-1所示。

表1-1 DSP 控制遥信信号出线引脚号DSP 控制I/O 口名字说明20 GPIOF13 主接触器控制输出 22 GPIOF12 涌流接触器控制输出 75 GPIOA3 主接触器遥信控制输入 102 GPIOA6 涌流接触器遥信控制输入 115 GPIOD1 系统检测遥信输入 116 GPIOA11 温度检测遥信输入 117 GPIOA12 开关机遥信输入二 PWM 控制信号本控制器共有4对(8路)PWM 控制输出,可控制4个IGBT 双管(或8个IGBT 单管),同时将4个IGBT 的故障保护信号进行逻辑与后送到DSP2812芯片的PDPINTA 和PDPINTB 引脚,用于故障保护。

对所使用引脚的定义如错误!未找到引用源。

所示:表2-1 PWM 控制信号定义引脚号DSP 控制I/O 口名字说明45 GPIOB0/PWM7 A 相上桥臂PWM 输出 46 GPIOB1/PWM8 A 相下桥臂PWM 输出 47 GPIOB2/PWM9 B 相上桥臂PWM 输出 48 GPIOB3/PWM10 B 相下桥臂PWM 输出 49 GPIOB4/PWM11 C 相上桥臂PWM 输出 50 GPIOB5/PWM12 C 相下桥臂PWM 输出 98 GPIOA4/PWM5 N 相上桥臂PWM 输出 101 GPIOA5/PWM6 N 相下桥臂PWM 输出 79GPIOD5/T —3—C —T —R —I —P —-—PD —P —I —N —T —B —IGBT 故障保护信号输入110GPIOD0/T —1—C —T —R —I —P —-—PD —P —I —N —T —A —IGBT 故障保护信号输入三 指示灯控制本控制器还设计有5个指示灯,保留给厂家调试时用。

TIDSP2812中文手册

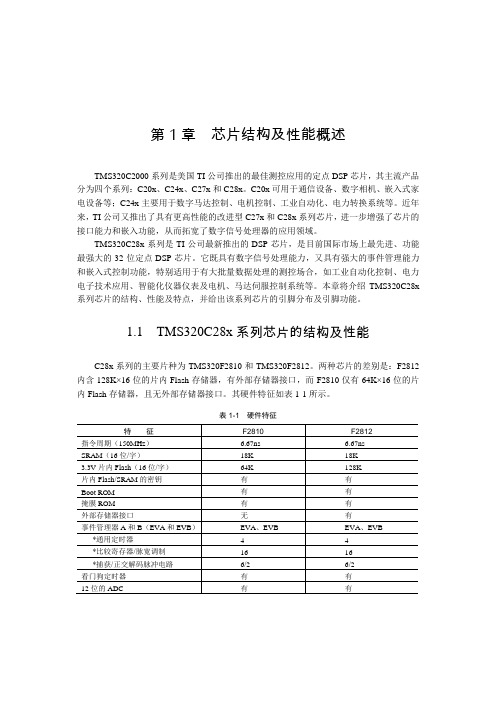

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x 系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征TMS320C28x系列DSP的CPU与外设(上)·2·注:‡“S”是温度选择(-40℃~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

输入/输出

ADC 模拟输入信号

I

I

I

I

采样/保持 A 的 8 通道模拟输入。在器件未

I

上电之前 ADC 引脚不会被驱动

I

I

I

第1章 芯片结构及性能概述

·5·

名字

ADCINB7 ADCINB6 ADCINB5 ADCINB4 ADCINB3 ADCINB2 ADCINB1 ADCINB0

引脚号 179 针 176 针 128 针

O/Z

— 的下降沿将选择寄存器的内容从 TDO 移出

带上拉功能的仿真器 I/O 口引脚 0,当

I/O/Z

TGST 为高电平时,此引脚用作中断输入。 PU 该中断来自仿真系统,并通过 JTAG 扫描

定义为输入/输出

仿真器引脚 1,当 TGST 为高电平时,此引

I/O/Z

脚输出无效,用作中断输入。该中断来自 PU 仿真系统的输入,通过 JTAG 扫描定义为

VDD

P9 75

56

VDD

P12 —

63

VDD

K12 100

74

VDD

G12 112

82

VDD

C14 112

82

VDD

B10 143

102

VDD

C8 154

110

续表

I/O/Z PU/PDS

说明

I I I I I I I I

O

O

O I I I I I I I I I I

电源信号

采样/保持 B 的 8 通道模拟输入。在器件未 上电之前 ADC 引脚不会

—

VSS

P8

70

53

VSS

M10 78

59

VSS

L11 86

62

VSS

K13 99

73

VSS

J14 105

—

VSS

G13 113

—

VSS

E14 120

88

VSS

B14 129

95

VSS

D10 142

—

VSS

C10 —

103

VSS VDDAIO VSSAIO

B8 153 109

B2

1

1

A2 176 128

·4·

第1章 芯片结构及性能概述

名字

179 针

GHH 封装

引脚号 176 针

PGF 封装

128 针

PBK 封装

TRST

B12 135

98

TCK TMS

A12 136

99

D13 126

92

TDI TDO

C13 131

96

D12 127

93

EMU0

D11 137 100

EMU1

C9

146

105

ADCINA7 B5

ADCLO

B3 175 127

VSSA1

F3 15

15

VSSA2

C5 165 117

VDDA1

F4 14

14

VDDA2

A5 166 118

VSS1

C6 163

115

VDD1

A6 162

114

VDDAIO

B2

1

1

VSSAIO

A2 176

128

VDD

H1 23

20

VDD

L1 37

29

VDD

P5 56

42

名字

XA[18] XA[17] XA[16] XA[15] XA[14] XA[13] XA[12] XA[11] XA[10] XA[9] XA[8] XA[7] XA[6] XA[5] XA[4] XA[3] XA[2] XA[1] XA[0] XD[15] XD[14] XD[13] XD[12] XD[11] XD[10] XD[9] XD[8] XD[7] XD[6] XD[5] XD[4] XD[3] XD[2] XD[1] XD[0]

179 针 GHH 封装

D7 B7 A8 B9 A10 E10 C11 A14 C12 D14 E12 F12 G14 H13 J12 M11 N10 M2 G5 A9 B11 J10 L14 N9 L9 M8 P7 L5 L3 J5 K3 J3 H5 H3 G3

引脚号 176 针 PGF 封装

158 156 152 148 144 141 138 132 130 125 125 121 111 108 103 85 80 43 18 147 139 97 96 74 73 68 65 54 39 36 33 30 27 24 21

悬空或为低电平,器件以功能模式操作,

测试复位信号被忽略

注意:在 TRST 上不要用上拉电阻。它内部

I

PD 有上拉部件。在强噪声的环境中需要使用

附加上拉电阻,此电阻值根据调试器设计

的驱动能力而定。一般取 22kΩ 即能提供足 够的保护。因为有了这种应用特性,所以

使得调试器和应用目标板都有合适且有效

的操作

167

119

ADCINA6 D5

168

120

ADCINA5 E5

169

121

ADCINA4 A4

170

122

ADCINA3 B4

171

123

ADCINA2 C4

172

124

ADCINA1 D4

173

125

ADCINA0 A3

174

126

续表

I/O/Z PU/PDS

说明

有内部上拉的 JTAG 测试复位。当它为高 电平时扫描系统控制器件的操作。若信号

第1章 芯片结构及性能概述

续表

名字

引脚号

179 针 176 针 PGF 128 针

GHH

封装

PBK

封装

封装

PU/PD I/O/Z

S

说明

XINTF 信号(仅 F2812)

可选择微处理器/微计算机模式。可以在两

者之间切换。为高电平时外部接口上的区

域 7 有效,为低电平时区域 7 无效,可使

XMP/ MC F1

XHOLDA 有效(低)时外部器件只能使

用外部总线

XZCS 0AND1

P1

44

XINTF 区域 0 和区域 1 的片选,当访问

—

O/Z

— XINTF 区域 0 或 1 时有效(低)

XZCS2 P13

88

XINTF 区域 2 的片选。当访问 XINTF 区域

—

O/Z

— 2 时有效(低)

XZCS6AND7

I

PU JTAG 测试时钟,带有内部上拉功能

JTAG 测试模式选择端,有内部上拉功能,

I

PU 在 TCK 的上升沿 TAP 控制器计数一系列的

控制输入

带上拉功能的 JTAG 测试数据输入端。在

I

PU TCK 的上升沿,TDI 被锁存到选择寄存器、

指令寄存器或数据寄存器中

JTAG 扫描输出,测试数据输出。在 TCK

ADC 参考电压输出(2V)。需要在该引脚 上接一个低 ESR(50mΩ~1.5Ω)的 10μF 陶 瓷旁路电容,另一端接至模拟地 ADC 参考电压输出(1V)。需要在该引脚 上接一个低 ESR(50mΩ~1.5Ω)的 10μF 陶 瓷旁路电容,另一端接至模拟地 ADC 外部偏置电阻(24.9kΩ) 测试引脚,为 TI 保留,必须悬空 ADC 模拟地 ADC 模拟电源(3.3V) 普通低侧模拟输入 ADC 模拟地 ADC 模拟地 ADC 模拟电源(3.3V) ADC 模拟电源(3.3V) ADC 数字地 ADC 数字电源(1.8V) I/O 模拟电源(3.3V) I/O 模拟地

O/Z

—

— 的前一周期、当前周期和后一周期的值确

定。注意: XRD 和 XWE 是互斥信号

XR/ W

N4

51

通常为高电平,当为低电平时表示处于写

—

O/Z

— 周期,当为高电平时表示处于读周期

第1章 芯片结构及性能概述

·3·

引脚号

名

字

179 针 176 针 128 针 I/O/Z

GHH PGF PBK

—

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

—

I/O/Z

PU

说明 19 位地址总线 16 位数据总线

·2·

—

I

PU 的操作完成且没有即将对 XINTF 进行访

问时,XINTF 释放总线。此信号是异步输

入并与 XTIMCLK 同步

外部 DMA 保持确认信号。当 XINTF 响应 XHOLD 的请求时 XHOLDA 呈低电平,所

XHOLDA K10

82

有的 XINTF 总线和选通端 呈高阻态 。

—

O/Z

— XHOLD 和 XHOLDA 信号同时发出。当

I/O 模拟电源(3.3V) I/O 口模拟地

VDDIO

J4

31